具有用于2晶体管竖直存储器单元的共享读取/写入数据线的存储器装置的制作方法

具有用于2晶体管竖直存储器单元的共享读取/写入数据线的存储器装置

1.相关申请

2.本技术要求2018年12月26日提交的第62/782,142号美国临时申请的优先权,所述美国临时申请以全文引用的方式并入本文中。

背景技术:

3.存储器装置广泛用于计算机和许多其它电子物品中来存储信息。存储器装置通常分类成两种类型:易失性存储器装置和非易失性存储器装置。易失性存储器装置的实例包含动态随机存取存储器(dram)装置。非易失性存储器装置的实例包含快闪存储器装置(例如,快闪存储器棒)。存储器装置通常具有存储信息的许多存储器单元。在易失性存储器装置中,如果供应功率与存储器装置断开连接,那么存储于存储器单元中的信息丢失。在非易失性存储器装置中,即使供应功率与存储器装置断开连接,存储于存储器单元中的信息也保留。

4.本文中的描述涉及易失性存储器装置。最常规易失性存储器装置将信息以电荷形式存储在包含于存储器单元中的电容器结构中。随着对装置存储密度的需求增加,许多常规技术提供缩小存储器单元的大小以便增大给定装置区域的装置存储密度的方式。然而,如果存储器单元大小收缩到某一尺寸,那么物理限制和制造约束可能对此类常规技术设置造成挑战。不同于一些常规存储器装置,本文描述的存储器装置包含可克服常规技术所面对的挑战的特征。

附图说明

5.图1示出根据本文描述的一些实施例的呈包含易失性存储器单元的存储器装置形式的设备的框图。

6.图2示出根据本文描述的一些实施例的包含二晶体管(2t)存储器单元的存储器阵列的存储器装置的一部分的示意图。

7.图3示出根据本文描述的一些实施例的包含在存储器装置的读取操作期间使用的实例电压的图2的存储器装置。

8.图4示出根据本文描述的一些实施例的包含在存储器装置的写入操作期间使用的实例电压的图2的存储器装置。

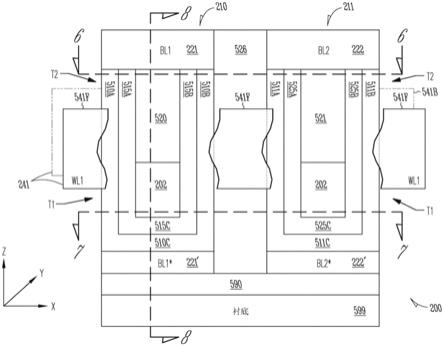

9.图5、图6、图7和图8示出根据本文描述的一些实施例的图2的存储器装置的结构的不同视图。

10.图9a到图9r示出根据本文描述的一些实施例的形成存储器装置的过程。

11.图10a到图10e示出根据本文描述的一些实施例的形成另一存储器装置的过程,图10a到图10e所示的形成存储器装置的过程可以是形成图9a到图9r的存储器装置的过程的变化形式。

12.图11a、图11b和图11c示出根据本文描述的一些实施例的包含存储器单元的多个

叠组的存储器装置结构的不同视图。

具体实施方式

13.本文描述的存储器装置包含易失性存储器单元,其中存储器单元中的每一个可包含两个晶体管(2t)。两个晶体管中的一者具有电荷存储结构,其可形成存储器单元的存储器元件以存储信息。本文描述的存储器装置可具有允许存储器装置的大小相对小于类似常规存储器装置的大小的结构(例如,4f2单元覆盖面积)。所描述的存储器装置可以包含控制存储器单元的两个晶体管的信号存取线。这可以降低功耗并改进处理。下文参考图1到图10e论述所描述存储器装置和其变化形式的其它改进和益处。

14.图1示出根据本文描述的一些实施例的呈包含易失性存储器单元的存储器装置100形式的设备的框图。存储器装置100包含存储器阵列101,其可含有存储器单元102。存储器装置100是易失性存储器装置(例如,dram装置),使得存储器单元102是易失性存储器单元。因此,如果供应功率(例如,供应电压vcc)与存储器装置100断开连接,那么存储于存储器单元102中的信息可能丢失(例如,无效)。在下文中,vcc被称为表示一些电压电平,然而,其不限于存储器装置(例如,存储器装置100)的供应电压(例如,vcc)。例如,如果存储器装置(例如,存储器装置100)具有基于vcc而产生内部电压的内部电压产生器(图1中未示出),那么此类内部电压可代替vcc使用。

15.在存储器装置100的物理结构中,存储器单元102中的每一个可包含在存储器装置100的衬底(例如,半导体衬底)上方在不同层级中竖直地形成(例如,在不同层中堆叠在彼此上方)的晶体管(例如,两个晶体管)。包含存储器单元102的存储器阵列101的结构可包含下文参考图2到图10e描述的存储器阵列和存储器单元的结构。

16.如图1所示,存储器装置100可包含存取线104(例如,“字线”)和数据线(例如,位线)105。存储器装置100可使用存取线104上的信号(例如,字线信号)来存取存储器单元102和数据线105以提供待存储(例如,写入)于存储器单元102中或从所述存储器单元读取(例如,感测)的信息(例如,数据)。

17.存储器装置100可包含地址寄存器106以接收线(例如,地址线)107上的地址信息addr(例如,行地址信号和列地址信号)。存储器装置100可包含可用于解码来自地址寄存器106的地址信息addr的行存取电路系统(例如,x

‑

解码器)108和列存取电路系统(例如,y

‑

解码器)109。基于经解码地址信息,存储器装置100可确定待在存储器操作期间存取哪些存储器单元102。存储器装置100可执行写入操作以将信息存储于存储器单元102中,且执行读取操作以读取(例如,感测)存储器单元102中的信息(例如,先前存储的信息)。存储器装置100也可执行操作(例如,刷新操作)以刷新(例如,保持有效)存储于存储器单元102中的信息的值。存储器单元102中的每一个可被配置成存储可表示至多一个位(例如,具有二进制0(“0”)或二进制1(“1”)的单个位)或超过一个位(例如,具有至少两个二进制位的组合的多个位)的信息。

18.存储器装置100可接收分别在线130和132上的供应电压,包含供应电压vcc和vss。供应电压vss可在地面电位(例如,具有近似地零伏特的值)下操作。供应电压vcc可包含从如电池的外部电源或交流电到直流电(ac

‑

dc)转换器电路供应到存储器装置100的外部电压。

19.如图1所示,存储器装置100可包含存储器控制单元118,其包含电路系统(例如,硬件组件),以基于线(例如,控制线)120上的控制信号而控制存储器装置100的存储器操作(例如,读取和写入操作)。线120上的信号的实例包含行存取选通信号ras*、列存取选通信号cas*、写入启用信号we*、芯片选择信号cs*、时钟信号ck和时钟启用信号cke。这些信号可以是提供到dram装置的信号的一部分。

20.如图1所示,存储器装置100可包含可携载信号dq0到dqn的线(例如,全局数据线)112。在读取操作中,提供到线112(以信号dq0到dqn的形式)的(从存储器单元102读取的)信息的值(例如,“0”或“1”)可基于数据线105上的信号的值。在写入操作中,提供到数据线105(待存储于存储器单元102中)的信息的值(例如,“0”或“1”)可基于线112上的信号dq0到dqn的值。

21.存储器装置100可包含感测电路系统103、选择电路系统115和输入/输出(i/o)电路系统116。列存取电路系统109可基于地址信号addr而选择性地激活线(例如,选择线)上的信号。选择电路系统115可对线114上的信号作出响应以选择数据线105上的信号。数据线105上的信号可表示待存储于存储器单元102(例如,在写入操作期间)中的信息的值或从存储器单元102(例如,在读取操作期间)读取(例如,感测)的信息的值。

22.i/o电路系统116可用于将从存储器单元102读取的信息提供到线112(例如,在读取操作期间)且将来自线112(例如,由外部装置提供)的信息提供到数据线105以存储于存储器单元102中(例如,在写入操作期间)。线112可包含存储器装置100内的节点或存储器装置100可驻留于其中的封装上的引脚(或焊球)。存储器装置100外部的其它装置(例如,硬件存储器控制器或硬件处理器)可经由线107、112和120与存储器装置100通信。

23.存储器装置100可包含其它组件,这些组件在图1中未示出以免混淆本文描述的实例实施例。存储器装置100的至少一部分(例如,存储器阵列101的一部分)可包含与下文参考图10e描述的存储器装置中的任一者类似或一致的结构和操作。

24.图2示出根据本文描述的一些实施例的包含存储器阵列201的存储器装置200的一部分的示意图。存储器装置200可对应于图1的存储器装置100。例如,存储器阵列201可形成图1的存储器阵列101的一部分。如图2所示,存储器装置200可包含存储器单元210到215,其是易失性存储器单元(例如,dram单元)。为简单起见,存储器单元210到215当中的类似或相同元件给定相同标签。

25.存储器单元210到215中的每一个可包含两个晶体管t1和t2。因此,存储器单元210到215中的每一个可被称为2t存储器单元(例如2t增益单元)。晶体管t1和t2中的每一个可包含场效应晶体管(fet)。作为实例,晶体管t1可以是p沟道fet(pfet),且晶体管t2可以是n沟道fet(nfet)。晶体管t1可包含基于电荷存储的结构(例如,基于浮动栅极)。如图2所示,存储器单元210到215中的每一个可包含电荷存储结构202,其可包含晶体管t1的浮动栅极。电荷存储结构202可形成存储器单元210到215当中的相应存储器单元的存储器元件。电荷存储结构202可存储电荷。存储于存储器单元210到215当中的特定存储器单元中的信息的值(例如,“0”或“1”)可基于所述特定存储器单元的电荷存储结构202中的电荷量。

26.如图2所示,存储器单元210到215当中的特定存储器单元的晶体管t2(例如,晶体管t2的沟道区)可电耦合到(例如,直接耦合到)所述特定存储器单元的电荷存储结构202。因此,电路路径(例如,电流路径)可在存储器装置200的操作(例如,写入操作)期间直接形

成于特定存储器单元的晶体管t2与所述特定存储器单元的电荷存储结构202之间。

27.存储器单元210到215可配置于存储器单元群组2010和2011中。图2示出两个存储器单元群组(例如,2010和2011)作为一实例。然而,存储器装置200可包含超过两个存储器单元群组。存储器单元群组2010和2011可包含相同数目的存储器单元。例如,存储器单元群组2010可包含存储器单元210、212和214,且存储器单元群组2011可包含存储器单元211、213和215。图2示出存储器单元群组2010和2011中的每一个中的三个存储器单元作为一实例。存储器单元群组2010和2011中的存储器单元的数目可不同于三个。

28.存储器装置200可执行写入操作以将信息存储在存储器单元210到215中,且执行读取操作以从存储器单元210到215读取(例如,感测)信息。存储器装置200可被配置成用作dram装置。然而,不同于将信息存储在如电容器的容器的结构中的一些常规dram装置,存储器装置200可将信息以电荷的形式存储在电荷存储结构202(其可以是浮动栅极结构)中。如上文所提及,电荷存储结构202可以是晶体管t1的浮动栅极(例如,浮动栅极202)。因此,存储器装置200可被称为基于浮动栅极的dram装置。

29.如图2所示,存储器装置200可包含可携载相应信号(例如,字线信号)wl1、wl2和wln的存取线(例如,字线)241、242和243。存取线241、242和243可用于存取存储器单元群组2010和2011两者。存取线241、242和243中的每一个可构造成至少一个导电线(可彼此电耦合(例如,短接)的一个导电线或多个导电线)。存取线241、242和243可在存储器装置200的操作(例如,读取或写入操作)期间选择性地激活(例如,一次一个地激活)以存取存储器单元210到215当中的一或多个所选存储器单元。所选单元可被称为目标单元。在读取操作中,可从一或多个所选存储器单元读取信息。在写入操作中,信息可以是一或多个所选存储器单元中的所存储信息。

30.在存储器装置200中,单个存取线(例如,单个字线)可用于在存储器装置200的读取或写入操作期间控制(例如,接通或断开)相应存储器单元的晶体管t1和t2。一些常规存储器装置可使用多个(例如,两个分离的)存取线,用于在读取和写入操作期间控制对相应存储器单元的存取。与此类常规存储器装置(对同一存储器单元使用多个存取线)相比,存储器装置200使用存储器装置200中的单个存取线(例如,共用存取线)来控制相应存储器单元的两个晶体管t1和t2以存取相应存储器单元。这种技术可以节省空间并简化存储器装置200的操作。

31.在存储器装置200中,晶体管t1和t2中的每一个的栅极可以是相应存取线(例如,相应字线)的一部分。如图2所示,存储器单元210的晶体管t1和t2中的每一个的栅极可以是存取线241的一部分。存储器单元211的晶体管t1和t2中的每一个的栅极可以是存取线241的一部分。

32.存储器单元212的晶体管t1和t2中的每一个的栅极可以是存取线242的一部分。存储器单元213的晶体管t1和t2中的每一个的栅极可以是存取线242的一部分。

33.存储器单元214的晶体管t1和t2中的每一个的栅极可以是存取线243的一部分。存储器单元215的晶体管t1和t2中的每一个的栅极可以是存取线243的一部分。

34.存储器装置200可以包含数据线(例如,位线)221、221'、222和222',其可携带相应信号(例如,位线信号)bl1、bl1*、bl2和bl2*。在读取操作期间,存储器装置200可以使用数据线221和221'来获得从存储器单元群组2010的所选存储器单元读取(例如,感测)的信息,

并且使用数据线222和222'来从存储器单元群组2011的所选存储器单元读取信息。在写入操作期间,存储器装置200可以使用数据线221来提供待存储于存储器单元群组2010的所选存储器单元中的信息,并且使用数据线222来提供待存储于存储器单元群组2011的所选存储器单元中的信息。

35.存储器装置200可包含读取路径(例如,电路路径)。在读取操作期间从所选存储器单元读取的信息可经由耦合到所选存储器单元的读取路径获得。在存储器单元群组2010中,特定存储器单元(例如,210、212或214)的读取路径可包含通过所述特定存储器单元的晶体管t1的沟道区和数据线221和221'的电流路径(例如,读取电流路径)。在存储器单元群组2011中,特定存储器单元(例如,211、213或215)的读取路径可包含通过所述特定存储器单元的晶体管t1的沟道区和数据线222和222'的电流路径(例如,读取电流路径)。在其中晶体管t1是pfet的实例中,电流可以包含空穴导电(例如,在通过晶体管t1的沟道区(例如,n型半导体区)从数据线221到数据线221*的方向上的空穴导电)。由于晶体管t1可用于读取路径以在读取操作期间从相应存储器单元读取信息,所以晶体管t1可被称为读取晶体管且晶体管t1的沟道区可被称为读取沟道区。

36.存储器装置200可包含写入路径(例如,电路路径)。待在写入操作期间存储于所选存储器单元中的信息可经由耦合到所选存储器单元的写入路径提供到所选存储器单元。在存储器单元群组2010中,特定存储器单元的写入路径可包含所述特定存储器单元的晶体管t2(例如,可以包含通过晶体管t2的沟道区的写入电流路径)和数据线221。在存储器单元群组2011中,特定存储器单元(例如,211、213或215)的写入路径可包含所述特定存储器单元的晶体管t2(例如,可以包含通过晶体管t2的沟道区的写入电流路径)和数据线222。在其中晶体管t2是nfet的实例中,电流可以包含电子导电(例如,在通过晶体管t2的沟道区(例如,n型半导体区)从数据线221到电荷存储结构202的方向上的电子导电)。由于晶体管t2可用于写入路径以在写入操作期间将信息存储在相应存储器单元中,所以晶体管t2可被称为写入晶体管且晶体管t1的沟道区可被称为写入沟道区。

37.晶体管t1和t2中的每一个可具有阈值电压(vt)。晶体管t1具有阈值电压vt1。晶体管t2具有阈值电压vt2。阈值电压vt1和vt2的值可不同(不相等值)。例如,阈值电压vt2的值可大于阈值电压vt1的值。阈值电压vt1和vt2的值的差允许存储于读取路径上的晶体管t1中的电荷存储结构202中的信息的读取(例如,感测)而不影响(例如,而不接通)写入路径上的晶体管t2(例如,通过晶体管t2的路径)。这可经由写入路径的晶体管t2防止电荷从电荷存储结构202泄漏。

38.在存储器装置200的结构中,晶体管t1和t2可形成(例如,工程改造)为使得晶体管t1的阈值电压vt1可小于零伏(例如,vt1<0v)而不管晶体管t1的电荷存储结构202中存储的信息的值(例如,“0”或“1”),且vt1<vt2。当具有值“0”的信息存储于电荷存储结构202中时,电荷存储结构202可处于状态“0”。当具有值“1”的信息存储于电荷存储结构202中时,电荷存储结构202可处于状态“1”。因此,在此结构中,阈值电压vt1与vt2的值之间的关系可表示如下,针对状态“0”的vt1<针对状态“1”的vt1<0v,且vt2=0v(或替代地vt2>0v)。

39.在存储器装置200的替代结构中,晶体管t1和t2可形成(例如,工程改造)为使得针对状态“0”的vt1<针对状态“1”的vt1,其中针对状态“0”的vt1<0v(或替代地针对状态“0”的vt1=0v),针对状态“1”的vt1>0v,且vt1<vt2。

40.在另一替代结构中,晶体管t1和t2可形成(例如,工程改造)为使得vt1(针对状态“0”)<vt1(针对状态“1”),其中针对状态“0”的vt1=0v(或替代地针对状态“0”的vt1>0v,且vt1<vt2。

41.在存储器装置200的读取操作期间,可一次一个地选择相同存储器单元群组的仅一个存储器单元以从所选存储器单元读取信息。例如,可在读取操作期间一次一个地选择存储器单元群组2010的存储器单元210、212和214以从所选存储器单元(例如,这一实例中的存储器单元210、212和214中的一个)读取信息。在另一实例中,可在读取操作期间一次一个地选择存储器单元群组2011的存储器单元211、213和215以从所选存储器单元(例如,这一实例中的存储器单元211、213和215中的一个)读取信息。

42.在读取操作期间,可并行地选择(或替代地可依序选择)共用相同存取线(例如,存取线241、242或243)的不同存储器单元群组(例如,存储器单元群组2010和2011)的存储器单元。例如,可在读取操作期间并行地选择存储器单元210和211以从存储器单元210和211读取(例如,并行地读取)信息。可在读取操作期间并行地选择存储器单元212和213以从存储器单元212和213读取(例如,并行地读取)信息。可在读取操作期间并行地选择存储器单元214和215以从存储器单元214和215读取(例如,并行地读取)信息。

43.在读取操作期间从存储器单元群组2010的所选存储器单元读取的信息的值可基于从包含所选存储器单元(例如,存储器单元210、212或214)的晶体管t1和数据线221和221'的读取路径(上文所描述)检测(例如感测)的电流的值而确定。在读取操作期间从存储器单元群组2011的所选存储器单元读取的信息的值可基于从包含所选存储器单元(例如,存储器单元211、213或215)的晶体管t1和数据线222和222'的读取路径检测(例如感测)的电流的值而确定。

44.存储器装置200可包含检测电路系统(未示出),所述检测电路系统可在读取操作期间操作以检测(例如,感测)包含数据线221和221'的读取路径上的电流(例如,电流i1,未示出),且检测包含数据线222和222'的读取路径上的电流(例如,电流i2,未示出)。检测到的电流的值可基于存储于所选存储器单元中的信息的值。例如,取决于存储于存储器单元群组2010的所选存储器单元中的信息的值,数据线221与221'之间的检测到的电流的值(例如,电流i1的值)可以是零或大于零。类似地,取决于存储于存储器单元群组2011的所选存储器单元中的信息的值,数据线222与222'之间的检测到的电流的值(例如,电流i2的值)可以是零或大于零。存储器装置200可包含将检测到的电流的值转换成存储于所选存储器单元中的信息的值(例如,“0”、“1”或多位值的组合)的电路系统(未示出)。

45.在存储器装置200的写入操作期间,可一次一个地选择相同存储器单元群组的仅一个存储器单元以将信息存储在所选存储器单元中。例如,可在写入操作期间一次一个地选择存储器单元群组2010的存储器单元210、212和214以将信息存储在所选存储器单元(例如,这一实例中的存储器单元210、212和214中的一个)中。在另一实例中,可在写入操作期间一次一个地选择存储器单元群组2011的存储器单元211、213和215以将信息存储在所选存储器单元(例如,这一实例中的存储器单元211、213和215中的一个)中。

46.在写入操作期间,可以并行地选择共用同一存取线(例如,存取线241、242或243)的不同存储器单元群组(例如,存储器单元群组2010和2011)的存储器单元。例如,可在写入操作期间并行地选择存储器单元210和211以将信息存储(例如,并行地存储)于存储器单元

210和211中。可在写入操作期间并行地选择存储器单元212和213以将信息存储(例如,并行地存储)在存储器单元212和213中。可在写入操作期间并行地选择存储器单元214和215以将信息存储(例如,并行地存储)在存储器单元214和215中。

47.待在写入操作期间存储于存储器单元群组2010的所选存储器单元中的信息可经由包含数据线221和所选存储器单元(例如,存储器单元210、212或214)的晶体管t2的写入路径提供。待在写入操作期间存储于存储器单元群组2011的所选存储器单元中的信息可经由包含数据线222和所选存储器单元(例如,存储器单元212、213或215)的晶体管t2的写入路径提供。如上文所描述,存储于存储器单元210到215当中的特定存储器单元中的信息的值(例如,二进制值)可基于那一特定存储器单元的电荷存储结构202中的电荷量。

48.在写入操作中,可通过在包含特定存储器单元的晶体管t2和耦合到所述特定存储器单元的数据线(例如,数据线221w或222w)的写入路径上施加电压而改变所述所选存储器单元的电荷存储结构202中的电荷量(以反映存储于所选存储器单元中的信息的值)。例如,如果待存储于存储器单元210、212和214当中的所选存储器单元中的信息具有一个值(例如,“0”),则可在数据线221w上施加具有一个值(例如,0v)的电压(例如,将0v提供到信号bl1)。在另一实例中,如果待存储于存储器单元210、212和214当中的所选存储器单元中的信息具有另一值(例如,“1”),则可在数据线221上施加具有另一值(例如,正电压)的电压(例如,将正电压提供到信号bl1)。因此,可通过提供待在特定存储器单元的写入路径(其包含晶体管t2)上(例如,以电压形式)存储的信息而将所述信息存储(例如,直接存储)在所述特定存储器单元的电荷存储结构202中。

49.图3示出根据本文描述的一些实施例的包含在存储器装置200的读取操作期间使用的实例电压v0、v1、v2和v3的图2的存储器装置200。图3的实例假定存储器单元210是读取操作期间用于读取(例如,感测)存储(例如,先前存储)于存储器单元210中的信息的所选存储器单元(例如,目标存储器单元)。假定存储器单元211到215是未选存储器单元。这意味着在从图3的实例中的存储器单元210读取信息时,不存取存储器单元211到215且不读取存储于存储器单元211到215中的信息。

50.在图3中,电压v0、v1、v2和v3可表示在存储器装置200的读取操作期间施加到相应存取线241、242和243以及数据线221、221'、222和222'的不同电压。作为实例,电压v0、v1、v2和v3可分别具有0v(例如,接地)、

‑

0.3v、

‑

0.75v和0.5v的值。在本说明书中使用的电压的特定值仅是实例值。可使用不同值。

51.在图3所示的读取操作中,电压v1可具有值(电压值)以接通存储器单元210(这一实例中的所选存储器单元)的晶体管t1和断开(或保持断开)存储器单元210的晶体管t2。这允许从存储器单元210读取信息。电压v0和v2可具有值,使得存储器单元211到215(这一实例中的未选存储器单元)中的每一个的晶体管t1和t2断开(例如,保持断开)。电压v3可具有值,使得可在包含数据线221和221'以及存储器单元210的晶体管t1的读取路径上形成电流(例如,读取电流)。这允许在耦合到存储器单元210的读取路径上检测电流。存储器装置200的检测电路系统(未示出)可用于将检测到的电流(在从所选存储器单元读取信息期间)的值转换成从所选存储器单元读取的信息的值(例如,“0”、“1”或多位值的组合)。在图3的实例中,数据线221和221'上的检测到的电流的值可转换成从存储器单元210读取的信息的值。

52.在图3所示的读取操作中,施加到相应存取线241、242和243的电压可使除存储器单元210的晶体管t1外的存储器单元211到215中的每一个的晶体管t1和t2断开(或保持断开)。取决于存储器单元210的晶体管t1的阈值电压vt1的值,存储器单元210的晶体管t1可或可不接通。例如,如果存储器装置200的存储器单元(例如,210到215)中的每一个的晶体管t1被配置成(例如,构造成)使得晶体管t1的阈值电压小于零(例如,vt1<0v)而不管存储于相应存储器单元210中的信息的值(例如,状态),那么这一实例中的存储器单元210的晶体管t1可接通且传导数据线221与221'之间的电流(经由存储器单元210的晶体管t1)。存储器装置200可基于数据线221与221'之间的电流的值而确定存储于存储器单元210中的信息的值。如上文描述,存储器装置200可包含在读取操作期间测量数据线221与221'之间(或数据线222与222之间)的电流的值的检测电路。

53.图4示出根据本文描述的一些实施例的包含在存储器装置200的写入操作期间使用的实例电压v0、v4、v5、v6和v7的图2的存储器装置200。图4的实例假定存储器单元210和211是写入操作期间用于将信息存储于存储器单元210和211中的所选存储器单元(例如,目标存储器单元)。假定存储器单元212到215是未选存储器单元。这意味着在信息存储于图4的实例中的存储器单元210和211中时,不存取存储器单元212到215且所存储信息不存储于存储器单元212到215中。

54.在图4中,电压v0、v4、v5、v6和v7可表示在存储器装置200的写入操作期间施加到相应存取线241、242和243以及数据线221、221'、222和222'的不同电压。作为实例,电压v0、v4和v5可分别具有0v、3.3v和

‑

0.75v的值。这些值是实例值。可使用不同值。

55.取决于存储于存储器单元210和211中的信息的值(例如,“0”或“1”),电压v6和v7的值可相同或不同。例如,如果存储器单元210和211将存储具有相同值的信息,则电压v6和v7的值可相同(例如,v6=v7)。作为实例,如果待存储于每个存储器单元210和211中的信息是“0”,则v6=v7=0v,如果待存储于每个存储器单元210和211中的信息是“1”,则v6=v7=1v到3v。

56.在另一实例中,如果存储器单元210和211将存储具有不同值的信息,则电压v6和v7的值可不同(例如,v6≠v7)。作为实例,如果“0”将存储于存储器单元210中且“1”将存储于存储器单元211中,则v6=0v且v7=1v到3v。作为另一实例,如果“1”将存储于存储器单元210中且“0”将存储于存储器单元211中,则v6=1v到3v且v7=0v。

57.1v到3v的电压的范围在此处作为实例使用。可使用电压的不同范围。此外,代替向特定写入数据线(例如,数据线221w或222w)施加0v(例如,v6=0v或v7=0v)以用于将具有值“0”的信息存储到耦合到所述特定写入数据线的存储器单元(例如,存储器单元210或211),可以向所述特定数据线施加正电压(例如,v6>0v或v7>0v)。

58.在图4的存储器装置200的写入操作中,电压v5可具有值,使得存储器单元212到215(这一实例中的未选存储器单元)中的每一个的晶体管t1和t2断开(例如,保持断开)。电压v4可具有值以接通存储器单元210和211(这一实例中的所选存储器单元)中的每一个的晶体管t2且形成存储器单元210的电荷存储结构202与数据线221之间的写入路径,和存储器单元211的电荷存储结构202与数据线222之间的写入路径。电流(例如,写入电流)可形成于存储器单元210的电荷存储结构202与数据线221之间。这一电流可影响(例如,改变)存储器单元210的电荷存储结构202上的电荷量以反映待存储于存储器单元210中的信息的值。

电流(例如,另一写入电流)可形成于存储器单元211的电荷存储结构202与数据线222之间。这一电流可影响(例如,改变)存储器单元211的电荷存储结构202上的电荷量以反映待存储于存储器单元211中的信息的值。

59.在图4的实例写入操作中,电压v6的值可使得存储器单元210的电荷存储结构202放电或充电,使得存储器单元210的电荷存储结构202上的所得电荷(例如,在放电或充电动作之后剩余的电荷)可反映存储于存储器单元210中的信息的值。类似地,这一实例中的电压v7的值可使得存储器单元211的电荷存储结构202放电或充电,使得存储器单元211的电荷存储结构202上的所得电荷(例如,在放电或充电动作之后剩余的电荷)可反映存储于存储器单元211中的信息的值。

60.根据本文描述的一些实施例,图5、图6、图7和图8示出关于x、y和z方向的图2的存储器装置200的结构的不同视图。图5示出关于x

‑

z方向的存储器装置200的侧视图。图6、图7和图8示出分别沿图5的线6

‑

6、7

‑

7和8

‑

8截取的视图。

61.为简单起见,图5到图8着重于存储器单元210和211的结构。图2的存储器装置200的其它存储器单元(例如,存储器单元212、213、214和215的结构可与图5中示出的存储器单元210和211的结构类似或相同。在图5到图8(其示出存储器装置200的物理结构)和图2(其以电路示意图形式示出存储器装置200)中,相同的元件被赋予相同的参考标号。

62.以下描述参考图5到图8。为简单起见,在图5到图8的描述中不重复对同一元件的详细描述。同样为简单起见,省略图5到图8以及本文描述的附图中的其它图(例如,图9a到图10e)中所示的大多数元件的横截面线(例如,剖面线)。可以从附图中的特定图省略存储器装置200的一些元件,以便不模糊在所述特定图中描述的元件的描述。图5到图10e中所示的元件的尺寸没有缩放。

63.如图5所示,存储器装置200可包含衬底599,在所述衬底上方可形成存储器单元210和211(例如,相对于衬底599竖直地形成)。衬底599可以是半导体衬底(例如,基于硅的衬底)或其它类型的衬底。z方向可以是垂直于衬底599的方向(例如,相对于衬底599的竖直方向)。x方向和y方向彼此垂直且垂直于z方向。

64.如图5到图8所示,数据线221、221'、222和222'(分别与信号bl1、bl1*、bl2和bl2*相关联)中的每一个可以具有y方向上的长度、x方向上的宽度和z方向上的厚度。数据线221、221'、222和222'中的每一个数据线可以包含可被构造成导电线(例如,导电区)的导电材料(或材料组合)。数据线221、221'、222和222'的实例材料包含金属、导电掺杂多晶硅或其它导电材料。

65.如图5所示,数据线221和221'可以包含位于存储器装置200的不同层级(相对于z方向)并且彼此电分离的相应导电区(形成数据线221和221'的相应导电材料的一部分)。类似地,数据线222和222'可以包含位于存储器装置200的不同层级并且彼此电分离的相应导电区(形成数据线222和222'的相应导电材料的一部分)。

66.数据线221和221'可以分别是底部和顶部数据线(相对于衬底599和z方向)。存储器单元210可以位于存储器单元211之间并且耦合到存储器单元211。数据线222和222'可以分别是底部和顶部数据线(相对于衬底599和z方向)。存储器单元211可以位于存储器单元210之间并耦合到存储器单元210。

67.存取线241(与信号wl1相关联)可以由部分541f和541b(例如,关于y方向的前导电

部分和后导电部分)的组合构造(可以包含所述部分)。部分541f和541b中的每一个可以包含导电材料(或材料组合),其可被构造成具有在x方向上连续延伸的长度的导电线(例如,导电区)。在图5中,部分地示出部分541a、541b、541c和541d以避免阻挡存储器装置200的其它元件的一些部分。

68.部分541f和541b中的每一个可以包含导电材料(例如,金属、导电掺杂多晶硅或其它导电材料)块(例如,层)。部分541f和541b中的每一个可以具有x方向上的长度(如图5所示)、z方向上的宽度(如图5所示)和y方向上的厚度(如图8所示)。

69.部分541f和541b可以彼此电耦合。例如,存储器装置200可以包含导电材料(例如,未示出),所述导电材料可以接触(例如,电耦合到)部分541f和541b,使得部分541f和541b(其作为单个存取线241的一部分)可以由相同的信号(例如,信号wl1)并行地施加。

70.在存储器装置200的替代结构中,可以省略部分541f或部分541b,使得存取线241可以仅包含部分541f或部分541b。在图5所示的结构中,包含两个部分541f和541b可以帮助在读取操作期间更好地控制存储器单元210和211中的每一个的晶体管t1(例如,图2中示意性地示出的晶体管t1)。

71.如图5所示,存储器装置200可以包含形成于衬底599的一部分上的电介质590。电介质590可以包含氧化硅。电介质590可以将数据线221'和222'与衬底599电分离。

72.电荷存储结构202可以包含半导体材料(例如,多晶硅)块(例如,层)、金属块(例如,层)或可捕获电荷的材料(或多种材料)块。用于电荷存储结构202和存取线241的部分541f和541b的材料可以相同也可以不同。如图5所示,电荷存储结构202可以位于数据线221'上方,并且可以比存取线241的部分541f和541b中的每一个更靠近(例如,在z方向上延伸更靠近)衬底599。

73.图5示出电荷存储结构202的顶边缘与存取线241的部分541f和541b中的每一个的边缘(例如,底边缘)相距特定距离(例如,图5所示的距离)的实例。然而,电荷存储结构202的顶边缘与部分541f和541b中的每一个的边缘(例如,底边缘)之间的距离可以变化。

74.图5示出部分541f和541b与(在z方向上)电荷存储结构202重叠的实例。然而,部分541f和541b可以不与电荷存储结构202重叠。

75.存储器装置200可以包含位于数据线221与电荷存储结构202之间的材料520。如图5所示,材料520可以电耦合到数据线221和存储器单元210的电荷存储结构202。如上所述,存储器单元210的电荷存储结构202可以形成存储器单元210的存储器元件。因此,存储器单元210可以包含相对于z方向位于衬底599与材料520之间的存储器元件(其是电荷存储结构202),并且所述存储器元件接触(例如,直接耦合到)材料520。

76.材料520可以形成存储器单元210的晶体管t2的源极(例如,源极端子)、漏极(例如,漏极端子)、源极与漏极之间的沟道区(例如,写入沟道区)。因此,如图5所示,存储器单元210的晶体管t2的源极、沟道区和漏极可以由例如材料520的单个相同材料块(或替代地,单个相同材料组合块)形成。因此,存储器单元210的晶体管t2的源极、漏极和沟道区可以由相同导电类型(例如,n型或p型)的相同材料(例如,材料520)形成。

77.存储器装置200可以包含材料521,所述材料可以形成存储器单元211的晶体管t2的源极(例如,源极端子)、漏极(例如,漏极端子)、以及源极与漏极之间的沟道区(例如,写入沟道区)。因此,如图5所示,存储器单元211的晶体管t2的源极、沟道区和漏极可以由例如

材料521的单个相同材料块(或替代地,单个相同材料组合块)形成。

78.材料520和521可以相同。例如,材料520和521中的每一个可以包含半导体材料块(例如,层)。在晶体管是pfet(如上所述)的实例中,材料520和521可以包含p型半导体材料(例如,p型硅)。

79.在另一实例中,形成材料520或材料521的半导体材料可以包含氧化物材料块。用于材料520和521的氧化物材料的实例包含半导体氧化物材料、透明导电氧化物材料和其它氧化物材料。

80.作为实例,材料520和521中的每一个可以包含以下中的至少一者:氧化锌锡(zto)、氧化铟锌(izo)、氧化锌(zno

x

)、氧化铟镓锌(igzo)、氧化铟镓硅(igso)、氧化铟(ino

x

,in2o3)、氧化锡(sno2)、氧化钛(tiox)、氮氧化锌(zn

x

o

y

n

z

)、氧化镁锌(mg

x

zn

y

o

z

)、氧化铟锌(in

x

zn

y

o

z

)、氧化铟镓锌(in

x

ga

y

zn

z

o

a

)、氧化锆铟锌(zr

x

in

y

zn

z

o

a

)、氧化铪铟锌(hf

x

in

y

zn

z

o

a

)、氧化锡铟锌(sn

x

in

y

zn

z

o

a

)、氧化铝锡铟锌(al

x

sn

y

in

z

zn

a

o

d

)、氧化硅铟锌(si

x

in

y

zn

z

o

a

)、氧化锌锡(zn

x

sn

y

o

z

)、氧化铝锌锡(al

x

zn

y

sn

z

o

a

)、氧化镓锌锡(ga

x

zn

y

sn

z

o

a

)、氧化锆锌锡(zr

x

zn

y

sn

z

o

a

)、氧化铟镓硅(ingasio)和磷化镓(gap)。

81.在存储器装置200中使用上述材料为存储器装置200提供改进和益处。例如,在从所选存储器单元(例如,存储器单元210或211)读取信息的读取操作期间,来自所选存储器单元的电荷存储结构202的电荷可能泄漏到所选存储器单元的晶体管t2。使用以上列出的材料用于晶体管t2的沟道区(例如,材料520或521)可减少或防止此类泄漏。这改进从所选存储器单元读取的信息的准确性且改进存储于本文描述的存储器装置(例如,存储器装置200)的存储器单元中的信息的保留。

82.以上列出的材料是材料520和521的实例。然而,可使用不同于以上列出的材料的其它材料(例如,相对高带隙材料)。

83.在图5中,材料520和存储器单元210的电荷存储结构202可以彼此电耦合(例如,直接耦合),使得材料520可以在存储器单元210的电荷存储结构202与材料520之间没有中间材料(例如,没有导电材料)的情况下接触存储器单元210的电荷存储结构202。在另一实例中,材料520可以电耦合到存储器单元210的电荷存储结构202,使得材料520不直接耦合到(不接触)存储器单元210的电荷存储结构202,但是,材料520通过存储器单元210的电荷存储结构202与材料520之间的中间材料(例如,导电材料,图5中未示出)耦合到(例如,间接接触)存储器单元210的电荷存储结构202。

84.如图5所示,存储器单元210可以包含彼此电耦合的部分510a、510b和510c。部分510a、510b和510c中的每一个可以包含半导体材料块。部分510a、510b和510c中的每一个的实例材料包含硅、多晶硅(例如,未掺杂或掺杂多晶硅)、锗、硅锗或其它半导体材料。

85.部分511a和510b中的每一个可以具有在z方向上延伸的长度。部分510c可以具有在x方向上的长度。如图5所示,部分510a、510b和510c可以形成“u”形(或接近“u”形)。

86.如上参考图2所述,存储器单元210的晶体管t1包含沟道区(例如,读取沟道区)。在图5中,存储器单元210的晶体管t1的沟道区可以包含部分510a、510b和510c(例如,可以由其组合形成)。部分510a、510b和510c可以电耦合到数据线221和222。如上参考图2所述,存储器单元210可以包含读取路径。在图5中,部分510a、510b和510c(例如,存储器单元210的晶体管t1的读取沟道区)可以是存储器单元210的读取路径的一部分,其可以在从存储器单

元210读取信息的读取操作期间携载电流(例如,读取电流)。例如,在读取操作期间,为了从存储器单元210读取信息,部分510a、510b和510c可以在数据线221与221'之间传导电流(例如,读取电流)。读取电流的方向可以是从数据线221到数据线221'(通过部分510a、510b和510)。在晶体管t1是pfet且晶体管t2是nfet的实例中,形成部分510a、510b和510c的材料可以具有与材料520或521不同的导电类型。例如,部分510a、510b和510c可以包含p型半导体材料(例如,p型硅),并且材料520和521可以包含n型半导体材料(例如,n型磷化镓(gap))。

87.存储器单元210可以包含电介质515a、515b和515c。电介质515a、515b和515c可以是栅极氧化物区,其将电荷存储结构202与部分510a、510b和510c电分离,且将材料520与部分510a、510b和510c电分离。电介质515a、515b和515c的实例材料可以包含二氧化硅、氧化铪(例如hfo2)、氧化铝(例如al2o3)或其它电介质材料。

88.如图5所示,部分541f的一部分可以跨越(例如,在x方向上重叠)部分510a和510b的一部分以及材料520的一部分。如上所述,部分510a和510b可以形成晶体管t1的读取沟道区的一部分,并且材料520可以形成晶体管t2的写入沟道区的一部分。因此,如图5所示,部分541f的一部分可以分别跨越(例如,重叠)晶体管t1和t2的读取和写入沟道的一部分(例如,在y方向上的一侧(例如,前侧))。尽管从图5所示的视图中隐藏,但部分541b的一部分可以跨越(例如,在x方向上重叠)部分510a和510b的一部分(例如,在y方向上的另一侧(例如,与前侧相对的后侧))以及材料521的一部分。如图5所示,存取线241也可以跨越(例如,在x方向上重叠)部分511a和511b的一部分(例如,存储器单元211的晶体管t1的读取沟道区的部分)和材料521的一部分(例如,存储器单元211的晶体管t2的写入沟道区的部分)。

89.存取线241跨越(例如,重叠)部分510a和510b以及材料520允许存取线241(单个存取线)控制(例如,接通或断开)存储器单元210的晶体管t1和t2以及存储器单元211的两个晶体管。类似地,存取线241跨越(例如,重叠)部分511a和511b以及材料521允许存取线241(单个存取线)控制(例如,接通或断开)存储器单元211的两个晶体管t1和t2。

90.如图6到图8所示,存储器装置200可以包含电介质515e和515f(例如,氧化物区),以将存取线241的部分541f和541b与存储器单元210和211的其它元件(例如,与部分510a、510b、510c、510d和510e(例如,读取沟道区)以及与电荷存储结构202)电分离。部分515e和515f的实例材料可以包含二氧化硅、氧化铪(例如hfo2)、氧化铝(例如al2o3)或其它电介质材料。

91.将部分510a、510b、510c、511a、511b和511c(读取沟道区)与存取线214的部分541f和541b分离的电介质材料(或多种电介质材料)可以与将电荷存储结构202与部分541f和541b分离的材料(或多种材料)相同(或替代地,不同)。此外,将部分510a、510b、510c、511a、511b和511c(读取沟道区)与存取线214的部分541f和541b分离的电介质材料(或多种电介质材料)的厚度可以与将电荷存储结构202与存取线214的部分541f和541b分离的材料(或多种材料)的厚度相同(或替代地,不同)。

92.如图8所示,部分541f和541b可以与材料520和存储器单元210的电荷存储结构202的相应侧相邻。例如,部分541f可以与材料520和电荷存储结构202中的每一个的部分的一侧(例如,图8的视图中在x方向上的右侧)相邻。在另一实例中,部分541b可以与材料520和电荷存储结构202中的每一个的部分的另一侧(例如,图8的视图中在x方向上的左侧(与右侧相反))相邻。

93.以上描述集中于存储器单元210的结构。存储器单元211可以包含以与上述存储器单元210的元件类似或相同的方式构造的元件。例如,如图5到图7所示,存储器单元211可以包含电荷存储结构202、沟道区(例如,写入沟道区)521、部分511a、511b和511c(例如,读取沟道区)以及电介质525a、525b和525c。用于电介质525a、525b和525c的材料(或多种材料)可以分别与用于电介质515a、515b和515c的材料(或多种材料)相同。

94.图9a到图9r示出根据本发明的一些实施例在形成存储器装置900的过程中的元件的横截面图。用于形成存储器装置900过程中的一些或全部可用于形成上文参考图2到图8描述的存储器装置200。

95.图9a示出在衬底999上方在z方向上以相应层级(例如,层)形成电介质材料990、导电材料927和材料930之后的存储器装置900。z方向(例如,竖直方向)是垂直于衬底999(例如,从所述衬底向外)的方向。z方向也垂直于x方向。电介质材料990、导电材料927和材料930可在衬底999上方一种材料接着另一种材料地按顺序方式形成。例如,图9a中使用的过程可以包含在衬底上方形成(例如,沉积)电介质材料990,在电介质材料990上方形成(例如,沉积)导电材料927,并且在导电材料927上方形成(例如沉积)材料930。

96.衬底999可与图5的衬底599相似或相同。图9a的电介质材料922可以包含氧化物材料(例如,二氧化硅sio2)。导电材料927可包含金属、导电掺杂多晶硅或其它导电材料。如下文在形成存储器装置900的后续过程中所述,导电材料927可被构造成形成存储器装置900的数据线,其可类似于存储器装置200的数据线221'和222'(图5)。材料930可以是“牺牲”材料,其可以在形成存储器装置900期间的某些点(在后续过程中)被去除。材料930可以包含氮化物材料(例如,亚硝酸硅sin4)或相对容易去除(例如,蚀刻掉)的其它材料。

97.图9b示出在形成开口(例如,沟槽)931、932和933以及数据线921'、922'、和923'之后的存储器装置900。图9b还示出信号(例如,位线信号)bl1*、bl2*和bl3*,其可以分别表示在存储器装置900的操作(例如,读取或写入)期间施加到数据线921'、922'和923'的信号。信号bl1*和bl2*可以类似于图5中的存储器装置500的信号bl1*和bl2*。

98.在图9b中,形成开口931、932和933可以包含去除(例如,通过图案化)开口931、932和933位置处的材料930的一部分,并留下部分930a、930b和930c(它们是材料930的剩余部分),如图9b所示。形成数据线921'、922'和923'可以包含去除导电材料923(在开口931、932和933位置处)的一部分,留下形成相应数据线921'、922'和923'的导电材料923的剩余部分。如图9b所示,数据线921'、922'和923'彼此电分离(在x方向上)。数据线921'和922'可以类似于图5所示的存储器装置200的数据线221'和222'(例如,底部数据线)。数据线923'可以是存储器装置900的另一数据线。

99.图9c示出在开口931、932和933中分别形成(例如填充)电介质材料951、952和953之后的存储器装置900。图9c中的过程可以包含在形成电介质材料951、952和953之后的平坦化过程(例如,化学机械抛光(cmp)过程)。此类平坦化过程可以使图9c所示的存储器装置900的结构的顶表面平滑(例如,平面化)。

100.图9d示出去除部分930a、930b和930c(图9c)之后的存储器装置900。图9d中的过程可以包含从图9d的存储器装置900的结构中去除部分930a、930b和930c的蚀刻过程。

101.图9e示出在数据线921'、922'和923'上方以及在电介质材料951、952和953上方形成(例如沉积)材料913(例如晶体管沟道材料)之后的存储器装置900。材料913可以在存储

器装置900的操作(例如,读取操作)期间传导电流。材料913的实例包含半导体材料。材料913可以与形成图5的存储器装置500的相应晶体管t1的部分510a、510b和510c(例如,读取沟道区)的材料具有相同属性。如下文在形成存储器装置900的后续过程(例如,图9l)中所述,材料913可以被构造成形成存储器装置900的相应存储器单元的晶体管(例如,晶体管t1)的沟道区(例如读取沟道区)。

102.图9f示出在材料913上方形成(例如沉积)电介质材料(例如栅极氧化物材料)942之后的存储器装置900。电介质材料942可以包含二氧化硅。如下文在形成存储器装置900的后续过程(例如,图9h)中所述,图9f的材料942可以被构造成形成存储器装置900的相应存储器单元的晶体管(例如,晶体管t1和t2)的栅极氧化物的一部分。

103.图9g示出在电介质材料942的部分之间的开放空间中形成(例如,填充)材料(例如,电荷存储材料)902a之后的存储器装置900。如下文在形成存储器装置900的后续过程(图9l)中所述,材料902a可以被构造成形成存储器装置900的相应存储器单元的电荷存储结构。材料902a可以包含与存储器装置500(图5)的存储器单元(例如,存储器单元210或211)的电荷存储结构202的材料相似或相同的材料(例如,多晶硅)。

104.图9h示出在去除图9g中的材料913、942、902a、952和953中的每一个的一部分之后的存储器装置900。图9h中的过程可以包含可去除材料913的一部分以形成部分(材料913的剩余部分)910a、910b和910c"、911a、911b、910c"和919a的过程(例如,cmp过程)。部分910a、910b和910c"的组合可以在后续过程中形成存储器单元910的晶体管(例如晶体管t1)的沟道区。部分911a、911b和910c"的组合可以形成存储器单元911的晶体管(例如晶体管t1)的沟道区。部分919a可以形成存储器单元911旁边的存储器单元的晶体管的沟道区的一部分。

105.图9h中的过程(例如,cmp过程)也可以去除材料942的一部分以形成部分(材料942的剩余部分)915a、915b、915c”、925a、925b、925c”和929a。部分915a、915b和915c”的组合可以在后续过程中形成存储器单元910的晶体管(例如,晶体管t1和t2)的栅极氧化物区的一部分。部分925a、925b和925c"的组合可以在后续过程中形成存储器单元911的晶体管(例如,晶体管t1和t2)的栅极氧化物区的一部分。部分929a可以形成存储器单元911旁边的存储器单元的晶体管的栅极氧化物区的一部分。

106.图9h中的过程还可以包含可以去除材料902a(图g)的一部分以形成凹槽(例如,开口)903和暴露在相应凹槽903处的部分(例如,沟道区)902b的过程(例如,在cmp过程之后执行的蚀刻过程)。部分902b是材料902a的剩余部分。

107.图9i示出在相应凹槽903中形成(例如沉积)材料920a、921a和922a之后的存储器装置900。材料920a、921a和922a可以包含与图5的存储器装置500的晶体管t2的部分(例如,写入沟道区)520或521(图5)的材料相似或相同的材料。如下文在形成存储器装置900的后续过程(图9l)中所述,材料920a可以形成存储器装置900的相应存储器单元的晶体管(例如晶体管t2)的沟道区(例如,写入沟道区)。

108.如图9i所示,存储器装置900的元件的一部分可以形成存储器单元910和911的一部分,所述存储器单元可以分别类似于存储器装置500的存储器单元210和211(图5)。

109.图9j示出关于图9i的存储器装置900的x

‑

y方向的顶视图。为简单起见,不重复图9j所示的元件的描述(参考图9i描述)。如图9j所示,存储器装置900的元件可以包含具有在y方向上延伸的长度的材料条。在形成存储器装置900的后续过程中,存储器装置900的位置

961、962和963处的材料将被去除(例如,在z方向上切割(例如,蚀刻以形成沟槽)),并且位置971和972处的存储器装置900的材料将保留(并且将是存储器装置900的相应存储器单元的各部分)。图9k中示出存储器装置900沿着线9k

‑

9k的另一视图。

110.图9k示出图9j的存储器装置900关于y

‑

z方向沿着图9j的线9k

‑

9k的侧视图。在图9k中,还示出存储器装置900相对于y

‑

z方向的位置961、962、963、971和972。位置961、962和963处的存储器装置900的结构(例如,材料920a、902b、915c”和910c”)将被去除(图9l)并且在数据线921'处停止,使得位置961、962和963处的数据线921'的材料不被去除。

111.图9l示出在形成开口(例如沟槽)961a、962a和963a以及部分920、920'、902'、915c、915c'、910c和910c'之后的存储器装置900。可通过去除位置961、962和963处的材料920a、902b、915c”和910c”中的每种材料的一部分(如上所述)而形成开口961a、962a和963a。在图9l中,部分920、920'、902、902'、915c、915c'、910c和910c'是图9k的相应材料920a、902b、915c”和910c”的剩余部分。

112.图9m示出在形成电介质材料945之后的存储器装置900。电介质材料945可以包含二氧化硅。

113.图9n示出在去除图9m中的电介质材料945的一部分之后的存储器装置900。图9n中示出电介质材料945的剩余部分。

114.图9o示出在形成电介质部分915e、915f和915g之后的存储器装置900。电介质部分915e、915f和915g可以包含二氧化硅。

115.图9p示出在形成导电材料941之后的存储器装置900。导电材料941可以包含金属、导电掺杂多晶硅或其它导电材料。在形成存储器装置900的后续过程中,导电材料941可被构造成形成存储器装置900的存取线(例如,字线)。

116.图9q示出在形成部分941f、941b、941f'和941b'之后的存储器装置900。形成部分941f、941b、941f'和941b'可以包含去除导电材料941(图9p)的一部分(例如,底部),留下作为图9q所示的部分941f、941b、941f'和941b'的导电材料941的一部分。去除导电材料941的一部分可以包含冲孔蚀刻过程,以在y方向上将导电材料941的各部分彼此电分离。例如,部分941b与部分941f'电分离。部分941f也在y方向上与导电材料941的另一部分(未示出)电分离。部分941b'也在y方向上与导电材料941的另一部分(未示出)电分离。

117.图9r示出在形成电介质材料980和数据线921之后的存储器装置900。图9r还示出信号(例如,位线信号)bl1,其可以表示在存储器装置900的操作(例如,读取或写入)期间施加到数据线921的信号。信号bl1可以类似于图5中的存储器装置500的信号bl1。在图9r中,电介质材料980可以包含二氧化硅。数据线921可以在形成电介质材料980之后形成,并且可以由导电材料(例如,金属、导电掺杂多晶硅或其它导电材料)形成。

118.如图9r所示,可以形成数据线921,使其与部分920和920'电耦合且与部分941f、941b、941f'和941b'电分离。例如,图9r中的过程可以包含在形成数据线921之前去除部分941f、941b、941f'和941b'中的每一部分的一部分(例如顶部),使得在形成数据线921时数据线921与部分941f、941b、941f'和941b'电分离。

119.如图9r所示,存储器装置900的一部分可形成存储器单元910和912,其可分别类似于存储器装置200的存储器单元210和212(示意性地示于图2中)。在图9r中,部分941f和941b可以是可用于在存储器装置900的存储器操作(例如,读取或写入操作)期间控制存储

器单元910的晶体管t1和t2的存取线(例如,字线和相关联信号wl1)的一部分。部分941f'和941b'可以是可用于在存储器装置900的存储器操作(例如,读取或写入操作)期间控制存储器单元912的晶体管t1和t2的存取线(例如,字线和相关联信号wl2)的一部分。图9q未示出存储器装置900的存储器单元911(图9i)。然而,存储器单元911可位于x方向上(例如,位于图9r中的存储器单元910的视图后方),并且可以共用包含部分941f和941b的同一存取线。

120.在图9r中,部分920可以形成存储器单元910的晶体管t2的沟道部分(例如,写入沟道部分),部分902可以形成存储器单元910的电荷存储结构(例如,晶体管t1的浮动栅极),部分915c可以形成存储器单元910的晶体管t1和t2的栅极氧化物的一部分,并且部分910c可以形成存储器单元910的晶体管t1的沟道部分(例如,读取沟道部分)的一部分。部分920'可以形成存储器单元912的晶体管t2的沟道部分(例如,写入沟道部分),部分902'可以形成存储器单元912的电荷存储结构(例如,晶体管t1的浮动栅极),部分915c'可以形成存储器单元912的晶体管t1和t2的栅极氧化物的一部分,并且部分910c可以形成存储器单元910的晶体管t1的沟道部分(例如,读取沟道部分)的一部分。

121.图10a到图10e示出根据本发明的一些实施例的在形成存储器装置1000的过程期间的元件的横截面图。用于形成存储器装置1000的一些或全部过程可以用于形成上文参考图2到图8描述的存储器装置200。形成存储器装置1000的过程可以是形成存储器装置900(图9a到图9r)的过程的变体。因此,不重复形成存储器装置900和1000的过程之间的类似元件(具有相同标签)。

122.图10a示出可以使用与图9a到图9l中的存储器装置900的元件类似或相同的过程来形成的存储器装置1000的元件。因此,图10a所示的存储器装置1000的元件可以类似于图9l所示的存储器装置900的元件。

123.图10b示出在形成电介质部分1015e、1015f和1015g之后的存储器装置900。电介质部分1015e、1015f和1015g可以包含二氧化硅。

124.图10c示出在形成导电材料1041之后的存储器装置900。导电材料941可以包含金属、导电掺杂多晶硅或其它导电材料。在形成存储器装置900的后续过程中,导电材料1041可被构造成形成存储器装置1000的存取线(例如,字线)。

125.图10d示出在形成部分1041f、1041b、1041f'和1041b'之后的存储器装置1000。形成部分1041f、1041b、1041f'和1041b'可以包含去除导电材料1041(图10e)的部分(例如,底部),留下作为图10d所示的部分1041f、1041b、1041f'和1041b'的导电材料1041的一部分。去除导电材料1041的一部分可以包含冲孔蚀刻过程,以在y方向上将导电材料1041的各部分彼此电分离。例如,部分1041b与部分1041f'电分离。部分1041f也在y方向上与导电材料1041的另一部分(未示出)电分离。部分1041b'也在y方向上与导电材料1041的另一部分(未示出)电分离。

126.图10e示出在形成电介质材料1080和数据线1021之后的存储器装置1000。图10e还示出信号(例如,位线信号)bl1,其可以表示在存储器装置1000的操作(例如,读取或写入)期间施加到数据线1021的信号。信号bl1可以类似于图5中的存储器装置500的信号bl1。在图10e中,电介质材料1080可以包含二氧化硅。数据线1021可以在形成电介质材料1080之后形成,并且可以由导电材料(例如,金属、导电掺杂多晶硅或其它导电材料)形成。

127.如图10e所示,可以形成数据线1021,使其与部分920和920'电耦合且与部分

1041f、1041b、1041f'和1041b'电分离。例如,图10e中的过程可以包含在形成数据线1021之前去除部分1041f、1041b、1041f'和1041b'中的每一个的一部分(例如顶部),使得在形成数据线1021时数据线1021与部分1041f、1041b、1041f'和1041b'电分离。

128.如图10e所示,存储器装置1000的一部分可形成存储器单元1010和1012,其可分别类似于存储器装置200的存储器单元210和212(示意性地示于图2中)。在图10e中,部分1041f和1041b可以是可用于在存储器装置1000的存储器操作(例如,读取或写入操作)期间控制存储器单元1010的晶体管t1和t2的存取线(例如,字线和相关联信号wl1)的一部分。部分1041f'和1041b'可以是可用于在存储器装置1000的存储器操作(例如,读取或写入操作)期间控制存储器单元1012的晶体管t1和t2的存取线(例如,字线和相关联信号wl2)的一部分。

129.在图10e中,部分920可以形成存储器单元1010的晶体管t2的沟道部分(例如,写入沟道部分),部分902可以形成存储器单元1010的电荷存储结构(例如,晶体管t1的浮动栅极),部分915c可以形成存储器单元1010的晶体管t1和t2的栅极氧化物的一部分,并且部分910c可以形成存储器单元1010的晶体管t1的沟道部分(例如,读取沟道部分)的一部分。部分920'可以形成存储器单元1012的晶体管t2的沟道部分(例如,写入沟道部分),部分902'可以形成存储器单元1012的电荷存储结构(例如,晶体管t1的浮动栅极),部分915c'可以形成存储器单元1012的晶体管t1和t2的栅极氧化物的一部分,并且部分910c可以形成存储器单元1010的晶体管t1的沟道部分(例如,读取沟道部分)的一部分。

130.图11a、图11b和图11c示出根据本文描述的一些实施例的包含存储器单元的多个叠组的存储器装置1100结构的不同视图。图11a示出存储器装置1100的分解图(例如,在z方向上)。图11b示出存储器装置110的x方向和z方向上的侧视图(例如,横截面图)。图11c示出存储器装置1100的y方向和z方向上的侧视图(例如,横截面图)。

131.如图11a所示,存储器装置1100可以包含叠组(存储器单元叠组)11050、11051、11052和11053,这些叠组在分解图中彼此分开示出,以便于查看存储器装置1100的叠组结构。实际上,叠组11050、11051、11052,和11053可以以其中一个叠组可以在衬底(例如,半导体(例如,硅)衬底)1199上方形成(例如,堆叠)于另一叠组之上的布置附接到彼此。例如,如图11a所示,层11050、11051、11052和11053可以在垂直于衬底1199的z方向上形成(例如,在相对于衬底1199的z方向上竖直地形成)。

132.如图11a所示,叠组11050、11051、11052和11053中的每一个可以具有在x方向和y方向上布置(例如,在x方向上布置成行,在y方向上布置成列)的存储器单元。例如,叠组11050可以包含存储器单元11100、11110、11120和11130(例如,布置成行)、存储器单元11200、11210、11220和11230(例如,布置成行)以及存储器单元11300、11310、11320和11330(例如,布置成行)。

133.叠组11051可以包含存储器单元11101、11111、11121和11131(例如,布置成行)、存储器单元11201、11211、11221和11231(例如,布置成行)以及存储器单元11301、11311、11321和11331(例如,布置成行)。

134.叠组11052可以包含存储器单元11102、11112、11122和11132(例如,布置成行)、存储器单元11202、11212、11222和11232(例如,布置成行)以及存储器单元11302、11312、11322和11332(例如,布置成行)。

135.叠组11053可以包含存储器单元11103、11113、11123和11133(例如,布置成行)、存储器单元11203、11213、11223和11233(例如,布置成行)以及存储器单元11303、11313、11323和11333(例如,布置成行)。

136.如图11a所示,叠组11050、11051、11052和11053可分别位于存储器装置1100的层级(例如,部分)1150、1151、1152和1153上(例如,在z方向上竖直地形成)。叠组11050、11051、11052和11053形成存储器装置1100的存储器单元的三维(3d)结构,其中存储器装置1100的不同层级的存储器单元可以位于(例如,形成于)存储器装置1100的不同层级(例如,不同竖直部分)1150、1151、1152和1153中。

137.叠组11050、11051、11052和11053可以一次形成一个叠组。例如,可以按照叠组11050、11051、11052和11053的顺序依次形成叠组11050、11051、11052和11053(例如,首先形成叠组11051且最后形成叠组11053)。在此实例中,一个叠组(例如叠组11051)的存储器单元可以在形成另一叠组(例如叠组11050)的存储器单元之后或者在形成另一叠组(例如叠组11052)的存储器单元之前形成。替代地,叠组11050、11051、11052和11053可以并行地(例如,同时)形成,使得叠组11050、11051、11052和11053的存储器单元可以并行地形成。例如,可以并行地形成存储器装置1100的层级1150、1151、1152和1153中的存储器单元。

138.叠组11050、11051、11052和11053中的每一个的存储器单元的结构可以包含上文参考图1到图10e描述的存储器单元的结构。例如,叠组11050、11051、11052和11053的存储器单元的结构可以包含存储器装置200、900和1000的存储器单元的结构。

139.存储器装置1100可以包含数据线(例如,位线)和存取线(例如,字线)以存取叠组11050、11051、11052和11053的存储器单元。为简单起见,图11a中省略了存储器单元的数据线和存取线。然而,存储器装置1100的数据线和存取线可以分别类似于上文参考图1到图10e描述的存储器装置的数据线和存取线。

140.作为实例,图11a示出包含四个叠组(例如11050、11051、11052和11053)的存储器装置1100。然而,叠组的数目可不同于四个。作为实例,图11a示出包含存储器单元的一个层级(例如,层)的叠组11050、11051、11052和11053中的每一个。然而,叠组中的至少一个(例如,叠组11050、11051、11052和11053中的一或多个)可以具有两个(或更多)层级的存储器单元。图11a示出其中叠组11050、11051、11052和11053中的每一个包含x方向上的四个存储器单元(例如,成行)和y方向上的三个存储器单元(例如,成列)的实例。然而,成行、成列或两者的存储器单元的数目可变化。

141.设备(例如,存储器装置100、200、900、1000和1100)和方法(例如,存储器装置100和200的操作,以及形成存储器装置900和1000的方法)的图示旨在提供对各种实施例的结构的一般理解,而不是旨在提供可能利用本文描述的结构的设备的所有元件和特征的完整描述。这里的设备例如指任一装置(例如,存储器装置100、200、900、1000和1100中的任何一个)或系统(例如,可以包含存储器装置100、200、900、1000和1100中的任何一个的电子产品)。

142.上文参考图1至图10e描述的任何组件可以多种方式实现,包含经由软件进行模拟。因此,设备(例如,存储器装置100、200、900、1000和1100)或上文描述的这些存储器装置中的每一个的一部分都可以在本文中表征为“模块”(modules或module)。此类模块可包含硬件电路系统、单处理器和/或多处理器电路、存储器电路、软件程序模块和对象和/或固件

及其组合,如对于各种实施例的特定实施方案来说需要和/或适当。例如,此类模块可包含于系统操作模拟包中,例如软件电信号模拟包、电力使用和范围模拟包、电容

‑

电感模拟包、电力/散热模拟包、信号发射

‑

接收模拟包,和/或用以操作或模拟各种潜在实施例的操作的软件和硬件的组合。

143.本文描述的存储器装置(例如,存储器装置100、200、900、1000和1100)可包含于设备(例如,电子电路系统)中,所述设备如高速计算机、通信和信号处理电路系统、单处理器或多处理器模块、单个或多个嵌入式处理器、多核处理器、消息信息开关,以及包含多层、多芯片模块的专用模块。此类设备可进一步包含为多种其它设备(例如,电子系统)(例如电视机、蜂窝电话、个人计算机(例如,膝上型计算机、桌上型计算机、手持式计算机、平板计算机等)、工作站、无线电、视频播放器、音频播放器(例如,mp3(动画专家组、音频层3)播放器)、车辆、医疗装置(例如心脏监视器、血压监视器等)、机顶盒等)内的子组件。

144.上文参考图1到图10e描述的实施例包含设备和形成所述设备的方法。其中一个设备包含第一数据线、第二数据线、导电线以及耦合到第一和第二数据线的存储器单元。存储器单元包含第一晶体管和第二晶体管。第一晶体管包含电耦合到第一和第二数据线的第一区,以及与第一区电分离的电荷存储结构。第二晶体管包含与第一区电分离的第二区,所述第二区电耦合到电荷存储结构和第二数据线。导电线与第一和第二沟道区电分离。导电线的一部分跨越第一晶体管的第一区的一部分和第二晶体管的第二区的一部分。描述了包含额外设备和方法的其它实施例。

145.在具体实施方式和权利要求书中,相对于两个或更多个元件(例如,材料)使用的术语“在

…

上”、一个“在”另一个“上”意味着元件之间(例如,材料之间)的至少一些接触。术语“在

…

上方”意味着元件(例如,材料)极为接近,但可能具有一或多个额外介入元件(例如,材料)而使得接触是可能的但不是要求的。“在

…

上”或“在

…

上方”都不暗示如本文所使用的任何方向性,除非如此陈述。

146.在具体实施方式和权利要求书中,通过术语“中的至少一个”接合的项目列表可意味着所列项目的任何组合。例如,如果列举项目a和b,那么短语“a和b中的至少一个”意味着仅a;仅b;或a和b。在另一实例中,如果列举项目a、b和c,那么短语“a、b和c中的至少一个”意味着仅a;仅b;仅c;a和b(不包含c);a和c(不包含b);b和c(不包含a);或所有的a、b和c。项目a可包含单个元件或多个元件。项目b可包含单个元件或多个元件。项目c可包含单个元件或多个元件。

147.在具体实施方式和权利要求书中,通过术语“中的一个”接合的项目列表可意味着所列项目中的仅一个。例如,如果列出项目a和b,那么短语“a和b中的一个”意味着仅a(不包含b)或仅b(不包含a)。在另一实例中,如果列出项目a、b和c,那么短语“a、b和c中的一个”意味着仅a;仅b;或仅c。项目a可包含单个元件或多个元件。项目b可包含单个元件或多个元件。项目c可包含单个元件或多个元件。

148.以上描述和图式说明本发明主题的一些实施例,以使所属领域的技术人员能够实践本发明主题的实施例。其它实施例可并有结构性、逻辑、电、过程以及其它变化。实例仅代表可能的变化。一些实施例的部分及特征可包含在其它实施例的那些部分及特征中,或代替那些部分及特征。在阅读和理解以上描述后,所属领域的技术人员将明白许多其它实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1