半导体存储装置的制作方法

本发明涉及半导体存储装置。

背景技术:

作为使用半导体存储装置的装置的一例,能够列举出如日本特开2016

‑

184233号公报(专利文献1)所记载那样的经由信号线对存储器进行数据传输的存储器控制器。以下,在背景技术的说明中,括号内所示的附图标记是专利文献1的附图标记。如专利文献1的图2所示,该存储器控制器(c)具有作为半导体存储装置的存储电路(15)。而且,如专利文献1的段落0021、0022所述,该存储器控制器(c)构成为,将该存储电路(15)用作用于存储工作用数据的工作存储器,来进行替换处理或复原处理等各种处理。现有技术文献专利文献专利文献1:日本特开2016

‑

184233号公报

技术实现要素:

另外,目前为止在比较频繁地进行数据改写的半导体存储装置(上述的工作存储器等)中通常使用易失性存储器,现在正在研究用作为可改写的非易失性存储器的一种的磁阻存储器(mram)来替换该易失性存储器。这样,在半导体存储装置中使用磁阻存储器的情况下,可以考虑在磁阻存储器中不仅存储如工作数据那样比较频繁地改写的数据,也存储如设定数据(程序或初始设定数据等)那样改写频率较低的数据。然而,磁阻存储器如果在其结构上想要确保数据的可改写次数较多,则数据的保持期间变短,因此,如果以能够获得可与易失性存储器替换的程度的可改写的次数的方式构成磁阻存储器,则易于缩短如设定数据那样的改写频率较低的数据的保持期间。其结果,当使用半导体存储装置的装置启动时,需要从其他存储装置加载设定数据,可能会使启动时间变长,或可能因这样的处理而增大功耗。因此,在半导体存储装置中使用磁阻存储器的情况下,期望实现能够适当地确保数据的可改写次数和数据的保持期间这两者的技术。本发明的半导体存储装置,具有由作为一个逻辑部的对象逻辑部访问的两种磁阻存储器即第一磁阻存储器和第二磁阻存储器,所述对象逻辑部、所述第一磁阻存储器以及所述第二磁阻存储器形成于一个半导体芯片,所述第一磁阻存储器的矫顽力大于所述第二磁阻存储器的矫顽力。根据该结构,由于第一磁阻存储器的矫顽力大于第二磁阻存储器的矫顽力,因此,就第二磁阻存储器而言,能够使矫顽力较小以确保较多的数据的可改写次数,并且,就第一磁阻存储器而言,能够使矫顽力较大以确保较长的数据的保持期间。即,通过使用两种磁阻存储器,能够在半导体存储装置中形成两种存储器区域,其中,一种是由第二磁阻存储器形成的具有较多数据的可改写次数的存储器区域,另一种是由第一磁阻存储器形成的具有较

长数据的保持期间的存储器区域。而且,根据上述的结构,能够实现对象逻辑部能够访问这样的两种存储器区域的半导体芯片。如上所述,根据上述的结构,在半导体存储装置中使用磁阻存储器的情况下,能够适当地确保数据的可改写次数和数据的保持期间。半导体存储装置的进一步的特征和优点可以通过参考附图说明的实施方式的以下描述而得以明确化。

附图说明

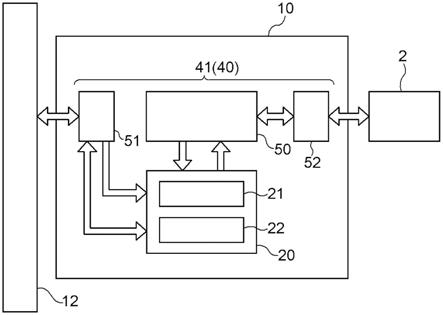

图1是表示半导体芯片的一例的概略结构的框图。图2是表示功能模块的一例的概略结构的框图。图3是表示半导体存储装置的一例的概略结构的立体图。图4是表示半导体存储装置与对象逻辑部之间的配置关系的一例的图。

具体实施方式

参照附图对半导体存储装置的实施方式进行说明。在本实施方式中,以半导体存储装置作为寄存器(寄存器文件(register file))使用的情况为例进行说明。半导体存储装置20是形成于半导体芯片1的存储装置。因此,半导体存储装置20(例如,构成半导体存储装置20的存储器单元、对存储器单元进行数据改写的改写电路)使用半导体材料而形成。在图1中示出了形成有半导体存储装置20的半导体芯片1的一例。半导体芯片1例如为soc(system on a chip:片上系统)。半导体芯片1具有集成于一片芯片的多个电路(半导体集成电路)。在半导体芯片1中形成有构成后述的逻辑部40的电路、以及构成半导体存储装置20(存储器部)的电路。在半导体芯片1中也可以形成有构成其他功能部(例如,模拟部)的电路。半导体芯片1所具有的多个电路形成于该半导体芯片1所内置的半导体基板(硅晶粒等半导体晶粒(die))。例如,半导体芯片1具有一片半导体基板,半导体芯片1所具有的所有电路能够配置为形成于该一片半导体基板。如图1所示,半导体芯片1具有通过内部总线12相互连接的多个功能模块10。另外,半导体芯片1具有cpu(central processing unit:中央处理器)等处理器11,处理器11通过内部总线12与每个功能模块10连接。每个功能模块10例如作为实现处理器11的外围功能(支持功能等)的外围逻辑部而发挥功能,或者,作为半导体芯片1与外部装置2(设置于半导体芯片1的外部的装置)之间交换数据或信号的接口部而发挥功能。外部装置2例如是设置于半导体芯片1的外部的存储装置、传感器等。在图1所示的例子中,多个功能模块10的一部分是用于与外部装置2之间交换数据或信号的功能模块10。功能模块10以及处理器11分别具有逻辑部40。逻辑部40具有逻辑电路(逻辑电路),并使用该逻辑电路进行处理(运算处理、转换处理等)。如图2所示,在本实施方式中,半导体存储装置20是附属于功能模块10的半导体存储装置,并通过该功能模块10所具有的逻辑部40进行访问。即,如果将访问半导体存储装置20的一个逻辑部40作为对象逻辑部41,则在本实施方式中,对象逻辑部41是一个功能模块10所具有的逻辑部40。在本实施方式中,半导体存储装置20作为具有对象逻辑部41的功能模块10的寄存器而发挥功能,对象逻辑部41

(具体来说,是后述的运算电路50)基于存储在半导体存储装置20中的数据进行动作。在图2中示出了具有对象逻辑部41的功能模块10的一例。以下,将图2所示的功能模块10以外的功能模块10称为其他功能模块10。如图2所示,对象逻辑部41具有运算电路50以及第一电路51。运算电路50被配置为据动作程序进行运算处理。使运算电路50动作的动作程序被存储于半导体存储装置20(具体来说,是后述的第一磁阻存储器21)。第一电路51与内部总线12和半导体存储装置20连接,并被配置为控制半导体存储装置20与其他功能模块10或处理器11之间的经由内部总线12的数据传输。即,第一电路51是作为内部总线控制部而发挥功能的控制电路。在第一电路51与半导体存储装置20之间形成有用于指定半导体存储装置20内的地址的地址总线和用于交换数据的数据总线,第一电路51被配置为读写已指定的地址的数据。图2所示的功能模块10是用于与外部装置2之间交换信号的功能模块,对象逻辑部41具有第二电路52。第二电路52与运算电路50连接,并且经由外部总线与外部装置2连接。第二电路52是作为外部信号控制部而发挥功能的控制电路。第二电路52被配置为,将从运算电路50输入的数据转换为信号并输出至外部装置2,并且将从外部装置2输入的信号转换为数据并输出至运算电路50。此外,该第二电路52也可以配置为仅进行从第二电路52向外部装置2的信号输出以及从外部装置2向第二电路52的信号输入中的任意一方。如图2所示,半导体存储装置20具有由对象逻辑部41访问的两种磁阻存储器即第一磁阻存储器21和第二磁阻存储器22。磁阻存储器(mram:magnetoresistive random access memory)是将磁隧道结(magnetic tunnel junctions)作为存储器单元30的非易失性存储器。如图3示意性所示,构成磁阻存储器的存储器单元30(磁隧道结)具有以下的结构:作为绝缘体层的第二层32被夹在作为两个强磁性体层的第一层31与第三层33之间。强磁性体层例如使用强磁性半导体材料而形成。第一层31以及第三层33中的一方为磁化固定的固定层,而第一层31以及第三层33中的另一方是磁化可变的自由层。通过改变自由层的磁化方向来切换存储器单元30(磁隧道结)的电阻值的高低,从而能够使存储器单元30存储1比特的信息。存储器单元30在与半导体芯片1的厚度方向d正交的平面上呈阵列状(二维阵列状)排列配置,虽然省略了详细说明,但用于对存储器单元30进行数据改写的改写电路被配置为使用晶体管(单元选择用晶体管)来选择改写对象的存储器单元30。如图3和图4示意性所示,对象逻辑部41、第一磁阻存储器21和第二磁阻存储器22形成于一个半导体芯片1。即,第一磁阻存储器21以及第二磁阻存储器22为嵌入式mram。其中,对象逻辑部41、第一磁阻存储器21以及第二磁阻存储器22混载于同一半导体基板(半导体晶粒(die))中。具体来说,第一磁阻存储器21以及第二磁阻存储器22相对于对象逻辑部41一体形成于表面侧d1(表层侧)。换言之,对象逻辑部41形成于半导体芯片1中的第一磁阻存储器21以及第二磁阻存储器22的背面侧d2(内层侧)。其中,表面侧d1是厚度方向d的一侧(相对于半导体基板形成各元件的一侧),背面侧d2是厚度方向d的另一侧(与表面侧d1相反的一侧)。第一磁阻存储器21的矫顽力大于第二磁阻存储器22的矫顽力。具体来说,构成第一磁阻存储器21的存储器单元30的矫顽力(具体来说,自由层的矫顽力)大于构成第二磁阻存储器22的存储器单元30的矫顽力(具体来说,自由层的矫顽力)。在本实施方式中,通过使

构成第一磁阻存储器21的存储器单元30的体积大于构成第二磁阻存储器22的存储器单元30的体积,从而使构成第一磁阻存储器21的存储器单元30的矫顽力大于构成第二磁阻存储器22的存储器单元30的矫顽力。存储器单元30的体积例如能够为第一层31、第二层32、以及第三层33的各层的体积的合计。作为构成第一磁阻存储器21的存储器单元30的体积大于构成第二磁阻存储器22的存储器单元30的体积的结构的一例,构成第一磁阻存储器21的存储器单元30的面积(沿着厚度方向d观察的面积,以下相同)能够大于构成第二磁阻存储器22的存储器单元30的面积。在该情况下,由于第一层31的厚度、第二层32的厚度以及第三层33的厚度能够在第一磁阻存储器21与第二磁阻存储器22之间共用,因此,能够抑制在半导体芯片1上形成两种磁阻存储器而导致的制造工序的复杂化。如上所述,由于第一磁阻存储器21的矫顽力大于第二磁阻存储器22的矫顽力,就第二磁阻存储器22而言,能够使矫顽力变得较小以确保较多的数据的可改写次数,并且,就第一磁阻存储器21而言,能够使矫顽力变得较大以确保较长的数据的保持期间。即,作为对象逻辑部41能够访问的存储器区域,能够在半导体芯片1上形成两种存储器区域,一种是由第二磁阻存储器22形成的数据的可改写次数较多的存储器区域,另一种是由第一磁阻存储器21形成的数据的保持期间较长的存储器区域。第一磁阻存储器21由于数据的保持期间较长,因此,从缩短使用半导体芯片1的装置的启动时间的观点来看,优选将在该装置启动时对象逻辑部41所需的数据存储于第一磁阻存储器21。从这样的观点来看,在本实施方式中,在第一磁阻存储器21中存储有设定数据。在存储于第一磁阻存储器21的设定数据中,包括对象逻辑部41(具体来说,运算电路50)的动作程序。在存储于第一磁阻存储器21的设定数据中还可以包括其他数据,例如,可以包括对象逻辑部41(具体来说,运算电路50)的初始设定数据,或者包括用于在对象逻辑部41(具体来说,运算电路50)中的运算的常数(控制常数等)的数据。另一方面,第二磁阻存储器22由于数据的可改写次数较多,因此,从半导体存储装置20的寿命的长期化的观点来看,优选将比较频繁地改写的数据存储于第二磁阻存储器22。从这样的观点出发,在本实施方式中,在第二磁阻存储器22中存储有工作数据。在存储于第二磁阻存储器22的工作数据中,包含对象逻辑部41(具体来说,运算电路50)的运算结果。在存储于第二磁阻存储器22的工作数据中还可以包括其他数据,例如,可以包含向对象逻辑部41(具体来说,运算电路50)输入的输入数据,或者包含从对象逻辑部41(具体来说,运算电路50)输出的输出数据。如图4示意性所示,在本实施方式中,第二磁阻存储器22相比第一磁阻存储器21配置在更靠近运算电路50的位置。在本实施方式中,如上所述,由于工作数据被存储在第二磁阻存储器22中,因此,与第一磁阻存储器21相比,第二磁阻存储器22更频繁地进行与运算电路50之间的数据交换。由此,通过将频繁地进行与运算电路50之间的数据交换的第二磁阻存储器22配置在运算电路50的附近,能够将运算电路50与第二磁阻存储器22之间的布线路径长度抑制得较短。其结果,能够将用于向各部供给的时钟信号的时钟树60的长度抑制得较短,从而能够实现功耗的降低。例如,通过将第二磁阻存储器22的至少一部分配置于在沿着厚度方向d的方向观察时与运算电路50重叠的位置,并将第一磁阻存储器21的至少一部分配置于在从该方向观

察时与第一电路51或第二电路52重叠的位置,能够实现第二磁阻存储器22相比第一磁阻存储器21配置于更靠近运算电路50的位置的结构。(其他实施方式)接下来,对半导体存储装置的其他实施方式进行说明。(1)在上述的实施方式中,以半导体存储装置20用作寄存器(寄存器文件)的情况为例进行了说明。但是,并不限定于这样的结构,也可以是半导体存储装置20用作寄存器以外的存储装置的结构。例如,半导体存储装置20能够被配置为作为处理器11的缓存而使用。在该情况下,对象逻辑部41是处理器11所具有的逻辑部40。而且,在第一磁阻存储器21中存储有已缓存的数据块(block)的标签(地址),在第二磁阻存储器22中存储有已缓存的数据块的内容。即,第一磁阻存储器21为标签阵列(地址阵列),第二磁阻存储器22为数据阵列。此外,处理器11除了cpu以外,也可以是gpu(graphics processing unit:图形处理器)等。另外,例如,半导体存储装置20也可以被配置为作为经由内部总线12与处理器11连接的存储装置而使用。在该情况下,对象逻辑部41为处理器11所具有的逻辑部40。而且,将由第一磁阻存储器21形成的存储器区域作为程序区域而使用,将由第二磁阻存储器22形成的存储器区域作为数据区域而使用。(2)在上述的实施方式中,以通过使构成第一磁阻存储器21的存储器单元30的体积大于构成第二磁阻存储器22的存储器单元30的体积,从而使第一磁阻存储器21的矫顽力大于第二磁阻存储器22的矫顽力的结构为例进行了说明。但是,并不限定于这样的结构,也可以通过使构成第一磁阻存储器21的存储器单元30与构成第二磁阻存储器22的存储器单元30之间的结构以及材料中的至少一个不同,从而使第一磁阻存储器21的矫顽力大于第二磁阻存储器22的矫顽力。在该情况下,与上述的实施方式不同,构成第一磁阻存储器21的存储器单元30的体积也可以在构成第二磁阻存储器22的存储器单元30的体积以下。(3)在上述的实施方式中,以第二磁阻存储器22相比第一磁阻存储器21配置在更靠近运算电路50的位置的结构为例进行了说明。但是,并不限定于这样的结构,例如,也可以采用如下的结构:第一磁阻存储器21相比第二磁阻存储器22配置在更靠近运算电路50的位置。(4)此外,上述的各实施方式中公开的结构只要不产生矛盾,也能够与其他实施方式中公开的结构组合来应用(包括作为其他实施方式而说明的实施方式彼此的组合)。关于其他结构,在本说明书中公开的实施方式在所有方面仅是例示。因此,能够在不脱离本发明的主旨的范围内适当地进行各种改变。(上述实施方式的概要)以下,对在上述说明的半导体存储装置的概要进行说明。

38.半导体存储装置(20)具有由作为一个逻辑部(40)的对象逻辑部(41)访问的两种磁阻存储器即第一磁阻存储器(21)和第二磁阻存储器(22),所述对象逻辑部(41)、所述第一磁阻存储器(21)以及所述第二磁阻存储器(22)形成于一个半导体芯片(1),所述第一磁阻存储器(21)的矫顽力大于所述第二磁阻存储器(22)的矫顽力。根据该结构,由于第一磁阻存储器(21)的矫顽力大于第二磁阻存储器(22)的矫顽力,因此,就第二磁阻存储器(22)而言,能够使矫顽力变得较小以确保较多的数据的可改写

次数,并且,就第一磁阻存储器(21)而言,能够使矫顽力变得较大以确保较长的数据的保持期间。即,通过使用两种磁阻存储器(21,22),能够在半导体存储装置(20)中形成两种存储器区域:一种是由第二磁阻存储器(22)形成的数据的可改写次数较多的存储器区域,另一种是由第一磁阻存储器(21)形成的数据的保持期间较长的存储器区域。而且,根据上述的结构,能够实现对象逻辑部(41)能够访问这样的两种存储器区域的半导体芯片(1)。如上所述,根据上述的结构,在半导体存储装置(20)中使用磁阻存储器的情况下,能够适当地确保数据的可改写次数和数据的保持期间这两者。其中,优选地,构成所述第一磁阻存储器(21)的存储器单元(30)的体积大于构成所述第二磁阻存储器(22)的存储器单元(30)的体积。根据该结构,通过在第一磁阻存储器(21)与第二磁阻存储器(22)之间共用结构或材料,并且使存储器单元(30)的体积不同,能够使第一磁阻存储器(21)的矫顽力大于第二磁阻存储器(22)的矫顽力。因此,与需要使第一磁阻存储器(21)与第二磁阻存储器(22)之间的结构或材料不同的情况相比,能够降低半导体芯片(1)的制造成本。另外,优选地,在所述第一磁阻存储器(21)中存储有包括所述对象逻辑部(41)的动作程序的设定数据,在所述第二磁阻存储器(22)中存储有包括所述对象逻辑部(41)的运算结果的工作数据。根据该结构,通过将设定数据存储在数据的保持期间较长的第一磁阻存储器(21)中,能够基本上消除在使用半导体芯片(1)的装置启动时将设定数据写入到第一磁阻存储器(21)中的需要,从而能够实现启动时间的缩短,并且能够降低这样的写入处理所需的功耗。另外,根据上述的结构,通过将比较频繁地改写的工作数据存储在数据的可改写次数较多的第二磁阻存储器(22)中,也能够适当地确保半导体存储装置(20)的寿命。此外,虽然数据的保持期间比第一磁阻存储器(21)短,但第二磁阻存储器(22)也能够使数据保持一定程度的期间。因此,在使用半导体芯片(1)的装置启动时将工作数据存储在第二磁阻存储器(22)中的情况下,也能够通过利用该工作数据来进一步缩短启动时间。如上所述,在所述第一磁阻存储器(21)中存储有所述设定数据,在所述第二磁阻存储器(22)中存储有所述工作数据的结构中,优选地,所述对象逻辑部(41)具有按照所述动作程序进行运算处理的运算电路(50),所述第二磁阻存储器(22)相比所述第一磁阻存储器(21)配置在更靠近所述运算电路(50)的位置。在第一磁阻存储器(21)中存储有设定数据,在第二磁阻存储器(22)中存储有工作数据的情况下,与第一磁阻存储器(21)相比,第二磁阻存储器(22)更频繁地进行与运算电路(50)之间的数据交换。根据上述的结构,通过将频繁地进行与运算电路(50)之间的数据交换的第二磁阻存储器(22)配置在运算电路(50)的附近,能够将运算电路(50)与第二磁阻存储器(22)之间的布线路径长度抑制得较短,从而实现功耗的降低。本发明的半导体存储装置只要能够起到上述的各效果中的至少一个即可。附图标记的说明:1 半导体芯片20 半导体存储装置21 第一磁阻存储器

22 第二磁阻存储器30 存储器单元40 逻辑部41 对象逻辑部50 运算电路

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1