存储器元件及其制备方法与流程

1.本发明是有关于一种半导体结构及其制备方法。本发明特别是有关于 一种存储器元件及其制备方法。

背景技术:

2.近来,闪存的使用需求日渐增加。快闪存储装置可分为或非门(nor) 或与非门(nand)快闪存储装置。其中,或非门存储装置通过将每个存储 单元的一端连接至接地,另一端连接至位线,典型地提供较快的编程与读 取速度。一般而言,或非门闪存是为二维型态,存储单元存在于一衬底的 二维阵列中。然而,随着现在的应用越来越多,二维结构的尺寸限制已不 敷使用。因此,为提供更高的存储容量的存储器装置,目前仍亟需研发一 种具有更优异的电特性(例如是具有良好的数据保存可靠性和操作速度)的 三维或非门存储器元件。

技术实现要素:

3.在本发明中,提供一种存储器元件及其制备方法,以解决至少一部分 上述问题。

4.根据本发明的一实施例,存储器元件包括一衬底、一叠层结构、多个 通道结构、一存储层以及多个隔离结构。衬底具有一上表面。叠层结构位 于衬底的上表面上,其中叠层结构包括依序叠层于衬底上的一第一绝缘 层、一第一导电层、一第二绝缘层、一第二导电层以及一第三绝缘层。通 道结构穿过叠层结构并电性连接于衬底,其中各通道结构包括一上部部分 及一下部部分,上部部分对应于第二导电层,下部部分对应于第一导电层。 存储层位于第二导电层与上部部分之间。隔离结构穿过叠层结构以将叠层 结构分隔为多个次叠层。

5.根据本发明的一实施例,存储器元件的制备方法包括下列步骤。首先, 提供一衬底,衬底具有一上表面;接着,在衬底的上表面上形成一叠层本 体,其中叠层本体包括依序叠层于衬底的上表面上的一第一绝缘层、一第 一导电层、一第二绝缘层、一上牺牲层以及一第三绝缘层;形成穿过叠层 本体的多个第一开口;形成多个通道结构于第一开口中,且通道结构电性 连接于衬底,其中各个通道结构包括一上部部分及一下部部分,下部部分 对应于第一导电层,上部部分位于下部部分的上方;形成对应于该上部部 分的一存储层;形成穿过叠层本体的多个第二开口;移除上牺牲层并在上 牺牲层被移除的位置形成一上部开口;填充一导电材料于上部开口中以形 成一第二导电层,如此便形成包括第一绝缘层、第一导电层、第二绝缘层、 第二导电层以及第三绝缘层的一叠层结构;此后,在第二开口中形成多个 隔离结构,隔离结构将叠层结构分隔为多个次叠层。

6.根据本发明的一实施例,存储器元件的制备方法包括下列步骤。首先, 提供一衬底,衬底具有一上表面;接着,在衬底的上表面上形成一叠层本 体,其中叠层本体包括依序叠层于衬底的上表面上的一第一绝缘层、一下 牺牲层、一第二绝缘层、一上牺牲层以及一第三绝缘层;形成穿过叠层本 体的多个第一开口;形成多个通道结构的多个下部部分于第

一开口中;在 各个第一开口中形成对应于上牺牲层的一存储层;形成通道结构的多个上 部部分于第一开口中,上部部分位于下部部分之上;形成穿过叠层本体的 多个第二开口;移除上牺牲层及下牺牲层,并分别在上牺牲层与下牺牲层 被移除的位置形成一上部开口及一下部开口;填充一导电材料于上部开口 与下部开口中以分别形成一第二导电层及一第一导电层,如此便形成包括 第一绝缘层、第一导电层、第二绝缘层、第二导电层以及第三绝缘层的一 叠层结构;此后,在第二开口中形成多个隔离结构,隔离结构将叠层结构 分隔为多个次叠层。

7.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并 配合所附附图,作详细说明如下。然而,本发明的保护范围当视前述的权 利要求书所界定者为准。

附图说明

8.图1a绘示根据本发明的一实施例的存储器元件的俯视图。

9.图1b绘示沿图1的a-a'联机的根据本发明的一实施例的存储器元 件的剖面图。

10.图1c绘示根据本发明的另一实施例的存储器元件的剖面图。

11.图1d绘示根据本发明的又一实施例的存储器元件的剖面图。

12.图1e绘示根据本发明的又一实施例的存储器元件的剖面图。

13.图1f绘示根据本发明的又一实施例的存储器元件的剖面图。

14.图1g绘示根据本发明的又一实施例的存储器元件的剖面图。

15.图1h绘示根据本发明的又一实施例的存储器元件的剖面图。

16.图2a至图2n绘示根据本发明的一实施例的存储器元件的形成方法 的剖面图。

17.图3a至图3m绘示根据本发明的另一实施例的存储器元件的形成方 法的剖面图。

18.图4a至图4l绘示根据本发明的又一实施例的存储器元件的形成方法 的剖面图。

19.图5绘示根据本发明的一实施例的存储器元件的等效电路图。

20.图6a绘示根据本发明的一实施例的通过福勒-诺德汉注入 (fowler-nordheim injection)进行编程操作的存储器元件的等效电路图。

21.图6b绘示根据本发明的一实施例的通过通道热电子注入 (channel-hot-electron injection)进行编程操作的存储器元件的等效电路图。

22.图7a绘示根据本发明的一实施例的通过福勒-诺德汉注入进行擦除操 作的存储器元件的等效电路图。

23.图7b绘示根据本发明的一实施例的通过带对带隧穿诱发热空穴 (band-to-band tunneling induced hot hole injection)进行擦除操作的存储器元 件的等效电路图。

24.图8绘示根据本发明的一实施例的读取操作的存储器元件的等效电路 图。

25.图9a至图9r绘示根据本发明的又一实施例的存储器元件的形成方 法的剖面图。

26.图10a至图10k绘示根据本发明的又一实施例的存储器元件的形成 方法的剖面图。

27.图11a至图11m绘示根据本发明的又一实施例的存储器元件的形成 方法的剖面图。

28.图12a至图12k绘示根据本发明的又一实施例的存储器元件的形成 方法的剖面图。

29.图13绘示根据本发明的一实施例的通过福勒-诺德汉注入 (fowler-nordheim injection)进行编程操作的存储器元件的等效电路图。

30.图14a绘示根据本发明的一实施例的通过福勒-诺德汉注入进行擦除 操作的存储器元件的等效电路图。

31.图14b绘示根据本发明的一实施例的通过带对带隧穿诱发热空穴进 行擦除操作的存储器元件的等效电路图。

32.图15绘示根据本发明的一实施例的读取操作的存储器元件的等效电 路图。

33.【符号说明】

34.100、200、300、400、500、600、700:存储器元件

35.110、210、310、410、510、610、710:衬底

36.110a、210a、310a、410a、510a、610a、710a:上表面

37.112、212、312、412、512、612、712:通道结构

38.112a、212a、312a:下部部分

39.112b、212b、312b:上部部分

40.112c、212c、312c、412c、512c、612c、712c、118、218、318、418、 518、618、718:掺杂区

41.112t:顶面

42.122、222、322、422、522、622、722:第一绝缘层

43.124、224、324、424、524、624、724:第二绝缘层

44.126、226、326、426、526、626、726:第三绝缘层

45.128、228、328:盖层

46.130、230、330、430、530、630、730:第一导电层

47.132、232、332、432、532、632、go4、go5、go6:热氧化层

48.132'、232'、332'、432'、532'、632'、732':氧化物层

49.140、240、340、440、540、640、740:上牺牲层

50.152、252、352、452、552、652、752:第一开口

51.154、254、354、454、554、654、754:第二开口

52.156、256、356、456、556、656、756:上部开口

53.162、262、362、462、562、662、762:存储层

54.164、364、664:保护层

55.166、266、366、566、666、766:介电材料

56.172、272、372、472、572、672、772:第二导电层

57.172'、272'、372'、472'、572'、672'、772':导电材料

58.174、274、374、474、574、674、774:隔离结构

59.176、276、376、476、576、676、776:导电连接结构

60.211:掺杂物

61.342、442、642、742:下牺牲层

62.259、459、559、759:垂直开口

63.358、458、658:下部开口

64.472':导电材料

65.bl、bl0、bl1、bl2:位线

66.cl4、cl5、cl6、cl7:顶导电层

67.csl:共同源极线

68.gsl0、gsl1、gsl2:接地选择线

69.h1:第一高度

70.h2:第二一高度

71.m、m1、m2、m3、m4、m5、m6、m7:存储单元

72.ol4、ol5、ol6、ol7:顶绝缘层

73.p1:顶部开口

74.s1、s2、s3、s4、s5、s6、s7:叠层结构

75.s1'、s2'、s3'、s4'、s5'、s6'、s7':叠层本体

76.slt1:第一沟道

77.slt2:第二沟道

78.slt3:第三沟道

79.ss1、ss2:次叠层

80.t、t1、t2、t3、t4、t5、t6、t7、ts4、ts5、ts6、ts7:晶体管

81.un、un1、un2、un3、un4、un5、un6、un7、un

t

:单元存储单 元

82.wl0、wl1、wl2:字线

具体实施方式

83.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实 施例,并参照附图,对本发明进一步详细说明。

84.在下文的详细描述中,为了便于解释,提供各种的特定细节以整体理 解本发明的实施例。然而,应理解的是,一或多个实施例能够在不采用这 些特定细节的情况下实现。在其他情况下,为了简化附图,已知的结构及 元件是以示意图表示。

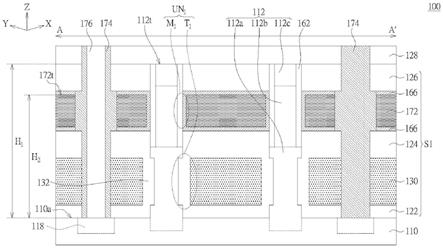

85.图1a绘示根据本发明的一实施例的存储器元件100的俯视图;图1b 绘示沿图1的a-a'联机的根据本发明的一实施例的存储器元件100的剖 面图。

86.请参照图1a,多个位线bl及共同源极线csl位于叠层结构s1的上 方,其中多个位线bl及共同源极线csl沿着平行于衬底110的上表面 110a(绘示于图1b)的第一方向(例如是y轴方向)延伸,且多个位线bl沿 着垂直于第一方向的一第二方向(例如是x轴方向)排列且分开。位线bl 分别电性连接于对应的通道结构112。共同源极线csl电性连接于对应的 导电连接结构176。

87.请同时参照图1a及图1b,存储器元件100包括一衬底110、一叠层 结构s1、一盖层128、多个通道结构112、一热氧化层132、一存储层162、 一介电材料166、多个隔离结构174以及多个导电连接结构176。叠层结 构s1形成于衬底110的上表面110a上。叠层结构s1包括依序(例如是沿 着z轴)叠层于衬底110上的一第一绝缘层122、一第一导电层130、一第 二绝缘层124、一第二导电层172以及一第三绝缘层126。盖层128可覆 盖叠层结构s1,亦即是位于第三绝缘层126上。在一些实施例中,衬底110可为硅衬底或其他合适的衬底。第一绝缘

层122、第二绝缘层124、第 三绝缘层126及盖层128可由氧化物所形成,例如是二氧化硅(sio2)。第 一导电层130与第二导电层172可由导电材料所形成,此导电材料例如是 钨(w)、铝(al)、氮化钛(tin)、氮化钽(tan)、掺杂或未掺杂的多晶硅 (poly-silicon)或其他合适的材料。在本实施例中,第一导电层130与第二 导电层172是由不同的材料所形成,例如分别由n型掺杂的多晶硅及钨所 形成,然本发明并不以此为限,第一导电层130与第二导电层172可由相 同的材料所形成。在一些实施例中,第一导电层130的厚度可为 可用于调整临界电压(vt)。

88.通道结构112穿过(例如是沿着z轴)叠层结构s1并电性连接于衬底 110,其中每个通道结构112包括一下部部分112a及一上部部分112b。上 部部分112b位于下部部分112a的上方,且上部部分112b直接连结于下部 部分112a。换言之,上部部分112b对应于第二导电层172,下部部分112a 对应于第一导电层130。通道结构112的顶部区域可具有一掺杂区112c, 例如是n型半导体的掺杂物,使得通道结构112可电性连接于位线bl。 在一些实施例中,通道结构112可为一外延生长层,例如是经由外延生长 (epitaxial growth)工艺所形成的单晶或多晶硅层或上述的任一组合,可以 是未掺杂或轻微p型掺杂的外延生长层。通道结构112(亦即是外延生长层) 的一顶面112t与衬底110的上表面110a之间具有一第一高度h1,第二导 电层172的一顶面172t与衬底110的上表面110a之间具有一第二高度h2, 第一高度h1可大于第二高度h2。相较于通道结构仅部分包括外延生长层 的比较例而言,由于本发明包括上部部分112b以及下部部分112a的通道 结构112是由外延生长工艺所形成,通道结构112可具有较低的电阻,具 有较佳的导电性,存储器元件100可具有较快的操作速度(例如是读取、写 入的操作速度)。

89.热氧化层132位于第一导电层130与通道结构112之间。例如,热氧 化层132环绕至少一部份的通道结构112的下部部分112a。在一些实施例 中,热氧化层132是直接对第一导电层130进行一氧化工艺所形成的一氧 化物层,例如是二氧化硅(sio2)。由于热氧化层132是经由直接氧化导电 层(例如是第一导电层130)所形成的氧化物层,而非是通过沉积工艺(例如 是化学气相沉积(cvd)、物理气相沉积(pvd)或其他沉积工艺)所形成的氧 化物层,热氧化层132的氧化物的纯度是大于沉积法所形成的绝缘层(例如 是第一绝缘层122、第二绝缘层124或第三绝缘层126)的氧化物的纯度。 相较于热氧化层是经由沉积工艺所形成的氧化物层的比较例而言,由于本 发明的热氧化层是直接对导电层进行氧化工艺所形成的氧化物层,热氧化 层具有较高的氧化物纯度及质量,可较佳地控制临界电压(vt),故可在低 功率的应用情形中有较低的临界电压,使存储器元件100可具有较佳的可 靠度。

90.存储层162位于第二导电层172与通道结构112的上部部分112b之 间。举例而言,存储层162沿着z轴方向延伸并环绕通道结构112的上部 部分112b。存储层162可以由包含氧化硅(silicon oxide)层、氮化硅(silicon nitride)层和氧化硅层的复合层(即,ono层)所构成。例如,存储层162可 包括隧穿层、捕捉层及阻挡层。隧穿层可包括二氧化硅(sio2)、二氧化硅 (sio2)/氮氧化硅(sion)所形成的双层结构或其他合适的材料。捕捉层可包 括氮化硅、多晶硅或其他合适的材料。阻挡层可包括二氧化硅(sio2)或其 他合适的材料。

91.介电材料166位于存储层162与第二导电层172之间。部分的介电材 料166可沿着衬底110的上表面110a上的法线方向延伸,部分的介电材 料166可沿着平行于衬底110的上表面110a的方向延伸,介电材料166 可包覆第二导电层172。在一些实施例中,介电材料166

可包括一高介电 常数材料(high k material),例如是氧化铝(al2o3)或其他合适的材料。介电 材料166亦可作为阻挡层,以防止电荷侧向扩散(lateral diffusion)。相较于 没有使用高介电常数材料作为介电材料的比较例而言,由于本案的介电材 料166可使用高介电常数材料,不需使用太高的电压即可进行存储器元件 的操作(例如是擦除与写入),故可使存储器元件的效能受到改善。

92.隔离结构174可穿过叠层结构s1,而将叠层结构s1分隔为多个次叠 层ss1、ss2。本实施例仅示例性绘示2个次叠层,然本发明并不以此为 限,次叠层的数量可大于2个。隔离结构174可由绝缘材料所形成,例如 是氧化物或其他合适的材料。相邻的次叠层ss1、ss2中的第二导电层172 之间可通过隔离结构174物理性及电性隔离,因此不同次叠层中的第二导 电层172可独立操作,例如是施加不同的电压。

93.导电连接结构176可穿过叠层结构s1,并例如是透过掺杂区118电性 连接于衬底110。掺杂区118例如是通过n型半导体的掺杂物所掺杂。导 电连接结构176可电性连接于共同源极线csl。

94.在一些实施例中,第一导电层130与热氧化层132之间的每一重叠位 置(intersection)可形成一晶体管t1,第二导电层172、介电材料166与存储 层162之间的每一重叠位置可形成一存储单元m1。晶体管t1与存储单元 m1通过通道结构112互相串连,并可共同形成一单元存储单元(unit cell)un1。第一导电层130可作为接地选择线(ground select line),第二导电 层172可作为字线。

95.图1c绘示根据本发明的另一实施例的存储器元件200的剖面图,存 储器元件200与存储器100具有类似的俯视图(例如是图1a),故图1c绘 示类似于沿图1的a-a'联机的剖面图。存储器元件200具有类似于存储 器100的结构,其不同之处在于存储层262的形状有所不同。

96.请参照图1c,存储器元件200包括一衬底210、一叠层结构s2、一 盖层228、多个通道结构212、一热氧化层232、一存储层262、一介电材 料266、多个隔离结构274以及多个导电连接结构276。叠层结构s2形成 于衬底210的上表面210a上。叠层结构s2包括依序(例如是沿着z轴)叠 层于衬底210上的一第一绝缘层222、一第一导电层230、一第二绝缘层 224、一第二导电层272以及一第三绝缘层226。盖层228可覆盖叠层结构 s2,亦即是位于第三绝缘层226上。在本实施例中,第一导电层230与第 二导电层272是由不同的材料所形成,例如分别由n型掺杂的多晶硅及钨 (w)所形成,然本发明并不以此为限,第一导电层230与第二导电层272 可由相同的材料所形成。在一些实施例中,第一导电层230的厚度可为 可用于调整临界电压(vt)。

97.通道结构212(例如是沿着z轴)穿过叠层结构s2并电性连接于衬底 210,其中每个通道结构212包括一上部部分212b及一下部部分212a。上 部部分212b对应于第二导电层272,下部部分212a对应于第一导电层230。 通道结构212的顶部区域可具有一掺杂区212c,例如是n型半导体的掺杂 物,使得通道结构212可电性连接于位线bl。在一些实施例中,通道结 构212可为一外延生长层,例如是经由外延生长(epitaxial growth)工艺所 形成的单晶或多晶硅层或上述的任一组合,可以是未掺杂或轻微p型掺杂 的外延生长层。相较于通道结构仅部分包括外延生长层的比较例而言,由 于本发明包括上部部分212b以及下部部分212a的通道结构212是由外延 生长工艺所形成,通道结构212可具有较低的电阻,具有

较佳的导电性, 存储器元件200可具有较快的操作速度(例如是读取、写入的操作速度)。

98.热氧化层232位于第一导电层230与通道结构212之间。例如,热氧 化层232环绕至少一部份的通道结构212的下部部分212a。在一些实施例 中,热氧化层232是直接对第一导电层230进行一氧化工艺所形成的一氧 化物,例如是二氧化硅(sio2)。由于热氧化层232是经由直接氧化导电层(例 如是第一导电层130)所形成的氧化物层,而非是通过沉积工艺(例如是化 学气相沉积(cvd)、物理气相沉积(pvd)或其他沉积工艺)所形成的氧化物 层,热氧化层232的氧化物的纯度是大于沉积法所形成的绝缘层(例如是第 一绝缘层222、第二绝缘层224或第三绝缘层226)的氧化物的纯度。相较 于热氧化层是经由沉积工艺所形成的氧化物层的比较例而言,由于本发明 的热氧化层是直接对导电层进行氧化工艺所形成的氧化物层,热氧化层具 有较高的氧化物纯度及质量,可较佳地控制临界电压(vt),故可在低功率 的应用情形中有较低的临界电压,使存储器元件200可具有较佳的可靠度。

99.存储层262位于第二导电层272与通道结构212的上部部分212b之 间。举例而言,部分的存储层262沿着衬底210的上表面210a的法线方 向(例如是z轴方向)延伸,部分的存储层262沿着平行于衬底210的上表 面210a的方向延伸。存储层262可环绕通道结构212的上部部分212b并 覆盖第二导电层272。存储层262可以由包含氧化硅(silicon oxide)层、氮 化硅(silicon nitride)层和氧化硅层的复合层(即,ono层)所构成。例如,存 储层262可包括隧穿层、捕捉层及阻挡层。隧穿层可包括二氧化硅(sio2)、 二氧化硅(sio2)/氮氧化硅(sion)所形成的双层结构或其他合适的材料。捕 捉层可包括氮化硅、多晶硅或其他合适的材料。阻挡层可包括二氧化硅 (sio2)或其他合适的材料。

100.介电材料266位于存储层262与第二导电层272之间。部分的介电材 料266可沿着衬底210的上表面210a的法线方向延伸,部分的介电材料266可沿着平行于衬底210的上表面210a的方向延伸,介电材料266可包 覆第二导电层272。在一些实施例中,介电材料266可包括一高介电常数 材料(high k material),例如是氧化铝(al2o3)或其他合适的材料。介电材料 266亦可作为阻挡层,以防止电荷侧向扩散(lateral diffusion)。相较于没有 使用高介电常数材料作为介电材料的比较例而言,由于本案的介电材料 266可使用高介电常数材料,不需使用太高的电压即可进行存储器元件的 操作(例如是擦除与写入),故可使存储器元件的效能受到改善。

101.隔离结构274可穿过叠层结构s2,而将叠层结构s2分隔为多个次叠 层。隔离结构274可由绝缘材料所形成,例如是氧化物或其他合适的材料。 相邻的次叠层中的第二导电层272之间可通过隔离结构274物理性及电性 隔离,因此不同次叠层中的第二导电层272可独立操作,例如是施加不同 的电压。

102.导电连接结构276可穿过叠层结构s2,并例如是透过掺杂区218电性 连接于衬底210。掺杂区218例如是通过n型半导体的掺杂物所掺杂。导 电连接结构276可电性连接于共同源极线。

103.在一些实施例中,第一导电层230与热氧化层232之间的每一重叠位 置(intersection)可形成一晶体管t2,第二导电层272、介电材料266与存储 层262之间的每一重叠位置可形成一存储单元m2。晶体管t2与存储单元 m2通过通道结构212互相串连,并可共同形成一单元存储单元(unit cell)un2。第一导电层230可作为接地选择线,第二导电层272可作为字 线。

104.相较于存储元件100而言,由于存储元件200的存储层262是部分沿 着衬底210的上表面210a的法线方向延伸,另一部分是沿着平行于衬底 210的上表面210a的方向延伸,具有类似u型的外型,可具有较佳的防 止电荷侧向扩散的能力,较不易影响临界电压。

105.图1d绘示根据本发明的又一实施例的存储器元件300的剖面图,存 储器元件300与存储器100具有类似的俯视图(例如是图1a),故图1d绘 示类似于沿图1a的a-a'联机的剖面图。存储器元件300具有类似于存 储器100的结构,其不同之处在于第一导电层330的材料有所不同,以及 介电材料366的分布位置有所不同。

106.请参照图1d,存储器元件300包括一衬底310、一叠层结构s3、一 盖层328、多个通道结构312、一热氧化层332、一存储层362、一介电材 料366、多个隔离结构374以及多个导电连接结构376。叠层结构s3形成 于衬底210的上表面210a上。叠层结构s3包括依序(例如是沿着z轴)叠 层于衬底310上的一第一绝缘层322、一第一导电层330、一第二绝缘层 324、一第二导电层372以及一第三绝缘层326。盖层328可覆盖叠层结构 s3,亦即是位于第三绝缘层326上。在一些实施例中,第一导电层330与 第二导电层372是由相同的导电材料所形成,此导电材料例如是钨(w)、 铝(al)、氮化钛(tin)、氮化钽(tan)、多晶硅(poly-silicon)或其他合适的材 料。在本实施例中,第一导电层330与第二导电层372皆由钨所形成。在 一些实施例中,第一导电层330的厚度可为可用于调整临 界电压(vt)。

107.通道结构312穿过(例如是沿着z轴)叠层结构s3并电性连接于衬底 310,其中每个通道结构312包括一上部部分312b及一下部部分312a。上 部部分312b对应于第二导电层372,下部部分312a对应于第一导电层330。 通道结构312的顶部区域可具有一掺杂区312c,例如是n型半导体的掺杂 物,使得通道结构312可电性连接于位线bl。在一些实施例中,通道结 构312可为一外延生长层,例如是经由外延生长(epitaxial growth)工艺所 形成的单晶或多晶硅层或上述的任一组合,可以是未掺杂或轻微p型掺杂 的外延生长层。相较于通道结构仅部分包括外延生长层的比较例而言,由 于本发明包括上部部分312b以及下部部分312a的通道结构312是由外延 生长工艺所形成,通道结构312可具有较低的电阻,具有较佳的导电性, 存储器元件300可具有较快的操作速度(例如是读取、写入的操作速度)。

108.热氧化层332位于第一导电层330与通道结构312之间。例如,热氧 化层332环绕至少一部份的通道结构312的下部部分312a。在一些实施例 中,热氧化层332是直接对通道结构312进行一氧化工艺所形成的一氧化 物,例如是二氧化硅(sio2)。由于热氧化层332是经由直接氧化导电层(例 如是通道结构312)所形成的氧化物层,而非是通过沉积工艺(例如是化学 气相沉积(cvd)、物理气相沉积(pvd)或其他沉积工艺)所形成的氧化物层, 热氧化层332的氧化物的纯度是大于沉积法所形成的绝缘层(例如是第一 绝缘层322、第二绝缘层324或第三绝缘层326)的氧化物的纯度。相较于 热氧化层是经由沉积工艺所形成的氧化物层的比较例而言,由于本发明的 热氧化层是直接对导电层进行氧化工艺所形成的氧化物层,热氧化层具有 较高的氧化物纯度及质量,可较佳地控制临界电压(vt),故可在低功率的 应用情形中有较低的临界电压,使存储器元件300可具有较佳的可靠度。

109.存储层362位于第二导电层372与通道结构312的上部部分312b之 间。举例而言,存储层362沿着衬底210的上表面210a的法线方向(例如 是z轴方向)延伸,可环绕通道结构312的上部部分312b。存储层362可 以由包含氧化硅(silicon oxide)层、氮化硅(silicon nitride)层和氧化硅层的复 合层(即,ono层)所构成。例如,存储层362可包括隧穿层、捕捉

层及阻 挡层。隧穿层可包括二氧化硅(sio2)、二氧化硅(sio2)/氮氧化硅(sion)所形 成的双层结构或其他合适的材料。捕捉层可包括氮化硅、多晶硅或其他合 适的材料。阻挡层可包括二氧化硅(sio2)或其他合适的材料。

110.介电材料366位于存储层362与第二导电层372之间,且位于第一导 电层330与热氧化层332之间。部分的介电材料366可沿着衬底310的上 表面310a的法线方向延伸,部分的介电材料366可沿着平行于衬底310 的上表面310a的方向延伸,介电材料366可包覆第一导电层330以及第 二导电层372。在一些实施例中,介电材料366可包括一高介电常数材料 (high k material),例如是氧化铝(al2o3)或其他合适的材料。介电材料366 亦可作为阻挡层,以防止电荷侧向扩散(lateral diffusion)。相较于没有使用 高介电常数材料作为介电材料的比较例而言,由于本案的介电材料366可 使用高介电常数材料,不需使用太高的电压即可进行存储器元件的操作(例 如是擦除与写入),故可使存储器元件300的效能受到改善。

111.隔离结构374可穿过叠层结构,而将叠层结构分隔为多个次叠层。隔 离结构374可由绝缘材料所形成,例如是氧化物或其他合适的材料。相邻 的次叠层中的第二导电层372之间可通过隔离结构374物理性及电性隔 离,因此不同次叠层中的第二导电层372可独立操作,例如是施加不同的 电压。

112.导电连接结构376可穿过叠层结构,并例如是透过掺杂区318电性连 接于衬底310。掺杂区318例如是通过n型半导体的掺杂物所掺杂。导电 连接结构376可电性连接于共同源极线。

113.在一些实施例中,第一导电层330与热氧化层332之间的重叠位置 (intersection)可形成一晶体管t3,第二导电层372、介电材料366与存储层 362之间的重叠位置可形成一存储单元m3。晶体管t3与存储单元m3通过 通道结构312互相串连,并可共同形成一单元存储单元(unit cell)un3。第 一导电层330可作为接地选择线,第二导电层372可作为字线。

114.本案的上述实施例提供一些具有2层导电层的存储器元件100~300, 然本发明并不限于此,导电层的数量亦可大于2。其中,下文中列举一些 具有3层导电层的存储器元件400~700的实施例。存储器元件400~700之 中类似于存储器元件100~300的元件是以类似的元件符号表示。相同的元 件名称可具有相同或类似的材料。

115.图1e绘示根据本发明的另一实施例的存储器元件400的剖面图,存 储器元件400与存储器100具有类似的俯视图(例如是图1a),故图1e绘 示类似于沿图1的a-a'联机的剖面图。

116.请参照图1e,存储器元件400包括一衬底410、一第一绝缘层422、 一第一导电层430、一第二绝缘层424、一第二导电层472、多个通道结构 412、热氧化层432及go4、一存储层462、一第三绝缘层426、一顶导电 层cl4、一顶绝缘层ol4、多个隔离结构474以及多个导电连接结构476。

117.在本实施例中,第一导电层430与第二导电层472是由不同的材料所 形成,例如分别由n型掺杂的多晶硅及钨(w)所形成,然本发明并不以此 为限,第一导电层430与第二导电层472可由相同的材料所形成。在一些 实施例中,第一导电层430的厚度可为可用于调整临界电 压(vt)。

118.通道结构412(例如是沿着z轴)穿过叠层结构s4并电性连接于衬底 410。通道结构412的顶部区域可具有一掺杂区412c,例如是n型半导体 的掺杂物,使得通道结构412可电性连接于位线bl。在一些实施例中, 通道结构412可为一外延生长层,例如是经由外延生长工艺所形成的单晶 或多晶硅层或上述的任一组合,可以是未掺杂或轻微p型掺杂的外延生长 层。

119.热氧化层432及go4分别位于第一导电层430与通道结构412之间, 以及顶导电层cl4与通道结构412之间。例如,热氧化层432环绕至少一 部份的通道结构412的下部部分,热氧化层go4环绕至少一部份的通道结 构412的上部部分。在一些实施例中,热氧化层432及go4是直接对通道 结构412进行一氧化工艺所形成的一氧化物,例如是二氧化硅(sio2)。由 于热氧化层432及go4是经由直接氧化通道结构412所形成的氧化物层, 而非是通过沉积工艺(例如是化学气相沉积(cvd)、物理气相沉积(pvd)或 其他沉积工艺)所形成的氧化物层,热氧化层432及go4的氧化物的纯度 是大于沉积法所形成的绝缘层(例如是第一绝缘层422、第二绝缘层424或 第三绝缘层426)的氧化物的纯度。相较于热氧化层是经由沉积工艺所形成 的氧化物层的比较例而言,由于本发明的热氧化层是直接对导电层进行氧 化工艺所形成的氧化物层,热氧化层具有较高的氧化物纯度及质量,可较 佳地控制临界电压(vt),故可在低功率的应用情形中有较低的临界电压, 使存储器元件400可具有较佳的可靠度。

120.存储层462位于第二导电层472与通道结构412之间。举例而言,部 分的存储层462沿着衬底410的上表面410a的法线方向(例如是z轴方向) 延伸,部分的存储层462沿着平行于衬底410的上表面410a的方向延伸。 存储层462可环绕通道结构412并覆盖第二导电层472。存储层462可以 由包含氧化铝(al2o3,aluminium oxide)、氧化硅(silicon oxide)层、氮化硅 (silicon nitride)层和氧化硅层的复合层(即,aono层)所构成。例如,存储 层462可包括隧穿层、捕捉层及阻挡层。隧穿层可包括二氧化硅(sio2)、 二氧化硅(sio2)/氮氧化硅(sion)所形成的双层结构或其他合适的材料。捕 捉层可包括氮化硅、多晶硅或其他合适的材料。阻挡层可包括二氧化硅 (sio2)或其他合适的材料。

121.隔离结构474可穿过叠层结构s4,而将叠层结构s4分隔为多个次叠 层。隔离结构474可由绝缘材料所形成,例如是氧化物或其他合适的材料。 相邻的次叠层中的第二导电层472之间可通过隔离结构474物理性及电性 隔离,因此不同次叠层中的第二导电层472可独立操作,例如是施加不同 的电压。

122.导电连接结构476可穿过叠层结构s4,并例如是透过掺杂区418电性 连接于衬底410。掺杂区418例如是通过n型半导体的掺杂物所掺杂。导 电连接结构476可电性连接于共同源极线。

123.在一些实施例中第一导电层430与热氧化层432之间的每一重叠位置 (intersection)可形成一晶体管t4,顶导电层cl4与热氧化层go4之间的每 一重叠位置可形成一晶体管ts4,第二导电层472与存储层462之间的每 一重叠位置可形成一存储单元m4。晶体管t4、晶体管ts4与存储单元m4通过通道结构412互相串连,并可共同形成一单元存储单元(unit cell)un4,亦可称作一存储单元串行。第一导电层430可作为接地选择线, 第二导电层472可作为字线,顶导电层cl4可作为串行选择线。

124.图1f绘示根据本发明的另一实施例的存储器元件500的剖面图,存 储器元件500

与存储器100具有类似的俯视图(例如是图1a),故图1f绘 示类似于沿图1的a-a'联机的剖面图。

125.请参照图1f,存储器元件500包括一衬底510、一第一绝缘层522、 一第一导电层530、一第二绝缘层524、一第二导电层572、多个通道结构 512、热氧化层532及go5、一存储层562、一第三绝缘层526、一顶导电 层cl5、一顶绝缘层ol5、多个隔离结构574以及多个导电连接结构576。

126.在本实施例中,第一导电层530与第二导电层572是由不同的材料所 形成,例如分别由n型掺杂的多晶硅及钨(w)所形成,然本发明并不以此 为限,第一导电层530与第二导电层572可由相同的材料所形成。在一些 实施例中,第一导电层530的厚度可为可用于调整临界电 压(vt)。

127.通道结构512(例如是沿着z轴)穿过叠层结构s5并电性连接于衬底 510。通道结构512的顶部区域可具有一掺杂区512c,例如是n型半导体 的掺杂物,使得通道结构512可电性连接于位线bl。在一些实施例中, 通道结构512可为一外延生长层,例如是经由外延生长工艺所形成的单晶 或多晶硅层或上述的任一组合,可以是未掺杂或轻微p型掺杂的外延生长 层。

128.热氧化层532及go5分别位于第一导电层530与通道结构512之间, 以及顶导电层cl5与通道结构512之间。例如,热氧化层532环绕至少一 部份的通道结构512的下部部分,热氧化层go5环绕至少一部份的通道结 构512的上部部分。在一些实施例中,热氧化层532及go5是直接对通道 结构512进行氧化工艺所形成的一氧化物,例如是二氧化硅(sio2)。由于 热氧化层532及go5是经由直接氧化通道结构512所形成的氧化物层,而 非是通过沉积工艺(例如是化学气相沉积(cvd)、物理气相沉积(pvd)或其 他沉积工艺)所形成的氧化物层,热氧化层532及go5的氧化物的纯度是 大于沉积法所形成的绝缘层(例如是第一绝缘层522、第二绝缘层524或第 三绝缘层526)的氧化物的纯度。相较于热氧化层是经由沉积工艺所形成的 氧化物层的比较例而言,由于本发明的热氧化层是直接对导电层进行氧化 工艺所形成的氧化物层,热氧化层具有较高的氧化物纯度及质量,可较佳 地控制临界电压(vt),故可在低功率的应用情形中有较低的临界电压,使 存储器元件500可具有较佳的可靠度。

129.存储层562位于第二导电层572与通道结构512之间。举例而言,部 分的存储层562沿着衬底510的上表面510a的法线方向(例如是z轴方向) 延伸,部分的存储层562沿着平行于衬底510的上表面510a的方向延伸。 存储层562可环绕通道结构512并覆盖第二导电层572。存储层562可以 由包含氧化硅(silicon oxide)层、氮化硅(silicon nitride)层和氧化硅层的复合 层(即,ono层)所构成。例如,存储层562可包括隧穿层、捕捉层及阻挡 层。隧穿层可包括二氧化硅(sio2)、二氧化硅(sio2)/氮氧化硅(sion)所形成 的双层结构或其他合适的材料。捕捉层可包括氮化硅、多晶硅或其他合适 的材料。阻挡层可包括二氧化硅(sio2)或其他合适的材料。

130.隔离结构574可穿过叠层结构s5,而将叠层结构s5分隔为多个次叠 层。隔离结构574可由绝缘材料所形成,例如是氧化物或其他合适的材料。 相邻的次叠层中的第二导电层572之间可通过隔离结构574物理性及电性 隔离,因此不同次叠层中的第二导电层572可独立操作,例如是施加不同 的电压。

131.导电连接结构576可穿过叠层结构s5,并例如是透过掺杂区518电性 连接于衬底410。掺杂区418例如是通过n型半导体的掺杂物所掺杂。导 电连接结构476可电性连接于共同源极线。

132.在一些实施例中第一导电层530与热氧化层532之间的每一重叠位置 (intersection)可形成一晶体管t5,顶导电层cl5与热氧化层go5之间的每 一重叠位置可形成一晶体管ts5,第二导电层572与存储层562之间的每 一重叠位置可形成一存储单元m5。晶体管t5、晶体管ts5与存储单元m5通过通道结构512互相串连,并可共同形成一单元存储单元(unit cell)un5,亦可称作一存储单元串行。第一导电层530可作为接地选择线, 第二导电层572可作为字线,顶导电层cl5可作为串行选择线。

133.图1g绘示根据本发明的另一实施例的存储器元件600的剖面图,存 储器元件600与存储器100具有类似的俯视图(例如是图1a),故图1f绘 示类似于沿图1的a-a'联机的剖面图。

134.请参照图1g,存储器元件600包括一衬底610、一第一绝缘层622、 一第一导电层630、一第二绝缘层624、一第二导电层672、多个通道结构 612、热氧化层632及go6、一存储层662、一第三绝缘层626、一顶导电 层cl6、一顶绝缘层ol6、多个隔离结构674以及多个导电连接结构676。

135.通道结构612(例如是沿着z轴)穿过叠层结构s6并电性连接于衬底 610。通道结构612的顶部区域可具有一掺杂区612c,例如是n型半导体 的掺杂物,使得通道结构612可电性连接于位线bl。在一些实施例中, 通道结构612可为一外延生长层,例如是经由外延生长工艺所形成的单晶 或多晶硅层或上述的任一组合,可以是未掺杂或轻微p型掺杂的外延生长 层。

136.热氧化层632及go6分别位于第一导电层630与通道结构612之间, 以及顶导电层cl6与通道结构612之间。例如,热氧化层632环绕至少一 部份的通道结构612的下部部分,热氧化层go6环绕至少一部份的通道结 构612的上部部分。在一些实施例中,热氧化层632及go6是直接对通道 结构612进行一氧化工艺所形成的一氧化物,例如是二氧化硅(sio2)。由 于热氧化层632及go6是经由直接氧化通道结构612所形成的氧化物层, 而非是通过沉积工艺(例如是化学气相沉积(cvd)、物理气相沉积(pvd)或 其他沉积工艺)所形成的氧化物层,热氧化层632及go6的氧化物的纯度 是大于沉积法所形成的绝缘层(例如是第一绝缘层622、第二绝缘层624或 第三绝缘层626)的氧化物的纯度。相较于热氧化层是经由沉积工艺所形成 的氧化物层的比较例而言,由于本发明的热氧化层是直接对导电层进行氧 化工艺所形成的氧化物层,热氧化层具有较高的氧化物纯度及质量,可较 佳地控制临界电压(vt),故可在低功率的应用情形中有较低的临界电压, 使存储器元件600可具有较佳的可靠度。

137.存储层662位于第二导电层672与通道结构612之间。举例而言,存 储层662沿着衬底610的上表面610a的法线方向(例如是z轴方向)延伸。 存储层662可以由包含氧化硅(silicon oxide)层、氮化硅(silicon nitride)层和 氧化硅层的复合层(即,ono层)所构成。例如,存储层662可包括隧穿层、 捕捉层及阻挡层。隧穿层可包括二氧化硅(sio2)、二氧化硅(sio2)/氮氧化 硅(sion)所形成的双层结构或其他合适的材料。捕捉层可包括氮化硅、多 晶硅或其他合适的材料。阻挡层可包括二氧化硅(sio2)或其他合适的材料。

138.隔离结构674可穿过叠层结构s6,而将叠层结构s6分隔为多个次叠 层。隔离结构674可由绝缘材料所形成,例如是氧化物或其他合适的材料。 相邻的次叠层中的第二导电层672之间可通过隔离结构674物理性及电性 隔离,因此不同次叠层中的第二导电层672可独立操作,例如是施加不同 的电压。

139.导电连接结构676可穿过叠层结构s6,并例如是透过掺杂区618电性 连接于衬底610。掺杂区618例如是通过n型半导体的掺杂物所掺杂。导 电连接结构676可电性连接于共同源极线。

140.在一些实施例中第一导电层630与热氧化层632之间的每一重叠位置 (intersection)可形成一晶体管t6,顶导电层cl6与热氧化层go6之间的每 一重叠位置可形成一晶体管ts6,第二导电层672与存储层662之间的每 一重叠位置可形成一存储单元m6。晶体管t6、晶体管ts6与存储单元m6通过通道结构612互相串连,并可共同形成一单元存储单元(unit cell)un6,亦可称作一存储单元串行。第一导电层630可作为接地选择线, 第二导电层672可作为字线,顶导电层cl6可作为串行选择线。

141.图1h绘示根据本发明的另一实施例的存储器元件700的剖面图,存 储器元件700与存储器100具有类似的俯视图(例如是图1a),故图1h绘 示类似于沿图1的a-a'联机的剖面图。

142.请参照图1h,存储器元件700包括一衬底710、一第一绝缘层722、 一第一导电层730、一第二绝缘层724、一第二导电层772、多个通道结构 712、氧化物层732'、一存储层762、一第三绝缘层726、一顶导电层cl7、 一顶绝缘层ol7、多个隔离结构774以及多个导电连接结构776。在一些 实施例中,第一绝缘层722、第二绝缘层724、氧化物层732'、第三绝缘 层726及顶绝缘层ol7可由相同的材料所形成。

143.通道结构712(例如是沿着z轴)穿过叠层结构s7并电性连接于衬底 710。通道结构712的顶部区域可具有一掺杂区712c,例如是n型半导体 的掺杂物,使得通道结构712可电性连接于位线bl。在一些实施例中, 通道结构712可为一外延生长层,例如是经由外延生长工艺所形成的单晶 或多晶硅层或上述的任一组合,可以是未掺杂或轻微p型掺杂的外延生长 层。

144.氧化物层732'位于第一导电层730与通道结构712之间,以及顶导 电层cl7与通道结构712之间。

145.存储层762位于第二导电层772与通道结构712之间。举例而言,一 部分的存储层762沿着衬底710的上表面710a的法线方向(例如是z轴方 向)延伸,一部分的存储层762沿着平行于衬底710的上表面710a的方向 延伸。存储层762可以由包含氧化硅(silicon oxide)层、氮化硅(silicon nitride) 层和氧化硅层的复合层所构成。例如,存储层762可包括隧穿层、捕捉层 及阻挡层。隧穿层可包括二氧化硅(sio2)、二氧化硅(sio2)/氮氧化硅(sion) 所形成的双层结构或其他合适的材料。捕捉层可包括氮化硅、多晶硅或其 他合适的材料。阻挡层可包括二氧化硅(sio2)或其他合适的材料。

146.隔离结构774可穿过叠层结构s7,而将叠层结构s7分隔为多个次叠 层。隔离结构774可由绝缘材料所形成,例如是氧化物或其他合适的材料。 相邻的次叠层中的第二导电层772之间可通过隔离结构774物理性及电性 隔离,因此不同次叠层中的第二导电层772可独立操作,例如是施加不同 的电压。

147.导电连接结构776可穿过叠层结构s7,并例如是透过掺杂区718电性 连接于衬底710。掺杂区718例如是通过n型半导体的掺杂物所掺杂。导 电连接结构776可电性连接于共同源极线。

148.在一些实施例中第一导电层730与氧化物层732'之间的每一重叠位 置(intersection)可形成一晶体管t7,顶导电层cl7与氧化物层732'之间 的每一重叠位置可形成一晶体管ts7,第二导电层772与存储层762之间 的每一重叠位置可形成一存储单元m7。晶体管t7、晶体管ts7与存储单 元m7通过通道结构712互相串连,并可共同形成一单元存储单元(unit cell)un7,亦可称作一存储单元串行。第一导电层730可作为接地选择线, 第二导电层772可作为字线,顶导电层cl7可作为串行选择线。

149.图2a至图2n绘示根据本发明的一实施例的存储器元件100的形成 方法的剖面图。

150.请参照图2a,提供一衬底110,并在衬底110的上表面110a上形成 一叠层本体s1',叠层本体s1'包括依序(例如是通过沉积工艺)叠层于衬 底110的上表面110a上的一第一绝缘层122、一第一导电层130、一第二 绝缘层124、一上牺牲层140以及一第三绝缘层126。

151.在一些实施例中,衬底110可为硅衬底或其他合适的衬底。第一绝缘 层122、第二绝缘层124及第三绝缘层126可由氧化物所形成,例如是二 氧化硅。第一导电层130可由导电材料所形成,此导电材料例如是钨(w)、 铝(al)、氮化钛(tin)、氮化钽(tan)、掺杂或未掺杂的多晶硅(poly-silicon) 或其他合适的材料。在一些实施例中,第一导电层130可为n型掺杂的多 晶硅层。上牺牲层140可由氮化硅(sin)所形成。

152.请参照图2b,形成多个第一开口152,每个第一开口152穿过叠层本 体s1'将一部份衬底110暴露于外。在一些实施例中,第一开口152可通 过刻蚀法所形成,例如是干刻蚀法。在一些实施例中,衬底110可受到过 刻蚀(overetched),使第一开口152的底部低于衬底110的上表面110a。

153.请参照图2c,通过一氧化工艺将由第一开口152所暴露出的第一导 电层130的一侧表面形成一部分的氧化物层132',并将由第一开口152 所暴露出的衬底110的表面形成一部分的氧化物层132'。在一些实施例中, 第一导电层130为n型掺杂的多晶硅层,衬底110为硅衬底,经由氧化工 艺及高温,第一开口152所暴露出的第一导电层130的侧表面形成包括二 氧化硅的氧化物层132',并将由第一开口152所暴露出的衬底110的表面 形成包括二氧化硅层的氧化物层132'。

154.请参照图2d,移除第一开口152中的多余的氧化物层132',形成直 接接触于第一导电层130的热氧化层132,并将衬底110暴露出。在一些 实施例中,第一开口152中的多余的氧化物层132'是通过浸泡一溶剂所 移除,该溶剂例如是氢氟酸(hf)。由于热氧化层132是经由直接氧化导电 层(例如是第一导电层130)所形成的氧化物层,而非是通过沉积工艺(例如 是化学气相沉积(cvd)、物理气相沉积(pvd)或其他沉积工艺)所形成的氧 化物层,热氧化层132的氧化物的纯度是大于沉积法所形成的绝缘层(例如 是第一绝缘层122、第二绝缘层124或第三绝缘层126)的氧化物的纯度。

155.请参照图2e,通过一第一外延生长工艺形成覆盖热氧化层132的通 道结构的下部部分112a,热氧化层132位于第一导电层130与通道结构的 下部部分112a之间。亦即,通道结构的下部部分112a为硅的外延生长层。 通道结构的下部部分112a的顶面的高度是大于第一导电层130的顶面的 高度。

156.此后,通过一离子注入将p型的掺杂物注入通道结构的下部部分112a 之中。此p型的掺杂物有助于调整临界电压。

157.请参照图2f,形成覆盖第一开口152的部分侧壁及通道结构的下部部 分112a的一存储层162。存储层162可以由包含氧化硅(silicon oxide)层、 氮化硅(silicon nitride)层和氧化硅层的复合层(即,ono层)所构成。例如, 存储层162可包括隧穿层、捕捉层及阻挡层。隧穿层可包括二氧化硅 (sio2)、二氧化硅(sio2)/氮氧化硅(sion)所形成的双层结构或其他合适的材 料。捕捉层可包括氮化硅、多晶硅或其他合适的材料。阻挡层可包括二氧 化硅(sio2)或其他合适的材料。

158.接着,通过一沉积工艺成在存储层162上形成一保护层164。保护层 164可防止存储层162在后续工艺中受到破坏。保护层164例如是氮化硅、 多晶硅或其他合适的材料。

159.请参照图2g,通过一刻蚀工艺移除部分的存储层162及保护层164, 以暴露出通道结构的下部部分112a。刻蚀工艺可为干刻蚀工艺或湿刻蚀工 艺。

160.请参照图2h,通过浸泡一溶剂移除保护层164,使存储层162暴露出。 此溶剂例如是热磷酸(h3po4),然本发明并不限于此,只要是可移除保护层 164但不会破坏存储层162的溶剂即可。

161.请参照图2i,通过一第二外延生长工艺形成通道结构的上部部分 112b,如此一来变形成包括下部部分112a及上部部分112b的通道结构 112。在本实施例中,通道结构112为硅的外延生长层。

162.此后,通过一离子注入在通道结构112的顶部形成一掺杂区112c,掺 杂区112c例如是n型半导体的重掺杂区。掺杂区112c可用于后续工艺中 形成接触结构,以电性连接于位线。

163.请参照图2j,通过一沉积工艺形成覆盖叠层本体s1'的一覆盖层128, 亦即是覆盖层128覆盖第三绝缘层126及通道结构112。

164.此后,通过一刻蚀工艺形成穿过叠层本体s1'的第二开口154。此刻 蚀工艺例如是一干刻蚀工艺。之后,可通过一离子注入在对应于第二开口 154的衬底110上形成掺杂区118。掺杂区118例如是包括重掺杂的n型 半导体。或者,形成掺杂区118的步骤可在移除上牺牲层140之后进行。

165.请参照图2k,通过一刻蚀工艺从第二开口154移除上牺牲层140,以 在上牺牲层140被移除的位置形成上部开口156。此刻蚀工艺可以是一等 向刻蚀(isotropic etching)(例如是湿刻蚀法),且可以是一高选择性刻蚀,例 如是选择性刻蚀氮化硅而不刻蚀二氧化硅与多晶硅。

166.接着,通过一沉积工艺,形成沿着第二开口154及上部开口156的侧 壁延伸且覆盖覆盖层128的一介电材料166。在一些实施例中,介电材料 166可包括一高介电常数材料(high k material),例如是氧化铝(al2o3)或其 他合适的材料。介电材料166亦可作为阻挡层,以防止电荷侧向扩散(lateral diffusion)。

167.请参照图2l,通过一沉积工艺将导电材料172'填充于第二开口154 及上部开口156之中。导电材料172'可包括钨(w)、铝(al)、氮化钛(tin)、 氮化钽(tan)或其他合适的材料。

168.请参照图2m,通过一刻蚀工艺移除位于第二开口154中的导电材料 172',形成位

于上部开口156之中的第二导电层172。此刻蚀工艺例如是 一干刻蚀工艺。在一些实施例中,刻蚀工艺可一并移除一部份位于上部开 口156中的导电材料。第二导电层172可包括钨(w)、铝(al)、氮化钛(tin)、 氮化钽(tan)或其他合适的导电材料。在本实施例中,第二导电层172包 括钨(w)。从而,便形成包括第一绝缘层122、第一导电层130、第二绝缘 层124、第二导电层172及第三绝缘层126的叠层结构s1。

169.请参照图2n,通过一沉积工艺,将一绝缘材料填充于第二开口154 中,以形成多个隔离结构174。隔离结构174可包括氧化物或其他合适的 绝缘材料。

170.此后,请回头参照图1b,形成穿过隔离结构174并沿着衬底110的 上表面110a的法线方向延伸的多个垂直开口,再通过一沉积工艺填充一 导电材料于这些垂直开口中,以形成多个导电连接结构176。导电连接结 构176可包括钨(w)、铝(al)、氮化钛(tin)或其他合适的导电材料。如此 一来,便形成如图1b所示的存储器元件100。

171.图3a至图3m绘示根据本发明的一实施例的存储器元件200的形成 方法的剖面图。

172.请参照图3a,提供一衬底210,并在衬底210的上表面210a上形成 一叠层本体s2',叠层本体s2'包括依序(例如是通过沉积工艺)叠层于衬 底210的上表面210a上的一第一绝缘层222、一第一导电层230、一第二 绝缘层224、一上牺牲层240以及一第三绝缘层226。

173.在一些实施例中,衬底202可为硅衬底或其他合适的衬底。第一绝缘 层222、第二绝缘层224及第三绝缘层226可由氧化物所形成,例如是二 氧化硅。第一导电层230可由导电材料所形成,此导电材料例如是钨(w)、 铝(al)、氮化钛(tin)、氮化钽(tan)、掺杂或未掺杂的多晶硅(poly-silicon) 或其他合适的材料。在一些实施例中,第一导电层230可为n型掺杂的多 晶硅层。上牺牲层240可由氮化硅(sin)所形成。

174.请参照图3b,形成多个第一开口252,每个第一开口252穿过叠层本 体s2'将一部份衬底210暴露于外。在一些实施例中,第一开口252可通 过刻蚀法所形成,例如是干刻蚀法。在一些实施例中,衬底210可受到过 刻蚀(overetched),使第一开口252的底部低于衬底210的上表面210a。

175.请参照图3c,通过一离子注入将一掺杂物211注入于对应于第一开 口252的衬底210中。掺杂物211例如是p型的掺杂物。掺杂物211有助 于调整临界电压。

176.请参照图3d,通过一氧化工艺将由第一开口252所暴露出的第一导 电层230的一侧表面形成一部分的氧化物层232',并将由第一开口252 所暴露出的衬底210的表面形成一部分的氧化物层232'。在一些实施例 中,第一导电层230为n型掺杂的多晶硅层,衬底210为硅衬底,经由氧 化工艺及高温,第一开口252所暴露出的第一导电层230的侧表面形成包 括二氧化硅的氧化物层232',并将由第一开口252所暴露出的衬底210 的表面形成包括二氧化硅的氧化物层232'。

177.请参照图3e,移除第一开口252中的多余的氧化物层232',形成直 接接触于第一导电层230的热氧化层232,并将衬底210暴露出。在一些 实施例中,第一开口252中的多余的氧化物层232'是通过浸泡一溶剂所 移除,此溶剂例如是氢氟酸(hf)。由于热氧化层232是经由直接氧化导电 层(例如是第一导电层230)所形成的氧化物层,而非是通过沉积工艺(例如 是化学气相沉积(cvd)、物理气相沉积(pvd)或其他沉积工艺)所形成的氧 化物层,热氧化层232的氧化物的纯度是大于沉积法所形成的绝缘层(例如 是第一绝缘层222、第二绝缘层224或第三绝缘层226)的氧化物的纯度。

178.请参照图3f,通过同一道第一外延生长工艺形成通道结构212的下部 部分212a以及上部部分212b。通道结构212的下部部分212a对应于第一 导电层230。通道结构212的上部部分212b对应于上牺牲层240。通道结 构212的下部部分212a覆盖热氧化层232,热氧化层232位于第一导电层 230与通道结构212的下部部分212a之间。在本实施例中,通道结构212 的整体为硅的外延生长层。

179.此后,通过一离子注入在通道结构212的顶面形成一掺杂区212c。掺 杂区212c例如是n型半导体的重掺杂区。掺杂区212c可用于后续工艺中 形成接触结构,以电性连接于位线。

180.请参照图3g,通过一沉积工艺形成覆盖叠层本体s2'的一覆盖层228, 亦即是覆盖层228覆盖第三绝缘层226及通道结构212。在本实施例中, 可通过一热工艺,使掺杂物211扩散至通道层212的下部部分212a。热工 艺可活化掺杂物211。

181.请参照图3h,通过一刻蚀工艺形成穿过叠层本体s2'的第二开口254。 此刻蚀工艺例如是一干刻蚀工艺。之后,可透过第二开口254在衬底210 上形成掺杂区218。掺杂区218例如是包括重掺杂的n型半导体。或者, 形成掺杂区218的步骤可在移除上牺牲层240之后进行。

182.请参照图3i,通过一刻蚀工艺从第二开口254移除上牺牲层240,以 在上牺牲层240被移除的位置形成上部开口256。此刻蚀工艺可以是一等 向刻蚀(isotropic etching)(例如是湿刻蚀法),且可以是一高选择性刻蚀,例 如是选择性刻蚀氮化硅(sin)而不刻蚀二氧化硅(sio2)。

183.接着,通过沉积工艺,依序形成沿着第二开口254的侧壁、上部开口 256的侧壁、通道结构212的部分侧壁延伸并且覆盖覆盖层128的一存储 层262与一介电材料266。存储层262可以由包含氧化硅(silicon oxide)层、 氮化硅(silicon nitride)层和氧化硅层的复合层(即,ono层)所构成。例如, 存储层162可包括隧穿层、捕捉层及阻挡层。隧穿层可包括二氧化硅 (sio2)、二氧化硅(sio2)/氮氧化硅(sion)所形成的双层结构或其他合适的材 料。捕捉层可包括氮化硅、多晶硅或其他合适的材料。阻挡层可包括二氧 化硅(sio2)或其他合适的材料。在一些实施例中,介电材料266可包括一 高介电常数材料(high k material),例如是氧化铝(al2o3)或其他合适的材 料。介电材料166亦可作为阻挡层,以防止电荷侧向扩散(lateral diffusion)。

184.请参照图3j,通过一沉积工艺将导电材料272'填充于第二开口254 及上部开口256之中。导电材料272'可包括是钨(w)、铝(al)、氮化钛(tin)、 氮化钽(tan)或其他合适的材料。

185.请参照图3k,通过一刻蚀工艺移除位于第二开口254中的导电材料 272',形成位于上部开口256之中的第二导电层272。此刻蚀工艺例如是 一干刻蚀工艺。在一些实施例中,刻蚀工艺可一并移除一部份位于上部开 口256中的导电材料。第二导电层272可包括钨(w)、铝(al)、氮化钛(tin)、 氮化钽(tan)或其他合适的导电材料。在本实施例中,第二导电层272包 括钨(w)。从而,便形成包括第一绝缘层222、第一导电层230、第二绝缘 层224、第二导电层272及第三绝缘层226的叠层结构s2。

186.请参照图3l,通过一沉积工艺,将一绝缘材料填充于第二开口254 中,以形成多个隔离结构274。隔离结构274可包括氧化物或其他合适的 绝缘材料。

187.请参照图3m,形成穿过隔离结构274并沿着衬底210的上表面210a 的法线方向延伸的多个垂直开口259。

188.此后,请回头参照图1c,通过一沉积工艺填充一导电材料于这些垂 直开口259中,以形成多个导电连接结构276。导电连接结构276可包括 钨(w)、铝(al)、氮化钛(tin)或其他合适的导电材料。如此一来,便形成 如图1c所示的存储器元件200。

189.图4a至图4l绘示根据本发明的一实施例的存储器元件300的形成方 法的剖面图。

190.请参照图4a,提供一衬底310,并在衬底310的上表面310a上形成 一叠层本体s3',叠层本体s3'包括依序(例如是通过沉积工艺)叠层于衬 底310的上表面310a上的一第一绝缘层322、一下牺牲层342、一第二绝 缘层324、一上牺牲层340以及一第三绝缘层326。

191.在一些实施例中,衬底310可为硅衬底或其他合适的衬底。第一绝缘 层322、第二绝缘层324及第三绝缘层326可由氧化物所形成,例如是二 氧化硅。下牺牲层342及上牺牲层340可由氮化硅(sin)所形成。

192.请参照图4b,形成多个第一开口352,每个第一开口352穿过叠层本 体s3'将一部份衬底310暴露于外。在一些实施例中,第一开口352可通 过刻蚀工艺所形成,例如是干刻蚀工艺。在一些实施例中,衬底310可受 到过刻蚀(overetch),使第一开口352的底部低于衬底310的上表面310a。

193.请参照图4c,通过一第一外延生长工艺形成通道结构的下部部分 312a。亦即,通道结构的下部部分312a为硅的外延生长层。通道结构的 下部部分312a的顶面的高度是大于下牺牲层342的顶面的高度。

194.此后,通过一离子注入将p型的掺杂物注入通道结构的下部部分312a 之中。此p型的掺杂物有助于调整临界电压。

195.请参照图4d,形成覆盖第一开口352的部分侧壁及通道结构的下部 部分312a的一存储层362。存储层362可以由包含氧化硅(silicon oxide) 层、氮化硅(silicon nitride)层和氧化硅层的复合层(即,ono层)所构成。例 如,存储层362可包括隧穿层、捕捉层及阻挡层。隧穿层可包括二氧化硅 (sio2)、二氧化硅(sio2)/氮氧化硅(sion)所形成的双层结构或其他合适的材 料。捕捉层可包括氮化硅、多晶硅或其他合适的材料。阻挡层可包括二氧 化硅(sio2)或其他合适的材料。

196.接着,通过一沉积制成在存储层362上形成一保护层364。保护层364 可防止存储层362在后续工艺中受到破坏。保护层364例如是氮化硅、多 晶硅或其他合适的材料。

197.请参照图4e,通过一刻蚀工艺移除部分的存储层362及保护层364, 以暴露出通道结构的下部部分312a。刻蚀工艺可为干刻蚀工艺或湿刻蚀工 艺。

198.请参照图4f,通过浸泡一溶剂移除保护层364,使存储层362暴露出。 此溶剂例如是热磷酸(h3po4),然本发明并不限于此,只要是可移除保护层 364但不会破坏存储层362的溶剂即可。

199.请参照图4g,通过一第二外延生长工艺形成通道结构的上部部分 312b,如此一来变形成包括下部部分312a及上部部分312b的通道结构 312。在本实施例中,通道结构312为硅的外延生长层。

200.此后,通过一离子注入在通道结构312的顶部形成一掺杂区312c,掺 杂区312c例如是n型半导体的重掺杂区。掺杂区312c可用于后续工艺中 形成接触结构,以电性连接于

位线。

201.接着,通过一沉积工艺形成覆盖叠层本体s3'的一覆盖层328,亦即 是覆盖层328覆盖第三绝缘层326及通道结构312。

202.请参照图4h,通过一刻蚀工艺形成穿过叠层本体s3'的第二开口354。 此刻蚀工艺例如是一干刻蚀工艺。之后,可通过一离子注入在对应于第二 开口354的衬底310上形成掺杂区318。掺杂区318例如是包括重掺杂的 n型半导体。或者,形成掺杂区318的步骤可在移除上牺牲层340与下牺 牲层342之后进行。

203.请参照图4i,通过一刻蚀工艺从第二开口354移除上牺牲层340与下 牺牲层342,以分别在上牺牲层340与下牺牲层342被移除的位置形成上 部开口356及下部开口358。此刻蚀工艺可以是一等向刻蚀(isotropic etching)(例如是湿刻蚀法),且可以是一高选择性刻蚀,例如是选择性刻蚀 氮化硅而不刻蚀二氧化硅。

204.接着,通过一氧化工艺将由下部开口358所暴露出的通道结构312的 一侧表面形成热氧化层332。在一些实施例中,通道结构312为硅的外延 生长层,经由氧化工艺及高温,下部开口358所暴露出的通道结构312的 侧表面形成包括二氧化硅的热氧化层332。

205.此后,通过一沉积工艺,形成沿着第二开口354、下部开口358及上 部开口356的侧壁延伸且覆盖覆盖层328的一介电材料366。在一些实施 例中,介电材料366可包括一高介电常数材料(high k material),例如是氧 化铝(al2o3)或其他合适的材料。介电材料366亦可作为阻挡层,以防止电 荷侧向扩散(lateral diffusion)。

206.请参照图4j,通过一沉积工艺将导电材料372'填充于第二开口354、 下部开口358及上部开口356之中。导电材料372'可包括是钨(w)、铝(al)、 氮化钛(tin)、氮化钽(tan)或其他合适的材料。

207.请参照图4k,通过一刻蚀工艺移除位于第二开口354中的导电材料 372',形成位于下部开口358之中的第一导电层330以及位于上部开口356 之中的第二导电层372。此刻蚀工艺例如是一干刻蚀工艺。在一些实施例 中,刻蚀工艺可一并移除一部份位于上部开口356与下部开口358中的导 电材料372'。第一导电层330以及第二导电层372可分别包括钨(w)、 铝(al)、氮化钛(tin)、氮化钽(tan)或其他合适的导电材料。在本实施例中, 第一导电层330及第二导电层372可包括相同的导电材料,例如是钨(w)。 从而,便形成包括第一绝缘层322、第一导电层330、第二绝缘层324、第 二导电层372及第三绝缘层326的叠层结构s3。

208.请参照图4l,通过一沉积工艺,将一绝缘材料填充于第二开口354 中,以形成多个隔离结构374。隔离结构374可包括氧化物或其他合适的 绝缘材料。

209.此后,请回头参照图1d,形成穿过隔离结构374并沿着衬底310的 上表面310a的法线方向延伸的多个垂直开口,再通过一沉积工艺填充一 导电材料于这些垂直开口中,以形成多个导电连接结构376。导电连接结 构376可包括钨(w)、铝(al)、氮化钛(tin)或其他合适的导电材料。如此 一来,便形成如图1d所示的存储器元件300。

210.图5绘示根据本发明的一实施例的存储器元件100、200或300的等 效电路图。

211.存储器元件100、200或300可为三维或非门(nor)型存储器元件。在 存储器元件100、200或300的阵列区中示例性绘示3条字线wl0、wl1、 wl2,3条位线bl0、bl1、bl2以及3条接地选择线gsl0、gsl1、gsl2。 然而,本发明并不限于此,字线、位线及接地选择线的数量可

以分别大于 3。每个字线与通道结构的重叠位置形成存储单元m,每个接地选择线与 通道结构的重叠位置形成晶体管t。存储单元m位于晶体管t的上方, 且通道结构串联存储单元m与晶体管t。一个存储单元m与一个晶体管t可共同形成一单元存储单元(unit cell)un。每个晶体管t电性连接于共同 源极线csl。字线(例如是wl0、wl1、wl2)之间可通过隔离结构所电性 隔离。

212.图6a绘示根据本发明的一实施例的通过福勒-诺德汉注入 (fowler-nordheim injection)进行编程操作的存储器元件的等效电路图。

213.请参照图6a,欲对目标单元存储单元un

t

进行编程操作,字线wl0 及接地选择线gsl0为选择,字线wl0施加编程电压vpgm1,接地选择 线gsl0施加0v。字线wl1及接地选择线gsl1为未选择,施加0伏特 (v)。共同源极线施加一共同源极电压v

csl

。位线bl0施加0v。位线bl1 施加抑制电压v

inhibit

。耦接于位线bl1的单元存储单元则被抑制。

214.图6b绘示根据本发明的一实施例的通过通道热电子注入 (channel-hot-electron injection)进行编程操作的存储器元件的等效电路图。

215.请参照图6b,欲对目标单元存储单元un

t

进行编程操作,字线wl0 及接地选择线gsl0为选择。字线wl0施加编程电压vpgm1,接地选择 线gsl0施加编程电压vpgm2。字线wl1及接地选择线gsl1为未选择, 施加0伏特(v)。共同源极线csl施加0v。位线bl0施加漏极编程电压 vdpgm。位线bl1施加0v。编程电压vpgm2可小于编程电压vpgm1。 在一些实施例中,编程电压vpgm1可为5~10v。漏极编程电压vdpgm可 为4~10v。

216.图7a绘示根据本发明的一实施例的通过福勒-诺德汉注入进行擦除操 作的存储器元件的等效电路图。

217.请参照图7a,欲对目标单元存储单元un

t

(例如是包括2个存储单元 与2个晶体管)进行擦除操作,字线wl0及接地选择线gsl0为选择。字 线wl0施加0v。接地选择线gsl0施加擦除电压vers2。字线wl1及 接地选择线gsl1为未选择,皆为浮接(floating)(亦即是没有施加电压)。共 同源极线施加一共同源极电压v

csl

。p型井(p well)施加一p型井电压 v

pwi

。外围电路施加一擦除电压vers1。位线bl0与bl1为浮接。共同源 极电压v

csl

可相同于擦除电压vers1及p型井电压v

pwi

。

218.图7b绘示根据本发明的一实施例的通过带对带隧穿诱发热空穴 (band-to-band tunneling induced hot hole injection)进行擦除操作的存储器元 件的等效电路图。

219.请参照图7b,欲对目标单元存储单元un

t

进行擦除操作,字线wl0 及接地选择线gsl0为选择。接地选择线gsl0施加0v。字线wl0施加 一接地擦除电压vgers。接地擦除电压vgers可小于0。字线wl1及接地 选择线gsl1为未选择,施加0伏特(v)。位线bl0可施加一漏极擦除电 压vders。漏极擦除电压vders可大于0。位线bl1可施加0v。共同源极 线施加一共同源极电压v

csl

。使用位线偏压(bl bias)(擦除/抑制)(+vders 用于擦除,0v则非用于抑制)施加福勒-诺德汉擦除(fowler-nordheim erase),以进行位线替代性的擦除操作(所有gsl(例如gsl0,gsl1

…

)=0v, csl=+vcsl)。

220.图8绘示根据本发明的一实施例的读取操作的存储器元件的等效电路 图。

221.请参照图8,欲对目标单元存储单元un

t

(例如是包括2个存储单元与 2个晶体管)进行读取操作,字线wl0及接地选择线gsl0为选择。字线 wl0可施加0v。接地选择线gsl0可施加一电源电压v

cc

。字线wl1 及接地选择线gsl1为未选择,施加0伏特(v)。位线bl0与bl1可

施加 一位线读取电压vblr。共同源极线施加一共同源极电压v

csl

。在本发明的 存储器元件中进行读取操作时,所有施加于位线、字线、接地选择线的电 压可等于或小于电源电压v

cc

,故能够降低功耗。

222.图9a至图9r绘示根据本发明的一实施例的存储器元件400的形成 方法的剖面图。

223.请参照图9a,提供一衬底410,并在衬底410的上表面410a上形成 一叠层本体s4',叠层本体s4'包括依序(例如是通过沉积工艺)叠层于衬 底410的上表面410a上的一下牺牲层442、一第二绝缘层424、一上牺牲 层440、一第三绝缘层426、一顶牺牲层sf4以及一顶绝缘层ol4。

224.在一些实施例中,衬底410可为硅衬底或其他合适的衬底。第二绝缘 层424、第三绝缘层426及顶绝缘层ol4可由氧化物所形成,例如是二氧 化硅。下牺牲层442、上牺牲层440及顶牺牲层sf4可由氮化硅(sin)所形 成。

225.请参照图9b,形成多个第一开口452,每个第一开口452穿过叠层本 体s4'将一部份衬底410暴露于外。在一些实施例中,第一开口452可通 过刻蚀工艺所形成,例如是干刻蚀工艺。在一些实施例中,衬底410可受 到过刻蚀(overetch),使第一开口452的底部低于衬底410的上表面410a。

226.请参照图9c,通过同一道第一外延生长工艺形成通道结构412。亦即, 在本实施例中,通道结构412的整体(包括下部部分及上部部分)为硅的外 延生长层。

227.请参照图9d,通过一刻蚀工艺形成穿过顶牺牲层sf4以及顶绝缘层 ol4的多个第一沟道slt1。

228.请参照图9e,透过第一沟道slt1移除顶牺牲层sf4。顶牺牲层sf4 被移除的空间形成一顶部开口460。接着通过一氧化工艺将暴露出的通道 结构412的上部分的一侧表面形成热氧化层go4。在一些实施例中,通道 结构412为p型掺杂的多晶硅外延生长层,经由氧化工艺及高温,暴露出 的通道结构412的侧表面形成包括二氧化硅的热氧化层go4。

229.请参照图9f,通过一沉积工艺在顶部开口460及第一沟道slt1中沉 积一导电材料cl4'。导电材料cl4'可包括钨(w)、铝(al)、氮化钛(tin)、 氮化钽(tan)、掺杂或未掺杂的多晶硅(poly-silicon)或其他合适的材料。

230.请参照图9g,通过一刻蚀工艺移除部分的导电材料cl4',形成一顶 部开口p1,并在第三绝缘层426与顶绝缘层ol4之间形成顶导电层cl4。

231.请参照图9h,通过一沉积工艺,将一绝缘材料填充于顶部开口p1中。

232.请参照图9i,通过一刻蚀工艺,形成穿过顶绝缘层ol4及第三绝缘 层426的第二沟道slt2,接着移除上牺牲层440,形成上部开口456。此 后,通过一沉积工艺,形成沿着第二沟道slt2及上部开口456延伸的存 储层462,存储层462可以由包含氧化铝(al2o3,aluminium oxide)、氧化 硅(silicon oxide)层、氮化硅(silicon nitride)层和氧化硅层的复合层(即, aono层)所构成。

233.请参照图9j,通过一沉积工艺,沉积一导电材料472'于存储层462 上。导电材料472'可包括钨(w)、铝(al)、氮化钛(tin)、氮化钽(tan)或 其他合适的导电材料。亦即,导电材料472'填充于第二沟道slt2及上 部开口456之中。

234.请参照图9k,通过一刻蚀工艺移除部分的导电材料472'及存储层462,形成第三沟道slt3,并留存位在第二绝缘层424与第三绝缘层426 之间的第二导电层472及存储层462。

235.请参照图9l,通过一沉积工艺,将一绝缘材料填充在第三沟道slt3 中。

236.请参照图9m,通过一刻蚀工艺,形成穿过下牺牲层442、第二绝缘 层424、第三绝缘层426及顶绝缘层ol4的第二开口454。此后,通过一 刻蚀工艺从第二开口454移除下牺牲层442,以下牺牲层442被移除的位 置形成下部开口458。

237.请参照图9n,通过一氧化工艺将由下部开口458所暴露出的通道结 构412的一侧表面形成热氧化层432,并将衬底410所暴露出的上表面形 成第一绝缘层422。例如,热氧化层432及第一绝缘层422可分别包括二 氧化硅。

238.请参照图9o,通过一沉积工艺将导电材料430'填充于第二开口454 及下部开口458之中。导电材料430'可包括是多晶硅或其他合适的材料。

239.请参照图9p,通过一刻蚀工艺移除位于第二开口454中的导电材料 430',形成位于下部开口458之中的第一导电层430。在一些实施例中, 刻蚀工艺可一并移除一部份位于下部开口458中的导电材料。第一导电层 2430可包括多晶硅或其他合适的导电材料。从而,便形成包括第一绝缘层 422、第一导电层430、第二绝缘层424、第二导电层472、第三绝缘层426、 顶导电层cl4及顶绝缘层ol4的叠层结构s4。在一些实施例中,可通过 一离子注入在通道结构412的顶部及衬底410的暴露于第二开口454的表 面分别形成掺杂区412c及418,掺杂区412c及418例如是n型半导体的 重掺杂区。掺杂412c及418可用于后续工艺中形成接触结构,以分别电 性连接于位线及共同源极线。

240.请参照图9q,通过一沉积工艺,将一绝缘材料填充于第二开口454 中,以形成多个隔离结构474。隔离结构474可包括氧化物或其他合适的 绝缘材料。

241.请参照图9r,形成穿过隔离结构474并沿着衬底410的上表面410a 的法线方向延伸的多个垂直开口459。

242.此后,请回头参照图1e,通过一沉积工艺填充一导电材料于这些垂 直开口459中,以形成多个导电连接结构476。导电连接结构476可包括 钨(w)、铝(al)、氮化钛(tin)或其他合适的导电材料。如此一来,便形成 如图1e所示的存储器元件400。

243.图10a至图10k绘示根据本发明的一实施例的存储器元件500的形 成方法的剖面图。

244.请参照图10a,提供一衬底510,并在衬底510的上表面510a上形成 一叠层本体s5',叠层本体s5'包括依序(例如是通过沉积工艺)叠层于衬 底510的上表面510a上的一第一绝缘层522、一第一导电层530、一第二 绝缘层524、一上牺牲层540、一第三绝缘层526、一顶导电层cl5以及 一顶绝缘层ol5。

245.在一些实施例中,衬底510可为硅衬底或其他合适的衬底。一第一绝 缘层522、第二绝缘层524、第三绝缘层526及顶绝缘层ol5可由氧化物 所形成,例如是二氧化硅。上牺牲层540可由氮化硅(sin)所形成。

246.请参照图10b,形成多个第一开口552,每个第一开口552穿过叠层 本体s5'将一部份衬底510暴露于外。在一些实施例中,第一开口552 可通过刻蚀工艺所形成,例如是干刻蚀工艺。在一些实施例中,衬底510 可受到过刻蚀(overetch),使第一开口552的底部低于衬底510的上表面 510a。

247.请参照图10c,通过一氧化工艺将由第一开口552所暴露出的第一导 电层530的一侧表面形成一部分的氧化物层532',并将由第一开口552 所暴露出的衬底510的表面形成

一部分的氧化物层532',以及将顶导电层 cl5的一侧表面形成一氧化物层go5。在一些实施例中,第一导电层530 及顶导电层cl5分别为n型掺杂的多晶硅层,衬底510为硅衬底,经由氧 化工艺及高温,第一开口552所暴露出的第一导电层530的侧表面形成包 括二氧化硅的氧化物层532',并将由第一开口552所暴露出的衬底510 的表面形成包括二氧化硅层的氧化物层532'。

248.请参照图10d,移除第一开口552中的多余的氧化物层532',形成直 接接触于第一导电层530的热氧化层532,并将衬底510暴露出。由于热 氧化层532是经由直接氧化导电层(例如是第一导电层530)所形成的氧化 物层,而非是通过沉积工艺(例如是化学气相沉积(cvd)、物理气相沉积(pvd)或其他沉积工艺)所形成的氧化物层,热氧化层532的氧化物的纯度 是大于沉积法所形成的绝缘层(例如是第一绝缘层522、第二绝缘层524或 第三绝缘层526)的氧化物的纯度。在一些实施例中,通过一离子注入将p 型的掺杂物注入衬底510之中。此p型的掺杂物有助于调整临界电压。

249.请参照图10e,通过一第一外延生长工艺形成覆盖热氧化层532及 go5的通道结构512,热氧化层532位于第一导电层530与通道结构512 之间,热氧化层go5位于顶导电层cl5与通道结构512之间。

250.请参照图10f,通过一刻蚀工艺形成穿过第一绝缘层522、第一导电 层530、第二绝缘层524、上牺牲层540、第三绝缘层526、顶导电层cl5 及顶绝缘层ol5的第二开口554。接着,移除上牺牲层540,以在上牺牲 层540被移除的位置形成上部开口556。接着,通过一离子注入在通道结 构512的顶部及衬底510的暴露于第二开口554的表面分别形成掺杂区 512c及518,掺杂区512c及518例如是n型半导体的重掺杂区。掺杂512c 及518可用于后续工艺中形成接触结构,以分别电性连接于位线及共同源 极线。

251.请参照图10g,通过一沉积工艺,依序形成沿着第二开口554及上部 开口556的侧壁延伸且覆盖顶绝缘层ol5的一存储层562及一介电材料 566。存储层562可以由包含氧化硅(silicon oxide)层、氮化硅(silicon nitride) 层和氧化硅层的复合层(即,ono层)所构成。例如,存储层562可包括隧 穿层、捕捉层及阻挡层。隧穿层可包括二氧化硅(sio2)、二氧化硅(sio2)/ 氮氧化硅(sion)所形成的双层结构或其他合适的材料。捕捉层可包括氮化 硅、多晶硅或其他合适的材料。阻挡层可包括二氧化硅(sio2)或其他合适 的材料。在一些实施例中,介电材料566可包括一高介电常数材料(high k material),例如是氧化铝(al2o3)或其他合适的材料。介电材料566亦可作 为阻挡层,以防止电荷侧向扩散(lateral diffusion)。

252.请参照图10h,通过一沉积工艺将导电材料572'填充于第二开口554 及上部开口556之中。导电材料572'可包括钨(w)、铝(al)、氮化钛(tin)、 氮化钽(tan)或其他合适的材料。

253.请参照图10i,通过一刻蚀工艺移除位于第二开口554中的导电材料 572',形成位于上部开口556之中的第二导电层572。此刻蚀工艺例如是 一干刻蚀工艺。在一些实施例中,刻蚀工艺可一并移除一部份位于上部开 口556中的导电材料。第二导电层572可包括钨(w)、铝(al)、氮化钛(tin)、 氮化钽(tan)或其他合适的导电材料。在本实施例中,第二导电层572包 括钨(w)。从而,便形成包括第一绝缘层522、第一导电层530、第二绝缘 层524、第二导电层572、第三绝缘层526、顶导电层cl5及顶绝缘层ol5 的叠层结构s5。

254.请参照图10j,通过一沉积工艺,将一绝缘材料填充于第二开口554 中,以形成多个隔离结构574。隔离结构574可包括氧化物或其他合适的 绝缘材料。

255.请参照图10k,形成穿过隔离结构574并沿着衬底510的上表面510a 的法线方向延伸的多个垂直开口559。

256.此后,请回头参照图1f,通过一沉积工艺填充一导电材料于这些垂直 开口559中,以形成多个导电连接结构576。导电连接结构576可包括钨 (w)、铝(al)、氮化钛(tin)或其他合适的导电材料。如此一来,便形成如 图1f所示的存储器元件500。

257.图11a至图11m绘示根据本发明的一实施例的存储器元件600的形 成方法的剖面图。

258.请参照图11a,提供一衬底610,并在衬底610的上表面610a上形成 一叠层本体s6',叠层本体s6'包括依序(例如是通过沉积工艺)叠层于衬 底610的上表面610a上的一下牺牲层642、一第二绝缘层624、一上牺牲 层640、一第三绝缘层626、一顶牺牲层sf6以及一顶绝缘层ol6。

259.在一些实施例中,衬底610可为硅衬底或其他合适的衬底。第二绝缘 层624、第三绝缘层626及顶绝缘层ol6可由氧化物所形成,例如是二氧 化硅。下牺牲层642、上牺牲层640及顶牺牲sf6可由氮化硅(sin)所形成。

260.请参照图11b,形成多个第一开口652,每个第一开口652穿过叠层 本体s6'将一部份衬底610暴露于外。在一些实施例中,第一开口652 可通过刻蚀工艺所形成,例如是干刻蚀工艺。在一些实施例中,衬底610 可受到过刻蚀(overetch),使第一开口652的底部低于衬底610的上表面 610a。

261.请参照图11c,通过一第一外延生长工艺形成通道结构的下部部分612a。亦即,通道结构的下部部分612a为硅的外延生长层。通道结构的 下部部分612a的顶面的高度是大于下牺牲层642的顶面的高度。

262.此后,通过一离子注入将p型的掺杂物注入通道结构的下部部分612a 之中。此p型的掺杂物有助于调整临界电压。

263.请参照图11d,形成覆盖第一开口652的部分侧壁及通道结构的下部 部分612a的一存储层662。存储层662可以由包含氧化硅(silicon oxide) 层、氮化硅(silicon nitride)层和氧化硅层的复合层(即,ono层)所构成。例 如,存储层662可包括隧穿层、捕捉层及阻挡层。隧穿层可包括二氧化硅 (sio2)、二氧化硅(sio2)/氮氧化硅(sion)所形成的双层结构或其他合适的材 料。捕捉层可包括氮化硅、多晶硅或其他合适的材料。阻挡层可包括二氧 化硅(sio2)或其他合适的材料。

264.接着,通过一沉积制成在存储层662上形成一保护层664。保护层664 可防止存储层662在后续工艺中受到破坏。保护层664例如是氮化硅、多 晶硅或其他合适的材料。

265.请参照图11e,通过一刻蚀工艺移除部分的存储层662及保护层664, 以暴露出通道结构的下部部分612a。刻蚀工艺可为干刻蚀工艺或湿刻蚀工 艺。

266.请参照图11f,通过浸泡一溶剂移除保护层664,使存储层662暴露 出。此溶剂例如是热磷酸(h3po4),然本发明并不限于此,只要是可移除保 护层664但不会破坏存储层662的溶剂即可。

267.请参照图11g,通过一第二外延生长工艺形成通道结构的上部部分 612b'。

268.请参照图11h,移除部分的上部部分612b'及存储层662,形成穿过 顶绝缘层ol6、顶牺牲层sf6及一部分的第三绝缘层626的垂直开口。此 垂直开口的宽度可大于通道结构的下部部分612a的宽度。接着,通过一 第三外延生长工艺形成通道结构的上部部分612b。

269.请参照图11i,通过一刻蚀工艺形成穿过叠层本体s6'的第二开口654。 此刻蚀工艺例如是一干刻蚀工艺。之后,可通过一离子注入在对应于第二 开口654的衬底610上形成掺杂区618,并在通道结构612的顶部形成一 掺杂区612c。掺杂区612c及618例如是包括重掺杂的n型半导体。或者, 形成掺杂区612c及618的步骤可在移除上牺牲层640与下牺牲层642之 后进行。

270.请参照图11j,通过一刻蚀工艺从第二开口654移除顶牺牲层sf6、 上牺牲层640与下牺牲层642,以分别在顶牺牲层sf6、上牺牲层640与 下牺牲层642被移除的位置形成顶部开口660、上部开口656及下部开口 658。此刻蚀工艺可以是一等向刻蚀(isotropic etching)(例如是湿刻蚀法), 且可以是一高选择性刻蚀,例如是选择性刻蚀氮化硅而不刻蚀二氧化硅。

271.接着,通过一氧化工艺将由下部开口658所暴露出的通道结构612的 一侧表面形成热氧化层632,将由下部开口658所暴露出的衬底610的上 表面610a形成第一绝缘层622,并将由顶部开口660所暴露出的通道结构 612的一侧表面形成热氧化层go6。在一些实施例中,通道结构612为硅 的外延生长层,经由氧化工艺及高温,顶部开口660所暴露出的通道结构 612的侧表面及下部开口658所暴露出的通道结构612的侧表面分别形成 包括二氧化硅的热氧化层go6与632。

272.此后,通过一沉积工艺,形成沿着第二开口654、下部开口658、上 部开口656及顶部开口660的侧壁延伸且覆盖顶绝缘层ol6的一介电材料 666。在一些实施例中,介电材料666可包括一高介电常数材料(high k material),例如是氧化铝(al2o3)或其他合适的材料。介电材料666亦可作 为阻挡层,以防止电荷侧向扩散(lateral diffusion)。

273.请参照图11k,通过一沉积工艺将导电材料672'填充于第二开口654、 顶部开口660、下部开口658及上部开口656之中。导电材料672'可包 括是钨(w)、铝(al)、氮化钛(tin)、氮化钽(tan)或其他合适的材料。

274.请参照图11l,通过一刻蚀工艺移除位于第二开口654中的导电材料 672',形成位于下部开口658之中的第一导电层630、位于上部开口656 之中的第二导电层672以及位于顶部开口660之中的顶导电层cl6。此刻 蚀工艺例如是一干刻蚀工艺。在一些实施例中,刻蚀工艺可一并移除一部 份位于顶部开口660、上部开口656与下部开口658中的导电材料672'。 第一导电层630、第二导电层672及顶导电层cl6可分别包括钨(w)、铝 (al)、氮化钛(tin)、氮化钽(tan)或其他合适的导电材料。在本实施例中, 第一导电层630、第二导电层672及顶导电层cl6可包括相同的导电材料, 例如是钨(w)。从而,便形成包括第一绝缘层622、第一导电层630、第二 绝缘层624、第二导电层672、第三绝缘层626、顶导电层cl6及顶绝缘 层ol6的叠层结构s6。

275.请参照图11m,通过一沉积工艺,将一绝缘材料填充于第二开口654 中,以形成多个隔离结构674。隔离结构674可包括氧化物或其他合适的 绝缘材料。

276.此后,请回头参照图1g,形成穿过隔离结构674并沿着衬底610的 上表面610a的法线方向延伸的多个垂直开口,再通过一沉积工艺填充一 导电材料于这些垂直开口中,以形

成多个导电连接结构676。导电连接结 构676可包括钨(w)、铝(al)、氮化钛(tin)或其他合适的导电材料。如此 一来,便形成如图1g所示的存储器元件600。

277.图12a至图12k绘示根据本发明的一实施例的存储器元件700的形 成方法的剖面图。

278.请参照图12a,提供一衬底710,并在衬底710的上表面710a上形成 一叠层本体s7',叠层本体s7'包括依序(例如是通过沉积工艺)叠层于衬 底710的上表面710a上的一第一绝缘层722、一第一导电层730、一第二 绝缘层724、一上牺牲层740、一第三绝缘层726、一顶导电层cl7以及 一顶绝缘层ol7。

279.在一些实施例中,衬底710可为硅衬底或其他合适的衬底。一第一绝 缘层722、第二绝缘层724、第三绝缘层726及顶绝缘层ol7可由氧化物 所形成,例如是二氧化硅。下牺牲层742、上牺牲层740及顶绝缘层ol7 可由氮化硅(sin)所形成。

280.请参照图12b,形成多个第一开口752,每个第一开口752穿过叠层 本体s7'将一部份衬底710暴露于外。在一些实施例中,第一开口752 可通过刻蚀工艺所形成,例如是干刻蚀工艺。在一些实施例中,衬底710 可受到过刻蚀(overetch),使第一开口752的底部低于衬底710的上表面 710a。

281.请参照图12c,通过一沉积工艺在第一开口752的侧壁及底部上形成 氧化物层732'。在一些实施例中,第一绝缘层722、第二绝缘层724、氧 化物层732'、第三绝缘层726及顶绝缘层ol7可由相同的材料所形成。

282.请参照图12d,移除第一开口752中的多余的氧化物层732',并将衬 底510暴露出。在一些实施例中,通过一离子注入将p型的掺杂物注入衬 底710之中。此p型的掺杂物有助于调整临界电压。

283.请参照图12e,通过一第一外延生长工艺形成覆盖氧化物层732'的 通道结构712。

284.请参照图12f,通过一刻蚀工艺形成穿过第一绝缘层722、第一导电 层730、第二绝缘层724、上牺牲层740、第三绝缘层726、顶导电层cl7 及顶绝缘层ol7的第二开口754。接着,移除上牺牲层740,以在上牺牲 层740被移除的位置形成上部开口756。接着,通过一离子注入在通道结 构712的顶部及衬底710的暴露于第二开口754的表面分别形成掺杂区 712c及718,掺杂区712c及718例如是n型半导体的重掺杂区。掺杂712c 及718可用于后续工艺中形成接触结构,以分别电性连接于位线及共同源 极线。

285.请参照图12g,移除对应于上部开口756的氧化物层732'(亦即是移 除氧化物层732'的中间部分),此后通过一沉积工艺,依序形成沿着第二 开口754及上部开口756的侧壁延伸且覆盖顶绝缘层ol7的一存储层762 及一介电材料766。存储层762可以由包含氧化硅(silicon oxide)层、氮化 硅(silicon nitride)层和氧化硅层的复合层(即,ono层)所构成。例如,存储 层762可包括隧穿层、捕捉层及阻挡层。隧穿层可包括二氧化硅(sio2)、 二氧化硅(sio2)/氮氧化硅(sion)所形成的双层结构或其他合适的材料。捕 捉层可包括氮化硅、多晶硅或其他合适的材料。阻挡层可包括二氧化硅 (sio2)或其他合适的材料。在一些实施例中,介电材料766可包括一高介 电常数材料(high k material),例如是氧化铝(al2o3)或其他合适的材料。介 电材料766亦可作为阻挡层,以防止电荷侧向扩散(lateral diffusion)。

286.请参照图12h,通过一沉积工艺将导电材料772'填充于第二开口754 及上部开口

756之中。导电材料772'可包括钨(w)、铝(al)、氮化钛(tin)、 氮化钽(tan)或其他合适的材料。

287.请参照图12i,通过一刻蚀工艺移除位于第二开口754中的导电材料 772',形成位于上部开口756之中的第二导电层772。此刻蚀工艺例如是 一干刻蚀工艺。在一些实施例中,刻蚀工艺可一并移除一部份位于上部开 口756中的导电材料。第二导电层772可包括钨(w)、铝(al)、氮化钛(tin)、 氮化钽(tan)或其他合适的导电材料。在本实施例中,第二导电层772包 括钨(w)。从而,便形成包括第一绝缘层722、第一导电层730、第二绝缘 层724、第二导电层772、第三绝缘层726、顶导电层cl7及顶绝缘层ol7 的叠层结构s7。

288.请参照图12j,通过一沉积工艺,将一绝缘材料填充于第二开口754 中,以形成多个隔离结构774。隔离结构774可包括氧化物或其他合适的 绝缘材料。

289.请参照图12k,形成穿过隔离结构774并沿着衬底710的上表面710a 的法线方向延伸的多个垂直开口759。

290.此后,请回头参照图1h,通过一沉积工艺填充一导电材料于这些垂 直开口759中,以形成多个导电连接结构776。导电连接结构776可包括 钨(w)、铝(al)、氮化钛(tin)或其他合适的导电材料。如此一来,便形成 如图1h所示的存储器元件700。

291.第13~15图绘示根据本发明的一实施例的操作存储器元件400、500、 600或700的等效电路图。

292.存储器元件400、500、600或700可为三维或非门(nor)型存储器元 件。在第13~15图中,存储器元件400、500、600或700的阵列区中示例 性绘示2条串行选择线ssl0、ssl1,2条字线wl0、wl1,2条位线bl0、 bl1以及2条接地选择线gsl0、gsl1。然而,本发明并不限于此,串行 选择线、字线、位线及接地选择线的数量可以分别大于2。每个字线与通 道结构的重叠位置形成存储单元m,每个接地选择线与通道结构的重叠位 置形成晶体管t,每个串行选择线与通道结构的重叠位置形成晶体管ts。 存储单元m位于晶体管t的上方,晶体管ts位于存储单元m的上方, 且通道结构串联晶体管ts、存储单元m与晶体管t。一个晶体管ts、一 个存储单元m与一个晶体管t可共同形成一单元存储单元(unit cell)un。 每个晶体管t电性连接于共同源极线csl。字线(例如是wl0、wl1)的间 可通过隔离结构所电性隔离。

293.图13绘示根据本发明的一实施例的通过福勒-诺德汉注入 (fowler-nordheim injection)进行编程操作的存储器元件的等效电路图。

294.请参照图13,欲对目标单元存储单元un

t

进行编程操作,串行选择线 ssl0、字线wl0及接地选择线gsl0为选择,串行选择线ssl0施加导 通电压vpass,字线wl0施加编程电压vpgm1,接地选择线gsl0施加0 v。串行选择线ssl1、字线wl1及接地选择线gsl1为未选择,施加0 伏特(v)。共同源极线施加一共同源极电压v

csl

。位线bl0施加0v。位 线bl1施加抑制电压v

inhibit

。耦接于位线bl1的单元存储单元则被抑制。 在一实施例中,导通电压vpass大于抑制电压v

inhibit

,以传送抑制电压v

inhibit

至单元存储单元中。在一实施例中,导通电压vpass等于抑制电压v

inhibit

, 用于自我升压(self-boosting),且可减轻编程的干扰。

295.图14a绘示根据本发明的一实施例的通过福勒-诺德汉注入进行擦除 操作的存储器元件的等效电路图。

296.请参照图14a,欲对目标单元存储单元un

t

(例如是包括不同串行的2 个存储单元与4个晶体管)进行擦除操作,串行选择线ssl0、字线wl0 及接地选择线gsl0为选择。串行选

择线ssl0施加擦除电压vers3或为 浮接。字线wl0施加0v。接地选择线gsl0施加擦除电压vers2。串行 选择线ssl1、字线wl1及接地选择线gsl1为未选择,皆为浮接。共同 源极线施加一共同源极电压v

csl

。p型井(p well)施加一p型井电压v

pwi

。 外围电路施加一擦除电压vers1。位线bl0与bl1为浮接。共同源极电压 v

csl

可相同于擦除电压vers1及p型井电压v

pwi

。

297.图14b绘示根据本发明的一实施例的通过带对带隧穿诱发热空穴进 行擦除操作的存储器元件的等效电路图。

298.请参照图14b,欲对目标单元存储单元un

t

进行擦除操作,串行选择 线ssl0、字线wl0及接地选择线gsl0为选择。串行选择线ssl0施加 导通电压vpass。接地选择线gsl0施加0v。字线wl0施加一接地擦除 电压vgers。接地擦除电压vgers可小于0。串行选择线ssl1、字线wl1 及接地选择线gsl1为未选择,施加0伏特(v)。位线bl0可施加一漏极 擦除电压vders。漏极擦除电压vders可大于0。位线bl1可施加0v。共 同源极线施加一共同源极电压v

csl

。

299.图15绘示根据本发明的一实施例的读取操作的存储器元件的等效电 路图。

300.请参照图15,欲对目标单元存储单元un

t

(例如是包括不同存储器串 行的2个存储单元与4个晶体管)进行读取操作,串行选择线ssl0、字线 wl0及接地选择线gsl0为选择。串行选择线ssl0可施加一电源电压 v

cc

。字线wl0可施加0v。接地选择线gsl0可施加一电源电压v

cc

。 串行选择线ssl1、字线wl1及接地选择线gsl1为未选择,施加0伏特 (v)。位线bl0与bl1可施加一位线读取电压vblr。共同源极线施加一共 同源极电压v

csl

。在本发明的存储器元件中进行读取操作时,所有施加于 位线、字线、接地选择线的电压可等于或小于电源电压v

cc

,故能够降低 功耗。

301.本案提供一种存储器元件、及其制备方法和操作方法。由于本案的存 储器元件为三维结构,可应用于或非门存储器元件,相较于一般二维的或 非门存储器元件而言具有更小的单元存储单元的面积。再者,本案的存储 器元件可使用高介电常数材料做为介电材料,可不需要太高的电压即可进 行存储器元件的操作(例如是擦除、写入、编程)。并且,根据本案的一实 施例,通道结构为一外延生长层,相较于通道结构仅部分包括外延生长层 或主要由多晶硅层所形成的比较例而言具有较佳的电特性,使得接地选择 线可获得较佳的控制能力,临界电压可较为小且分布较为集中(tight distribution)。此外,本案的热氧化层是通过直接对于第一导电层或通道结 构进行氧化工艺所形成的氧化物,相较于一般通过沉积法形成的热氧化层 而言,可具有较高的氧化物纯度,故有利于临界电压的调控,可具有较小 的临界电压。因此,本案的存储器元件可具有较低的能耗,具备较佳的可 靠度且效能亦可获得改善。

302.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行 了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而 已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修 改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1