半导体结构及其形成方法、熔丝阵列与流程

1.本发明涉及半导体技术领域,尤其涉及一种半导体结构及其形成方法、一种熔丝阵列。

背景技术:

2.随着半导体工艺水平的改进以及集成电路复杂度的提高,芯片内器件数量不断增加,而单个元器件如晶体管或存储单元的失效,往往会导致整个集成电路的功能失效。

3.例如,采用半导体工艺制造的dram芯片会不可避免的产生缺陷存储的单元,而dram芯片上通常会形成有冗余存储单元,利用冗余存储单元去永久替换缺陷存储单元,即可修复dram芯片。常见的方法是在集成电路中形成一些可以熔断的连接线,也就是熔丝(fuse)结构,在芯片生产完成时,若其中有部分存储单元或电路出现功能问题,就可以通过选择性地熔断(或破坏)与缺陷电路相关的熔丝结构,同时激活冗余的存储单元以形成新的电路来替换,实现修复的目的。

4.激光熔丝是一种常用的熔丝结构,通过激光束熔断熔丝,使得电路结构发生变化。现有技术中的激光熔丝结构,在后续的熔丝熔断工艺中需要较大的能量,造成工艺参数难以控制以及能量过大会损伤熔丝结构周围的器件。

5.如何降低熔丝熔断能量,是目前亟待解决的问题。

技术实现要素:

6.本发明所要解决的技术问题是,提供一种半导体结构及其形成方法、一种熔丝阵列,降低熔断时所需的激光能量。

7.为了解决上述问题,本发明提供了一种半导体结构,包括:至少两个第一通孔,位于衬底上方;第一导电层,位于所述第一通孔上方,与所述第一通孔电连接;至少两个第二通孔,位于所述第一导电层上方;第二导电层,位于所述第二通孔上方,通过所述第二通孔与所述第一导电层电连接;其中,所述第一通孔与所述第二导电层在所述衬底上的投影均不重叠。

8.可选的,还包括:保护层,覆盖所述第二导电层;熔丝开窗区,位于所述保护层上方,所述第二通孔、所述第二导电层均位于所述熔丝开窗区内。可选的,所述熔丝开窗区为一凹槽,所述凹槽的底部为所述保护层的一部分。

9.可选的,所述第二导电层沿着x方向布置,所述第一导电层沿着y方向布置,所述x方向和所述y方向垂直。

10.可选的,所述第一通孔包括接触孔、金属层与金属层之间通孔中的一种。

11.可选的,所述第二导电层包括第n层金属层、第n-1层金属层、第n-2层金属层、第二层金属层中的一种,所述n为大于等于5的正整数。

12.可选的,所述第一导电层与所述第二导电层具有不同的导电率。

13.可选的,所述第一导电层包括多晶硅、钨金属、铝金属、铜金属中的一种或多种,所

述第二导电层包括钨金属、铝金属、铜金属中的一种或多种。

14.本发明的技术方案还提供一种熔丝阵列,包括上述任一项所述半导体结构,多个所述半导体结构以m行、n列的阵列布置,所述m和n均为正偶数。

15.本发明的技术方案还提供一种半导体结构的形成方法,包括:在衬底上方形成至少两个第一通孔;在所述第一通孔上方形成第一导电层,所述第一导电层与所述第一通孔电连接;在所述第一导电层上方形成至少两个第二通孔;在所述第二通孔上方形成第二导电层,通过所述第二通孔与所述第一导电层电连接;其中,所述第一通孔与所述第二导电层在所述衬底上的投影均不重叠。

16.可选的,还包括:在所述第二导电层上方形成一保护层;在所述保护层上方形成一凹槽,作为熔丝开窗区,所述第二通孔、所述第二导电层均位于所述熔丝开窗区内。

17.本发明的半导体结构中,第一通孔与第二半导体层在衬底上的投影无重叠,在对第二半导体层进行熔断时,只需要对第二半导体层及其下方的第二通孔进行熔断即可,可以降低熔断能量,熔断过程更易控制。

附图说明

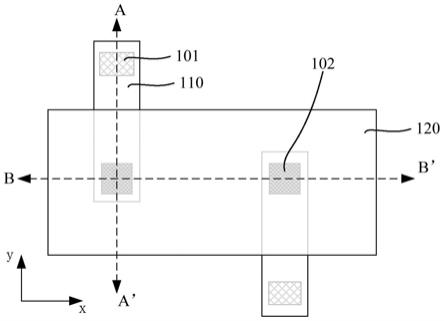

18.图1a至图1c为本发明一具体实施方式的半导体结构的结构示意图;

19.图2a至图2c为本发明一具体实施方式的半导体结构的结构示意图;

20.图3a至图6b为本发明一具体实施方式的半导体结构的形成过程的结构示意图;

21.图7为本发明一具体实施方式的熔丝阵列的结构示意图;

22.图8为本发明一具体实施方式的熔丝阵列上方形成有熔丝开窗区的俯视示意图。

具体实施方式

23.如背景技术中所述,目前的熔丝熔断工艺中需要较大的能量。在对熔丝进行激光熔断过程中,如果仅仅是将熔丝熔断,熔断过程中产生的金属飞溅或设高温导致的金属扩散迁移,依然有可能使得熔丝连接的两个导电通路之间发生短路。尤其是,现在的集成电路工艺中,越来越多的采用多孔介电材料,作为各金属层间的介质层材料。为了能够使得所述激光熔丝连接的两个导电通路之间彻底断开,通常需要会将整个导电通路进行垂直熔断,将熔丝及其下方的导电通路上的金属均进行激光融断,从而使得金属在高温下彻底被汽化排出。

24.为了解决上述问题,发明人提出一种新的半导体结构及其形成方法,以及一种形成的熔丝阵列。

25.下面结合附图对本发明提供的半导体结构及其形成方法、一种熔丝阵列的具体实施方式做详细说明。

26.请参考图1a至图1c,为本发明一具体实施方式的半导体结构的结构示意图。图1b为沿图1a中a-a’线的剖面示意图,图1c为沿图1a中b-b’线的剖面示意图。

27.所述半导体结构包括:至少两个第一通孔101,位于衬底上方;第一导电层110,位于所述第一通孔101上方,与所述第一通孔101电连接;至少两个第二通孔102,位于所述第一导电层110上方;第二导电层120,位于所述第二通孔102上方,通过所述第二通孔102与所述第一导电层110电连接;其中,所述第一通孔101与所述第二导电层120在所述衬底上的投

影均不重叠。

28.所述第一通孔101、第二通孔102、第一导电层110以及第二导电层120均形成于介质层(图中未示出)。

29.该具体实施方式中,以两个第一通孔101作为示例。所述第一导电层110为倒装状金属块,该具体实施方式中,以两个第一导电层110作为示例。所述第一导电层110与其下方的第一通孔101及其上方的第二通孔102构成导电通路。该具体实施方式中,两个所述第一通孔101、两个所述第一导电层110构成两条导电通路。所述第二导电层120通过所述第二通孔102连接至所述两条导电通路,使得两条所述导电通路之间形成电连接。

30.该具体实施方式中,所述第二导电层120为第二层金属层,所述第一导电层110为第一层金属层。相应的,所述第一通孔101为连接至衬底或晶体管的接触孔,所述第二通孔102为金属层与金属层之间的连接通孔。

31.在其他具体实施方式中,所述第二导电层120还可以为第n层金属层、第n-1层金属层、第n-2层金属层中的一种,所述n为大于等于5的正整数;所述第一导电层110为所述第二导电层120内下一层的金属层。所述第一导电层110下方还形成有其他层的金属层。所述第二通孔102为金属层与金属层之间的连接通孔,所述第一通孔101也为金属层与金属层之间的连接通孔。

32.所述第一导电层110的材料包括多晶硅、钨金属、铝金属、铜金属中的一种或多种;所述第二导电层120的材料包括钨金属、铝金属、铜金属中的一种或多种。所述第一导电层110与所述第二导电层120的材料可以相同,也可以不同,本领域技术人员,可以根据所述第一导电层110和所述第二导电层120的实际位置选择合适的导电材料。由于所述第二导电层120位于上方,长度较大,需要选择具有更小电阻率的材料,以减少电阻。在一个具体实施方式中,所述第一导电层110的材料为铝,所述第二导电层120的材料为铜。在其他具体实施方式中,所述第一导电层110和所述第二导电层120的材料均为铜。

33.可以根据所述第一通孔101和所述第二通孔102的位置选择合适的通孔材料。在一个具体实施方式中,所述第一通孔101为连接至晶体管的接触通孔,材料为钨,所述第二通孔102为金属层间连接通孔,材料为铜。在另一具体实施方式中,所述第一通孔101和所述第二通孔102的材料相同,均为铜或其他金属。

34.由于所述第一通孔101和所述第二导电层120在衬底上的投影不重叠,所述第一通孔101的投影位于所述第二导电层120的外侧。所以在对第二导电层120进行熔断的过程中,第二导电层120及其正下方的第二通孔102以及部分第一导电层110被熔断后,熔断的金属材料与所述第一通孔101之间的距离较大,不易与所述第一通孔101之间造成短路。从而,在对所述第二导电层120进行熔断时,只需要对所述第二导电层120及其投影面内的第二通孔102进行熔断。进一步可以对第二通孔102下方的部分第一导电层110进行熔断,即仅需要对图1b中虚线框内的导电结构进行熔断,以确保导电通路之间能够被彻底断开。无需对下方的整条导电通路上的导电材料全部进行熔断,从而避免了在熔断时使用过大的激光能量,进而避免了对熔丝结构周围的器件造成损伤。可以根据版图空间等合理设计所述第一通孔101与所述第二导电层120之间的水平距离。所述水平距离可以为0.5微米~10微米,但考虑到不同制造厂商和不同制程的差异,上述水平距离的具体值不应理解为一种对本发明的半导体结构的限制,本领域技术人员在此基础上可以进行合理的调整。

35.进一步的,当所述第一导电层为第二层或更上层的金属层时,所述第一通孔101下方连接的导电通路上的导电层及各层间通孔在衬底上的投影也不重叠,使得导电通孔始终位于其上方连接的导电层的投影外侧,进而避免对第二导电层进行熔断过程中,与第一通孔下方的导电层或连接通孔之间造成短路。

36.该具体实施方式中,所述第二导电层120沿着x方向布置,所述第一导电层110沿着y方向布置,即所述第二导电层120的长度方向沿x方向,所述第一导电层110的长度方向沿y方向。所述x方向和所述y方向垂直,以尽量提高所述第一通孔101与所述第二导电层120之间的距离最大。该具体实施方式中,两个所述第一通孔110在衬底上的投影分别位于所述第二导电层120在衬底上投影的两侧,提高两个所述第一通孔110分别所在的两个导电通路之间的距离,避免在对第二导电层120进行熔断的过程中,所述两个导电通路之间由于熔断金属的飞溅或扩散等造成短路问题。

37.请参考图2a至图2c,为本发明另一具体实施方式的半导体结构的结构示意图。图2b为沿图2a中a-a’线的剖面示意图,图2c为沿图2a中b-b’线的剖面示意图。

38.该具体实施方式中,所述第二导电层220与每个第一导电层210之间通过多个第二通孔202连接,相应的所述第一导电层210与所述第二导电层220之间的重叠面积也更大,有利于在对第二导电层220进行熔断时,同时对其投影下方的第一导电层210也进行熔断,以减少激光熔断时,激光光束的对准难度。

39.在本发明的其他具体实施方式中,所述半导体结构还包括保护层和所述熔丝开窗区,所述保护层覆盖所述导电层,所述熔丝开窗区,位于所述保护层上方,所述第二通孔、所述第二导电层均位于所述熔丝开窗区内。当不需要对所述第二导电层进行熔断时,所述保护层能够保护所述第二导电层,当需要对所述第二导电层进行熔断时,直接通过所述熔丝开窗区对所述第二导电层及其下方的第二通孔以及部分第一导电层进行熔断。

40.进一步的,所述熔丝开窗区为一凹槽,所述凹槽的底部为所述保护层的一部分。

41.本发明的技术方案,还提供一种上述半导体结构的形成方法。

42.请参考图3a至图6b为本发明一具体实施方式的半导体结构的形成方法。

43.请参考图3a至图3b,提供衬底(图中未示出),在所述衬底上方形成有第一介质层310,在所述第一介质层310内形成至少两个第一通孔301。图3b为沿图3a中c-c’线的剖面示意图。

44.形成所述第一通孔301的方法包括:刻蚀所述第一介质层310至下层导体,形成通孔,在所述通孔内填充导电材料,并进行平坦化,形成所述第一通孔301。该具体实施方式中,以形成两个所述第一通孔301作为示例。

45.请参考图4a至图4c,在所述第一介质层310上形成第二介质层320,以及位于所述第二介质层320内的第一导电层321,所述第一导电层321连接至所述第一通孔301。图4b为沿图4a中c-c’线的剖面示意图,图4c为沿图4a中d-d’线的剖面示意图。

46.所述第一导电层321形成方法,包括刻蚀所述第二介质层320形成凹槽后,在所述凹槽内填充导电材料,形成所述第一导电层321。在其他具体实施方式中,也可以通过形成覆盖所述第一介质层310的导电材料层后,对所述导电材料层进行图形化而形成所述第一导电层321,然后再在所述第一导电层321上形成介质材料,并进行平坦化处理,形成表面与所述第一导电层321表面齐平第二介质层320。所述第一导电层321的横截面可以为矩形、圆

形、多边形等平面图形。

47.请参考图5a至图5c,在所述第二介质层320表面形成阻挡层3301以及覆盖所述阻挡层3301的第三介质层330;在所述第三介质层330内形成第二通孔302以及位于所述第二通孔302的第二导电层322。图5b为沿图5a中c-c’线的剖面示意图,图5c为沿图5a中d-d’线的剖面示意图。

48.所述第二通孔302底部贯穿所述阻挡层3301,位于所述第一导电层321表面,连接所述第一导电层321和所述第二导电层322,所述第二导电层322通过所述第二通孔302连接两个第一导电层321,使得两个所述第一导电层321所在的两个导电通路之间连接。通过激光熔断所述第二导电层322即可断开所述两个导电通路。

49.所述第二导电层322和所述第二通孔302可以通过双大马士革工艺形成,具体的,在所述第三介质层330内形成通孔及位于所述通孔上方的凹槽,然后填充在所述通孔和凹槽内填充导电材料并进行平坦化,在通孔内形成所述第二通孔302,在所述凹槽内形成第二导电层322。

50.在其他具体实施方式中,还可以分别形成所述第二通孔302和所述第二导电层322。

51.在所述第二导电层322、第二通孔302与所述第三介质层330之间还可以形成有金属阻挡层,以避免金属材料内原子的扩散。所述金属阻挡层的材料可以为tin、tan等中的一种。

52.在一些具体实施方式中,所述阻挡层3301的材料可以为sin、sion或sicn等,用于阻挡所述第一导电层321内的金属原子向所述第三介质层330内扩散。所述第一介质层310、第二介质层320以及第三介质层330的材料可以为氧化硅、氮氧化硅、碳氧化硅等集成电路支撑中常用的层间介质层材料,或者还可以为无定型碳、多孔氧化硅等等低k介电材料。

53.请参考图6a至图6b,依次形成覆盖所述第三介质层330的阻挡层3401以及位于所述阻挡层3401表面的第四介质层340;刻蚀所述第四介质层340,形成位于所述第二导电层322和所述第二通孔302上方的熔丝开窗区341。

54.所述熔丝开窗区341位于所述半导体结构上方,通常所述熔丝开窗区341的尺寸会大于所述半导体结构的尺寸,使得所述半导体结构位于所述熔丝开窗区341所在区域内。所述熔丝开窗区341底部与所述第二导电层322表面之间具有部分厚度的介质材料,作为覆盖所述第二导电层322的保护层。当不需要对所述第二导电层322进行熔断时,所述保护层能够保护所述第二导电层322,当需要对所述第二导电层322进行熔断时,直接通过所述熔丝开窗区341对所述第二导电层322和所述第二通孔302进行熔断。

55.所述第二导电层322表面的保护层的厚度较小,以进一步减小激光熔断时的能量。在一些具体实施方式中,还可以在所述第二导电层322所在的金属层或更上层的金属层内形成对准标记,所述对准标记位于所述熔丝开窗区341之外,所有熔丝结构相对于所述对准标记均具有固定的坐标,便于通过所述对准标记对所述熔丝结构进行激光对准。

56.所述该具体实施方式中,所述保护层包括阻挡层3401和位于所述阻挡层3401上的刻蚀所述第四介质层340后剩余的部分厚度的介质层。

57.在其他具体实施方式中,在形成熔丝开窗区341的过程中,可以以所述阻挡层3401作为刻蚀停止层,使得所述第二导电层322上仅覆盖有阻挡层3401作为保护层。以所述阻挡

层3401作为刻蚀停止层时,刻蚀所述第四介质层340的停止时机较容易控制,保护层的厚度仅由所述阻挡层3401的厚度决定。可以选择两种不同的材料作为阻挡层3401和第四介质层340,使得刻蚀所述第四介质层340的过程中,对第四介质层340和阻挡层3401具有较高的刻蚀选择比。所述阻挡层3401还用于阻挡所述第二导电层322的材料向所述第四介质层340内扩散。在一些具体实施方式中,所述阻挡层3401的材料可以为氮化硅、碳氮化硅等,所述第四介质层340的材料可以为氧化硅、氮氧化硅、碳氧化硅等集成电路支撑中常用的层间介质层材料,或者还可以为无定型碳、多孔氧化硅等等低k介电材料。

58.上述具体实施方式中,所述第一介质层310、第二介质层320、第三介质层330、第四介质层340以及阻挡层3301、3401均作为衬底上方的层间介质层或层间介质层内的一部分,用于隔离各金属层及层间互连结构。

59.本发明的具体实施方式还提供一种熔丝阵列,包括上述具体实施方式中所形成的半导体结构。具体的,多个所述半导体结构以m行、n列的阵列布置。在一些具体实施方式中,所述m和n均为正偶数。所述熔丝阵列构成可编程阵列,通过对所述熔丝阵列内的各半导体结构的熔断选择,对电路进行熔断控制。

60.请参考图7,为本发明一具体实施方式的熔丝阵列的结构示意图。

61.该具体实施方式中,所述熔丝阵列包括8个上述半导体结构701,以2行、4列的阵列布置。

62.为了减少熔丝阵列的面积,不同行的半导体之间相互错开,以减少相邻行之间的间距。

63.所述半导体结构的第一通孔连接至下方的电路702,所述电路702可以连接至其他半导体器件。通过选择性对其中的部分半导体结构进行熔断操作,可以改变电路702的连接关系,从而实现对芯片的修复等操作,例如,将冗余存储单元替代出现问题的存储单元,实现对存储芯片的修复。

64.请参考图8,为本发明一具体实施方式的熔丝阵列上方形成有熔丝开窗区的俯视示意图。

65.所述熔丝阵列上方形成有介质层800,所述介质层800内形成有熔丝开窗区801,所述熔丝开窗区801位于所述熔丝阵列的上方,暴露所述熔丝阵列内的所有熔丝结构,即所述半导体结构701。所述熔丝开窗区801底部与所述半导体结构701之间可以具有部分厚度的介质层800作为保护层。

66.以上所述仅是本发明的实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1