立体存储器装置及其制造方法与流程

1.本发明是有关于一种半导体存储器技术,且特别是有关于一种立体存储器装置及其制造方法。

背景技术:

2.在高密度存储器装置的制造中,集成电路中每单位面积的数据量已成为关键因素。特别是为了达到有竞争力的位成本(bit cost),每一位的单元尺寸不断缩小,但是对于传统的平面nor闪存阵列结构来说仍旧不足。尤其是低vcc/功率应用的2t-nor闪存,其需求的是选择晶体管要具备低阈值电压(vt)且不发生击穿(punch through)。

3.由于平面存储器单元的尺寸缩小是通过减小存储器单元的栅极长度方式来达成,所以一旦栅极长度变小就会缩短通道长度,容易发生漏极区与源极区之间不正常的击穿现象,而严重影响此存储器单元的电性表现,而导致数据误判。

技术实现要素:

4.本发明提供一种立体存储器装置,能同时达到缩减存储器单元面积与避免击穿现象发生的功效。

5.本发明另提供一种立体存储器装置的制造方法,能制作出存储器单元密度高且不易发生击穿的nor闪存。

6.本发明的立体存储器装置,包括衬底、多个叠层结构、多个共同源极线接触窗以及多个nor闪存。衬底具有与一第一方向平行且交替排列的多条共同源极线(csl)与多个存储器单元(cell)区。叠层结构则形成于衬底的多个存储器单元区上,且每个叠层结构包括与衬底电性隔离的一接地选择线(gsl)层以及与接地选择线层电性隔离并形成于其上的一字线(wl)层。共同源极线接触窗沿一第二方向形成于衬底的多条共同源极在线,以连接每个共同源极线。nor闪存则穿过叠层结构并设置于多个存储器单元区内,且每个nor闪存包括一外延柱、一电荷捕捉层、一高介电常数(high-k)层与一第一绝缘层。外延柱是从衬底外延形成,且外延柱在穿过接地选择线层的部分具有内缩侧壁。电荷捕捉层是位于外延柱与叠层结构中的wl层之间;高介电常数层则是位于电荷捕捉层与wl层之间。第一绝缘层位于外延柱的上述内缩侧壁与gsl层之间。

7.在本发明的一实施例中,每个共同源极线接触窗并与共同源极线直接接触。

8.在本发明的一实施例中,上述电荷捕捉层环绕外延柱并可延伸至字线层的上表面与下表面。

9.在本发明的一实施例中,上述立体存储器装置还可包括一第二绝缘层,形成于所述共同源极线接触窗与所述叠层结构之间

10.在本发明的一实施例中,上述立体存储器装置还可包括形成于外延柱的顶面内的多个第一导电型掺杂区。

11.在本发明的一实施例中,上述立体存储器装置还可包括形成于外延柱底下的衬底

内的多个第二导电型掺杂区。

12.在本发明的一实施例中,上述衬底为硅衬底,上述外延柱为硅外延柱。

13.本发明的立体存储器装置的制造方法,包括提供一个具有与一第一方向平行且交替排列的多个共同源极线(csl)区与多个存储器单元(cell)区的衬底。然后,在所述衬底上形成一叠层结构,且叠层结构包括互相交替的n+1层第一材料层与n层第二材料层,n为大于1的整数。于存储器单元区上的叠层结构中形成多个穿孔,直到露出衬底,再从所述衬底成长多个外延柱贯穿所述穿孔。在共同源极线区上的叠层结构中形成多个第一狭缝,并露出最上层的第二材料层,其中每个第一狭缝对准每个共同源极线区。先完全移除最上层的第二材料层,以形成露出每个外延柱的一部分的第一空间,再在第一狭缝的表面与露出的每个外延柱的表面共形地沉积一电荷捕捉层。接着,在第一狭缝下方形成露出多个共同源极线区的多个第二狭缝,并露出最下层的第二材料层。完全移除最下层的第二材料层,以形成露出每个外延柱的另一部分的第二空间,再进行热氧化法,以于露出的每个外延柱的表面与所述共同源极线区的表面形成热氧化层。于第一空间与第二空间中露出的热氧化层的表面与电荷捕捉层的表面上沉积一高介电常数(high-k)层,然后在第一空间与第二空间内沉积金属材料。之后,在原本的第一狭缝与第二狭缝的位置形成截断金属材料的多个第三狭缝,并露出衬底,其中留在第一空间内的金属材料作为字线,留在第二空间内的金属材料是作为接地选择线。进行离子注入工艺,以在露出的衬底内形成多条共同源极线。然后在第三狭缝内沉积绝缘层,再沿一第二方向于所述绝缘层中形成多个共同源极线接触窗,分别连接所述多个共同源极线。

14.基于上述,本发明将存储器阵列改成立体装置,不但能缩减存储器单元面积,还可通过工艺的改良,在nor闪存中加入high-k层作为阻挡氧化层(blocking oxide)与带隙工程隧穿氧化层(bandgap engineered tunnel oxide),并且可选择使用金属栅极(字线)来改善存储器性能。此外,本发明的工艺方法可实现在gsl与外延通道之间设置质量佳的绝缘层,以避免击穿现象发生。

15.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附附图作详细说明如下。

附图说明

16.图1是依照本发明的第一实施例的一种立体存储器装置的俯视图。

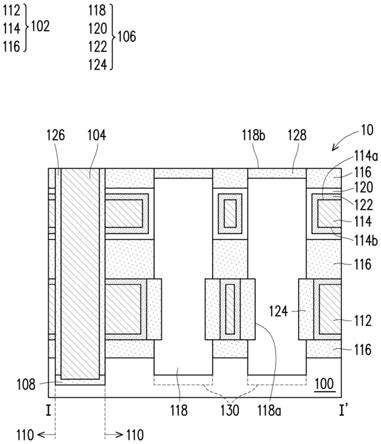

17.图2是图1的i-i

′

线段的剖面示意图。

18.图3显示图2中的外延柱与电荷捕捉层的立体示意图。

19.图4是第一实施例的一种立体存储器装置的立体简化图。

20.图5a至图5r是依照本发明的第二实施例的一种立体存储器装置的制造流程剖面示意图。

21.图6是依照本发明的第三实施例的一种立体存储器装置于擦除操作期间的一种电路图。

22.图7是依照本发明的第三实施例的一种立体存储器装置于擦除操作期间的另一种电路图。

23.图8是依照本发明的第四实施例的一种立体存储器装置于读取操作期间的一种电

路图。

24.【符号说明】

25.10:立体存储器装置

26.100、500:衬底

27.102、506:叠层结构

28.104、546:共同源极线接触窗

29.106:nor闪存

30.108、540:共同源极线

31.110、504:存储器单元区

32.112:接地选择线层

33.114:字线层

34.114a:上表面

35.114b:下表面

36.116、544:绝缘层

37.118、514:外延柱

38.118a、514a:内缩侧壁

39.118b、500a、514b:顶面

40.120、524:电荷捕捉层

41.122、532:高介电常数层

42.124:第一绝缘层

43.126:第二绝缘层

44.128:第一导电型掺杂区

45.130:第二导电型掺杂区

46.502:共同源极线区

47.5081、5082、5083:第一材料层

48.5101、5102:第二材料层

49.512:穿孔

50.512a:底部

51.513:p型离子注入工艺

52.516:第三材料层

53.518:硬掩模层

54.518a:开口

55.520:第一狭缝

56.522:第一空间

57.526:第二狭缝

58.528:第二空间

59.530:热氧化层

60.534:金属材料

61.536:第三狭缝

62.538:离子注入工艺

63.542:掺杂区

64.bl、bl0、bl1:位线

65.csl:线路

66.gsl0、gsl1:接地选择线

67.vblr:读取电压

68.vers1、vers2、vgers、vders:擦除电压

69.wl0、wl1:字线

具体实施方式

70.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

71.以下内容提供许多不同的实施方式或实施例,用于实施本发明的不同特征。而且,这些实施例仅为示范例,并不用来限制本发明的范围与应用。再者,为了清楚起见,各区域或结构元件的相对尺寸(如长度、厚度、间距等)及相对位置可能缩小或放大。另外,在各附图中使用相似或相同的元件符号表示相似或相同元件或特征。

72.图1是依照本发明的第一实施例的一种立体存储器装置的俯视图;图2是图1的i-i

′

线段的剖面示意图。

73.请同时参照图1与图2,第一实施例的立体存储器装置10包括衬底100、多个叠层结构102、多个共同源极线接触窗104以及多个nor闪存106。衬底100具有与一第一方向平行且交替排列的多条共同源极线(csl)108与多个存储器单元(cell)区110。叠层结构102则形成于衬底100的多个存储器单元区110上,且每个叠层结构102包括与衬底100电性隔离的一接地选择线(gsl)层112以及与接地选择线层112电性隔离并形成于其上的一字线(wl)层114。更详细地说,每个叠层结构102至少由三层绝缘层116与上述接地选择线层112和字线层114所构成,并通过绝缘层116达成接地选择线层112和字线层114的电性隔离。在一实施例中,接地选择线层112和字线层114都是金属材料(例如钨);在另一实施例中,接地选择线层112是多晶硅,而字线层114是金属材料(例如钨)。共同源极线接触窗104是沿一第二方向形成于衬底10的多条共同源极线108上,以连接每个共同源极线108,且共同源极线接触窗104可与共同源极线108直接接触。在本实施例中,第一方向垂直于第二方向;但本发明并不限于此,上述第一方向也可与第二方向之间具有一夹角(如锐角)。多条位线bl可平行第二方向配置,并电性耦接至底下的nor闪存106,共同源极线接触窗104则经由同一条线路csl外接出去。

74.请继续参照图2,第一实施例中的nor闪存106则穿过叠层结构102并设置于存储器单元区110内,且每个nor闪存106至少包括一外延柱118、一电荷捕捉层120、一高介电常数(high-k)层122与一第一绝缘层124。外延柱118是从衬底100外延形成的,其中上述衬底100为硅衬底,则外延柱118为硅外延柱,所以不同于传统由多晶硅构成的元件通道,具有更高的迁移率(mobility)可改善元件的效能,且外延柱118在穿过接地选择线层112的部分具有内缩侧壁118a。也就是说,外延柱118的截面形状若是圆形,则穿过接地选择线层112的部分的直径会小于其他部分的直径,这是因为在此处具有第一绝缘层124来隔离外延柱118与接

地选择线层112,且第一绝缘层124可以是通过热氧化法形成的热氧化层。然而,本发明并不限于此,上述外延柱118的截面形状也可以是椭圆形、方形、多边形或其组合。至于电荷捕捉层120是位于外延柱118与叠层结构102中的字线层114之间;举例来说,电荷捕捉层120的位置可环绕外延柱118并延伸至字线层114的上表面114a与下表面114b,因此电荷捕捉层120的结构会如同图3所示,其显示外延柱118与电荷捕捉层120的立体图。在一实施例中,电荷捕捉层120例如ono层或onono层。而高介电常数层122是位于电荷捕捉层120与字线层114之间。在一实施例中,高介电常数层122的材料例如二氧化铪(hfo2)、二氧化钛(tio2)、二氧化锆(zro2)、氧化钽(ta2o5)或氧化铝(al2o3)。另外,在本实施例中,于共同源极线接触窗104与叠层结构102之间有一第二绝缘层126,作为电性隔离结构。

75.在图2中,立体存储器装置10还包括形成于外延柱118的顶面118b内的第一导电型掺杂区128,且第一导电型掺杂区128可与共同源极线108具有相同的导电型。另外,在外延柱118底下的衬底100内还可形成有第二导电型掺杂区130,其可调节接地选择线层112的阈值电压(vt),以使gsl的vt变小并具有很窄的vt分布。在一实施例中,上述第一导电型是n型、上述第二导电型是p型;在另一实施例中,上述第一导电型是p型、上述第二导电型是n型。

76.为了更清楚了解本发明的立体存储器装置的结构,请参照图4,其中仅显示第一实施例的wl层114、gsl层112、衬底100、外延柱118、csl108与csl接触窗104。从图4可观察到,代表元件通道的外延柱118是被wl层114包围,所以本发明的立体存储器装置10是属于gaa元件,因此具有较好的栅极可控性(gate controllability)与较好的元件效能。

77.图5a至图5r是依照本发明的第二实施例的一种立体存储器装置的制造流程剖面示意图。

78.请先参照图5a,提供一个衬底500,其具有共同源极线(csl)区502与存储器单元(cell)区504,且本实施例可对照图1得到,衬底500的共同源极线区502与存储器单元区504实际上是在第一方向平行且交替排列的多个区域;也就是说,共同源极线区502是后续要形成共同源极线(请见图1标示的108)的区域,存储器单元区504是后续要形成存储器的区域(请见图1标示的110)。然后,在衬底500上形成一叠层结构506,且叠层结构506包括互相交替的n+1层第一材料层与n层第二材料层,n为大于1的整数。譬如图5a显示的是三层第一材料层5081、5082、5083与两层第二材料层5101、5102构成的叠层结构506。然而,本发明并不限于此,叠层结构506中也可加设其他中间层,以利工艺进行。

79.接着,请参照图5b,于存储器单元区504上的叠层结构506中形成多个穿孔512,直到露出衬底500。在本实施例中,穿孔512的底部512a可低于衬底500的顶面500a。然而,本发明并不限于此;在另一实施例中,穿孔512的底部512a可与衬底500的顶面500a齐平。而在形成穿孔512之后,还可额外进行一道p型离子注入工艺513,以调节后续形成的接地选择线的阈值电压(vt)。

80.然后,请参照图5c,从衬底500成长多个外延柱514贯穿穿孔512。举例来说,衬底500若是硅衬底,则外延形成的外延柱514可为(单晶)硅外延柱。在本实施例中,外延柱514的形成方式可采型目前既有的外延工艺。

81.接着,请参照图5d,为了在共同源极线区502上的叠层结构506中形成多个狭缝,可先在衬底500上全面形成一层第三材料层516,且形成方式可以利用沉积或涂布的方式,在

叠层结构506上形成覆盖外延柱514的膜层。上述第三材料层516可与第一材料层5083是相同材料,以利后续工艺。但是,本发明并不限于此,第三材料层516的材料也可不同于第一材料层5083。为了表面的平坦度,还可在第三材料层516形成后进行如cmp的平坦化工艺。

82.然后,请参照图5e,在第三材料层516上形成一层硬掩模层518,其中硬掩模层518为了后续刻蚀形成狭缝时能作为刻蚀掩模,所以优先选用刻蚀率远低于叠层结构506的材料;在一实施例中,硬掩模层518的材料例如多晶硅、第一材料层508

1,2,3

的材料例如氧化硅、第二材料层5108

1,2

的材料例如氮化硅。但是,本发明并不限于此,上述材料的选用也可根据需求做变化。

83.之后,请参照图5f,图案化硬掩模层518,使其形成预定形成狭缝的开口518a,并暴露出第三材料层516。

84.随后,请参照图5g,以图案化的硬掩模层518作为刻蚀掩模,刻蚀去除开口518a内的第一材料层5083、最上层的第二材料层5102和部分第一材料层5082,而形成位于共同源极线区502上的第一狭缝520,并露出最上层的第二材料层5102,其中第一狭缝520优选是对准共同源极线区502。

85.接着,请参照图5h,完全移除最上层的第二材料层,以形成露出每个外延柱514的一部分的第一空间522。完全移除最上层的第二材料层的方法例如刻蚀,且所述刻蚀相对于第一材料层508

2,3

而对第二材料层5102具有高选择比。

86.之后,请参照图5i,在第一狭缝520的表面与露出的每个外延柱514的表面共形地沉积一电荷捕捉层524,其中电荷捕捉层524例如ono层或onono层。由于工艺的关系,除了外延柱514的表面,电荷捕捉层524还会全面形成在其他结构层露出的表面,如硬掩模层518、第三材料层516、第一材料层508

2,3

的表面。

87.接着,请参照图5j,在第一狭缝502下方形成露出共同源极线区502的第二狭缝526,并露出最下层的第二材料层5101。在一实施例中,形成第二狭缝526的步骤包括先回刻蚀电荷捕捉层524,直到露出第一狭缝520的底面,再使用为了形成第一狭缝520的掩模进行光刻刻蚀工艺,直到露出衬底500。在一实施例中,形成第二狭缝526的步骤包括先回刻蚀电荷捕捉层524,直到露出第一狭缝520的底面,再使用剩下的电荷捕捉层524作为刻蚀掩模,刻蚀掉第一狭缝520下方的第一材料层5082、最下层的第二材料层5101与第一材料层5081。

88.然后,请参照图5k,完全移除最下层的第二材料层,以形成露出每个外延柱514的另一部分的第二空间528。完全移除最下层的第二材料层的方法例如刻蚀,且所述刻蚀相对于第一材料层508

1,2

而对第二材料层5101具有高选择比。

89.接着,请参照图5l,进行热氧化法,以于露出的每个外延柱514的表面与共同源极线区502的表面形成热氧化层530。由于热氧化层530的质量佳,所以能降低击穿现象发生的机率,其中热氧化层530的厚度例如在100nm~300nm之间,且会使得外延柱514于热氧化层530所在部位具有内缩侧壁514a。

90.之后,请参照图5m,于第一空间522与第二空间528中露出的热氧化层530的表面与电荷捕捉层524的表面上沉积一高介电常数(high-k)层532,其中沉积高介电常数层532的方法例如pvd、cvd、ald等。高介电常数层532的材料例如二氧化铪(hfo2)、二氧化钛(tio2)、二氧化锆(zro2)、氧化钽(ta2o5)或氧化铝(al2o3)。由于工艺的关系,除了上述提及的表面,高介电常数层532还会全面形成在其他结构层露出的表面,如硬掩模层518、第一材料层

508

1,2

的表面。

91.然后,请参照图5n,在第一空间522与第二空间528内沉积金属材料534,金属材料534例如钨。

92.之后,请参照图5o,在原本的第一狭缝(请见图5j的520)与第二狭缝(请见图5j的526)的位置形成截断金属材料534的第三狭缝536,并露出衬底500,其中留在第一空间528内的金属材料534可作为字线,留在第二空间528内的金属材料可作为接地选择线。而且,形成第三狭缝536的步骤可使用为了形成第一狭缝的掩模进行光刻刻蚀工艺,直到露出衬底500。另外,在刻蚀出第三狭缝536之前,可选择先移除硬掩模层(请见图5n的518)、第三材料层(请见图5n的516)与部分叠层结构506(如第一材料层5083),直到露出外延柱514的顶面514b。但是,本发明并不限于此,也可在第三狭缝536形成之后的后续工艺将上述膜层移除。

93.接着,请参照图5p,进行离子注入工艺538,以在露出的衬底500内形成多条共同源极线540。同时,若是外延柱514的顶面514b已露出,则可在进行上述离子注入工艺538的同时,在每个外延柱514的顶面514形成掺杂区542,有助于改善后续电性接触的导电率。

94.然后,请参照图5q,在第三狭缝536内沉积绝缘层544,其中沉积绝缘层544的方法例如低温氧化层沉积(low temperature oxidation)等。

95.随后,请参照图5r,于绝缘层544中形成共同源极线接触窗546,连接共同源极线540,其中形成共同源极线接触窗546方是例如先在绝缘层544中刻蚀形成露出共同源极线540的开口,然后于此开口中沉积金属材料(如钨)直到填满口,再进行如cmp的金属平坦化步骤,得到共同源极线接触窗546。若是对照图1可得到,共同源极线接触窗(请见图1标示的104)是沿第二方向排列,并且每一条共同源极线(请见图1标示的108)都至少有一个共同源极线接触窗,以由同一条线路csl连接。由于本实施例的共同源极线接触窗546是利用一道沉积工艺连通至衬底500内的共同源极线540,所以本发明的立体存储器装置能达成按位(by-bit)擦除的操作。

96.以下说明本发明的立体存储器装置的电路及其操作。

97.首先,关于立体存储器装置的pgm操作,可实行常见的方式,譬如利用+vg fn注入(fn injection)或者通道热电子注入(channel-hot-electron injection)的方式对被选存储器单元进行pgm(编程)。

98.关于立体存储器装置的ers(擦除)操作,则有两种方式。图6显示的是立体存储器装置于可选字线的擦除操作;图7显示的是立体存储器装置于可选位的擦除操作。

99.在图6中,两条wl分别连接四个nor闪存,若要擦除虚线框住的两个nor闪存,则可对共同源极线供应擦除电压vers1以及对接地选择线gsl0供应擦除电压vers2,字线wl0为0v,其余线路则维持浮动(floating),以完成按分页(by-page)擦除的操作。

100.在图7中,为了擦除虚线框住的单一个nor闪存,可对字线wl0供应小于0v的擦除电压vgers以及对位线bl0供应擦除电压vders,其余线路则为0v,以完成by-bit擦除的操作。

101.关于立体存储器装置的read(读取)操作,如图8所示。

102.在图8中显示的是一种低功率读取的操作,虚线框住的是要读取的存储器单元,未选单元的字线wl1和接地选择线gsl1都是0v;被选单元的字线wl0为0v(其中低阈值电压lvt<0v且高阈值电压hvt>0v)、对接地选择线gsl0供应vcc且不需要增压电路(pumping circuit),供应位线bl0、bl1的电压都是读取电压vblr。

103.综上所述,本发明将nor闪存阵列改成垂直式的立体存储器装置,不但能缩减存储器单元面积,还可通过工艺的改良,在nor闪存中加入high-k材料作为阻挡介电层与带隙工程隧穿介电层。此外,本发明的工艺方法可实现在gsl与外延通道之间设置质量佳的绝缘层,以避免击穿现象发生;还能选择沉积金属作为栅极(字线),进而改善存储器单元的性能。

104.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1