存储元件及其制造方法与流程

1.本发明属于半导体和存储技术领域,涉及一种存储元件及其制造方法。

背景技术:

2.随着科技日新月异,电子元件的进步增加了对更大储存能力的需要。为了满足高储存密度(high storage density)的需求,存储体元件尺寸变得更小而且集成度更高。因此,存储体元件的型态已从平面型栅极(planar gate)结构的二维存储体元件(2d memory device)发展到具有垂直通道(vertical channel,vc)结构的三维存储体元件(3d memory device)。然而,具有垂直通道结构的三维存储元件仍面临许多挑战。

技术实现要素:

3.本发明提供一种存储元件及其制造方法,可以在单位面积内具有纵向叠置的多个存储单元,以有效利用基底的面积,并且,可与现有工艺相容。

4.本发明实施例提出一种存储元件,包括:至少一半导体层,位于介电层上方;第一位线与第二位线,其中所述第一位线位于所述介电层上,所述第二位线位于第一位线上方;第一字线与第二字线,位于所述第一位线与所述第二位线之间;源极线,位于所述第一字线与所述第二字线之间;通道柱,贯穿所述第一字线、所述源极线与所述第二字线,且与所述第一位线、所述源极线及所述第二位线连接;

5.第一电荷储存结构,环绕所述第一字线的顶面与底面,并介于所述第一字线的侧壁与所述通道柱的侧壁的下部之间;以及第二电荷储存结构,环绕所述第二字线的顶面与底面,并介于所述第二字线的侧壁与所述通道柱的所述侧壁的上部之间。所述第一字线、所述第一电荷储存结构与所述通道柱形成第一存储单元;所述第二字线、所述第二电荷储存结构与所述通道柱形成第二存储单元。

6.本发明实施例还提出一种存储元件的制造方法,包括:在介电层上形成第一位线;以及至少一循环工艺。所述至少一循环工艺包括以下步骤。在所述第一位线与所述介电层上形成第一叠层结构、导体层及第二叠层结构,其中所述第一叠层结构与所述第二叠层结构各自分别包括由下而上的第一绝缘层、牺牲层与第二绝缘层,所述导体层作为源极线;形成穿过所述第二叠层结构、所述导体层及所述第一叠层结构的孔;在所述孔中形成通道柱,所述导通柱连接所述第一位线;在所述第二叠层结构、所述导体层以及至少一部分所述第一叠层结构中形成凹槽;移除所述凹槽所裸露的所述第二叠层结构及所述第一叠层结构的所述牺牲层,以形成第一字线沟道与第二字线沟道,所述第一字线沟道与第二字线沟道裸露出所述通道柱的侧壁;形成第一电荷储存结构以覆盖所述第一字线沟道的顶面与底面以及所述通道层的侧壁,并形成第二电荷储存结构以覆盖所述第二字线沟道的顶面与底面以及所述通道层的所述侧壁;在所述第一字线沟道中形成第一字线,并在所述第二字线沟道中形成第二字线;在所述凹槽中填入绝缘材料;以及在所述第二叠层结构上方形成第二位线,所述第二位线与所述通道柱电性连接。所述第一字线、所述第一电荷储存结构与所述通

道柱形成第一存储单元;所述第二字线、所述第二电荷储存结构与所述通道柱形成第二存储单元。

7.本发明的三维存储元件在单位面积内可以包括纵向叠置的多个存储单元,可以有效利用基底的面积。并且,本发明的三维存储元件的制作工艺可与现有工艺相容。

附图说明

8.图1a是依照本发明的实施例的存储元件的俯视图。

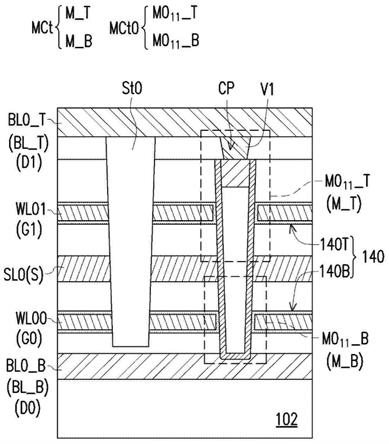

9.图1b是图1a的线b-b’的剖面图。

10.图1c是图1a的线c-c’的剖面图。

11.图2是图1a的局部等效电路图。

12.图3a至图3j是依照本发明的实施例的存储元件的制造流程的剖面示意图。

13.图4a至图4b是依照本发明的又一实施例的存储元件的局部制造流程的剖面示意图。

14.图5是依照本发明的其他实施例的存储元件的俯视图。

15.图6a是依照本发明的实施例的三维存储元件的俯视图。

16.图6b是图6a的线b-b’的剖面图。

17.图6c是图6a的线c-c’的剖面图。

18.图7是图6c的等效电路图。

19.【符号说明】

20.10:存储元件

21.10’:三维存储元件

22.146:阻挡层

23.100:基底

24.102:介电层

25.110:第一叠层结构

26.112、132:第一绝缘层

27.1114、134:牺牲层

28.116、136:第二绝缘层

29.120:导体层

30.170:导体层

31.130:第二叠层结构

32.138:孔

33.140、140a、140’、140b、140t、140b’、140t’:电荷储存结构

34.142:隧穿层

35.144:电荷储存层

36.146:阻挡层

37.150、150a:通道层

38.150b:半导体柱

39.152:绝缘芯

40.152a:绝缘材料

41.154:导电插塞

42.154a:导电层

43.162:停止层

44.164、164s:凹槽

45.168:源极线沟道

46.172、174:栅极沟道

47.bl_b、bl0_b、bl1_b、bl2_b、bl3_b、bl4_b、bl5_b、bl6_b、bl7_b、bl8_b、bl9_b、bl_b’、bl0_b’、bl1_b’、bl2_b’、bl3_b’、bl4_b’、bl_t、bl0_t、bl1_t、bl2_t、bl3_t、bl4_t、bl5_t、bl6_t、bl7_t、bl8_t、bl9_t、bl_t’、bl0_t’、bl1_t’、bl2_t’、bl3_t’、bl4_t’:位线

48.blk、blk0、blk1、blk’、blk0’:区块

49.cp、cp1、cp2、cp3、cp4、cp5:通道柱

50.d1:第一方向

51.d2:第二方向

52.d3:第三方向

53.d0、d1、d0’、d1’:漏极

54.dp、dp’:虚设柱

55.g0、g0’、g1、g1’:栅极

56.ml:金属层

57.m_b、m0

11

_b、m0

12

_b、m0

13

_b、m1

11

_b、m1

12

_b、m1

13

_b、m_b’:第一存储单元

58.m_t、m0

11

_t、m0

12

_t、m0

13

_t、m1

11

_t、m1

12

_t、m1

13

_t、m_t’:第二存储单元

59.mct、mct0、mct1、mct’、mct0’:存储单元组

60.r1:第一区

61.r2:第二区

62.s、s’:源极

63.sl0、sl1、sl0’:源极线

64.slc、slc’:源极线接触窗

65.st、st0、st1、st2、st’、st0’、st1’:绝缘墙

66.t、t1、t2:半导体层

67.v1、v2、v3、v4、v5、v1’、v2’:介层窗

68.wl、wl00、wl01、wl10、wl11、wl’、wl00’、wl01’:字线

69.wlc0、wlc1、wlc0’、wlc1’:字线接触窗

70.w1、w2、w3、w4:宽度

具体实施方式

71.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

72.请参照图1a,本发明实施例的存储元件10是一种三维nor快闪存储元件,其设置在基底100上。基底100包括以多个绝缘墙st分隔开的多个区块(block)blk。在图1a中多个区

块(block)blk以两个区块blk0与区块blk1来表示,但不以此为限。区块blk0与区块blk1是以绝缘墙(或称绝缘缝)st0、st1、st2分隔开。存储元件10包括多个存储单元组mct位于各区块blk的第一区r1中。第一区r1又可称为存储单元区。在各区块blk中的多个存储单元组mct可以分别排列成多行与多列所形成的阵列。相邻两行的存储单元组mct可以对齐或是相错开。举例来说,区块blk0中的存储单元组mct0排列成多行与多列所形成的阵列,且相邻两行的存储单元组mct0可以彼此相错(如图1a所示),或彼此对齐(未示出)。区块blk1中的存储单元组mct1亦排列成多行与多列所形成的阵列,且相邻两行的存储单元组mct1可以彼此相错(如图1a所示),或彼此对齐(未示出)。此外,区块blk0中的奇数列的存储单元组mct0与区块blk1中的奇数列的存储单元组mct1彼此在第一方向d1上对齐。区块blk0中的偶数列的存储单元组mct0与区块blk1中的偶数列的存储单元组mct1彼此彼此在第一方向d1上对齐。

73.请参照图1b,每一个存储单元组mct包括在第三方向d3上两个叠置的第一存储单元m_b与第二存储单元m_t。举例来说,在图2中,区块blk0中具有第一存储单元m0

11

_b、m0

12

b、m0

13

b与第二存储单元m0

11

_t、m0

12

_t、m0

13

_t。第二存储单元m0

11

_t、m0

12

_t、m0

13

_t分别设置在第一存储单元m0

11

_b、m0

12

_b、m0

13

_b上方,且分别形成一个存储单元组mct0。同样地,区块blk1中具有第一存储单元m1

11

_b、m1

12

_b、m1

13

_b与第二存储单元m1

11

_t、m1

12

_t、m1

13

_t。第二存储单元m1

11

_t、m1

12

_t、m1

13

_t分别设置在第一存储单元m1

11

_b、m1

12

_b、m1

13

_b上方,且分别形成一个存储单元组mct1。

74.请参照图1a与图2,存储元件10还包括在第一方向d1延伸的位线bl_b与位线bl_t。位线bl_t对应设置在位线bl_b上方。位线bl_b例如是包括bl0_b、bl1_b、

…

bl9_b,或更多的位线。位线bl_t例如是包括bl0_t、bl1_t、

…

bl9_t,或更多的位线。每一位线bl_b与位线bl_t可以串接不同区块blk中的第一存储单元的漏极以及第二存储单元的漏极。举例来说,位线bl0_b可以串接区块blk0中的第一存储单元m0

11

_b的漏极与区块blk1中的第一存储单元m1

11

_b的漏极。位线bl0_t可以串接区块blk0中的第二存储单元m0

11

_t的漏极与区块blk1中的第二存储单元m1

11

_t的漏极。

75.请参照图1a与图2,存储元件10还包括多条源极线sl,以连接同一区块blk中同一行的多个第一存储单元与多个第二存储单元的共用源极。举例来说,存储元件10还包括源极线sl0与sl1。源极线sl0可以串接区块blk0中的第一存储单元m0

11

_b与第二存储单元m0

11

_t的共用源极、第一存储单元m0

12

_b与第二存储单元m0

12

_t的共用源极以及第一存储单元m0

13

_b与第二存储单元m0

13

_t的共用源极。同样地,源极线sl1可以串接区块blk1中的第一存储单元m1

11

_b与第二存储单元m1

11

_t的共用源极、第一存储单元m1

12

_b与第二存储单元m1

12

_t的共用源极以及第一存储单元m1

13

_b与第二存储单元m1

13

_t的共用源极。

76.请参照图1a与图2,存储元件10还包括多条字线wl,以连接同一区块blk中同一行的多个第一存储单元的栅极或同一行的多个第二存储单元的栅极。举例来说,字线wl00连接区块blk0中同一行(第一行)的第一存储单元m0

11

_b、m0

12

_b、m0

13

_b的栅极。字线wl01连接区块blk0中同一行(第二行)的第二存储单元m0

11

_t、m0

12

_t、m0

13

_t的栅极。字线wl10连接区块blk1中同一行(第一行)的第一存储单元m1

11

_b、m1

12

_b、m1

13

_b的栅极。字线wl11连接区块blk1中同一行(第二行)的第二存储单元m1

11

_t、m1

12

_t、m1

13

_t的栅极。

77.请参照图1b,在本实施例中,在区块blk0中的存储单元组mct0包括第一存储单元m0

11

_b与第二存储单元m0

11

_t。第一存储单元m0

11

_b包括栅极g0(即字线wl00)、电荷储存结

构140b、通道柱cp、位线bl0_b(漏极d0)与源极线sl0(源极s,或称共用源极)。第二存储单元m0

11

_t设置在第一存储单元m0

11

_b上方。第二存储单元m0

11

_t包括栅极g1(即字线wl01)、电荷储存结构140t、通道柱cp、位线bl0_t(漏极d1)以及源极线sl0(源极s,或称共用源极)。栅极g0与栅极g1设置在位线bl0_b(漏极d0)与位线bl0_t(漏极d1)之间。

78.电荷储存结构140b与电荷储存结构140t彼此分离,且形成电荷储存结构140。电荷储存结构140t位于电荷储存结构140b的上方。电荷储存结构140b覆盖并物理性接触栅极g0的顶面与底面,并且位于栅极g0的侧壁与通道柱cp的外侧壁的下部之间并与其彼此接触。电荷储存结构140t覆盖并物理性接触栅极g1的顶面与底面,并且位于栅极g1的侧壁与通道柱cp的外侧壁的上部之间并与其彼此接触。源极线sl0(源极s)设置在栅极g0与栅极g1之间。源极线sl0(源极s)为连续层,其与通道柱cp的外侧壁的中部物理性接触。位线bl0_b(漏极d0)与通道柱cp的底面物理性接触。位线bl0_t(漏极d1)经由介层窗v1与通道柱cp的顶面电性连接。

79.请参照图1a与1c,字线wl00的末端经由字线接触窗wlc0与金属层ml连接。字线wl01的末端经由字线接触窗wlc1与金属层ml连接。源极线sl0的末端经由源极线接触窗slc与金属层ml连接。字线wl00的末端、源极线sl0的末端、字线wl01的末端设置在区块blk0的第二区r2。字线wl00的末端、源极线sl0的末端、字线wl01的末端可以呈阶梯状,因此第二区r2又可称为阶梯区。

80.请参照图1a与1b,在一些实施例中,在第二区r2中还包括多个虚设柱(dummy pillar)dp。虚设柱dp是用来提供工艺中结构的支撑性,以避免层或结构的塌陷。虚设柱dp可以是在形成存储孔(或称通道孔)以及通道柱cp时同时形成。虚设柱dp的结构可以与通道柱cp的结构相同,但尺寸可以与存储孔(或称通道孔)的尺寸相同或相似。以设置在区块blk0的通道柱cp与虚设柱dp来说,通道柱cp下方会有第一位线bl0_b且与位线bl0_b电性连接,而虚设柱dp下方则不会有位线bl0_b且与位线bl0_b电性不连接。通道柱cp上方会形成介层窗,例如是介层窗v1,以与位线bl0_t电性连接,而虚设柱dp上方则不会形成介层窗,因此虚设柱dp与位线bl0_t电性不连接。虚设柱dp的侧壁周围会有栅极go、源极线sl0、栅极g1或电荷储存结构140与其接触。

81.请参照图3a,本发明实施例的存储元件10(如图1a所示)的制造方法如下。以下的实施例是以形成单一存储单元组mct来说明,然而,通过以下所述的工艺可以形成多个存储单元组mct。首先,提供基底(未示出)。基底包括半导体基底,例如是硅基底。在基底上形成介电层102。介电层102的材料例如是化学气相沉积法形成的氧化硅。在所述介电层102上形成位线bl_b。位线bl_b又可称为漏极(d0)。在一些实施例中,位线bl_b的形成方法例如是利用化学气相沉积法形成掺杂的多晶硅,然后再经由光刻与刻蚀工艺进行图案化。然后,形成另一介电层(未示出),然后执行诸如化学机械研磨工艺的平坦化工艺,以去除位线bl_b上的所述另一介电层。在替代实施例中,在形成位线bl_b之前,先形成所述另一介电层,然后对所述另一介电层进行图案化以形成位线沟道。此后,在所述另一介电层上及位线沟道形成并填入掺杂的多晶硅层,然后执行诸如化学机械研磨工艺的平坦化工艺以去除所述另一介电层上的掺杂的多晶硅层,从而形成位线bl_b。

82.接着,在位线bl_b与介电层102上形成第一叠层结构110、导体层120及第二叠层结构130。第一叠层结构110包括由下而上叠层的第一绝缘层112、牺牲层114与第二绝缘层

116。第一绝缘层112、第二绝缘层116的材料例如是化学气相沉积法形成的氧化硅。牺牲层114的材料与第一绝缘层112及第二绝缘层116的材料不同,例如是化学气相沉积法形成的氮化硅。第一绝缘层112、牺牲层114与第二绝缘层116的厚度可以相同或相异。

83.导体层120例如是化学气相沉积法形成的掺杂的多晶硅层。导体层120作为源极线sl(源极s)。第二叠层结构130包括由下而上叠层的第一绝缘层132、牺牲层134与第二绝缘层136。第一绝缘层132、第二绝缘层136的材料例如是化学气相沉积法形成的氧化硅。牺牲层134的材料与第一绝缘层132及第二绝缘层136的材料不同,例如是化学气相沉积法形成的氮化硅。第一绝缘层132、牺牲层134与第二绝缘层136的厚度可以相同或相异。举例来说,第二绝缘层136的厚度可以大于第一绝缘层132与牺牲层134的厚度。

84.请参照图3b,通过光刻与刻蚀工艺进行图案化工艺,以在第二叠层结构130、导体层120及第一叠层结构110中形成孔138。孔138又可称为存储孔(memory hole)或通道孔(channel hole)。孔138裸露出位线bl_b。从图1a所示的俯视图中来看,孔138的形状可以是圆形、椭圆形等。在一些实施例中,亦在基底的阶梯区(未示出)的第二叠层结构130、导体层120及第一叠层结构110中形成多个孔(未示出),孔的下方并无位线bl_b。这些孔是用来形成虚设柱(如图1a所示),以在后续工艺中支撑半导体元件的结构,以避免层或结构的塌陷。

85.请参照图3c至3e,进行在孔138中形成通道柱(channel pillar)cp的工艺。在一些实施例中,通道柱cp的形成方法包括以下步骤。首先,在第二叠层结构130上以及孔138中形成通道层150a与绝缘材料152a,如图3c所示。通道层150a共形地覆盖第二叠层结构130、孔138的侧壁以及位线bl_b的顶面,并且与位线bl_b电性连接。通道层150a包括掺杂的半导体材料、未掺杂的半导体材料或其组合。举例来说,通道层150a可以是先经由化学气相沉积工艺或是物理气相形成未掺杂的多晶硅层,然后再经由回火工艺来形成。绝缘材料152a覆盖在通道层150a上,并且填满孔138。绝缘材料152a例如是以化学气相沉积法形成的氧化硅、氮化硅、氮氧化硅、其他合适的介电材料或其组合。

86.请参照图3d,移除部分绝缘材料152a,以在孔138中形成绝缘芯152。移除的工艺可以采用单一阶段刻蚀工艺、两阶段刻蚀工艺、多阶段刻蚀工艺、化学机械研磨工艺或其组合。刻蚀工艺可以例如是各向异性刻蚀、各向同性刻蚀或其组合等方法。绝缘芯152的顶面低于第二叠层结构130的顶面,因此,在绝缘芯152的顶面上具有凹槽(未示出)。接着,在第二叠层结构130的顶面上以及绝缘芯152上方的凹槽中形成导电层154a。导电层154a例如是经由化学气相沉积工艺或是物理气相沉积工艺形成的掺杂的多晶硅、钨、铂或其组合。

87.请参照图3e,进行回刻蚀或是化学机械研磨工艺,以移除第二叠层结构130的顶面上的导电材料层154a,以在凹槽中形成导电插塞154,以完成通道柱cp的制作。通道柱cp包括绝缘芯152、导电插塞154以及通道层150。绝缘芯152位于孔138中。导电插塞154位于绝缘芯152上,并且与通道层150电性连接。通道层150为一共形层,其环绕绝缘芯152与导电插塞154的侧壁,并且包覆绝缘芯152的底部,与导电插塞154、位线bl_b以及导体层120电性连接。导体层120作为源极线sl,或源极s。在一些实施例中,与绝缘芯152、导电插塞154以及通道层150相似的结构亦形成在基底的阶梯区的多个孔(未示出)中,以形成虚设柱。虚设柱的下方无位线bl_b,且虚设柱与位线bl_b电性不连接。

88.请参照图3f,在第二叠层结构130上形成停止层162。停止层162的材料包括以cvd形成的氧化硅、氮化硅、氮氧化硅、碳化硅或其组合。在一些实施例中,停止层162包括与最

顶层的第二绝缘层136的材料不同的材料。接着,在停止层162、第二叠层结构130、导体层120以及第一叠层结构110中形成凹槽164。在一些实例中,凹槽164的深度至少延伸穿过牺牲层114,使凹槽164的底部裸露出第一绝缘层112。

89.请参照图3f,进行刻蚀工艺,移除牺牲层114与134,以形成栅极沟道172与174。刻蚀的方法可以采用干法刻蚀、湿法刻蚀或其组合。在牺牲层114与134为氮化硅的实施例中,可以采用磷酸作为刻蚀剂。在进行此阶段工艺时,在基底的阶梯区的虚设柱可以提供工艺中结构的支撑性,以避免层或结构的塌陷。

90.请参照图3g,在栅极沟道172与174所裸露的表面以及凹槽164的侧壁形成电荷储存结构140a以及导体层170。在一实施例中,电荷储存结构140a可以包括隧穿层142、电荷储存层144、阻挡层(blocking layer)146。隧穿层142/电荷储存层144/阻挡层146例如是氧化物/氮化物/氧化物(ono)的复合层,或其他材料所形成的复合层。电荷储存结构140a也可以例如是氧化物/氮化物/氧化物/氮化物/氧化物(onono)的复合层、硅/氧化物/氮化物/氧化物/硅(sonos)、氧化铝/氧化物/氮化物/氧化物(al2o3/o/n/o)或是其他合适的复合层。电荷储存结构140a可以通过化学气相沉积、热氧化、氮化、刻蚀等工艺来形成。导体层170例如是经由化学气相沉积工艺或是物理气相沉积工艺形成导体材料,例如掺杂的多晶硅、非晶硅、钨(w)、钴(co)、铝(al)、硅化钨(wsi

x

)或硅化钴(cosi

x

)。

91.请参照图3h,进行各向异性刻蚀工艺,将覆盖在停止层162的顶面上以及填入于凹槽164之中的导体层170以及电荷储存结构140a移除,以形成电荷储存结构140以及栅极g0与栅极g1。电荷储存结构140包括彼此分隔的电荷储存结构140b与电荷储存结构140t。

92.电荷储存结构140b与栅极g0形成在栅极沟道172之中。电荷储存结构140b覆盖栅极g0的顶面与底面,并且位于栅极g0的侧壁与通道柱cp的外侧壁的下部之间。电荷储存结构140t与栅极g1形成在栅极沟道174之中。电荷储存结构140t覆盖栅极g1的顶面与底面,并且位于栅极g1的侧壁与通道柱cp的外侧壁的上部之间。

93.请参照图3i,在凹槽164之中形成绝缘墙st。绝缘墙st的形成方法例如是以化学气相沉积法或是旋涂法在停止层162上形成绝缘材料层,例如是氧化硅、旋涂式玻璃等。之后,再以停止层162为研磨停止层或是刻蚀停止层,进行回刻蚀工艺或是化学机械研磨工艺,以移除停止层162上的绝缘材料层。

94.请参照图3j,在停止层162中形成介层窗(via)v1。介层窗v1的形成方法例如是以光刻和刻蚀法在停止层162中形成介层窗孔(via hole)。之后,经由化学气相沉积工艺或是物理气相沉积工艺在停止层162上形成导体材料,例如掺杂的多晶硅、非晶硅、钨(w)、钴(co)、铝(al)、硅化钨(wsi

x

)或硅化钴(cosi

x

)。其后,进行回刻蚀工艺或是化学机械研磨工艺,将覆盖在停止层162的表面上的导体材料移除。

95.之后,在停止层162上形成位线bl_t(漏极d1)。位线bl_t的形成方法例如是利用化学气相沉积法形成掺杂的多晶硅,然后再经由光刻与刻蚀工艺进行图案化。位线bl_t经由介层窗v1与通道柱cp的电性连接。

96.栅极g0、电荷储存结构140b、通道柱cp的下部、漏极d0与源极s形成第一存储单元m_b。栅极g1、电荷储存结构140t、通道柱cp的上部、漏极d1与源极s形成第二存储单元m_t。第二存储单元m_t叠置在第一存储单元m_b上。此外,电荷储存结构140b和电荷储存结构140t彼此分离且未与源极s物理性接触。电荷储存结构140b与源极s之间以第一绝缘层116

分隔;电荷储存结构140t与源极s之间以第一绝缘层132分隔。

97.在上述的实施例中,通道柱cp包括绝缘芯152、导电插塞154以及通道层150,然而,本发明实施例不以此为限。在其他的实施例中,通道柱cp可以是由实心的掺杂的半导体柱150b所构成,如图4a与图4b所示。请参照图3c与图4a,掺杂的半导体柱150b的形成方法例如是在第二叠层结构130上形成掺杂的半导体层,且掺杂的半导体层还填满孔138。掺杂的半导体层例如是掺杂的磊晶硅(外延生长的硅)。其后,进行回刻蚀工艺或是化学机械研磨工艺,将覆盖在停止层162的表面上的导体材料移除。以此种具有实心的掺杂的半导体柱150b作为通道柱cp的存储元件如图4b所示。请参照图4b,通道柱cp为实心的掺杂的半导体柱150b,其与位线bl_b(漏极d0)直接接触且电性连接,并且与介层窗v1直接接触且直接经由介层窗v1与位线bl_t电性连接,而无需再经由导电插塞。在阶梯区的虚设柱dp的结构可以与通道柱cp的组合结构相同,但尺寸可以与存储孔(或称通道孔)的尺寸相同或相似。

98.此外,请参照图1a,在一些实施例中,每一个通道柱cp的上、下方可以被单一条位线bl_b以及单一条位线bl_t跨过。例如,存储单元组mct0的通道柱cp被单一位线bl0_b以及单一条位线bl0_t跨过。在另一些实施例中,每一个通道柱cp的上、下方可以被两条位线bl_t及其下方的两条位线bl_b(未示出)跨过,如图5所示。

99.请参照图5,存储元件包括位线bl_b(未示出)与位线bl_t。位线bl_b包括bl0_b、bl1_b

……

...bl19_b(未示出)。位线bl_t包括bl0_t、bl1_t

……

..bl19_t。位线bl0_t、bl1_t均跨过同一列的通道柱cp1与cp3,且在通道柱cp1所定义的宽度w1与通道柱cp3所定义的宽度w3之内。位线bl0_t与通道柱cp1电性连接;而与通道柱cp3电性不连接。位线bl1_t与通道柱cp1电性不连接,但与通道柱cp3电性连接。位线bl2_t、bl3_t均跨过同一列的通道柱cp2与cp4,且在通道柱cp2所定义的宽度w2与通道柱cp4所定义的宽度w4之内。位线bl2_t与通道柱cp2电性连接,但与通道柱cp4电性不连接。位线bl3_t与通道柱cp4电性不连接;而与通道柱cp4电性连接。换言之,同一列的通道柱cp(例如cp1与cp3)上方的介层窗v(例如v1与v3),在第一方向d1上是相错开的,而并未对齐。而在同一行的通道柱cp(例如cp1与cp5)上方的介层窗v(例如v1与v5),在第二方向d2上可以对齐或是相错开的。

100.在另一些实施例中,上述的存储元件也可以通过堆叠而制作成三维存储元件。

101.请参照图6a、图6b与图6c,三维存储元件10’包括多层半导体层t。在图6b与图6c中以两层(tier)半导体层t1与t2来说明,然而,本发明不以此为限,三维存储元件10’可以包含更多层半导体层。例如,三维存储元件10’可以包括2至12层半导体层t。半导体层t1与上述存储元件10具有相似的结构。然,为简要起见,在图6a、图6b与图6c中仅绘出两个绝缘墙st’(例如st0、st1)以及单一个区块blk’(例如blk0’)。

102.请参照图6a与图6b,半导体层t2与半导体层t1具有相似的结构。半导体层t2包括以多个绝缘墙st’(例如st0’、st1’)分隔开的多个在各区块blk’(例如blk0’)中的多个存储单元组mct’(例如mct0’),多个存储单元组mct’的结构与排列方式可与各区块blk中的多个存储单元组mct的结构与排列方式相同或相似。半导体层t2包括多个存储单元组mct’。每一个存储单元组mct’包括在第三方向d3上两个叠置的第三存储单元m_b’与第四存储单元m_t’。

103.请参照图6a,半导体层t2还包括在第一方向d1延伸的多条位线bl_b’与多条位线bl_t’。位线bl_b’例如是包括bl0_b’、bl1_b’、bl2_b’、bl3_b’、bl4_b’,或更多的位线。位线

bl_t’例如是包括bl0_t’、bl1_t’、bl2_t’、bl3_t’、bl4_t’,或更多的位线。半导体层t2的每一位线bl_b’位于半导体层t1的位线bl_t上,半导体层t2的每一位线bl_t’位于位线bl_b’上。半导体层t1的位线bl_b、bl_t与半导体层t2的bl_b’、bl_t’的末端可以呈阶梯状。位线bl_b经由位线接触窗blc0与金属层ml连接。在本实施例中,位线bl_t、bl_b’可以共用,其可经由位线接触窗blc2与金属层ml连接。位线bl_t’经由位线接触窗blc3与金属层ml连接。

104.请参照图6a与图6c,半导体层t2还包括在第二方向d2延伸的字线wl00’与字线wl01’以及源极线sl0’。在第二区r2中,半导体层t1的字线wl00的末端经由字线接触窗wlc0与金属层ml连接。字线wl01的末端经由字线接触窗wlc1与金属层ml连接。源极线sl0的末端经由源极线接触窗slc与金属层ml连接。半导体层t2的字线wl00’的末端经由字线接触窗wlc0’与金属层ml连接。字线wl01’的末端经由字线接触窗wlc1’与金属层ml连接。源极线sl0’的末端经由源极线接触窗slc’与金属层ml连接。

105.字线wl00的末端、源极线sl0的末端、字线wl01的末端、字线wl00’的末端、源极线sl0’的末端、字线wl01’的末端设置在区块blk0的第二区r2,且可以呈阶梯状。此外,在第二区r2中还可包括多个虚设柱dp’,以提供工艺中结构的支撑性,避免层或结构的塌陷。虚设柱dp’的结构可与虚设柱dp相似。

106.图7绘示出图6c的等效电路图。请参照图6c与图7,存储单元m_b包括栅极g0、源极s、漏极d0、电荷储存结构140b以及通道柱cp。存储单元m_t包括栅极g1、源极s、漏极d1、电荷储存结构140t以及通道柱cp。存储单元m_b’包括栅极g0’、源极s’、漏极d0’、电荷储存结构140b’以及通道柱cp’。存储单元m_t’包括栅极g1’、源极s’、漏极d1’、电荷储存结构140t’以及通道柱cp’。存储单元m_b’与存储单元m_t’共用源极s’。存储单元m_b’的漏极d0’与存储单元m_t的漏极d1共用。电荷储存结构140b’和电荷储存结构140t’彼此分离,其合称为电荷储存结构140’。

107.三维存储元件10’的制造方法可以依照上述方法形成半导体元件10完成第一半导体层t1的制作。之后,进行循环工艺即可完成第二半导体层t2的制作。所述至少一循环工艺包括重复图3a中形成第一叠层结构110、导体层120以及第二叠层结构130的步骤至图3j的形成多条位线bl_t,和/或依据图4a与图4b。

108.综上所述,本发明的异或(nor)闪存存储元件在单位面积内包括纵向叠置的两个存储单元,可以有效利用基底的面积。本发明的三维nor快闪存储元件在单位面积内可以包括纵向叠置的多个个存储单元,可以有效利用基底的面积。此外,本发明的nor闪存存储元件以及三维nor闪存存储元件的工艺可与现有工艺相容。

109.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1