具有横向绝缘栅极双极性晶体管的功率元件及其制造方法与流程

1.本发明涉及一种功率元件,特别是指一种具有横向绝缘栅极双极性晶体管(lateral insulated gate bipolar transistor,ligbt)的功率元件。本发明还涉及功率元件的制造方法。

背景技术:

2.图1a与图1b显示一种现有技术的具有横向绝缘栅极双极性晶体管(lateral insulated gate bipolar transistor,ligbt)的功率元件(功率元件100)的俯视示意图与剖视示意图。功率元件100用以控制飞轮马达中的飞轮电流;其中飞轮电流流经功率元件100后,以驱动飞轮马达。其中,飞轮马达用以控制飞轮(flywheel),以于飞轮的旋转运动中储存旋转动能,其为本领域技术人员所熟知,在此不予赘述。一般而言,功率元件100包含多个彼此并联的ligbt,以及一个pn二极管,其中pn二极管与多个ligbt并联。由于pn二极管会产生高的反向恢复电荷(reverse recovery charge,qrr),使得功率元件100的切换速度受到限制,并产生不可忽视的功率损耗与相对于金属氧化半导体(metal oxide semiconductor,mos)功率元件较低的电能转换效率。

3.如图1a与图1b所示,功率元件100形成于半导体基板11上,其包含彼此并联的横向绝缘栅极双极性晶体管ligbt1及ligbt2以及pn二极管pn1。图1b显示图1a中,剖线aa’的剖视示意图。pn二极管pn1包括第一场氧化区121、第一n型区131、第一n型延伸区141、第一p型区151、第一栅极161、反向端171以及顺向端181;其中,第一n型区131、第一n型延伸区141、第一p型区151、反向端171以及顺向端181都形成于第一绝缘底层12上的一外延层中。第一绝缘结构iso1包括第一绝缘底层12以及第一绝缘侧壁123,其中第一绝缘底层12形成于半导体基板11上并连接于半导体基板11。第一绝缘结构iso1在外延层的上表面下,封闭式地包围pn二极管pn1,使pn二极管pn1在外延层的上表面下,电气隔绝其他元件。

4.横向绝缘栅极双极性晶体管ligbt1及ligbt2并联,都形成于半导体基板11上,且结构相同。其中,如图1a与图1b所示,横向绝缘栅极双极性晶体管ligbt2包括第二场氧化区122、第二n型区132、第二n型延伸区142、第二p型区152、第二栅极162、漏极172、发射极182以及p型接触极184;其中,第二n型区132、第二n型延伸区142、第二p型区152、漏极172、发射极182以及p型接触极184形成于第二绝缘底层12’上的该外延层中。第二绝缘结构iso2包括第二绝缘底层12’以及第二绝缘侧壁124,其中第二绝缘结构iso2在外延层的上表面下,封闭式地包围横向绝缘栅极双极性晶体管ligbt1与ligbt2,使横向绝缘栅极双极性晶体管ligbt1与ligbt2在外延层的上表面下,电气隔绝其他元件。横向绝缘栅极双极性晶体管ligbt1与横向绝缘栅极双极性晶体管ligbt2结构上完全相同,以彼此并联方式电连接。如图1a所示,第三绝缘侧壁125形成环状封闭侧壁,将第一绝缘侧壁123与第二绝缘侧壁124包围于其中,也就是将功率元件100包围于第三绝缘侧壁125所形成的环状封闭侧壁中。

5.如前所述,以功率元件100控制飞轮马达中的飞轮电流,由于pn二极管pn1会产生高的反向恢复电荷(reverse recovery charge,qrr),使得功率元件100的切换速度受到限

制,并产生不可忽视的功率损耗与相对较低的电能转换效率。

6.有鉴于此,本发明即针对上述现有技术的不足,提出一种具有横向绝缘栅极双极性晶体管的功率元件及其制造方法,可降低qrr提高功率元件100的切换速度,又可以降低功率消耗,以提高电能转换效率。

技术实现要素:

7.就其中一个观点言,本发明提供了一种功率元件,包含:多个横向绝缘栅极双极性晶体管(lateral insulated gate bipolar transistor,ligbt),彼此并联;以及一顺向导通单元,与该多个横向绝缘栅极双极性晶体管并联,该顺向导通单元由一pn二极管与一肖特基二极管并联形成;其中该pn二极管与该肖特基二极管共享一第一n型区、一反向端、一第一n型延伸区、一第一场氧化区、一第一栅极以及一第一p型区;其中该第一n型区、该反向端、该第一n型延伸区以及该第一p型区形成于该半导体基板上的一外延层中;其中该第一n型区与该第一p型区形成一pn结,由俯视图视之,该pn接面具有一交错的梳齿交界面(staggered comb-teeth interface);其中一金属导线于该交错的梳齿交界面正上方延伸,交错接触下方的该第一n型区与该第一p型区。

8.就另一观点言,本发明提供了一种功率元件制造方法,其中该功率元件形成于一半导体基板上,该功率元件制造方法包含:形成彼此并联的多个横向绝缘栅极双极性晶体管(lateral insulated gate bipolar transistor,ligbt);以及形成一顺向导通单元,与该多个横向绝缘栅极双极性晶体管并联,其中该顺向导通单元由一pn二极管与一肖特基二极管并联所形成;其中该pn二极管与该肖特基二极管共享一第一n型区、一反向端、一第一n型延伸区、一第一场氧化区、一第一栅极以及一第一p型区;其中该第一n型区、该反向端、该第一n型延伸区以及该第一p型区形成于该半导体基板上的一外延层中;其中该第一n型区与该第一p型区形成一pn结,由俯视图视之,该pn接面具有一交错的梳齿交界面(staggered comb-teeth interface);其中一金属导线于该交错的梳齿交界面正上方延伸,交错接触下方的该第一n型区与该第一p型区。

9.在一种较佳的实施型态中,该横向绝缘栅极双极性晶体管的一发射极与一漏极分别与该顺向导通单元的一顺向端与该反向端对应电连接。

10.在一种较佳的实施型态中,该顺向导通单元的底面与侧面由一第一绝缘结构所包围,且该多个横向绝缘栅极双极性晶体管的底面与侧面由一第二绝缘结构所包围。

11.在一种较佳的实施型态中,该横向绝缘栅极双极性晶体管包括:一第二n型区,形成于该半导体基板上的该外延层中;一第二p型区,形成于该外延层中;一发射极,具有n型导电型,形成于该第二p型区中;一p型接触极,形成于该第二p型区中,以作为该第二p型区的电气接点;一第二栅极,形成于该外延层上,其中部分该第二栅极连接于该第二p型区之上;一第二n型延伸区,形成于该第二n型区中,且该第二n型延伸区与该第二p型区由该第二n型区隔开;一漏极,具有p型导电型,形成于该第二n型延伸区中;以及一第二场氧化区,形成于该外延层上,位于该发射极与该漏极之间。

12.在一种较佳的实施型态中,该第一n型延伸区与该第二n型延伸区、该第一p型区与该第二p型区、该反向端与该发射极,分别由对应相同的微影工艺步骤与离子注入工艺步骤同时形成;其中该第一栅极与该第二栅极由相同的一栅极工艺步骤同时形成;其中该第一

场氧化区与该第二场氧化区由相同的一氧化工艺步骤同时形成。

13.在一种较佳的实施型态中,该第一栅极于该交错的梳齿交界面正上方延伸,交错接触下方的该第一n型区与该第一p型区,其中该第一栅极与该金属导线平行排列且不直接接触。

14.在一种较佳的实施型态中,该半导体基板上由一绝缘层完全接触覆盖,且该外延层形成并接触于该绝缘层上,部分该绝缘层用以作为该第一绝缘结构的一第一绝缘底层,且另一部分该绝缘层用以作为该第二绝缘结构的一第二绝缘底层。

15.在一种较佳的实施型态中,该外延层具有n型导电型,且部分该外延层用以作为该第一n型区,且另一部分该外延层用以作为该第二n型区。

16.在一种较佳的实施型态中,该外延层具有p型导电型,且该第一n型区与该第二n型区由相同的微影工艺步骤与离子注入工艺步骤同时形成。

17.以下通过具体实施例详加说明,应当更容易了解本发明的目的、技术内容、特点及其所实现的功效。

附图说明

18.图1a与图1b显示一种现有技术的具有横向绝缘栅极双极性晶体管(lateral insulated gate bipolar transistor,ligbt)的功率元件(功率元件100)的俯视示意图与剖视示意图。

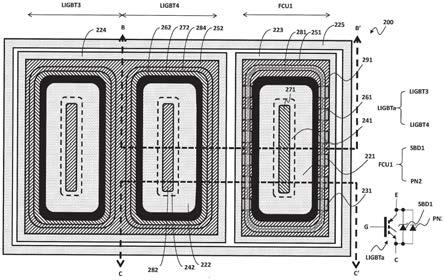

19.图2a-图2c显示根据本发明的功率元件的一种实施方式示意图。

20.图3显示根据本发明的一种实施方式的俯视示意图,其显示pn结具有交错的梳齿交界面(staggered comb-teeth interface);其中金属导线291于交错的梳齿交界面正上方延伸,交错接触下方的n型区231与p型区251。

21.图4a-图4c显示根据本发明的功率元件的另一种实施方式示意图。

22.图5a-图5c显示根据本发明的功率元件的又一种实施方式示意图。

23.图6a-图6r显示根据本发明的功率元件的制造方法的一种实施方式示意图。

24.图中符号说明

25.200,400,500:功率元件

26.121,221,421,521:第一场氧化区

27.122,222,422,522:第二场氧化区

28.123,223,423,523:第一绝缘侧壁

29.124,224,424,524:第二绝缘侧壁

30.125,225,425,525:第三绝缘侧壁

31.131,231,431,531:第一n型区

32.141,241,441,541:第一n型延伸区

33.132,232,432,532:第二n型区

34.142,242,442,542:第二n型延伸区

35.151,251,451,551:第一p型区

36.152,252,452,552:第二p型区

37.161,261,462,562:第一栅极

38.162,262,462,562:第二栅极

39.171,271,471,571:反向端

40.172,272,472,572:漏极

41.181,281,481,581:顺向端

42.182,282,482,582:发射极

43.184,284,484,584:p型接触极

44.291,491,591:金属导线

45.aa’,bb’,cc’,dd’,ee’,ff’,gg’:剖线

46.c:漏极

47.e:发射极

48.f:顺向端

49.fcu1,fcu2,fcu3:顺向导通单元

50.g:栅极

51.igbta,igbtb,igbtc:横向绝缘栅极双极性晶体管单元

52.ligbt1,ligbt2,ligbt3,ligbt4,ligbt5,lighb6,ligbt7,ligbt8:横向绝缘栅极双极性晶体管

53.pn1,pn2,pn3,pn4:pn二极管

54.r:反向端

55.sbd1,sdb2,sbd3:肖特基二极管

具体实施方式

56.涉及本发明的前述及其他技术内容、特点与功效,在以下配合参考附图的较佳实施例的详细说明中,将可清楚地呈现。本发明中的附图均属示意,主要意在表示工艺步骤以及各层之间的上下次序关系,至于形状、厚度与宽度则并未依照比例绘制。

57.图2a-图2c显示根据本发明的功率元件的一种实施方式示意图。如图2a-图2c所示,功率元件200形成于半导体基板21上,其包含彼此并联的横向绝缘栅极双极性晶体管ligbt3及ligbt4以及顺向导通单元fcu1。图2b与图2c分别显示图2a中,剖线bb’与剖线cc’的剖视示意图。其中,并联的横向绝缘栅极双极性晶体管ligbt3及ligbt4组成一个横向绝缘栅极双极性晶体管单元igbta;且顺向导通单元fcu1由一个pn二极管pn2与一个肖特基二极管sbd1并联形成。在功率元件200中,横向绝缘栅极双极性晶体管单元igbta与顺向导通单元fcu1的耦接方式,如图2a中的电路符号小图所示意,其中,横向绝缘栅极双极性晶体管单元igbta具有栅极g、发射极e与漏极c;导通单元fcu1具有顺向端f与反向端r。顺向导通单元fcu1与横向绝缘栅极双极性晶体管ligbt3及ligbt4并联。其中,横向绝缘栅极双极性晶体管单元igbta的漏极c与发射极e分别与顺向导通单元fcu1的顺向端f与反向端r对应电连接。

58.根据本发明,横向绝缘栅极双极性晶体管单元igbta不限于由两个横向绝缘栅极双极性晶体管ligbt3及ligbt4组成,也可以由3个或以上的横向绝缘栅极双极性晶体管并联组成。根据本发明,顺向导通单元也可以是多个,在一种较佳的实施例中,顺向导通单元的数量少于横向绝缘栅极双极性晶体管的数量。

59.其中,顺向导通单元fcu1包括第一场氧化区221、第一n型区231、第一n型延伸区241、第一p型区251、第一栅极261、反向端271以及顺向端281。顺向导通单元fcu1的底面与侧面由第一绝缘结构iso3所包围。其中,第一绝缘结构iso3包括第一绝缘底层22以及第一绝缘侧壁223。

60.其中顺向导通单元fcu1中的pn二极管pn2与肖特基二极管sbd1共享第一n型区231、反向端271、第一n型延伸区241、第一场氧化区221、第一栅极261以及第一p型区251。其中第一n型区231与第一p型区251形成pn结,由俯视图视之(请参阅图3),该pn结具有交错的梳齿交界面(staggered comb-teeth interface),如图3中粗黑虚线所示意。其中金属导线291于该交错的梳齿交界面正上方延伸,交错接触下方的第一n型区231与第一p型区251。

61.横向绝缘栅极双极性晶体管ligbt3及ligbt4并联,都形成于半导体基板21上,且结构相同。其中,如图2a-图2c所示,横向绝缘栅极双极性晶体管ligbt4包括第二场氧化区222、第二n型区232、第二n型延伸区242、第二p型区252、第二栅极262、漏极272、发射极282以及p型接触极284。横向绝缘栅极双极性晶体管ligbt3及ligbt4的底面与侧面由第二绝缘结构iso4所包围。其中,第二绝缘结构iso4包括第二绝缘底层22’以及第二绝缘侧壁224。横向绝缘栅极双极性晶体管ligbt3与横向绝缘栅极双极性晶体管ligbt4结构上完全相同,以彼此并联方式电连接,也就是横向绝缘栅极双极性晶体管ligbt3中的第二栅极、漏极、发射极以及p型接触极分别电连接横向绝缘栅极双极性晶体管ligbt4的第二栅极262、漏极272、发射极282以及p型接触极284。

62.因此,前述横向绝缘栅极双极性晶体管单元igbta的漏极c与发射极e分别与顺向导通单元fcu1的顺向端f与反向端r对应电连接,是指漏极272与顺向端281电连接,发射极282与反向端271电连接。电连接的方式,可在外延层上方形成金属接触点与金属导线实现,此为本领域技术人员所熟知,在此不予赘述。

63.如图2a所示,第三绝缘侧壁225形成环状封闭侧壁,将第一绝缘侧壁223与第二绝缘侧壁224包围于其中,也就是将功率元件200包围于第三绝缘侧壁225所形成的环状封闭侧壁中。其中,横向绝缘栅极双极性晶体管ligbt3及ligbt4的发射极与漏极分别与顺向导通单元fcu1的顺向端281与反向端271对应电连接。

64.其中,第一绝缘底层22与第二绝缘底层22’形成于半导体基板21上。半导体基板21例如但不限于为p型或n型的半导体硅基板,也可以为其他半导体基板。例如于半导体基板21上形成二氧化硅层,部分作为第一绝缘底层22,另一部分作为第二绝缘底层22’。于该二氧化硅层上,例如形成n型外延层,部分作为第一n型区231,另一部分作为第二n型区232。前述半导体基板21、二氧化硅层与n型外延层可以采用绝缘层上硅(silicon on insulator,soi)晶圆来实现,其为本领域技术人员所熟知,在此不予赘述。

65.第一绝缘侧壁223、第二绝缘侧壁224与第三绝缘侧壁225例如但不限于由相同的深沟蚀刻工艺步骤,同时形成深沟;并且由相同的沉积工艺步骤,同时将绝缘材质,例如但不限于二氧化硅等,沉积于前述的深沟中,以形成第一绝缘侧壁223、第二绝缘侧壁224与第三绝缘侧壁225。且第一绝缘侧壁223、第二绝缘侧壁224与第三绝缘侧壁225与下方的连接于半导体基板21上的二氧化硅层连接,以于外延层中,分别形成封闭的范围。其中,在一种较佳的实施例中,顺向导通单元fcu1的底面与侧面由第一绝缘结构iso3所包围,且多个横向绝缘栅极双极性晶体管ligbt3、ligbt4的底面与侧面由第二绝缘结构iso4所包围。

66.请继续参阅图2a-图2c,其中,第一n型延伸区241与第二n型延伸区242形成于半导体基板21的外延层中。其中,第二n型延伸区242形成于第二n型区232中,且第二n型延伸区242与第二p型区252由第二n型区242隔开。例如但不限于由相同的微影工艺步骤,同时定义第一n型延伸区241与第二n型延伸区242的区域;并且由相同的离子注入工艺步骤,同时将n型杂质,以加速离子的形式,注入由前述的微影工艺步骤所定义的区域,以形成第一n型延伸区241与第二n型延伸区242。第一n型延伸区241与第二n型延伸区242具有n型导电型,形成于前述n型外延层中,且位于n型外延层上表面下并连接于上表面。

67.第一场氧化区221与第二场氧化区222例如但不限于由相同的氧化工艺步骤,同时形成于前述n型外延层上表面上并连接于上表面。第一场氧化区221与第二场氧化区222并不限于如图2b与图2c所示的区域氧化(local oxidation of silicon,locos)结构,也可为浅沟槽绝缘(shallow trench isolation,sti)结构。如图2a所示,第一场氧化区221与第二场氧化区222由俯视图视之,例如为环形封闭结构,分别包围部分第一n型延伸区241与第二n型延伸区242。第一场氧化区221位于顺向端281与反向端271之间。第二场氧化区222位于发射极282与漏极272之间。

68.第一p型区251与第二p型区252例如但不限于由相同的微影工艺步骤,同时定义第一p型区251与第二p型区252的区域;并且由相同的离子注入工艺步骤,同时将p型杂质,以加速离子的形式,注入由前述的微影工艺步骤所定义的区域,以形成第一p型区251与第二p型区252。第一p型区251与第二p型区252具有p型导电型,形成于前述n型外延层中,且位于n型外延层上表面下并连接于上表面。如图2a所示,第一p型区251与第二p型区252由俯视图视之,例如为环形封闭区域,分别包围第一场氧化区221与第二场氧化区222。其中,如俯视图图2a所示,并参阅俯视图图3,第一p型区251侧面的边界具有梳齿状边界,以与第一n型区231形成具有交错的梳齿交界面(staggered comb-teeth interface)的pn结,如图3中粗黑虚线所示意。图2b所示的剖线bb’的剖视示意图,显示剖线bb’经过第一p型区251正上方,而图2c所示的剖线cc’的剖视示意图,显示剖线cc’未经过第一p型区251正上方。

69.如图2a所示,第一栅极261与第二栅极262由俯视图视之,例如都为环形封闭区域。由俯视图图2a视之,第一栅极261形成并接触于部分第一场氧化区221上,并环绕其他部分第一场氧化区221。由俯视图图2a视之,第二栅极262形成并接触于部分第二场氧化区222之上,并环绕其他部分第二场氧化区222。

70.第一栅极261与第二栅极262例如但不限于由相同的栅极工艺步骤同时形成于该外延层上。部分第一栅极261与部分第二栅极262分别连接于第一p型区251之上与第二p型区252之上;另一部分第一栅极261与另一部分第二栅极262分别连接于第一场氧化区221之上与第二场氧化区222之上。其中,第一栅极261与第二栅极262例如分别包括各自的介电层(dielectric layer)、导电层(conductive layer)与间隔层(spacer layer),此为本领域技术人员所熟知,在此不予赘述。因此,所述栅极工艺步骤包含形成介电层的微影、氧化等工艺步骤;形成导电层的微影、沉积等工艺步骤;以及形成间隔层的沉积、蚀刻等工艺步骤。

71.在本实施例中,第一栅极261于该交错的梳齿交界面正上方延伸,交错接触下方的第一n型区231与第一p型区251,其中第一栅极261与金属导线291平行排列且不直接接触。

72.顺向端281、发射极282与p型接触极284例如但不限于由相同的微影工艺步骤,同时定义顺向端281、发射极282与p型接触极284的区域;并且由相同的离子注入工艺步骤,同

时将p型杂质,以加速离子的形式,注入由前述的微影工艺步骤所定义的区域,以形成顺向端281、发射极282与p型接触极284。顺向端281、发射极282与p型接触极284具有p型导电型,分别形成于第一p型区251、第二n型延伸区242与第二p型区252中,且位于n型外延层上表面下并连接于上表面。如图2a所示,顺向端281与p型接触极284由俯视图视之,例如都为环形封闭区域,分别包围第一栅极261与漏极272。p型接触极284用以作为第二p型区252的电气接点。

73.反向端271与漏极272例如但不限于由相同的微影工艺步骤(包含以栅极262作为屏蔽),同时定义反向端271与漏极272的区域;并且由相同的离子注入工艺步骤,同时将n型杂质,以加速离子的形式,注入由前述的微影工艺步骤所定义的区域,以形成反向端271与漏极272于第一n型延伸区241与第二n型延伸区242中。反向端271与漏极272具有n型导电型,形成于前述n型外延层中,且位于n型外延层上表面下并连接于上表面。如图2a所示,漏极272由俯视图视之,例如为环形封闭区域,包围第二栅极262。

74.本发明优于现有技术的处,以本实施例来说,不仅是将肖特基二极管与pn二极管并联后,再与横向绝缘栅极双极性晶体管并联,以于功率元件操作时,降低反向恢复电荷,提高功率元件的切换速度,降低功率元件操作时的功率损耗,提高电能转换效;另外将肖特基二极管与pn二极管整合,肖特基二极管与pn二极管共享:n型区、反向端、n型延伸区、场氧化区、栅极以及p型区,因此并未增加功率元件的面积,即可实现技术效果。此外,由于功率元件需要耐受高达数百伏特的高压,因此,以本实施例来说,肖特基二极管sbd1的第一n型区231邻接pn二极管pn2的第一p型区251,可使肖特基二极管sbd1施以逆向偏压时,第一p型区251使肖特基二极管sbd1的第一n型区231完全耗尽而夹止(pinch off),降低肖特基二极管sbd1的漏电流。

75.图3显示根据本发明的一种实施方式的俯视示意图,其显示pn结具有交错的梳齿交界面(staggered comb-teeth interface);其中金属导线291于交错的梳齿交界面正上方延伸,交错接触下方的n型区231与p型区251。金属导线291于该交错的梳齿交界面正上方延伸,交错接触下方的第一n型区231与第一p型区251。金属导线291与第一n型区231形成肖特基接触,且金属导线291与第一p型区251形成奥姆接触。在本实施例中,第一栅极261于交错的梳齿交界面正上方延伸,交错接触下方的第一n型区231与第一p型区251,其中第一栅极261与金属导线291平行排列且不直接接触。

76.图4a-图4c显示根据本发明的功率元件的另一种实施方式示意图。如图4a-图4c所示,功率元件400形成于半导体基板41上,其包含彼此并联的横向绝缘栅极双极性晶体管ligbt5及ligbt6以及顺向导通单元fcu2。图4b与图4c分别显示图4a中,剖线dd’与剖线ee’的剖视示意图。其中,并联的横向绝缘栅极双极性晶体管ligbt5及ligbt6组成一个横向绝缘栅极双极性晶体管单元igbtb;且顺向导通单元fcu2由一个pn二极管pn3与一个肖特基二极管sbd2并联形成。在功率元件400中,横向绝缘栅极双极性晶体管单元igbtb与顺向导通单元fcu2的耦接方式,如图4a中的电路符号小图所示意,其中,横向绝缘栅极双极性晶体管单元igbtb具有栅极g、发射极e与漏极c;导通单元fcu2具有顺向端f与反向端r。顺向导通单元fcu2与横向绝缘栅极双极性晶体管ligbt5及ligbt6并联。其中,横向绝缘栅极双极性晶体管单元igbtb的漏极c与发射极e分别与顺向导通单元fcu2的顺向端f与反向端r对应电连接。

77.其中,顺向导通单元fcu2包括第一场氧化区421、第一n型区431、第一n型延伸区441、第一p型区451、第一栅极461、反向端471以及顺向端481。顺向导通单元fcu2的底面与侧面由第一绝缘结构iso5所包围。其中,第一绝缘结构iso5包括第一绝缘底层42以及第一绝缘侧壁423。

78.其中顺向导通单元fcu2中的pn二极管pn3与肖特基二极管sbd2共享第一n型区431、反向端471、第一n型延伸区441、第一场氧化区421、第一栅极461以及第一p型区451。其中第一n型区431与第一p型区451形成pn结,由俯视图视之,该pn结具有交错的梳齿交界面(staggered comb-teeth interface)。其中金属导线491于该交错的梳齿交界面正上方延伸,交错接触下方的第一n型区431与第一p型区451。

79.横向绝缘栅极双极性晶体管ligbt5及ligbt6并联,都形成于半导体基板41上,且结构相同。其中,如图4a-图4c所示,横向绝缘栅极双极性晶体管ligbt6包括第二场氧化区422、第二n型区432、第二n型延伸区442、第二p型区452、第二栅极462、漏极472、发射极482以及p型接触极484。横向绝缘栅极双极性晶体管ligbt5及ligbt6的底面与侧面由第二绝缘结构iso6所包围。其中,第二绝缘结构iso6包括第二绝缘底层42’以及第二绝缘侧壁424。横向绝缘栅极双极性晶体管ligbt5与横向绝缘栅极双极性晶体管ligbt6结构上完全相同,以彼此并联方式电连接,也就是横向绝缘栅极双极性晶体管ligbt5中的第二栅极、漏极、发射极以及p型接触极分别电连接横向绝缘栅极双极性晶体管ligbt6的第二栅极462、漏极472、发射极482以及p型接触极484。

80.因此,前述横向绝缘栅极双极性晶体管单元igbtb的漏极c与发射极e分别与顺向导通单元fcu2的顺向端f与反向端r对应电连接,是指漏极472与顺向端481电连接,发射极482与反向端471电连接。

81.如图4a所示,第三绝缘侧壁425形成环状封闭侧壁,将第一绝缘侧壁423与第二绝缘侧壁424包围于其中,也就是将功率元件400包围于第三绝缘侧壁425所形成的环状封闭侧壁中。

82.本实施例与图2a-图2c所示的实施例不同之处在于,在本实施例中,如图4a与图4c所示,金属导线291也可以于肖特基二极管sbd2中,接触顺向端481。在本实施例中,肖特基二极管sbd2的第一n型区431除了邻接pn二极管的第一p型区451,还使第一p型区451也整合于肖特基二极管sbd2中,邻接第一n型区431,也就是第一p型区451在两个方向,邻接第一n型区431,使得肖特基二极管sbd2在逆向偏压的操作时,更快地实现完全耗尽而夹止,降低漏电流。

83.图5a-图5c显示根据本发明的功率元件的另一种实施方式示意图。如图5a-图5c所示,功率元件500形成于半导体基板51上,其包含彼此并联的横向绝缘栅极双极性晶体管ligbt7及ligbt8以及顺向导通单元fcu3。图5b与图5c分别显示图5a中,剖线ff’与剖线gg’的剖视示意图。其中,并联的横向绝缘栅极双极性晶体管ligbt7及ligbt8组成一个横向绝缘栅极双极性晶体管单元igbtc;且顺向导通单元fcu3由一个pn二极管pn4与一个肖特基二极管sbd3并联形成。在功率元件500中,横向绝缘栅极双极性晶体管单元igbtc与顺向导通单元fcu3的耦接方式,如图5a中的电路符号小图所示意。其中,横向绝缘栅极双极性晶体管单元igbtc具有栅极g、发射极e与漏极c;导通单元fcu3具有顺向端f与反向端r。顺向导通单元fcu3与横向绝缘栅极双极性晶体管ligbt7及ligbt8并联。其中,横向绝缘栅极双极性晶

体管单元igbtc的漏极c与发射极e分别与顺向导通单元fcu3的顺向端f与反向端r对应电连接。

84.其中,顺向导通单元fcu3包括第一场氧化区521、第一n型区531、第一n型延伸区541、第一p型区551、第一栅极561、反向端571以及顺向端581。顺向导通单元fcu3的底面与侧面由第一绝缘结构iso7所包围。其中,第一绝缘结构iso7包括第一绝缘底层52以及第一绝缘侧壁523。

85.其中顺向导通单元fcu3中的pn二极管pn4与肖特基二极管sbd3共享第一n型区531、反向端571、第一n型延伸区541、第一场氧化区521、第一栅极561以及第一p型区551。其中第一n型区531与第一p型区551形成pn结,由俯视图视之,该pn结具有交错的梳齿交界面(staggered comb-teeth interface)。其中金属导线591于该交错的梳齿交界面正上方延伸,交错接触下方的第一n型区531与第一p型区551。

86.横向绝缘栅极双极性晶体管ligbt7及ligbt8并联,都形成于半导体基板51上,且结构相同。其中,如图5a-图5c所示,横向绝缘栅极双极性晶体管ligbt8包括第二场氧化区522、第二n型区532、第二n型延伸区542、第二p型区552、第二栅极562、漏极572、发射极582以及p型接触极584。横向绝缘栅极双极性晶体管ligbt7及ligbt8的底面与侧面由第二绝缘结构iso8所包围。其中,第二绝缘结构iso8包括第二绝缘底层52’以及第二绝缘侧壁524。横向绝缘栅极双极性晶体管ligbt7与横向绝缘栅极双极性晶体管ligbt8结构上完全相同,以彼此并联方式电连接,也就是横向绝缘栅极双极性晶体管ligbt7中的第二栅极、漏极、发射极以及p型接触极分别电连接横向绝缘栅极双极性晶体管ligbt8的第二栅极562、漏极572、发射极582以及p型接触极584。

87.因此,前述横向绝缘栅极双极性晶体管单元igbtc的漏极c与发射极e分别与顺向导通单元fcu3的顺向端f与反向端r对应电连接,是指漏极572与顺向端581电连接,发射极582与反向端571电连接。

88.如图5a所示,第三绝缘侧壁525形成环状封闭侧壁,将第一绝缘侧壁523与第二绝缘侧壁524包围于其中,也就是将功率元件500包围于第三绝缘侧壁525所形成的环状封闭侧壁中。

89.本实施例与图4a-图4c所示的实施例不同之处在于,在本实施例中,如图5b与图5c所示,在半导体基板51上形成二氧化硅层,部分作为第一绝缘底层52,另一部分作为第二绝缘底层52’。于该二氧化硅层上,例如并不是形成n型外延层,而是形成p型外延层;因此,第一n型区531与第二n型区532例如但不限于由相同的微影工艺步骤,同时定义第一n型区531与第二n型区532的区域;并且由相同的离子注入工艺步骤,同时将n型杂质,以加速离子的形式,注入由前述的微影工艺步骤所定义的区域,以形成第一n型区531与第二n型区532。

90.图6a-图6r显示根据本发明的功率元件200的制造方法的一种实施方式示意图。图6a、图6c、图6e、图6g、图6i、图6k、图6m、图6o以及图6q显示如图2b中,自剖线bb’视之的功率元件200制造方法的剖视示意图。图6b、图6d、图6f、图6h、图6j、图6l、图6n、图6p以及图6r显示如图2c中,自剖线cc’视之的功率元件200制造方法的剖视示意图。如图6a与图6b所示,首先形成第一绝缘底层22与第二绝缘底层22’形成于半导体基板21上。半导体基板21例如但不限于为p型或n型的半导体硅基板,也可以为其他半导体基板。例如于半导体基板21上形成二氧化硅层,部分作为第一绝缘底层22,另一部分作为第二绝缘底层22’。于该二氧化硅

层上,例如形成n型外延层,部分作为第一n型区231,另一部分作为第二n型区232。前述半导体基板21、二氧化硅层与n型外延层可以采用绝缘层上硅(silicon on insulator,soi)晶圆来实现,其为本领域技术人员所熟知,在此不予赘述。

91.接着,如图6c与图6d所示,形成第一绝缘侧壁223、第二绝缘侧壁224与第三绝缘侧壁225,其例如但不限于由相同的深沟蚀刻工艺步骤,同时形成深沟;并且由相同的沉积工艺步骤,同时将绝缘材质,例如但不限于二氧化硅等,沉积于前述的深沟中,以形成第一绝缘侧壁223、第二绝缘侧壁224与第三绝缘侧壁225。且第一绝缘侧壁223、第二绝缘侧壁224与第三绝缘侧壁225与下方的连接于半导体基板21上的二氧化硅层连接,以于外延层中,分别形成封闭的范围。其中,在一种较佳的实施例中,顺向导通单元fcu1的底面与侧面由第一绝缘结构iso3所包围,且多个横向绝缘栅极双极性晶体管ligbt3、ligbt4的底面与侧面由第二绝缘结构iso4所包围。

92.接着,如图6e与图6f所示,形成第一n型延伸区241与第二n型延伸区242,其例如但不限于由相同的微影工艺步骤,同时定义第一n型延伸区241与第二n型延伸区242的区域;并且由相同的离子注入工艺步骤,同时将n型杂质,以加速离子的形式,注入由前述的微影工艺步骤所定义的区域,以形成第一n型延伸区241与第二n型延伸区242。第一n型延伸区241与第二n型延伸区242具有n型导电型,形成于前述n型外延层中,且位于n型外延层上表面下并连接于上表面。

93.接着,如图6g与图6h所示,形成第一场氧化区221与第二场氧化区222,其例如但不限于由相同的氧化工艺步骤,同时形成于前述n型外延层上表面上并连接于上表面。第一场氧化区221与第二场氧化区222并不限于如图6g与6h所示的区域氧化(local oxidation of silicon,locos)结构,也可为浅沟槽绝缘(shallow trench isolation,sti)结构。请同时参阅图2a,第一场氧化区221与第二场氧化区222由俯视图图2a视之,例如为环形封闭结构,分别包围部分第一n型延伸区241与第二n型延伸区242。

94.接着,如图6i与图6j所示,形成第一p型区251与第二p型区252,其例如但不限于由相同的微影工艺步骤,同时定义第一p型区251与第二p型区252的区域;并且由相同的离子注入工艺步骤,同时将p型杂质,以加速离子的形式,注入由前述的微影工艺步骤所定义的区域,以形成第一p型区251与第二p型区252。第一p型区251与第二p型区252具有p型导电型,形成于前述n型外延层中,且位于n型外延层上表面下并连接于上表面。请同时参阅图2a,第一p型区251与第二p型区252由俯视图图2a视之,例如为环形封闭区域,分别包围第一场氧化区221与第二场氧化区222。其中,如俯视图图2a所示,并参阅俯视图图3,第一p型区251侧面的边界具有梳齿状边界,以与第一n型区231形成具有交错的梳齿交界面(staggered comb-teeth interface)的pn结,如图3中粗黑虚线所示意。图6i所示的剖线bb’的剖视示意图,显示剖线bb’经过第一p型区251正上方,而图6j所示的剖线cc’的剖视示意图,显示剖线cc’未经过第一p型区251正上方。

95.接着,如图6k与图6l所示,形成第一栅极261与第二栅极262由俯视图图2a视之,第一栅极261与第二栅极262例如都为环形封闭区域。第一栅极261与第二栅极262例如但不限于由相同的栅极工艺步骤同时形成。其中,第一栅极261与第二栅极262例如分别包括各自的介电层(dielectric layer)、导电层(conductive layer)与间隔层(spacer layer),此为本领域技术人员所熟知,在此不予赘述。因此,所述栅极工艺步骤包含形成介电层的微

影、氧化等工艺步骤;形成导电层的微影、沉积等工艺步骤;以及形成间隔层的沉积、蚀刻等工艺步骤。

96.在本实施例中,第一栅极261于该交错的梳齿交界面正上方延伸,交错接触下方的第一n型区231与第一p型区251,其中第一栅极261与金属导线291平行排列且不直接接触。

97.接着,如图6m与图6n所示,形成顺向端281、发射极282与p型接触极284,其例如但不限于由相同的微影工艺步骤,同时定义顺向端281、发射极282与p型接触极284的区域;并且由相同的离子注入工艺步骤,同时将p型杂质,以加速离子的形式,注入由前述的微影工艺步骤所定义的区域,以形成顺向端281、发射极282与p型接触极284。顺向端281、发射极282与p型接触极284具有p型导电型,分别形成于第一p型区251、第二n型延伸区242与第二p型区252中,且位于n型外延层上表面下并连接于上表面。请同时参阅俯视图图2a,顺向端281与p型接触极284由俯视图视之,例如都为环形封闭区域,分别包围第一栅极261与漏极272。

98.接着,如图6o与图6p所示,形成反向端271与漏极272,其例如但不限于由相同的微影工艺步骤(包含以栅极262作为屏蔽),同时定义反向端271与漏极272的区域;并且由相同的离子注入工艺步骤,同时将n型杂质,以加速离子的形式,注入由前述的微影工艺步骤所定义的区域,以形成反向端271与漏极272。反向端271与漏极272具有n型导电型,形成于前述n型外延层中,且位于n型外延层上表面下并连接于上表面。请同时参阅俯视图图2a,漏极272由俯视图视之,例如为环形封闭区域,包围第二栅极262。

99.接着,如图6q与图6r所示,形成金属导线291于该交错的梳齿交界面正上方延伸,交错接触下方的第一n型区231与第一p型区251。形成金属导线的步骤,例如但不限于以金属沉积工艺步骤形成;此外,也可以先在第一n型区231与第一p型区251上形成多个金属接触点与第一n型区231与第一p型区251接触,再于该多个金属接触点上形成金属导线,此为本领域技术人员所熟知,在此不予赘述。

100.以上已针对较佳实施例来说明本发明,但以上所述,仅为使本领域技术人员易于了解本发明的内容,并非用来限定本发明的权利范围。在本发明的相同精神下,本领域技术人员可以想到各种等效变化。例如,在不影响元件主要的特性下,可加入其他工艺步骤或结构,如深井区等;又如,微影工艺步骤并不限于光罩工艺步骤,也可包含电子束微影工艺步骤。凡此种种,都可根据本发明的教示类推而得。此外,所说明的各个实施例,并不限于单独应用,也可以组合应用,例如但不限于将两实施例并用。因此,本发明的范围应涵盖上述及其他所有等效变化。此外,本发明的任一实施型态不必须实现所有的目的或优点,因此,权利要求任一项也不应以此为限。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1