半导体装置及其制造方法与流程

1.本发明涉及一种集成电路及其制造方法,且特别是涉及一种半导体装置及其制造方法。

背景技术:

2.在半导体工艺中,特别是装置不断地小型化之后,对准的精确度愈来愈重要。在晶背上制作构件时,必须具有穿硅对准(through silicon alignment,tsa)的能力,方可使光掩模与对准标记对准。然而,若有较厚的薄化衬底的需求时,将因为较厚的硅衬底的透明度过低难以对准,而无法具有足够的穿硅对准的能力。

技术实现要素:

3.本发明是针对一种半导体装置及其制造方法,可以提升晶背的对准能力。

4.根据本发明的实施例,提出一种半导体装置的制造方法,包括:提供衬底,所述衬底包括第一区与第二区;在所述衬底的所述第一区与所述第二区的第一表面上形成材料层,并在所述衬底的所述第二区的所述第一表面上形成对准标记;自所述衬底的第二表面将杂原子引入所述第二区的所述衬底中;以及使所述杂原子与所述衬底反应,以在所述第二区的所述衬底中形成与所述对准标记重叠的介电层。

5.根据本发明实施例所述,所述的半导体装置的制造方法还包括在所述自所述第二区的所述衬底的第二表面将杂原子引入所述衬底中之前,对所述衬底进行薄化工艺。

6.根据本发明实施例所述,所述杂原子包括氧、氮或其组合。

7.根据本发明实施例所述,所述介电层的折射率的n值小于1.5。

8.根据本发明实施例所述,所述使所述杂原子与所述衬底反应的方法包括进行热工艺或退火工艺。

9.根据本发明实施例所述,所述介电层与所述对准标记接触。

10.根据本发明实施例所述,所述介电层与所述对准标记被部分的所述衬底分隔。

11.本发明的实施例提出一种半导体装置的制造方法,包括:提供衬底,所述衬底包括第一区与第二区;自所述衬底的第一表面将杂原子引入所述第二区的所述衬底中;在所述第一区与所述第二区的所述衬底的所述第一表面上形成材料层,并在所述第二区的所述衬底中形成对准标记;以及使所述杂原子与所述衬底反应,以在所述第二区的所述衬底中形成与所述对准标记重叠的介电层。

12.根据本发明实施例所述,自所述衬底的第一表面将杂原子引入所述第二区的所述衬底中的方法包括:在所述衬底的所述第一表面上形成掩模层;进行所述衬底的缺角对准;将所述掩模层图案化,以在所述第二区的所述掩模层中形成开口,所述开口与所述对准标记对应;进行离子注入工艺;以及移除所述掩模层。

13.根据本发明实施例所述,所述杂原子包括氧、氮或其组合。

14.根据本发明实施例所述,所述使所述杂原子与所述衬底反应的方法包括进行热工

艺或是退火工艺。

15.根据本发明实施例所述,所述介电层与所述对准标记接触。

16.根据本发明实施例所述,所述介电层与所述对准标记被部分的所述衬底分隔。

17.本发明的实施例提出一种半导体装置,其特征在于包括:衬底,包括第一区与第二区;隔离结构,在所述第二区的所述衬底的中,自所述衬底的第一表面向所述衬底的第二表面延伸;对准标记,在所述第二区的所述衬底的中,自所述衬底的第一表面向所述衬底的第二表面延伸且与所述隔离结构在相同的水平高度;以及介电层,在所述第二区的所述衬底中且与所述对准标记重叠,其中在所述第二区的所述衬底的所述第一表面至所述第二表面之间的所述衬底的厚度小于在所述第一区的所述衬底的所述第一表面至所述第二表面之间的所述衬底的厚度。

18.根据本发明实施例所述,所述第一区与所述第二区均在芯片区中。

19.根据本发明实施例所述,所述介电层的折射率的n值小于1.5。

20.根据本发明实施例所述,所述介电层包括氧化硅、氮氧化硅或其组合。

21.根据本发明实施例所述,所述介电层与对准标记接触,或被所述衬底分隔。

22.根据本发明实施例所述,所述介电层的面积大于所述对准标记的面积根据本发明实施例所述,所述介电层与对准标记被所述衬底分隔。

23.基于上述,本发明的半导体装置及其制造方法,可以使得衬底保有足够的厚度,并且可提升晶背对准的精确度。

附图说明

24.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

25.图1a至图1h为本发明第一实施例的一种半导体装置的制造方法的流程剖面示意图;

26.图2为图1e中第二区的俯视图;

27.图3a至图3d为本发明第二实施例的一种半导体装置的制造方法的流程剖面示意图;

28.图4a至图4h为本发明第三实施例的一种半导体装置的制造方法的流程剖面示意图;

29.图5a至图5b为本发明第四实施例的一种半导体装置的制造方法的流程剖面示意图;

30.图6为一种半导体装置的制造方法的流程图;

31.图7为另一种半导体装置的制造方法的流程图。

具体实施方式

32.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

33.图1a至图1h绘示本发明第一实施例的一种半导体装置的制造方法的流程剖面示意图。图6绘示一种半导体装置的制造方法的流程图。

34.请参照图1a,提供衬底10。衬底10包括第一区r1与第二区r2。在一些实施例中,第一区r1为芯片区;第二区r2为切割道。在另一实施例中,第一区r1与第二区r2均为芯片区中相邻的两个区。衬底10可以是掺杂硅衬底、未掺杂硅衬底、绝缘体上覆硅(soi)衬底或外延衬底。掺杂硅的掺质可以为p型掺质、n型掺质或其组合。

35.请参照图1a与图6的动作s10,在第一区r1的衬底10内形成隔离结构12,以在衬底10中界定出有源区,并在第二区r2的衬底10内形成对准标记14。隔离结构12与对准标记14的材料可以相同或是相异。隔离结构12与对准标记14包括绝缘材料,例如是氧化硅、氮化硅或其组合。隔离结构12与对准标记14可以通过浅沟槽隔离法形成。在一些实施例中,隔离结构12与对准标记14自衬底10的表面10-1向衬底10的表面10-2’延伸,在相同的水平高度且具有相同的深度,但不以此为限。衬底10的表面10-1又可称为正面,表面10-2’又可称为背面。

36.请参照图1a与图2,第二区r2的对准标记14可以具有各种形状。举例来说,对准标记14可以包括多组结构,每一组结构包括多个彼此分隔且平行的条状物,且这一些条状物与衬底10相互交替设置,但不以此为限。

37.接着,请参照图1a与图6的动作s12,在衬底10的表面10-1上形成材料层16。表面10-1又可称为第一表面10-1。材料层16可以包括装置层与金属内连结构。装置层例如是有源装置或是无源装置。有源装置例如是晶体管、二极管或其组合。无源装置例如是电阻、电容、电感或其组合。金属内连结构用来连接装置层中的装置。金属内连结构可以包括多个介电层与多个导电特征。导电特征可连接装置层中两个或更多个装置。导电特征包括接触窗、多个介层窗与多个导线等。多个导线在与衬底10的表面10-1平行的平面上延伸,多个介层窗与衬底10的表面10-1垂直的方向上延伸,以连接纵向上相邻的两条导线。

38.在一些实施例中,在形成隔离结构12与对准标记14之前,或是在形成隔离结构12与对准标记14之后且在形成材料层16之前,还可以包括各种步骤。举例来说,可以在衬底10中形成各种p型或是n型导电型的阱区、深阱区、掺杂区等工艺。

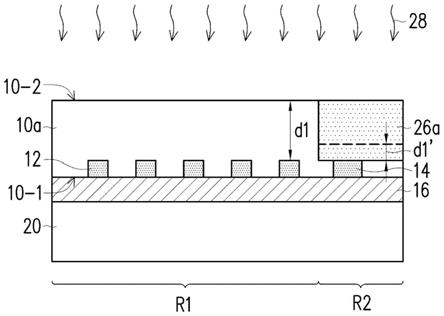

39.请参照图1b与图6的动作s14,将处理晶片(handling wafer)20置于衬底10的材料层16上。处理晶片20可以通过粘着层(未示出)粘着于材料层16上。粘着层可以是有机材料或是聚合物材料。

40.请参照图1c与图1d以及图6的动作s16与s18,将衬底10翻转,使衬底10a的表面10-2’朝上。接着,自衬底10的表面10-2’对衬底10a进行薄化工艺,以形成厚度薄化的衬底10a。衬底10a的表面10-2又可称为第二表面或背面。衬底10a的表面10-2与隔离结构12的表面之间的距离d1或是衬底10a的表面10-2与对准标记14的表面之间的距离d1大于4μm,例如是介于4μm至20μm之间,或更大。

41.请照图1e、图2与图6的动作s20,在衬底10a的表面10-2上形成具有开口23的图案化的掩模层22。开口23裸露出第二区r2的衬底10a的表面10-2。开口23的位置与对准标记14的位置重叠,且开口23的面积大于对准标记14的面积,而将对准标记14涵盖其中,如图2所示。图案化的掩模层22的形成方法例如是可以采用以下所述的步骤来进行。

42.请参照图1e与图6动作s201至s203。将掩模层(例如是光刻胶层)涂布于衬底10a的表面10-2上,再对掩模层(例如是光刻胶层)进行烘烤。之后,通过衬底10a本身的缺口(notch)来进行缺口对准工艺。由于欲形成的开口23只要能涵盖第二区r2中的对准标记14,

其所需的精确度较低,因此,通过缺口对准工艺即可以达到所需的精确度。之后,经由曝光与显影工艺进行图案化工艺,以在掩模层22(例如是光刻胶层)中形成开口23。

43.接着,请参照图1e与图6动作s22,以掩模层22为掩模,进行离子注入工艺24,将杂原子自衬底10a的表面10-2引入第二区r2的衬底10a中,以形成具有杂原子的掺杂区26。掺杂区26中的杂原子分布在衬底10a的表面10-2与对准标记14之间。杂原子例如是氧、氮或其组合。杂原子的剂量例如是10

13

至10

20

/cm2。

44.请参照图1f与图6的动作s24与s28。移除图案化的掩模层22。其后,进行退火工艺28,以使掺杂区26中的杂原子与衬底10a中的硅反应,以在第二区r2的衬底10a中形成介电层26a。退火工艺28可以在氮气的环境(n2ambient)中进行30分钟至120分钟。在一些实施例中,退火工艺28的温度例如是介于摄氏450度至摄氏1400度之间。在另一些实施例中,退火工艺28的温度例如是介于摄氏450度至摄氏900度之间。在又一些实施例中,退火工艺28的温度例如是介于摄氏450度至摄氏750度之间。介电层26a与对准标记14在纵向上重叠,其面积大于对准标记14的面积。介电层26a的材料例如是氧化硅、氮氧化硅或其组合。介电层26a的折射率低于硅的折射率。在可见光下,介电层26a的折射率的n值介于0至2之间。在一些实施例中,在可见光下,介电层26a的折射率的n值小于1.5。在另一些实施例中,在可见光下,介电层26a的折射率的n值小于1.46,或更小。举例来说,在摄氏450度退火形成的介电层26a在可见光下的折射率(n值)约为1.41。在摄氏600度退火形成的介电层26a在可见光下的折射率(n值)约为1.43。在摄氏750度退火形成的介电层26a在可见光下的折射率(n值)约为1.46。介电层26a的深度范围例如是4μm至20μm。在本实施例中,介电层26a的顶面与衬底10a的表面10-2共平面,但不以此为限。介电层26a的底面可与对准标记14接触,或相隔非零的距离d1’。距离d1’的范围小于4μm。

45.请参照图1g与图6的动作s30,在衬底10a的表面10-2上形成另一图案化的掩模层30。图案化的掩模层30具有多个开口32。图案化的掩模层30的形成方法如以下步骤所述。请参照图1g与图6的动作s301至s303。于衬底10a的表面10-2上形成另一掩模层(未示出)。掩模层可以由下而上依序包括垫氧化层、氮化硅层以及光刻胶层。在本发明中,由于对准标记14上方的衬底10a已被介电层26a取代,因此,第二区r2的衬底10a的表面10-1至表面10-2之间的衬底10a的厚度小于在第一区r1的衬底10a的表面10-1至表面10-2之间的衬底10a的厚度。由于介电层26a的折射率(n值)可大幅降低至1.5以下,介电层26a在光的照射下呈透明,因此可通过第二区r2的对准标记14来进行对准工艺。之后,经由曝光与显影工艺进行光刻胶层的图案化工艺,之后,再对氮化硅层以及垫氧化层进行蚀刻工艺,以形成开口32。

46.在介电层26a的底面与对准标记14的表面接触的实施例中,由于在对准标记14上方仅有透明的介电层26a,因此在形成图案化的掩模层30时,可以进行无穿硅对准工艺,光仅需穿介电质(through dielectric)而无需穿硅(through silicon),因此具有相当高的对准精确度。在介电层26a的底面与对准标记14的表面之间具有距离d1’的实施例中,由于距离d1’的范围小于4μm,因此,仍可以通过穿薄硅工艺而达到对准的目的。因此,所形成的开口32可以精确地形成在所期望的位置。举例来说,开口32的位置与隔离结构12相对应。

47.之后,请参照图1h与图6的动作s32与s34。以图案化的掩模层30为掩模,在衬底10a中形成深沟槽(未示出),之后,在深沟槽中回填绝缘材料,以形成隔离结构34。在深沟槽中回填绝缘材料的方法例如是在衬底10的表面10-2上以及深沟槽之中形成绝缘材料,例如是

氧化硅、氮化硅或其组合。其后,进行平坦化工艺将多余的绝缘材料移除。平坦化工艺例如是化学机械抛光工艺。其后,将图案化的掩模层30移除。隔离结构34可以与隔离结构12相对应,甚至对准。隔离结构34可以对准隔离结构12中一部分的隔离结构12。隔离结构34可以与隔离结构12相接触或是相隔非零距离。隔离结构34的深度范围例如是4μm至20μm。由于隔离结构34的深度相当深,因此又可称为深沟槽隔离结构。

48.其后,可以再进行后续工艺。举例来说,可以在相邻的两个隔离结构34之间的衬底10a之中形成光电二极管区(photodiode,pd)等工艺。在本实施例中,由于衬底10的表面10-2与隔离结构12之间的距离d1相当大,且隔离结构34具有相当大的深度,因此,形成在隔离结构34之间的衬底10a之中的光电二极管区可以具有相当大的面积。之后,还可包括将处理晶片20与衬底10a分离以及其他的工艺。

49.图3a至图3d绘示本发明第二实施例的一种半导体装置的制造方法的流程剖面示意图。

50.请参照图3a与图6的动作s20与s22。依照上述第一实施例的方法进行对应图1a至图1d以及图6的动作s10至s18的步骤之后,在薄化的衬底10a的表面10-2上形成具有开口23的图案化掩模层22。之后,进行离子注入工艺24’,将杂原子自衬底10a的表面10-2引入第二区r2的衬底10a中,以形成具有杂原子的掺杂区26’。掺杂区26’的位置与掺杂区26略有不同,掺杂区26’的顶面与衬底10a的表面10-2相隔非零距离d2。掺杂区26’中的杂原子的种类可以与掺杂区26中的杂原子种类相同。掺杂区26’中杂原子的剂量可以与掺杂区26中的杂原子的剂量相同。然而,在本实施例中,进行离子注入工艺24’的能量与离子注入工艺24的能量不同,以使得掺杂区26’的顶面与衬底10a的表面10-2相隔非零距离。

51.请参照图3b与图6的动作s24与s28,之后,依照上述第一实施例的方法,移除掩模层22。其后,进行退火工艺28,以使掺杂区26’中的杂原子与衬底10a中的硅反应,以在第二区r2的衬底10a中形成介电层26a’。退火工艺28的温度例如是摄氏450度至摄氏1400度。介电层26a’的材料、面积与介电层26a的材料、面积相似,但介电层26a’的顶面低于衬底10a的表面10-2。换言之,介电层26a’的顶面上仍由衬底10a覆盖。介电层26a’的顶面与衬底10a的表面10-2之间的距离d2的范围例如是大于0且小于4μm。介电层26a的底面可与对准标记14接触,或相隔非零的距离d2’。距离d2与d2’的总和的范围小于4μm。然而,若距离d2或距离d2与d2’的总和超过4μm,表示对准标记14上的衬底10a的厚度过厚,在光的照射下无法呈透明,在后续的对准工艺中将导致无法精确地进行穿硅对准。

52.请参照图3c与图6的动作s30,在衬底10a的表面10-2上形成另一图案化的掩模层30。图案化的掩模层30具有多个开口32。开口32的位置例如是与隔离结构12相对应。图案化的掩模层30的形成方法可依照第一实施例的方法。虽然,介电层26a’上方仍留有衬底10a,但由于该处的衬底10a的厚度(即距离d2)相当薄,且介电层26a’呈透明,因此仅需通过穿薄硅(through thin silicon)对准工艺,即可达到对准的目的。同样地,若是介电层26a’与对准标记14之间仍留有衬底10a,但由于该处的衬底10a的厚度(即距离d2’)与介电层26a’上方的衬底10a的厚度(即距离d2)的总和小于4μm,因此,仍可以通过穿薄硅工艺而达到对准的目的。

53.请参照图3d与图6的动作s32与s34,依照上述第一实施例的方法,在衬底10a中形成隔离结构34。之后,将图案化的掩模层30移除,再进行后续的工艺。

54.根据以上的实施例,在衬底中与对准标记对应的介电层是在衬底薄化之后才形成,然而,本发明不以此为限。与对准标记重叠的介电层也可以在衬底薄化之前形成,以下举例来说明之。

55.图4a至图4h绘示本发明第三实施例的一种半导体装置的制造方法的流程剖面示意图。图7绘示另一种半导体装置的制造方法的流程图。

56.请参照图4a与图7的动作s102与s104。在衬底10的表面10-1上形成图案化的掩模层22。图案化的掩模层22具有开口23,裸露出第二区r2的衬底10a的表面10-2。图案化的掩模层22可以采用上述第一实施例的方法来形成。接着,进行离子注入工艺24’,将杂原子自衬底10a的表面10-1引入第二区r2的衬底10a中,以形成具有杂原子的掺杂区26’。离子注入工艺24’可以采用上述第二实施例所述的离子注入工艺24’来进行,以使得掺杂区26’的顶面与衬底10a的表面10-2相隔非零距离d3。距离d3至少等于或大于后续欲形成的对准标记14的深度。

57.请参照图4b与图7的动作s106与s108,移除图案化的掩模层22。其后,可以选择性进行退火工艺28,以使掺杂区26’中的杂原子与衬底10a中的硅反应,以在第二区r2的衬底10a中形成介电层26a’。退火工艺28可以采用上述第一实施例的方法来进行。然而,本发明实施例不以此为限。在一些实施例中,可以省略退火工艺28,直接通过后续的其他工艺的热工艺来取代退火工艺28。举例来说,可以通过后续形成隔离结构12、材料层16之掺杂区的掺质活化工艺或是金属内连结构的介电层沉积等工艺来取代退火工艺28。

58.请参照图4c与图7的动作s110与s112。在衬底10中形成隔离结构12与对准标记14。隔离结构12位于第一区r1中;对准标记14位于第二区r2中,且与介电层26a在纵向上重叠。之后,再于隔离结构12与对准标记14上形成材料层16。隔离结构12、对准标记14与材料层16可以依照上述第一实施例所述的方法来形成。对准标记14可以与介电层26a’的表面接触或是相隔非零的距离d3’。距离d3’的范围例如是大于0且小于4μm。

59.在一些替代实施例中,用来形成掺杂区26’的离子注入工艺24’也可以在形成隔离结构12与对准标记14之后且在形成材料层16之前进行。同样地,在一些其它实施例中,在形成掺杂区26’之前,或是形成隔离结构12与对准标记14之前,抑或是在形成隔离结构12与对准标记14之后且在形成材料层16之前,可以包括各种步骤。举例来说,可以在衬底10中形成各种p型或是n型导电型的阱区、深阱区、掺杂区等工艺。

60.请参照图4d至图4f与图7的动作s114、s116与s118。将处理晶片20置于衬底10的材料层16上,然后再进行翻转,以使衬底10a位于处理晶片10上。其后,进行衬底10的薄化工艺,以形成厚度薄化的衬底10a。衬底10a的表面10-2与隔离结构12的表面之间的距离d4大于4μm,例如是介于4μm至20μm之间,或更大。在一些实施例中,在进行衬底10的薄化工艺中,部分的介电层26a’也被薄化。在另一些实施例中,在进行衬底10的薄化工艺中,介电层26a’未被薄化。在进行衬底10的薄化工艺后,介电层26a’被裸露出来。介电层26a’的顶面与衬底10a的表面10-2共平面。介电层26a’的底面与对准标记14的表面接触或是相隔非零的距离d3’。距离d3’的范围小于4μm。

61.请参照图4g与图7的动作s120,依照上述第一实施例的方法在衬底10a的表面10-2上形成具有开口32的图案化的掩模层30。同样地,介电层26a’的底面与对准标记14的表面接触或是介电层26a’的底面与对准标记14的表面之间具有距离d3’,在形成图案化的掩模

层30时可以进行无穿硅对准工艺或是进行穿薄硅对准工艺,光可以直接穿透透明的介电层26a’或穿过薄硅而行进至对准标记14,而通过对准标记14达到对准的目的。

62.请参照图4h与图7的动作s122以及s124。依照上述第一实施例的方法,在衬底10a中形成隔离结构34。之后,将图案化的掩模层30移除,再进行后续的工艺。

63.图5a至图5b绘示本发明第四实施例的一种半导体装置的制造方法的流程剖面示意图。

64.请参照图5a与图7的动作s118,依照上述第一实施例的方法进行对应图4a至图4d的步骤以及与图7的动作s102至s116之后,自翻转后的衬底10的表面10-2’对衬底10进行薄化工艺,以形成衬底10b。衬底10b的表面10-2与隔离结构12的表面之间的距离d5例如是4μm至20μm。在本实施例中,衬底10在薄化的过程中并未裸露出介电层26a的顶面,因此,衬底10b的表面10-2高于介电层26a’的顶面,且介电层26a’的顶面被衬底10b覆盖。换言之,介电层26a’的顶面与衬底10b的表面10-2之间的距离d6例如是大于0且小于4μm。然而,若距离d6超过4μm,表示介电层26a’上的衬底10a的厚度过厚,在光的照射下无法呈透明,将导致无法精确地进行穿硅对准。

65.同样地,介电层26a’的底面可与对准标记14接触,或相隔非零的距离d6’。距离d6与d6’的总和的范围小于4μm。

66.请参照图5b与图7的动作s120至s124,依照上述第三实施例对应图4g以及4h的步骤,在衬底10b中形成隔离结构34。之后,再进行后续工艺。同样地,由于距离d6本身或是距离d6与d6’的总和小于4μm,因此,在形成隔离结构34的过程中,可以通过穿薄硅对准工艺而达到对准的目的。

67.综上所述,在以上所述的本发明实施例中,通过在衬底中形成与对准标记重叠的介电层可减少对准标记上方的衬底的厚度。由于对准标记上方的衬底的厚度相当薄,因此,在晶背上制作构件或从晶背制作构件时,可以通过穿薄硅对准工艺或无穿硅对准工艺来进行光刻工艺。故,本发明实施例的方法可以使得衬底保有足够的厚度,并且可提升晶背对准的精确度。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1