半导体封装件的制作方法

1.本

技术实现要素:

是有关于一种半导体封装件。

背景技术:

2.双芯片封装(dual-die packaging)技术被广泛地应用于将两个集成电路芯片封装于单一封装模块中,使得单一封装模块能够提供双倍的功能或数据存储容量。如动态随机存取存储(dynamic random access memory,dram)芯片的记忆芯片通常以此方式封装,以允许单一封装模块提供双倍的功能或数据存储容量。近年来,各种双芯片封装技术已被开发及利用于半导体产业中。

3.一般而言,金线常被广泛地应用于将电流从电源传输至dram芯片中。然而,当dram芯片于操作过程中(例如,高频率操作过程中)需要瞬间大电流时,在高频率操作下的金线会形成大的电阻,从而限制瞬间大电流的传输。如此一来,在dram芯片中将产生瞬间电压降,并最终导致芯片的误操作。因此,期望开发出一种具有改善的功能性的半导体装置以克服上述问题。

发明内容

4.本发明的目的是有关于一种在需要瞬间大电流的情形下,仍可良好地执行其功能的半导体封装件。

5.根据本发明一些实施方式,半导体封装件包括第一基板、第一半导体芯片、第二半导体芯片、第二基板、至少一个第一焊球、至少一个第二焊球以及至少一个第三焊球。第一半导体芯片设置在第一基板上。第二半导体芯片设置在第一半导体芯片上。第二基板第一焊球垂直地设置于第一基板与第一半导体芯片之间。设置在二半导体芯片上。第二焊球垂直地设置于第二基板与第二半导体芯片之间。第三焊球垂直地设置于第一基板与第二基板之间。

6.在本发明一些实施方式中,第一半导体芯片的功能性表面面对第一基板。

7.在本发明一些实施方式中,第二半导体芯片的功能性表面面对第二基板。

8.在本发明一些实施方式中,第一焊球的尺寸小于第三焊球的尺寸。

9.在本发明一些实施方式中,第二焊球的尺寸小于第三焊球的尺寸。

10.在本发明一些实施方式中,第三焊球的球高度大于第一半导体芯片与第二半导体芯片的总厚度、第一焊球的球高度以及第二焊球的球高度之总和。

11.在本发明一些实施方式中,第三焊球由第一基板延伸至第二基板。

12.在本发明一些实施方式中,第三焊球横向地与第一半导体芯片及第二半导体芯片隔开。

13.在本发明一些实施方式中,半导体封装件还包括至少一个第四焊球,设置于第一基板背对第三焊球的表面。

14.在本发明一些实施方式中,第四焊球与第三焊球电性连接。

15.在本发明一些实施方式中,半导体封装件还包括至少一个第一铜柱以及至少一个第二铜柱,其中第一铜柱垂直地延伸于第一焊球与第一半导体芯片之间,且第二铜柱垂直地延伸于第二焊球与第二半导体芯片之间。

16.在本发明一些实施方式中,半导体封装件还包括粘胶层,夹置于第一半导体芯片与第二半导体芯片之间。

17.在本发明一些实施方式中,半导体封装件还包括至少一个第一重分布层,垂直地延伸于第一半导体芯片与第一焊球之间。

18.在本发明一些实施方式中,半导体封装件还包括至少一个第二重分布层,垂直地延伸于第二半导体芯片与第二焊球之间。

19.在本发明一些实施方式中,半导体封装件还包括成型模料,封装第一半导体芯片与第二半导体芯片。

20.在本发明一些实施方式中,成型模料还封装第三焊球。

21.在本发明一些实施方式中,半导体封装件还包括至少一个基板贯穿导通结构(through-substrate via,tsv),嵌入至第一基板中。

22.在本发明一些实施方式中,基板贯穿导通结构与第一焊球及第三焊球电性连接。

23.在本发明一些实施方式中,半导体封装件还包括至少一个基板贯穿导通结构,嵌入至第二基板中。

24.在本发明一些实施方式中,基板贯穿导通结构与第二焊球及第三焊球电性连接。

25.根据本发明上述实施方式,由于使用于传统的半导体封装件中的金线被取代为本发明中具有较大尺寸的第一焊球、第二焊球以及第三焊球,因此可避免由金线产生的大电阻以及其所造成的发生于半导体封装件中的瞬间电压降。因此,即使需要瞬间大电流,来自外部电子装置的电源供给仍可被稳定地提供至半导体封装件中。借此,即使在需要瞬间大电流的情形下,半导体封装件仍可良好地执行其功能。

附图说明

26.为让本发明的上述和其他目的、特征、优点与实施例能更明显易懂,结合附图说明如下:

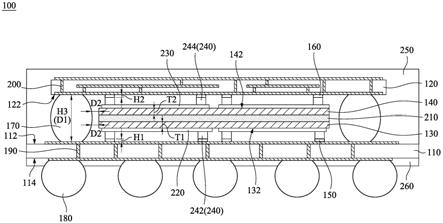

27.图1绘示根据本发明一实施方式的半导体封装件的侧视示意图。

28.主要附图标记说明:

29.100-半导体封装件,110-第一基板,112-表面,114-表面,120-第二基板,122-表面,130-第一半导体芯片,132-功能表面,140-第二半导体芯片,142-功能表面,150-第一焊球,160-第二焊球,170-第三焊球,180-第四焊球,190-第一导电结构,200-第二导电结构,210-粘合层,220-第一重分布层,230-第二重分布层,240-导电柱结构,242-第一铜柱,244-第二铜柱,250-成型模料,260-封装层,h1~h3-球高度,t1~t2-厚度,d1~d2-距离。

具体实施方式

30.以下将以附图公开本发明的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本发明。也就是说,在本发明部分实施方式中,这些实务上的细节是非必要的,因此不应用以限制本发

明。此外,为简化附图起见,一些公知惯用的结构与元件在附图中将以简单示意的方式绘示。另外,为了便于读者观看,附图中各元件的尺寸并非依实际比例绘示。

31.图1绘示根据本发明一实施方式的半导体封装件100的侧视示意图。半导体封装件100可包括第一基板110、第二基板120、第一半导体芯片130以及第二半导体芯片140。第一半导体芯片130设置在第一基板110上,而第二半导体芯片140设置在第一半导体芯片130上,且第二基板120设置在第二半导体芯片140上。换句话说,第一半导体芯片130及第二半导体芯片140垂直地共同堆叠并夹置于第一基板110与第二基板120之间。

32.半导体封装件100更可包括至少一个第一焊球150以及至少一个第二焊球160。在一些实施方式中,第一焊球150垂直地安装于第一基板110与第一半导体芯片130之间,以电性连接第一基板110与第一半导体芯片130。因此,第一半导体芯片130可通过第一焊球150及第一基板110进一步与外部电子装置(例如,电源)电性连接。在一些实施方式中,第二焊球160垂直地安装于第二基板120与第二半导体芯片140之间,以电性连接第二基板120与第二半导体芯片140。

33.为达到在半导体封装件100中进行的电性连接的目的,在一些实施方式中,第一半导体芯片130的功能表面132(例如,第一半导体芯片面对其重分布层220的表面)面向第一基板110,且第二半导体芯片140的功能表面142(例如,第二半导体芯片面对其重分布层230的表面)面向第二基板120。如此一来,第一焊球150及第二焊球160可分别在第一基板110与第一半导体芯片130之间以及在第二基板120与第二半导体芯片140之间进行电性连接。应了解到,本文中的“功能表面”是指具有例如是导电迹线、导电线或导电层的导电图案(例如,重分布层)。

34.半导体封装件100还包括垂直地安装于第一基板110与第二基板120之间的至少一个第三焊球170,以电性连接第一基板110与第二基板120。根据上述,第二半导体芯片140可通过第二焊球160及第三焊球170电性连接第一基板110,以进一步与外部电子装置(例如,电源)电性连接。如此一来,基于此电性连接的配置,包括第一半导体芯片130及第二半导体芯片140的双芯片封装得以被功能化。

35.由于使用于传统的半导体封装件中的金线被取代为本发明中具有较大尺寸的第一焊球、第二焊球以及第三焊球,因此可避免由金线产生的大电阻以及其所造成的发生于半导体封装件中的瞬间电压降。因此,即使需要瞬间大电流,来自外部电子装置的电源供给仍可被稳定地提供至半导体封装件中。

36.在一些实施方式中,第三焊球170由第一基板110延伸至第二基板120。更具体来说,第三焊球170由第一基板110的内表面112延伸至第二基板120的内表面122。换句话说,第一基板110的内表面112与第二基板120的内表面122之间的距离d1与第三焊球170的球高度h3实质上相同。第三焊球170的尺寸大于第一焊球150的尺寸以及第二焊球160的尺寸。在一些实施方式中,第三焊球170的球高度h3可取决于第一半导体芯片130与第二半导体芯片140的总厚度以及第一焊球150与第二焊球160的总球高度。举例来说,第三焊球170的球高度h3可与第一半导体芯片130的厚度t1、第二半导体芯片140的厚度t2、第一焊球150的球高度h1以及第二焊球160的球高度h2的总和实质上相同。借此,可避免半导体封装件100产生形变。

37.在一些实施方式中,第三焊球170与包括第一半导体芯片130与第二半导体芯片

140的双芯片封装横向地间隔开来。在一些实施方式中,第三焊球170与第一半导体芯片130(或第二半导体芯片140)之间的距离d2在约200μm至约1000μm的范围中,以防止第三焊球170与第一半导体芯片130(或第二半导体芯片140)之间发生非预期的接触,并维持半导体封装件100的小尺寸。举例来说,若距离d2小于约200μm,第三焊球170可能意外地接触第一半导体芯片130(或第二半导体芯片140);若距离d2大于约1000μm,可能导致半导体封装件100的尺寸难以减小。

38.在一些实施方式中,半导体封装件100还包括位于第一基板110背对第三焊球170的表面114上的至少一个第四焊球180。换句话说,第四焊球180被安装在第一基板110的外表面。在一些实施方式中,第四焊球180电性连接第一焊球150及第三焊球170,使得第一半导体芯片130及第二半导体芯片140可电性连接其他外部电子装置。

39.在一些实施方式中,第一焊球150、第二焊球160、第三焊球170及第四焊球180各自的数量可以是多个。举例来说,如图1所示,第一焊球150及第二焊球160各自的数量为四个,第三焊球170的数量为两个,且第四焊球180的数量为五个。然而,由于图1是半导体封装件100的侧视示意图,因此实际上总共可能存在更多的焊球。由第一半导体芯片130及第二半导体芯片140传输及/或传输至第一半导体芯片130及第二半导体芯片140的电流可随着第一焊球150以及第二焊球160各自的数量增加而变大,以加速半导体封装件100的操作。此外,由半导体封装件100的侧视图(例如,图1所示的侧视图)来看,焊球的位置设置可以是左右对称的,从而维持半导体封装件100的平衡。

40.在一些实施方式中,半导体封装件100还包括至少一个第一导电结构190以及至少一个第二导电结构200。第一导电结构190嵌入至第一基板110中(例如,基板贯穿导通结构(through-substrate via,tsv)延伸穿过第一基板110的整个厚度),以连接第一焊球150以及第四焊球180,从而使得电流可在外部电子装置与第一半导体芯片130之间传输。第二导电结构200嵌入至第二基板120中(例如,基板贯穿导通结构延伸穿过第二基板120的整个厚度),以连接第二焊球160以及第三焊球170,从而使电流可在外部电子装置与第二半导体芯片140之间传输。在一些实施方式中,第一导电结构190及第二导电结构200可各自包过相互连接的至少一个水平部及至少一个垂直部。

41.在一些实施方式中,半导体封装件100还包括夹置于第一半导体芯片130与第二半导体芯片140之间的粘合层210。粘合层210配置以将第一半导体芯片130粘合至第二半导体芯片140。举例来说,粘合层210将第一半导体芯片130背对功能表面132的表面粘合至第二半导体芯片140背对功能表面142的表面,使得第一半导体芯片130的功能表面132以及第二半导体芯片140的功能表面142可以分别面向第一基板110以及第二基板120,以进一步与第一基板110及第二基板120电性连接。

42.在一些实施方式中,半导体封装件100还包括至少一个第一重分布层220以及至少一个第二重分布层230。第一重分布层220设置在第一半导体芯片130的功能表面132上,并垂直地位于第一半导体芯片130与第一焊球150之间。第二重分布层230设置在第二半导体芯片140的功能表面142上,并垂直地位于第二半导体芯片140与第二焊球160之间。在一些实施方式中,半导体封装件100还包括位于第一重分布层220及第二重分布层230上的多个导电柱结构240(例如,铜柱),使得第一焊球150及第二焊球160可安装于其上。举例来说,半导体封装件100包括在第一焊球150与第一半导体芯片130之间垂直地延伸的至少一个第一

铜柱242及在第二焊球160与第二半导体芯片140之间垂直地延伸的至少一个第二铜柱244。

43.如前所述,第三焊球170的球高度h3可取决于第一半导体芯片130与第二半导体芯片140的总厚度以及第一焊球150与第二焊球160的总球高度的总和。在半导体封装件100还包括粘合层210、第一重分布层220、第二重分布层230以及导电柱结构240的实施方式中,第三焊球170的球高度h3更可以取决于粘合层210、第一重分布层220、第二重分布层230以及导电柱结构240的总厚度。

44.在一些实施方式中,半导体封装件100还包括封装第一半导体芯片130及第二半导体芯片140的成型模料250。在一些实施方式中,成型模料250还封装第二基板120、第一焊球150、第二焊球160以及第三焊球170。成型模料250配置以保护上述元件以避免其过度暴露于外界环境中。在一些实施方式中,半导体封装件100还包括设置在第一基板110的表面114的封装层260,且在该表面114上安装有第四焊球180。封装层260可保护第一导电结构190与第四焊球180的连接部分。因此,部分的第四焊球180嵌入至封装层260中。

45.根据本发明上述实施方式,通过第一焊球、第二焊球以及第三焊球的配置,可避免由金线产生的大电阻以及其所造成的发生于半导体封装件中的瞬间电压降,因此即使在需要瞬间大电流的情形下,半导体封装件仍可良好地执行其功能。

46.虽然本发明已以实施方式公开如上,然其并非用以限定本发明,任何所属领域的技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰,因此本发明的保护范围当视权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1