半导体组件的制作方法

1.本发明涉及一种集成电路,尤其涉及一种半导体组件。

背景技术:

2.一般而言,在半导体组件(例如是微机电(mems)组件)中通常会设置有特殊结构(例如是具有厚度的线路或嵌埋零组件等等),因此具有此特殊结构的区域与其周边区域之间会产生较明显高度差异,如此一来,会对后续形成的导电端子顶端的平面度产生不良影响,进而可能会影响半导体组件与电路板之间接合的品质。

3.此外,为了解决前述问题,依目前的做法会将欲形成导电端子的区域避开具有高度差异的区域,然而,随着半导体组件的微型化,需提高其空间利用率,因此如何在降低高度差异对导电端子顶端的平面度产生的不良影响提升半导体组件与电路板接合之间的品质的同时有效地增加半导体组件的空间利用率实为亟欲解决的重要课题。

技术实现要素:

4.本发明是针对一种半导体组件,其可以在降低高度差异对导电端子顶端的平面度产生的不良影响提升其与电路板接合之间的品质的同时还可以有效地增加空间利用率。

5.本发明的一种半导体组件,包括半导体晶圆、一导电层与一介电层、第一导电端子以及第二导电端子。半导体晶圆具有承载面。导电层与介电层位于承载面上。导电层与半导体晶圆电性连接。介电层覆盖导电层,并具有一第一开口与一第二开口。第一开口与第二开口暴露出部分导电层。第一开口的底部相对于承载面的一高度大于第二开口的底部相对于承载面的一高度。第一开口大于第二开口。第一导电端子位于第一开口并与导电层电性连接。第二导电端子位于第二开口并与导电层电性连接。

6.在本发明的一实施例中,上述的第一导电端子的一顶面与第二导电端子的一顶面实质上共平面。

7.在本发明的一实施例中,上述的第一导电端子的一高度小于所述第二导电端子的一高度。

8.在本发明的一实施例中,上述的第一开口与第二开口的比值范围介于一点零五比一至二比一之间。

9.在本发明的一实施例中,上述的半导体组件更包括凸出图案,位于第一开口与承载面之间。

10.在本发明的一实施例中,上述的半导体组件更包括一第一导电柱与一第二导电柱。第一导电柱位于第一开口且于第一导电端子与导电层之间。第二导电柱位于第二开口且于第二导电端子与导电层之间。

11.在本发明的一实施例中,上述的第一导电柱的一高度与第二导电柱的一高度实质上相等。

12.在本发明的一实施例中,上述的半导体晶圆包括一第一区域与一第二区域,第一

开口与第二开口分别位于第一区域与第二区域上,且第二区域上的介电层向上延伸至第一区域上的介电层。

13.在本发明的一实施例中,上述的第一区域上的介电层的一高度大于第二区域上的介电层的一高度。

14.在本发明的一实施例中,上述的半导体组件还包括一第一球底金属层以及一第二球底金属层。第一球底金属层位于第一开口且位于第一导电端子与导电层之间。第二球底金属层位于第二开口且位于第二导电端子与导电层之间。

15.基于上述,通过介电层的开口设计,将相对于半导体晶圆承载面的高度较高的区域上的第一开口设计成大于相对于半导体晶圆承载面的高度较低的区域上的第二开口,以调整形成于第一开口中的第一导电端子的高度与形成于第二开口中的第二导电端子的高度,补偿原本两区域之间的高度差异,进而可以降低高度差异对导电端子顶端的平面度产生的不良影响提升其与电路板接合之间的品质,因此,本发明的半导体组件在降低高度差异对导电端子顶端的平面度产生的不良影响提升其与电路板接合之间的品质的同时还可以有效地增加空间利用率。

16.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

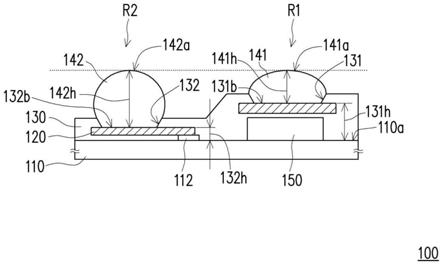

17.图1是本发明一实施例的半导体组件的剖面示意图;

18.图2是本发明另一实施例的半导体组件的剖面示意图;

19.图3是本发明又一实施例的半导体组件的剖面示意图;

20.图4是本发明再一实施例的半导体组件的剖面示意图。

21.附图标记说明

22.100、200、300、400:半导体组件

23.110:半导体晶圆

24.110a:承载面

25.112:接垫

26.120:导电层

27.130:介电层

28.131:第一开口

29.132:第二开口

30.131b、132b:底部

31.131h、132h、141h、142h、371h、372h:高度

32.141:第一导电端子

33.142:第二导电端子

34.141a、142a:顶面

35.150:凸出图案

36.261:第一球底金属层

37.262:第二球底金属层

38.371:第一导电柱

39.372:第二导电柱

40.r1:第一区域

41.r2:第二区域

具体实施方式

42.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同组件符号在附图和描述中用来表示相同或相似部分。

43.本文所使用的方向用语(例如,上、下、右、左、前、后、顶部、底部)仅作为参看所绘附图使用且不意欲暗示绝对定向。

44.以下将参考附图来全面地描述本发明的例示性实施例,但本发明还可按照多种不同形式来实施,且不应解释为限于本文所述的实施例。在附图中,为了清楚起见,各区域、部位及层的大小与厚度可不按实际比例绘制。为了方便理解,下述说明中相同的组件将以相同的符号标示来说明。

45.图1是本发明一实施例的半导体组件的剖面示意图。

46.请参考图1,在本实施例中,半导体组件100包括半导体晶圆110、一导电层120与一介电层130、第一导电端子141以及第二导电端子142。进一步而言,半导体晶圆110具有承载面110a,且承载面110a上可以具有接垫112。

47.半导体晶圆110可以是适宜的半导体晶圆,举例而言,半导体晶圆110例如是硅晶圆。接垫112可以是适宜的导电接垫或导电合金接垫,举例而言,接垫112例如是由铜、铝或其合金所形成,但本发明不限于此,且接垫设置数量可依实际设计而定,附图仅绘制一个做为示意说明,不用以局限本发明的设置数量。此外,半导体晶圆110中可以具有微机电线路,但本发明不限于此。

48.导电层120与介电层130位于承载面110a上。导电层120与半导体晶圆110电性连接。举例而言,导电层120可以是通过接垫112与半导体晶圆110接触并电性连接或通过信号传递。导电层120的材料例如是铜、铝、金、银、或其组合,而介电层130的材料可以包括非有机或有机介电材料,举例而言,介电层130的材料例如是氧化硅、氮化硅、碳化硅、氮氧化硅、聚酰亚胺、苯并环丁烯(benezocyclobutene,bcb),但本发明不限于此,导电层120的材料与介电层130的材料及层数可以视实际设计上的需求而定,并不以附图所揭为限。此外,导电层120可以是将通过信号重新分布出去的重布线路层(redistribution layer,rdl),但本发明不限于此。

49.介电层130覆盖导电层120,并具有一第一开口131与一第二开口132。第一开口131与第二开口132暴露出部分导电层120。在本实施例中,半导体晶圆110可以包括一第一区域r1与一第二区域r2,第一开口131与第二开口132可以分别位于第一区域r1与第二区域r2上,且第二区域r2上的介电层130向上延伸至第一区域r1上的介电层130,因此,第一区域r1上的介电层130的高度大于第二区域r2上的介电层130的高度。换句话说,第一开口131可以位于高度较高的第一区域r1,而第二开口132可以位于高度较低的第二区域r2,因此,第一开口131的底部131b相对于承载面110a的一高度131h大于第二开口132的底部132b相对于承载面110a的一高度132h。

50.在本实施例中,第一开口131大于第二开口132,以用于调整后续形成于其中的导电端子的高度。举例而言,第一开口131与第二开口132的比值范围可以介于一点零五比一至二比一之间,但本发明不限于此,第一开口131与第二开口132的比值范围可以视设计上的需求而定。此外,第一导电端子141位于第一开口131并与导电层120电性连接,第二导电端子142位于第二开口132并与导电层120电性连接。上述的第一导电端子141与第二导电子142所电性连接的导电层120可为同一条重布线线路,于其它实施例中,该二导电端子所连接的导电层120亦可为不同的重布线缐路,并不以附图所揭或相同标号为限。第一导电端子141与第二导电端子142可以是锡球且例如是通过电镀工艺、落球工艺或网印锡膏工艺所形成,但本发明不限于此。

51.通过介电层130的开口设计,将相对于半导体晶圆110承载面110a的高度较高的区域(如第一区域r1)上的第一开口131设计成大于相对于半导体晶圆110承载面110a的高度较低的区域(如第二区域r2)上的第二开口132,以调整形成于第一开口131中的第一导电端子141的高度141h与形成于第二开口132中的第二导电端子142的高度142h,补偿原本两区域之间的高度差异,进而可以降低高度差异对导电端子顶端的平面度产生的不良影响提升其与电路板接合之间的品质,因此,本发明的半导体组件100在降低高度差异对导电端子顶端的平面度产生的不良影响提升其与电路板接合之间的品质的同时还可以有效地增加空间利用率。

52.进一步而言,由于第一开口131大于第二开口132,因此,形成于第一开口131中的第一导电端子141的高度141h可以是小于形成于第二开口132中的第二导电端子142的高度142h,以使第一导电端子141的一顶面141a与第二导电端子142的一顶面142a可以实质上共平面(coplanar),以维持较好的顶端平面度,使半导体组件100与电路板之间具有较佳的接合品质。

53.在本实施例中,半导体组件100可以还包括凸出图案150,使第一区域r1具有高于第二区域r2的高度,以满足半导体组件110的功能需求。凸出图案150可以位于第一开口131与承载面110a之间。在一实施例中,凸出图案150例如是可以与导电层120电性连接或电性绝缘的线路或嵌埋零组件、被动组件等等。然而,本发明不限于此,凸出图案150的种类可以视半导体组件100的需求而定。

54.在此必须说明的是,以下实施例沿用上述实施例的组件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的组件,并且省略了相同技术内容的说明,关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

55.图2是本发明另一实施例的半导体组件的剖面示意图。请参考图2,本实施例的半导体组件200与半导体组件100的差别在于:半导体组件200可以还包括第一球底金属层261与第二球底金属层262,其中第一球底金属层261可以位于第一开口131且位于第一导电端子141与导电层120之间,而第二球底金属层262可以位于第二开口132且位于第二导电端子142与导电层120之间。

56.在本实施例中,通过第一球底金属层261与第二球底金属层262的设计可以提升后续位于半导体晶圆110上的构件的接合强度,减少因接合强度不佳而对半导体组件200产生不良影响的情况发生,进而可以提升半导体组件200的可靠度。

57.图3是本发明又一实施例的半导体组件的剖面示意图。请参考图3,本实施例的半

导体组件300与半导体组件100的差别在于:半导体组件300可以更包括第一导电柱371与第二导电柱372,其中第一导电柱371可以位于第一开口131且于第一导电端子141与导电层120之间,第二导电柱可以位于第二开口132且于第二导电端子142与导电层120之间。进一步而言,第一导电柱371与第二导电柱372可以分别对应于第一开口131与第二开口132的尺寸形成不同宽度,而由于第一导电柱371与第二导电柱372可以于同一电镀工艺中形成,因此,第一导电柱371的高度371h与第二导电柱372的高度372h可以实质上相等,但本发明不限于此。

58.在本实施例中,通过第一导电柱371与第二导电柱372的设计可以进一步提升半导体组件300的电性能力。此外,第一导电柱371与第二导电柱372的材质可为相同材质,于特定设计中,第一导电柱371与第二导电柱372亦可互为不同材质。而前述导电柱的材质可选自于金、银、铜、镍或其合金等。

59.图4是本发明再一实施例的半导体组件的剖面示意图。请参考图4,本实施例的半导体组件400与半导体组件300的差别在于:半导体组件400还可以包括如图2所示的第一球底金属层261与第二球底金属层262,以进一步提升第一导电柱371与第二导电柱372跟导电层120之间的接合强度。

60.综上所述,通过介电层的开口设计,将相对于半导体晶圆承载面的高度较高的区域上的第一开口设计成大于相对于半导体晶圆承载面的高度较低的区域上的第二开口,以调整形成于第一开口中的第一导电端子的高度与形成于第二开口中的第二导电端子的高度,补偿原本两区域之间的高度差异,进而可以降低高度差异对其上导电端子顶端的平面度产生的不良影响提升其与电路板接合之间的品质,因此,本发明的半导体组件在降低高度差异对导电端子顶端的平面度产生的不良影响提升其与电路板接合之间的品质的同时还可以有效地增加空间利用率。此外,通过第一球底金属层与第二球底金属层和/或第一导电柱与第二导电柱的设计可以进一步提升半导体组件的可靠度与电性能力。

61.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1