半导体装置及其制造方法与流程

半导体装置及其制造方法

1.[相关申请案]

[0002]

本技术案享受以日本专利申请案2020-046767号(申请日:2020年3月17日)作为基础申请案的优先权。本技术案通过参照该基础申请案而包含基础申请案的全部内容。

技术领域

[0003]

本发明的实施方式涉及一种半导体装置及其制造方法。

背景技术:

[0004]

有的三维结构的半导体存储装置中具有导电层与绝缘层交替地积层而成的积层体。其形成为积层体被柱状通道贯通,且在导电层与通道的交叉部分构成有存储单元。另一方面,积层体的端部形成为阶梯状而露出导电层,通过在此设置接点,各导电层与积层体的外部电连接。

[0005]

这种半导体存储装置中,存在如果增加存储容量那么导电层与绝缘层的积层数增加的倾向。如果积层数增加,那么积层体变高,因此相对于作为积层体下层部的导电层的接触孔变长,其形成所需要的时间也变长。这样一来,从在积层体的上层部导电层露出于接触孔的底面之后起,至在积层体的下层部形成接触孔为止这一段相对较长的时间内,该导电层暴露在蚀刻环境之下。因此,有可能发生下述情况:接触孔贯通导电层,在形成接点之后,上下相邻的导电层之间发生短路。

技术实现要素:

[0006]

本发明要解决的问题在于,提供一种能够减少导电层的接触不良的半导体装置及其制造方法,该半导体装置包含端部形成为阶梯状的积层体,且该导电层设置在阶梯形状的各阶上表面。

[0007]

本发明的一实施方式的半导体装置具备:积层体,包含交替地积层的第1膜与第2膜,且端部具有阶梯形状;厚膜体,设置在阶梯形状的台阶的上表面,厚于积层体中的第2膜,在下端与该第2膜相连,且相对于与所述上表面相邻的上一级台阶的侧面,具有间隔部;第3膜,覆盖积层体及厚膜体;及导电性柱状体,贯通第3膜,且与厚膜体相接。

附图说明

[0008]

图1(a)~(f)是示意性地表示经过实施方式的半导体装置制造方法的一连串步骤当中的主要步骤之后半导体装置的剖面的图。

[0009]

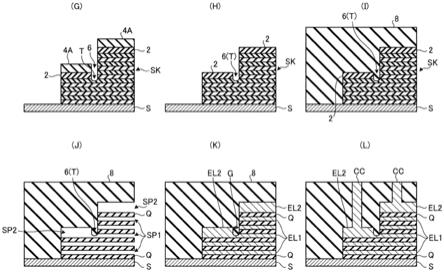

图2(g)~(l)是继图1之后,示意性地表示经过实施方式的半导体装置制造方法的一连串步骤当中的主要步骤之后半导体装置的剖面的图。

[0010]

图3(a)~(f)是示意性地表示经过实施方式的变化例1的半导体装置制造方法的一连串步骤当中的主要步骤之后半导体装置的剖面的图。

[0011]

图4(g)~(i)是继图3之后,示意性地表示经过实施方式的变化例1的半导体装置

制造方法的一连串步骤当中的主要步骤之后半导体装置的剖面的图。

[0012]

图5(a)~(d)是示意性地表示经过实施方式的变化例2的半导体装置制造方法的一连串步骤当中的主要步骤之后半导体装置的剖面的图。

具体实施方式

[0013]

以下,参照附图,对本发明的非限定性例示实施方式进行说明。所有附图中,对同一或对应的构件或零件附上同一或对应的参照符号,并省略重复的说明。另外,附图的目的并不在于表示构件或零件之间、或者各层厚度之间的相对比,因此,具体的厚度或尺寸可以参照以下非限定性实施方式,由业者来决定。

[0014]

参照图1及图2,对实施方式的半导体装置的制造方法进行说明。图1及图2是示意性地表示经过本制造方法的一连串步骤当中的主要步骤之后半导体装置的剖面的图。

[0015]

参照图1(a),在衬底s之上形成氧化硅(siox)层q与氮化硅(sin)层n交替地积层而成的积层体sk。各siox层q具有几乎相同的厚度,各sin层n也具有相同的厚度。氮化硅层n之后会被去除,将其去除后出现的空间会被嵌入例如钨(w)等金属,而成为导电层。该导电层作为相对于存储单元的字线发挥功能,该存储单元形成在以贯通积层体sk的方式设置的半导体柱。

[0016]

其次,如图1(b)所示,蚀刻积层体sk,使其端部具有阶梯形状。如图所示,在该经蚀刻而形成的阶梯的各阶上表面(踩踏面)露出sin层n。此外,如图1(b)所示,每3层sin层n便露出1层sin层n,且各sin层n露出于阶梯的各阶上表面。具体来说,虽省略了图示,但这种阶梯形状是由积层体sk的3个端部形成的,例如,各阶的3层sin层n当中,中央的sin层n露出于形成在另一端部的阶梯的各阶上表面,最下侧的sin层n露出于形成在再另一端部的阶梯的各阶上表面。另外,图1(b)中,仅图示有2阶,但阶数是与积层体sk中的sin层n及siox层q的数量相关的,例如也可以是几阶至十阶。这种阶梯形状可以利用例如采用压模微影法形成在积层体sk上表面的三维蚀刻掩膜来形成。

[0017]

接下来,如图1(c)所示,在露出的衬底s的上表面、露出于积层体sk各阶上表面的sin层n之上、及积层体sk的各阶侧面(竖立面)之上,堆积sin膜2。该sin膜2可以堆积在基底层即所谓的保形层。也就是说,sin膜2是与露出于积层体sk各阶上表面的sin层n几乎平行且以相同厚度形成的。另外,sin膜2相对于积层体sk的各阶侧面也几乎平行,且具有相同厚度。

[0018]

继而,以覆盖sin膜2的方式涂布抗蚀膜4,如图1(d)所示,将模板10压抵着该抗蚀膜4。模板10具有与积层体sk的阶梯形状对应的带有多级台阶的凹部形状。如果在模板10压抵着抗蚀膜4时透过模板10向抗蚀膜4照射紫外光,那么抗蚀膜4硬化,如图1(e)所示,获得阶梯形状的抗蚀膜4a(抗蚀图案)。

[0019]

其次,对抗蚀膜4a实施例如灰化处理。该灰化处理如下所述般实施:将抗蚀膜4a整体缩小,如图1(f)所示,将各阶上表面的抗蚀膜4a保留,而将衬底s上表面与各阶侧面的抗蚀膜4a去除。

[0020]

其后,将各阶上表面保留的抗蚀膜4a作为掩膜,如图2(g)所示,通过例如湿式蚀刻将各阶侧面上的sin膜2去除。从而阶梯形状的积层体sk的各阶侧面露出。此处,在各阶上表面的sin膜2与相邻的上一级台阶的侧面之间形成有槽部6。进而,在露出于槽部6底部的sin

层n形成有沟槽t。sin层n的沟槽t是在将各阶侧面上的sin膜2去除时形成的。因此,去除sin膜2时,要以不会去除所有sin层n且在sin层n形成沟槽t的方式,调整例如蚀刻时间等。关于沟槽t的功能、或通过沟槽t所达成的效果将在后文中进行说明。

[0021]

继而,如图2(h)所示,通过例如灰化将各阶之上保留的抗蚀膜4a去除。由此,sin膜2露出于各阶上表面。接下来,以覆盖这种结构的方式形成例如siox膜8(图2(i))。siox膜8可以采用以例如四乙氧基硅烷(teos)作为原料的等离子体化学气相沉积(ccvd)法来形成。由此,在所述槽部6与沟槽t中嵌入siox。

[0022]

接着,如图2(j)所示,经由以贯通积层体sk的方式形成在积层体sk的例如中央部的贯通孔或槽(未图示),将积层体sk中的sin层n去除,而形成空间sp1。此时,各阶上表面保留的sin膜2也一起被去除。从而,在各阶上部形成具有高度l2的空间sp2,该空间sp2的高度l2高于空间sp1的高度l1。

[0023]

接下来,采用例如原子层沉积(atomic layer deposition)法等,如图2(k)所示,在空间sp1及sp2中嵌入例如钨(w)等金属。由此,获得与空间sp1对应的导电层el1、及与空间sp2对应的导电层el2。此处,导电层el2与从积层体sk内部延伸的导电层el1相连,且与该导电层el1形成为单一体。另外,导电层el2形成为厚于该导电层el1的厚膜体。

[0024]

其后,形成从siox膜8的上表面贯通该siox膜8并到达导电层el2的接触孔,在接触孔中嵌入例如w,形成接点cc(图2(l))。

[0025]

如上所述,在本实施方式的半导体装置的制造方法中,以覆盖阶梯形状的积层体sk的方式形成siox膜8时,积层体sk的各阶上表面即sin层n之上保留有sin膜2。如果在形成siox膜8之后将sin层n去除,那么sin膜2也会被去除,从而在积层体sk的各阶上部形成空间sp2,该空间sp2高于通过去除sin层n而出现的空间sp1。在该空间sp2中嵌入w便形成导电层el2,因此所获得的是,比在空间sp1中嵌入w而形成的导电层el1厚的导电层el2。然后,相对于导电层el2,形成接点cc。

[0026]

假如sin层n之上没有sin膜2,那么在积层体sk的各阶上部会形成厚度与导电层el1相同的导电层。虽然导电层能够在形成接触孔时作为蚀刻终止层发挥功能,但是一旦导电层露出于接触孔底面之后长时间地暴露在蚀刻环境之下,那么导电层也会被蚀刻而变薄。这样一来,也有可能发生例如下述情况:接触孔贯通导电层,在形成接点之后,上下相邻的2层导电层之间发生短路。

[0027]

但是,根据实施方式的半导体装置的制造方法,能够使与接点cc相接的导电层el2厚于导电层el1,因此容易避免接触孔贯通导电层el2的情况。

[0028]

另外,要想使与接点相接的导电层的厚度更厚,也可以考虑加厚积层体sk中的sin层n。也就是,如果加厚sin层n,那么也能够加厚通过在去除sin层n后出现的空间中嵌入w而形成的导电层。但是,这种情况下,形成积层体sk所需要的时间变长,在形成存储单元用存储孔、或形成积层体sk的阶梯形状等步骤中,加工量增加,加工难度上升。

[0029]

而与此相对地,根据实施方式的半导体装置的制造方法,无需加厚导电层el1即可加厚与接点cc相接的导电层el2,因此能够避免形成积层体sk所需要的时间变长的情况,且在形成存储孔、或积层体sk的阶梯形状等的过程中,加工量不会增加,也能够避免加工难度上升的情况。

[0030]

另外,在实施方式的半导体装置的制造方法中,模板10压抵着以覆盖sin膜2的方

式形成的抗蚀膜4,从而获得抗蚀膜4a(图1(e))。如果将该抗蚀膜4a缩小,那么sin膜2露出于积层体sk的各阶侧面。该缩小处理是通过例如灰化而实施的,但由于sin膜2对灰化具有耐受性,因此sin膜2能够具有堆积时的厚度。从而,能够根据sin膜2的厚度,来决定通过将侧面的sin膜2去除而形成的槽部6的宽度。由于sin膜2的厚度再现性相对较好,因此也能够降低槽部6的宽度的不等。

[0031]

槽部6在形成siox膜8时被嵌入siox,而成为如图2(k)中的箭头g所示,使导电层el2与和导电层el2相连的导电层el1的上一层导电层el1相隔的间隔部(以下,有时称为间隔部6)。间隔部6有助于减少导电层el2与和导电层el2相连的导电层el1的上一层导电层el1之间的漏电流。因此,如果能够降低槽部6的宽度的不等,那么能够再现性良好地减少漏电流。另外,在槽部6的底部形成有沟槽t,沟槽t中也嵌入有siox,这有助于减少漏电流。

[0032]

此外,要想减少所述漏电流,也可以考虑在台阶的上表面形成越朝相邻的上一级台阶的侧面变得越薄的倾斜导电层,来代替导电层el2。据此,该倾斜导电层在相邻的上一级台阶的侧面附近变薄,因此能够使该倾斜导电层与和倾斜导电层相连的导电层的上一层导电层相隔。但是,要想获得这种倾斜导电层,需要将sin膜以越朝相邻的上一级台阶的侧面变得越薄的方式堆积。但是,有下述顾虑:如此堆积的控制未必容易,如果变得过薄,最终导电层也会变薄,如果变得过厚,又会产生漏电流。

[0033]

根据实施方式的半导体装置的制造方法,槽部6(及沟槽t)的宽度能够通过堆积在积层体sk各阶侧面的sin膜2的厚度来控制,由此能够使导电层el2与和导电层el2相连的导电层el1的上一层导电层el1相隔,从而能够减少它们之间的漏电流。另外,由于能够使导电层el2的厚度均等,因此即便接触孔的位置存在偏差,也能够避免接触孔贯通导电层el2的情况。

[0034]

(变化例1)

[0035]

其次,参照图3,对实施方式的变化例1的半导体装置的制造方法进行说明。变化例1在所使用的模板的形状不同这一方面与实施方式不同,而在其他方面与实施方式相同。以下,以不同点为中心,对变化例1的半导体装置的制造方法进行说明。

[0036]

参照图3(a),与参照图1(a)至图1(c)所说明的内容相同地,形成sin膜2,该sin膜2覆盖阶梯形状的积层体sk的各阶侧面与上表面。以覆盖sin膜2的方式涂布抗蚀膜4,如图3(b)所示,将模板20压抵着该抗蚀膜4。此处,在模板20形成有突起部20p。突起部20p以与所关注台阶的上表面的下述位置对应的方式设置,该位置是比起该台阶的侧面,更接近于与该台阶相邻且高于该台阶的那一级台阶的侧面。换句话说,突起部20p以与近接于下述sin膜2的位置对应的方式设置,该sin膜2从所关注台阶的上表面升起,形成在相邻的上一级台阶的侧面。如果在模板20压抵着抗蚀膜4的状态下透过模板20向抗蚀膜4照射紫外光,那么抗蚀膜4硬化,如图3(c)所示,获得抗蚀膜4b(抗蚀图案)。

[0037]

接下来,与参照图1(f)所说明的内容相同地,对抗蚀膜4b实施例如灰化处理,将抗蚀膜4b整体缩小。由此,将各阶上表面的抗蚀膜4b保留,而将衬底s上表面与各阶侧面的抗蚀膜4b去除。由此,sin膜2露出于各阶的侧面,接下来,通过例如湿式蚀刻将该sin膜2去除(图3(d))。此处,在各阶上表面保留的抗蚀膜4b与相邻台阶的侧面之间形成有槽部6a。该槽部6a具有堆积在积层体sk各阶侧面的sin膜2的厚度(宽度)、及模板20的突起部20p的宽度两者的合计宽度。也就是说,变化例1中的槽部6a与实施方式的半导体装置的制造方法中所

形成的槽部6相比,变宽了模板20的突起部20p的宽度那么多。

[0038]

此外,sin层n露出于槽部6a的底部。该sin层n随着sin膜2的去除,从上表面向下略微凹陷。也就是说,以不会去除所有sin层n且在sin层n形成沟槽t的方式,一边管理例如蚀刻时间等一边去除sin膜2。

[0039]

其后,将积层体sk的各阶上保留的抗蚀膜4b去除(图3(e)),并以覆盖积层体sk的方式形成siox膜8(图3(f))。

[0040]

接着,如图3(g)所示,经由以贯通积层体sk的方式形成在积层体sk的例如中央部的贯通孔或槽(未图示),将积层体sk中的sin层n去除,而形成空间sp1。此时,各阶上表面保留的sin膜2也一起被去除。从而,在各阶最上部的siox层q之上形成具有高度l2的空间sp2,该空间sp2的高度l2高于空间sp1的高度l1。

[0041]

接下来,采用例如原子层沉积(atomic layer deposition)法等,在空间sp1及sp2中嵌入例如钨(w)等金属(图3(h))。由此,获得与空间sp1对应的导电层el1、及与空间sp2对应的导电层el2。此处,导电层el2的厚度与空间sp2的高度l2几乎相等,且大于与空间sp1的高度l1几乎相等的导电层el1的厚度。

[0042]

其后,形成从siox膜8的上表面贯通该siox膜8并到达导电层el2的接触孔,在接触孔中嵌入例如w,形成接点cc(图3(i))。

[0043]

如上所述,在变化例1的半导体装置的制造方法中,也能够在各阶的上表面形成厚于导电层el1的导电层el2,从而能够使接点cc与导电层el2接触,因此达成与实施方式的半导体装置的制造方法相同的效果。

[0044]

另外,根据变化例1的半导体装置的制造方法,设置在模板20的突起部20p使槽部6a的宽度大于堆积在各阶侧面的sin膜2的厚度,因此能够使导电层el2与和导电层el2相连的导电层el1的上一层导电层el1充分地相隔,因此,能够进一步减少它们之间的漏电流。

[0045]

(变化例2)

[0046]

其次,参照图5,对实施方式的变化例2的半导体装置的制造方法进行说明。以下,以与变化例1的不同点为中心进行说明。

[0047]

参照图5(a),将模板30压抵着形成在sin膜2上的抗蚀膜4。该模板30除了突起部20p以外,还具有阶部30s。阶部30s设置于下述位置,该位置是在模板30压抵着抗蚀膜4时,与堆积在积层体sk台阶侧面的sin膜2对应。另外,阶部30s的厚度与堆积在积层体sk台阶侧面的sin膜2的厚度几乎相等。

[0048]

如果在模板30压抵着抗蚀膜4的状态下透过模板30向抗蚀膜4照射紫外光,那么如图5(b)所示,获得抗蚀膜4c(抗蚀图案)。其次,将抗蚀膜4c缩小,将积层体sk各阶侧面的sin膜2、及衬底s上表面保留的抗蚀剂去除。由此,如图5(d)所示,sin膜2露出于积层体sk的各阶侧面。

[0049]

以下,实施与参照图3(d)至图4(i)所说明的步骤相同的步骤,形成接点。

[0050]

根据变化例2的半导体装置的制造方法,由于模板30具有阶部30s,因此通过模板30而形成的抗蚀膜4c在各阶上表面中的宽度会变小。从而,能够缩短将抗蚀膜4c缩小所需要的时间。

[0051]

对本发明的多个实施方式进行了说明,但这些实施方式仅作为示例而提出,并未意图限定发明的范围。这些新颖的实施方式能够以其他各种形态来实施,且在不脱离发明

主旨的范围内,能够进行各种省略、替换、变更。这些实施方式及其变化包含在发明的范围或主旨中,并且包含在权利要求书中所记载的发明及其等同的范围内。

[0052]

[符号的说明]

[0053]2ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

sin膜

[0054]

4,4a,4b,4c

ꢀꢀ

抗蚀膜

[0055]

6,6a

ꢀꢀꢀꢀꢀꢀꢀꢀ

槽部

[0056]8ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

siox膜

[0057]

10,20,30

ꢀꢀꢀꢀ

模板

[0058]

20p

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

突起部

[0059]

30s

ꢀꢀꢀꢀꢀꢀꢀꢀ

阶部

[0060]

cc

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接点

[0061]

el1,el2

ꢀꢀꢀꢀ

导电层

[0062]

sp1,sp2

ꢀꢀꢀꢀ

空间

[0063]

s

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

衬底

[0064]

q

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氧化硅(siox)层

[0065]

n

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氮化硅(sin)层

[0066]

sk

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

积层体

[0067]

t

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

沟槽

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1