存储器元件及其制造方法与流程

[0001]

本发明涉及一种存储器元件及其制造方法,尤其涉及一种非易失性存储器及其制造方法。

背景技术:

[0002]

快闪存储器元件属于非易失性存储器元件的一种,且在近年来逐渐成为储存媒体的主流技术之一。然而,在快闪存储器元件的造过程中,难以避免地会产生一些带电的离子。这些离子有可能进入快闪存储器元件的栅极结构中,而对快闪存储器的运作造成影响,进而可能降低快闪存储器的可靠度。

技术实现要素:

[0003]

本发明提供一种快闪存储器元件及其制造方法,可提高快闪存储器的可靠度。

[0004]

本发明实施例的存储器元件包括栅极堆叠结构、第一绝缘层、第二绝缘层以及第一间隙壁。栅极堆叠结构设置于衬底上。第一绝缘层覆盖栅极堆叠结构的顶面与侧壁。第二绝缘层覆盖第一绝缘层的表面。栅极堆叠结构的顶角区域被第一绝缘层与第二绝缘层覆盖。第一间隙壁位于栅极堆叠结构的侧壁上,且覆盖第二绝缘层的表面。第一间隙壁的最顶端低于第二绝缘层的最顶面。第二绝缘层具有沿衬底的表面而自栅极堆叠结构的侧壁往外延伸的延伸部分,且所述延伸部分的端面实质上共面于第一间隙壁的表面。

[0005]

本发明实施例的存储器元件的制造方法包括下列步骤:在衬底上形成栅极堆叠结构;在衬底上依序形成覆盖栅极堆叠结构的第一绝缘层、第二绝缘层与掩模材料层;对掩模材料层进行离子植入工艺,以在掩模材料层中形成掺杂部分,其中掺杂部分罩盖栅极堆叠结构的顶部;以掺杂部分作为掩模而对掩模材料进行第一图案化工艺,以移除掩模材料层的沿衬底的表面延伸的底部部分;以及以第二图案化工艺移除掩模材料层的掺杂部分以及第二绝缘层的位于栅极堆叠结构的周围且暴露出来的底部部分,其中掩模材料层的残留部分形成第一间隙壁。

[0006]

基于上述,本发明实施例的存储器元件包括设置于衬底上的栅极堆叠结构,且包括覆盖栅极堆叠结构的第一绝缘层、第二绝缘层以及第一间隙壁。第一绝缘层覆盖栅极堆叠结构的顶面与侧壁,而第二绝缘层覆盖于第一绝缘层上。第一间隙壁覆盖于第二绝缘层上,且位于栅极堆叠结构的侧壁上。此外,第一间隙壁的最顶端低于第二绝缘层的最顶面。特别来说,栅极堆叠结构的顶角区域被第一绝缘层与第二绝缘层覆盖,而可防止工艺中所产生的带电离子进入栅极堆叠结构。因此,可提高存储器元件的可靠度。

[0007]

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

[0008]

图1是依照本发明一些实施例的流程图;

[0009]

图2a至图2k是图1所示的存储器元件的制造方法的各阶段的结构的剖视示意图;

[0010]

图3是依照本发明另一些实施例的剖视示意图。

具体实施方式

[0011]

请参照图1与图2a,进行步骤s100,以提供衬底100。接着,进行步骤s102,以在衬底100上形成栅极堆叠结构102。各栅极堆叠结构102包括穿隧介电层104、第一栅极106、第二栅极108以及栅极间介电层110。在本实施例中,由衬底100往上可依序为穿隧介电层104、第一栅极106、栅极间介电层110以及第二栅极108。在一些实施例中,穿隧介电层104的材料可为氧化硅、碳化硅或其他包含四价元素的介电材料。第一栅极106可作为浮置栅极,且第一栅极106的材料例如为多晶硅。在一些实施例中,栅极间介电层110可为多层结构。此多层结构可包括彼此交替堆叠的两种介电材料层(未示出)。举例而言,栅极间介电层110可为氧化硅-氮化硅-氧化硅(ono)多层结构。在一些实施例中,第二栅极108也可为多层结构。举例而言,第二栅极108可包括栅极层108a以及位于栅极层108a上的栅极层108b。栅极层108a与栅极层108b的材料可分别为导体材料。穿隧介电层104、第一栅极106、栅极间介电层110与第二栅极108起初可全面地形成于衬底100上。接着,图案化此些全面披覆的穿隧介电层104、第一栅极106、栅极间介电层110与第二栅极108,而形成如图2a所示的多个栅极结构102。在一些实施例中,形成穿隧介电层104、第一栅极106、第二栅极108与栅极间介电层110的方法可包括化学气相沉积工艺、镀覆工艺、其类似者或其组合。在一些实施例中,在第一栅极106与第二栅极108的过程中,可掺杂3价元素或5价元素。

[0012]

此外,在一些实施例中,各栅极堆叠结构102更可包括设置于第二栅极108上的顶盖结构112。顶盖结构112可包括顶盖层112a与设置于顶盖层112a上的顶盖层112b。在一些实施例中,顶盖层112a的材料与顶盖层112b的材料可分别为氮化硅与氧化硅,且其形成方法可包括化学气相沉积工艺。此外,在形成栅极堆叠结构102的过程中,顶盖结构112中的顶盖层112b可作为蚀刻工艺的硬掩模结构。形成栅极堆叠结构102的方法可包括一次微影工艺与至少两次蚀刻工艺。在所形成的栅极堆叠结构102中,顶盖结构112的侧壁可实质上共面于第二栅极108、栅极间介电层110、第一栅极106与穿隧介电层104的侧壁。

[0013]

请参照图1、图2a与图2b,进行步骤s104,以依序形成全面披覆的第一绝缘层114、第二绝缘层116与掩模材料层118。第一绝缘层114、第二绝缘层116与掩模材料层118共形地覆盖图2a所示的结构。换言之,栅极堆叠结构102的顶面与侧壁以及衬底100的未交叠于栅极堆叠结构102的部分均被第一绝缘层114、第二绝缘层116与掩模材料层118覆盖。在一些实施例中,第一绝缘层114与掩模材料层118可由第一材料构成,且第二绝缘层116可由对于第一材料具有蚀刻选择比的第二材料构成。举例而言,第一材料可为氧化硅,而第二材料可为氮化硅。此外,在一些实施例中,可通过化学气相沉积工艺形成第一绝缘层114、第二绝缘层116与掩模材料层118。

[0014]

请参照图1、图2b与图2c,进行步骤s106,以对掩模材料层118进行第一离子植入工艺。第一离子植入工艺可为斜向的离子植入工艺。在第一离子植入工艺期间,掺质可由各栅极堆叠结构102的一侧沿倾斜入射方向td1进入至掩模材料层118中。举例而言,上述倾斜入射方向td1与水平方向hd之间的夹角θ1可小于90

°

,例如是1

°

至45

°

。如此一来,掩模材料层118的未被遮蔽的第一部分118a经掺杂而被改质,而掩模材料层118的其他部分则保持原本

的成分。举例而言,未经掺杂的掩模材料层118可由氧化硅构成,而掩模材料层118的第一部分118a可经含氮的掺质掺杂为氮氧化硅或氮化硅。上述含氮的掺质可包括si3n4、氮氧化硅或其他相对于掩模材料层118的未经掺杂部分而具有足够蚀刻选择比的材料。在一些实施例中,掩模材料层118的经掺杂的第一部分118a可包括掩模材料层118的位于各栅极堆叠结构102上方的顶部区域以及位于各栅极堆叠结构102的一侧的纵向区域。上述纵向区域由对应的顶部区域往下延伸,且并未延伸至掩模材料层118的底部。换言之,各栅极堆叠结构102的顶面以及一侧壁的上部被掩模材料层118的经掺杂的第一部分118a覆盖,而上述侧壁的下部则是被掩模材料层118的未经掺杂的部分覆盖。在一些实施例中,掩模材料层118的第一部分118a的高度h1相对于掩模材料层118的总高度ht的比例可为1:3至1:10,但第一部分118a的高度h1大于或等于110nm。

[0015]

请参照图1、图2c与图2d,进行步骤s108,以对掩模材料层118进行第二离子植入工艺。第一离子植入工艺与第二离子植入工艺均可为斜向的离子植入工艺且两者可使用相同的掺质。在第二离子植入工艺中,掺质沿着倾斜入射方向td2进入至掩模材料层118中。倾斜入射方向td2与水平方向hd之间的夹角θ2小于90

°

,例如是1

°

至45

°

。在一些实施例中,夹角θ1可实质上等于夹角θ2,但倾斜入射方向td1与倾斜入射方向td2可彼此相对。在第二离子植入工艺期间,掩模材料层118的未被遮蔽的第二部分118b经掺质掺杂。在一些实施例中,上述的第二部分118b可包括掩模材料层118的位于各栅极堆叠结构102上方的顶部区域以及位于各栅极堆叠结构102的一侧的纵向区域。上述纵向区域由对应的顶部区域往下延伸,且并未延伸至掩模材料层118的底部。在一些实施例中,第二离子植入工艺期间所形成的第二部分118b局部地重叠于第一离子植入工艺期间所形成的第一部分118a。举例而言,第一部分118a的顶部区域可至少部分地重叠于第二部分118b的顶部区域。如此一来,这些重叠区域受到多次掺杂,而可具有较高的掺杂浓度。另一方面,第一部分118a的纵向区域与第二部分118b的纵向区域可局部地覆盖各栅极堆叠结构102的彼此相对的两侧壁。在一些实施例中,掩模材料层118的第二部分118b的高度h2可实质上等于第一部分118a的高度h1。

[0016]

在一些实施例中,完成上述的第一离子植入工艺与第二离子植入工艺之后,对掩模材料层118的经掺杂部分进行去耦等离子体氮化(decoupled plasma nitridation,dpn)处理,以使植入于掩模材料层118的第一部分118a与第二部分118b的掺质与掩模材料层118的材料产生反应。如此一来,可有效地协助将掩模材料层118的第一部分118a与第二部分118b改质,以使掩模材料层118的第一部分118a与第二部分118b的材料相对于掩模材料层118的其他部分的材料而具有足够的蚀刻选择比。在一些实施例中,掩模材料层118的第一部分118a与第二部分118b的表层被改质,而形成氮化物层。此外,在一些实施例中,dpn处理包括在氮气环境下对晶圆进行热处理。上述热处理的时间可少于或等于约24小时。再者,在一些实施例中,自进行第一与第二离子植入工艺的站点至热处理的站点之间的保存或运送时间不超过24小时。在元件的保存或运送期间,元件可放置于富含氮气或惰性气体(例如是ar气)的正压环境中。如此一来,可延长元件对于保存或运送时间的容忍范围。

[0017]

在下文中,第一部分118a与第二部分118b共同地称为掺杂部分dp。各掺杂部分dp具有类似于帽盖的形状,而罩盖对应栅极堆叠结构102的顶部。掺杂部分dp的成分不同于掩模材料层118的其他部分,而可相对于掩模材料层118的其他部分而具有蚀刻选择比。如此一来,在后续对掩模材料层118进行蚀刻工艺时,掺杂部分dp可作为掩模。

[0018]

请参照图1、图2d与图2e,进行步骤s110,以移除掩模材料层118的位于相邻栅极堆叠结构102之间的底部区域。在一些实施例中,可通过非等向性蚀刻工艺来进行步骤s110。在上述的非等向性蚀刻工艺期间,可以掩模材料层118的掺杂部分dp作为掩模,来选择性地移除掩模材料层118的未掺杂部分的特定区域。如图2d所示,掩模材料层118的未掺杂部分包括覆盖于各栅极堆叠结构102的侧壁上的纵向区域以及位于相邻纵向区域之间的底部区域。作为掩模的掺杂部分dp交叠于未掺杂部分的纵向区域,而并未交叠于未掺杂部分的底部区域。如此一来,在以掺杂部分dp作为掩模来进行非等向性蚀刻工艺时(请参照图2e),未掺杂部分的底部区域会被移除,而未掺杂部分的纵向区域则可保留下来。由此可知,移除掩模材料层118的未掺杂部分的特定区域的步骤可为自对准(self-aligning)的,而不需要额外进行微影工艺来定义欲移除的区域。在下文中,掩模材料层118的未掺杂部分的残留区域(亦即上述的纵向区域)称作第一间隙壁118c。此外,在移除掩模材料层118的未掺杂部分的底部区域之后,可暴露出下方的第二绝缘层116。

[0019]

请参照图1、图2e与图2f,进行步骤s112,以移除掩模材料层118的掺杂部分dp以及第二绝缘层116的位于相邻栅极堆叠结构102之间且暴露出来的部分(如图2e所示)。在一些实施例中,可通过非等向性蚀刻工艺来进行步骤s112。此外,在一些实施例中,掩模材料层118的掺杂部分dp由氮氧化硅或氮化硅构成,且其蚀刻速率相近于或实质上等于氮化硅所构成的第二绝缘层117的蚀刻速率。另一方面,掩模材料层118的未掺杂部分(亦即第一间隙壁118c)以及第一绝缘层114则可由氧化硅构成,且相对于第三绝缘材料118的掺杂部分dp以及第二绝缘材料116而具有较高的蚀刻选择比。如此一来,在进行非等向性蚀刻工艺时,可选择性地移除掩模材料层118的掺杂部分dp以及第二绝缘层116的暴露部分(如图2e所示),且此非等向性蚀刻工艺可停止于暴露出第一绝缘层114的位于相邻第一间隙壁118c之间的部分时。在一些实施例中,掩模材料层118(如图2c所示)的厚度约等于或大于第二绝缘层116的厚度。举例而言,第二绝缘层116的厚度对于掩模材料层118的厚度的比值范围约为1至1.25。在此些实施例中,在实质上完整地移除掩模材料层118的掺杂部分dp以及第二绝缘层116的位于相邻第一间隙壁118c之间的底部部分时,仍可至少部分地保留第二绝缘层116的原本被掺杂部分dp覆盖的顶部部分。因此,在完成步骤s112之后,各栅极堆叠结构102的顶部仍可完整地被第一绝缘层114与第二绝缘层116罩盖(cap)。

[0020]

在一些实施例中,在步骤s112的期间,有可能部分地移除第二绝缘层116的罩盖于各栅极堆叠结构102上的顶部部分。举例而言,第二绝缘层116的顶角区域可能被切除,而形成斜面ts。此外,在一些实施例中,在步骤s112的期间,有可能部分地移除第一间隙壁118c。举例而言,在进行步骤s112之前(请参照图2e),第一间隙壁118c可为覆盖于各栅极堆叠结构102的侧壁的绝缘墙。在步骤s112的期间,第一间隙壁118c可经部分地移除而形成楔形(wedge shape)结构。如图2f所示,第一间隙壁118c的顶部的宽度可小于底部的宽度,且第一间隙壁118c的暴露出的表面可实质上为斜面或曲面。另一方面,第一绝缘层114与第二绝缘层116的被第一间隙壁118c覆盖的部分可类似为l形。再者,在一些实施例中,在步骤s112的期间,也有可能部分地移除第一绝缘层114的位于相邻第一间隙壁118c之间的底部部分。在此些实施例中,第一绝缘层114的此些底部部分的厚度可小于第一绝缘层114的其他部分的厚度。

[0021]

请参照图1、图2f与图2g,进行步骤s114,以形成第三绝缘层120。在一些实施例中,

第三绝缘层120全面地形成于图2f所示的结构上,且共形地覆盖图2f所示的结构。换言之,第一绝缘层114、第二绝缘层116以及第一间隙壁118c的暴露出的表面此时皆被第三绝缘层120覆盖。在一些实施例中,第三绝缘层120的材料可等同于第一间隙壁118c与第一绝缘层114的材料,而相异于第二绝缘层116的材料。举例而言,第三绝缘层120、第一间隙壁118c与第一绝缘层114可由氧化硅构成,而第二绝缘层116可由氮化硅构成。此外,在一些实施例中,可通过化学气相沉积工艺形成第三绝缘层120。

[0022]

请参照图1、图2g与图2h,进行步骤s116,以移除第三绝缘层120的延伸于栅极堆叠结构102上以及沿衬底100的表面延伸的水平延伸部分。在一些实施例中,可通过非等向性蚀刻来进行步骤s116。在上述的非等向性蚀刻工艺期间,基于到达角(arriving angle)的差异,可选择性地移除第三绝缘层120的水平延伸部分,而保留第三绝缘层120的纵向延伸部分。如图2g所示,第三绝缘层120的水平延伸部分原先覆盖第二绝缘层116的最顶面以及第一绝缘层114的位于相邻第一间隙壁118c之间的底部部分。在移除第三绝缘层120的水平延伸部分后,可暴露出第二绝缘层116的最顶面。此外,在一些实施例中,在移除第三绝缘层120的水平延伸部分的期间,也可局部地移除第一绝缘层114的上述底部部分,而暴露出衬底100。在其他实施例中,第一绝缘层114的位于相邻第一间隙壁118c之间的部分在此步骤(亦即步骤s116)中并未被移除,而是在后续步骤(例如是图2k所示的步骤s122)中被移除。在下文中,第三绝缘层120的残留部分(亦即上述的纵向延伸部分)称作第二间隙壁120a。

[0023]

请参照图1、图2h与图2i,进行步骤s118,以形成导体层122。在一些实施例中,导体层122全面地形成于图2h所示的结构上,且填入于相邻栅极堆叠结构102之间的凹陷中。如此一来,衬底100、第二间隙壁120a以及第二绝缘层116的暴露部分可被导体层122覆盖。在一些实施例中,导体层122可接触于衬底100的暴露部分。此外,在一些实施例中,导体层122的材料可为多晶硅,且可通过化学气相沉积工艺而形成导体层122。

[0024]

请参照图1、图2i与图2j,进行步骤s120,以在导体层122中形成多个绝缘插塞124。多个绝缘插塞124位于多个栅极堆叠结构102上方,且分别交叠于多个栅极堆叠结构102。在一些实施例中,可在导体层122的顶部形成分别交叠于多个栅极堆叠结构102的多个开口,接着将绝缘材料填入此些开口中,而形成多个绝缘插塞124。此外,在一些实施例中,上述开口可暴露出第二绝缘层116的最顶面以及第二间隙壁120a的最顶面。如此一来,后续所形成的绝缘插塞124可覆盖第二绝缘层116与第二间隙壁120a的最顶面。在一些实施例中,用于形成绝缘插塞124的绝缘材料可为氮化硅,且可通过化学气相沉积工艺形成绝缘插塞124。

[0025]

请参照图1、图2j与图2k,进行步骤s122,以移除导体层122并形成多个接触结构126。在一些实施例中,可通过非等向性蚀刻工艺或等向性蚀刻工艺来移除导体层122。此外,在一些实施例中,形成多个接触结构126的方法可包括先在衬底上形成介电层(未示出)。接着,可在此介电层中形成多个穿孔,且在此些穿孔中填入导体材料,以形成多个接触结构126。举例而言,用于形成接触结构126的导体材料可为w、cu、al或包含上述元素的至少一者的硅化物,且接触结构126的形成方法可包括物理气相沉积工艺、化学气相沉积工艺、镀覆工艺或其组合。各接触结构126可电性连接于衬底100中的掺杂区(未示出)与设置于接触结构126上方的位线/源极线(未示出)之间。此外,各栅极堆叠结构102可位于两相邻接触结构126之间。

[0026]

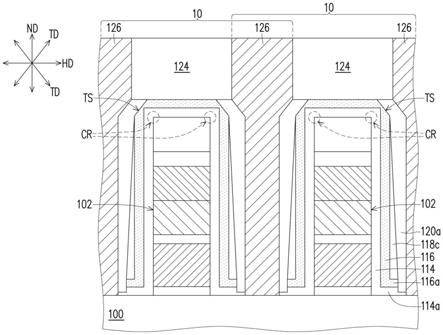

至此,已完成多个存储器元件10的制造。各存储器元件10可包括设置于衬底100上

的栅极堆叠结构102,且包括覆盖栅极堆叠结构102的第一绝缘层114、第二绝缘层116以及第一间隙壁118c。第一绝缘层114覆盖栅极堆叠结构102的顶面与侧壁,而第二绝缘层116覆盖于第一绝缘层114上。第一间隙壁118c覆盖于第二绝缘层116上,且位于栅极堆叠结构102的侧壁上。此外,第一间隙壁118c的最顶端低于第二绝缘层116的最顶面。特别来说,栅极堆叠结构102的顶角区域cr被第一绝缘层114与第二绝缘层116覆盖,而可防止工艺中所产生的带电离子进入栅极堆叠结构102。因此,可提高存储器元件10的可靠度。在一些实施例中,第一绝缘层114与第二绝缘层116可由不同的材料构成,而可阻挡带有不同电性(例如是正电与负电)的离子由栅极堆叠结构102的顶角区域cr进入栅极堆叠结构102。举例而言,第一绝缘层114可由氧化硅构成,而第二绝缘层116可由氮化硅构成。

[0027]

在一些实施例中,如图2k所示,第二绝缘层116的覆盖栅极堆叠结构102的顶角区域cr的部分具有倾斜表面ts。此倾斜表面ts的延伸方向td交错于水平方向hd以及衬底100的法线方向nd。再者,在一些实施例中,第一绝缘层114与第二绝缘层116也可向外延伸至衬底100的位于栅极堆叠结构102周围的部分上,而可具有l形的底部。在此些实施例中,第二绝缘层116的延伸部分116a的端面可实质上共面于第一间隙壁118c的表面。

[0028]

在一些实施例中,各存储器元件10还包括第二间隙壁120a。第二间隙壁120a设置于栅极堆叠结构102的侧壁上。第二间隙壁120a位于第一间隙壁118c的外侧,且向上延伸以覆盖栅极堆叠结构102的顶角区域cr。如此一来,通过设置第二间隙壁120a,可更进一步地阻挡带电离子由栅极堆叠结构102的顶角区域cr进入栅极堆叠结构102。在一些实施例中,第二间隙壁120a的顶面实质上共面于第二绝缘层116的最顶面。此外,在第二绝缘层116的覆盖栅极堆叠结构102的顶角区域cr的部分具有倾斜表面的实施例中,第二间隙壁120a的覆盖栅极堆叠结构102的顶角区域cr的部分也可对应地具有倾斜表面。在此些实施例中,第二间隙壁120a的此倾斜表面的延伸方向可实质上平行于第二绝缘层116的倾斜表面的延伸方向td。再者,在第一绝缘层114与第二绝缘层116由栅极堆叠结构102的侧壁往外延伸的实施例中,第二间隙壁120a可覆盖第二绝缘层116的延伸部分116a的端面。此外,第一绝缘层114的延伸部分114a的端面可实质上共面于第二间隙壁120a的表面,且延伸部分114a的交叠于第二间隙壁120a的区域可较延伸部分114a的其他区域而具有较小的厚度。

[0029]

在一些实施例中,各存储器元件10还包括绝缘插塞124。绝缘插塞124设置于第二绝缘层116的最顶面上。在一些实施例中,绝缘插塞124覆盖第二间隙壁120a的最顶面。在设置有绝缘插塞124的实施例中,各栅极堆叠结构102的顶面可被第一绝缘层114、第二绝缘层116以及绝缘插塞124覆盖,而阻挡由各栅极堆叠结构102的上方进入各栅极堆叠结构102的带电离子。

[0030]

图3是依照本发明另一些实施例的存储器元件20的剖视示意图。图3所示的存储器元件20相似于图2k所示的存储器元件,以下仅描述两者的差异处,相同或相似处则不再赘述。

[0031]

请参照图3,在存储器元件20中,第二绝缘层216的覆盖栅极堆叠结构102的顶角区域cr的部分具有圆弧表面rs。在一些实施例中,第二绝缘层216的此圆弧表面为外凸的(convex)圆弧表面。对应地,第二间隙壁220a的覆盖栅极堆叠结构102的顶角区域cr的部分也可具有圆弧表面,且此圆弧表面可为外凸的圆弧表面。

[0032]

在图3所示的实施例中,在图案化第二绝缘层216时(例如是参照图2f所示的步骤

s112),可进行一或多次沉积-蚀刻循环。举例而言,可通过高密度等离子体化学气相沉积工艺(high density plasma chemical vapor deposition,hdp-cvd)来进行上述包括至少一沉积-蚀刻循环的图案化步骤。如此一来,如图3所示,可使经图案化的第二绝缘层216的覆盖栅极堆叠结构102的顶角区域cr的部分具有圆弧表面rs,且可使后续形成于第二绝缘层216上的第二间隙壁220a的对应部分也具有圆弧表面。

[0033]

综上所述,本发明实施例的存储器元件包括设置于衬底上的栅极堆叠结构,且包括覆盖栅极堆叠结构的第一绝缘层、第二绝缘层以及第一间隙壁。第一绝缘层覆盖栅极堆叠结构的顶面与侧壁,而第二绝缘层覆盖于第一绝缘层上。第一间隙壁覆盖于第二绝缘层上,且位于栅极堆叠结构的侧壁上。此外,第一间隙壁的最顶端低于第二绝缘层的最顶面。特别来说,栅极堆叠结构的顶角区域被第一绝缘层与第二绝缘层覆盖,而可防止工艺中所产生的带电离子进入栅极堆叠结构。因此,可提高存储器元件的可靠度。

[0034]

虽然本发明已以实施例揭示如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的更改与润饰,故本发明的保护范围当视权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1