场限环-沟槽负斜角复合终端结构的制备方法与流程

[0001]

本发明属于功率半导体器件技术领域,具体涉及一种场限环-沟槽负斜角复合终端结构及制备方法。

背景技术:

[0002]

功率高压mos器件在研发过程中,终端技术的设计将会直接影响其器件的耐压和稳定性。常见的结终端技术分为平面结终端技术和台面结终端技术,其平面结终端技术包括场板、场限环、横向变掺杂、结终端延伸及复合结终端技术等;台面终端技术包括机械磨角、沟槽刻蚀和填充等技术。

[0003]

为了提高功率mos器件的终端击穿电压,通常采用的是场板和场限环的复合结构。此结构制作工艺比较简单,但对工艺参数的设计要求比较严格。并且当耐压较高时,占用芯片的面积较大,导致其反向漏电流也很大,即芯片的利用率低。因此,现有的终端技术不能折中器件的终端击穿电压和芯片利用率,从而很大程度的限制了功率高压mos器件的开发。

技术实现要素:

[0004]

本发明的目的是提供一种场限环-沟槽负斜角复合终端结构及制备方法,解决了功率mos器件的终端占用芯片面积大、终端击穿电压低以及高温稳定性差的问题。

[0005]

本发明所采用的技术方案为:场限环-沟槽负斜角复合终端结构的制备方法,其特征在于:所述方法包括以下步骤:步骤1、制备器件的有源区和终端区,终端区设置至少一个以上的场限环;步骤2、用掩模版1进行掩蔽曝光,在终端区刻蚀垂直沟槽;步骤3、用掩模版2进行掩蔽曝光,在终端区进行二次刻蚀,形成负斜角沟槽;步骤4、在负斜角沟槽区填充氮氧化硅绝缘材料,最后进行背面减薄、镀金及三端电极引出,得到场限环-沟槽负斜角复合终端结构。

[0006]

步骤2中,利用等离子体刻蚀机在终端区进行垂直刻蚀,形成两侧面垂直、高度为d1、窗口宽度为w1 的沟槽。

[0007]

步骤3中,利用等离子体刻蚀机在终端区进行二次刻蚀,在侧面形成负斜角为θ、高度为d的斜面。

[0008]

步骤4中,利用化学气相淀积法对负斜角沟槽区填充氮氧化硅绝缘材料,并用刻蚀或者机械研磨的方式去除多余的氮氧化硅;最后进行背面减薄、镀金及三端电极引出,得到场限环-沟槽负斜角复合终端结构。

[0009]

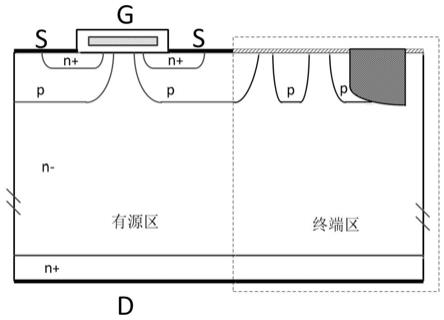

芯片中央为有源区,有源区外围为终端区,有源区和终端区共用n+衬底,即器件的漏极d,n+衬底上方设置为n-漂移区。

[0010]

在有源区的n-漂移区中设置有多个并联的元胞,元胞内与n-漂移区相邻的是p-body区,p-body区中有n+源区且上方设有源电极s。

[0011]

多晶硅栅极g设置在两个相邻源电极s之间,多晶硅栅极g做在栅氧化层上。

[0012]

在终端区,场限环p区与元胞中的p-body区同时形成,在第二个场限环中设置有沟槽负斜角。

[0013]

负斜角的角度为2

°

~4

°

。

[0014]

沟槽负斜角通过两步光刻-刻蚀完成,将沟槽设置为两侧垂直、单边斜角且深入到n

-ꢀ

漂移区,此沟槽用氮氧化硅来填充。

[0015]

本发明具有以下优点:本发明适用于功率mos 器件的场限环-沟槽负斜角复合终端结构,由于工艺简单,高温稳定性好,并且能在芯片面积与击穿电压两者之间取得较好的折衷,因此,该复合终端也可推广到igbt和iegt等功率器件。

附图说明

[0016]

图1是本发明步骤1的制作效果示意图;图2是本发明步骤2的制作效果示意图;图3是本发明步骤3的制作效果示意图;图4是本发明场限环-沟槽负斜角复合终端结构的剖面示意图;图5是采用本发明复合终端结构功率mosfet器件击穿特性的模拟曲线;图6是采用本发明复合终端结构功率mosfet器件在常温和高温下的击穿特性曲线;图7是本发明的另一种场限环-沟槽负斜角终端结构的剖面示意图。

具体实施方式

[0017]

下面结合具体实施方式对本发明进行详细的说明。

[0018]

本发明涉及一种场限环-沟槽负斜角复合终端结构的制备方法,所述方法包括以下步骤:步骤1、制备器件的有源区和终端区,终端区设置至少一个以上的场限环;步骤2、用掩模版1进行掩蔽曝光,在终端区刻蚀垂直沟槽;步骤3、用掩模版2进行掩蔽曝光,在终端区进行二次刻蚀,形成负斜角沟槽;步骤4、在负斜角沟槽区填充氮氧化硅绝缘材料,最后进行背面减薄、镀金及三端电极引出,得到场限环-沟槽负斜角复合终端结构。

[0019]

步骤2中,利用等离子体刻蚀机在终端区进行垂直刻蚀,形成两侧面垂直、高度为d1、窗口宽度为w1 的沟槽。

[0020]

步骤3中,利用等离子体刻蚀机在终端区进行二次刻蚀,在侧面形成负斜角为θ、高度为d的斜面。

[0021]

步骤4中,利用化学气相淀积法对负斜角沟槽区填充氮氧化硅绝缘材料,并用刻蚀或者机械研磨的方式去除多余的氮氧化硅;最后进行背面减薄、镀金及三端电极引出,得到场限环-沟槽负斜角复合终端结构。

[0022]

上述制备方法得到的场限环-沟槽负斜角复合终端结构,适用于功率mos器件,芯片中央为有源区,有源区外围为终端区,有源区和终端区共用n+衬底,即器件的漏极d,n+衬底上方设置为n-漂移区。

[0023]

在有源区的n-漂移区中设置有多个并联的元胞,元胞内与n-漂移区相邻的是p-body区,p-body区中有n+源区且上方设有源电极s。多晶硅栅极g设置在两个相邻源电极s之间,多晶硅栅极g做在栅氧化层上。

[0024]

在终端区,场限环p区与元胞中的p-body区同时形成,在第二个场限环中设置有沟槽负斜角。负斜角的角度为2

°

~4

°

。沟槽负斜角通过两步光刻-刻蚀完成,将沟槽设置为两侧垂直、单边斜角且深入到n

-ꢀ

漂移区,此沟槽用氮氧化硅来填充。

[0025]

参见附图对本发明进行进一步详细的说明:步骤1、用常规工艺制备器件的有源区,终端区设置至少有一个以上的场限环,主结与场限环1的间距s1,场限环1与场限环2的间距s2;终端区的场限环p区与有源区p-body区工艺一致,同时制作,参照图1;步骤2、用掩模版1进行掩蔽曝光,利用等离子体刻蚀机在终端区进行垂直刻蚀,形成两侧面垂直、高度为d1、窗口宽度为w1 的沟槽,参照图2;步骤3、用掩模版2进行掩蔽曝光,利用等离子体刻蚀机在终端区进行二次刻蚀,形成侧面负斜角为θ、斜面高度为d,参照图3;步骤4、利用化学气相淀积法对负斜角沟槽区填充氮氧化硅绝缘材料,并用刻蚀或者机械研磨的方式去除多余的氮氧化硅。最后进行背面减薄、镀金及三端电极引出,得到图4所示结构。

[0026]

本发明的场限环-沟槽负斜角复合终端结构,其耐压机理是:终端区设置的p型场限环,增大了有源区主结耗尽层的曲率半径,缓解了表面电场集中,降低了表面电场强度,从而提高了终端耐压。由于沟槽负斜角θ,会使空间电荷区展宽到了斜面,也使表面的电场集中得到缓解,耐压提高。因此,p型场限环与沟槽负斜角结合,会更大程度的缓解表面电场的集中,使得终端耐压提高。

[0027]

本发明适用于功率mos 器件的场限环-沟槽负斜角复合终端结构中,由于场限环的技术已成熟,此处只讨论在场限环基础上所加的沟槽负斜角的重要参数。沟槽的深度、宽度、斜角θ以及斜角的高度这些参数的设置均是至关重要的。

[0028]

以600v功率mosfet为例,选取最优参数:s1为5um、s2为10um 、d1为3.5μm、w1为90μm、θ为3

°

、d为2.5μm,对其击穿特性进行模拟仿真。

[0029]

图5给出了本发明复合终端结构功率mosfet器件击穿特性的模拟曲线,其中黑实线表示采用场限环-沟槽负斜角复合终端的击穿特性,黑虚线表示其体内平行平面结的击穿特性。可见,采用上述复合终端的功率mosfet 的终端击穿电压约为640v,平面结击穿电压约为688v,约为平面结的93%,其对应的终端区为160μm。通常,采用场限环结构只能实现平行平面结85%的击穿电压,且场限环尺寸至少需要210μm。这说明,采用该复合终端结构不仅提高了功率mosfet器件的体击穿电压,而且还能缩小终端面积,提高芯片利用率。

[0030]

图6是采用本发明复合终端结构功率mosfet器件在常温和高温下的击穿特性。

[0031]

本发明是适用于功率mosfet器件的复合终端结构,模拟其在常温(300k)和高温(420k)下的击穿特性曲线,由图可见,与具有相同终端尺寸的沟槽负斜角终端结构相比,常温下的终端击穿电压基本一致,但其在高温下的终端击穿电压更高、漏电流密度更低。所以,本发明的场限环-沟槽负斜角复合终端结构具有更好的高温稳定性。

[0032]

图7是本发明的另一种场限环-沟槽负斜角终端结构的剖面示意图;本发明实施例

2 的沟槽负斜角结构是,整个沟槽与表面法线方向夹角为δ,沟槽中填充氮氧化硅。由于终端击穿电压与沟槽底部的水平夹角成正比,同时与斜角深度成反比,因此此沟槽结构更有利于折中斜角高度和水平夹角。此沟槽底部呈斜面,同样也可减小沟槽底部电场线的分布曲率,使沟槽底部承受的耐压变大。采用实施例2 的沟槽负斜角结构,也可获得接近平行平面结的击穿电压,并且所需的沟槽深度和终端区尺寸均比上述结构的小。可见,实施例2 的沟槽负斜角结构比前述的第一种结构在节约终端区面积与提高器件终端击穿电压方面更为优越。但其制造工艺难度较大且成本比较高。

[0033]

综上所述,本发明适用于功率mos 器件的场限环-沟槽负斜角复合终端结构,由于工艺简单,高温稳定性好,并且能在芯片面积与击穿电压两者之间取得较好的折衷。因此,该复合终端也可推广到igbt和iegt等功率器件。

[0034]

本发明的内容不限于实施例所列举,本领域普通技术人员通过阅读本发明说明书而对本发明技术方案采取的任何等效的变换,均为本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1