半导体测试芯片及其制作方法与流程

1.本发明涉及一种半导体芯片及其制作方法,特别是涉及一种用于打线可靠度测试的半导体测试芯片及其制作方法。

背景技术:

2.随着电子产业品轻薄短小的需求及半导体技术的发展,半导体芯片的尺寸也越发微缩。其中,打线焊接则是能够让微缩尺寸的半导体芯片对外电连接的一重要技术,因此,如何确保半导体芯片打线的可靠度则是相关业者积极关注的重要课题。

3.半导体芯片用于与打线连接的金属层一般是由铝或铜构成。然而,铝或铜由于容易被氧化,以及容易吸附外在环境的异质离子,因此,当将表面氧化或是吸附异质离子(例如氯离子、氮离子等)的金属层进行打线、封装制成半导体组件使用的过程,由于所述金属氧化物及吸附于金属层的异质离子会影响该金属层的表面性质,或进一步对该金属层造成的腐蚀,或是于打线金属与金属层之间产生影响密着性的介金属化合物等,使得打线于半导体组件的使用过程剥离或脱落,而对组件的可靠度造成不良影响。

4.因此,为了确保芯片的可靠度与良率,于封装前一般会先对半导体组件进行打线的可靠度测试。然而,可靠度测试由于需模拟不同的环境条件并需要长时间测试,因此,测试极为耗时。

技术实现要素:

5.本发明的目的在于提供一种供用于半导体组件的打线可靠度测试的半导体测试芯片。

6.本发明半导体测试芯片,包含半导体基底及至少一测试芯片。

7.该至少一测试芯片设置在该半导体基底上,包括反向该半导体基底的顶面,及至少一自该顶面对外裸露的电连接垫。该电连接垫包含金属层及以原子沉积方式形成于该金属层的至少部分表面的金属化合物层。

8.较佳地,本发明所述的半导体测试芯片,其中,该金属化合物层包括含卤素金属化合物、含氮金属化合物,及含氧金属化合物的其中至少一者。

9.较佳地,本发明所述的半导体测试芯片,其中,该金属化合物层的厚度介于2nm至50nm。

10.较佳地,本发明所述的半导体测试芯片,其中,该至少一测试芯片还包含供该至少一测试芯片对外电连接的测试电路。

11.较佳地,本发明所述的半导体测试芯片,其中,该半导体测试芯片包含多个阵列分布于该半导体基底的测试芯片,其中,每一测试芯片还包含测试电路,且所述测试芯片可借由所述测试电路电连接。

12.较佳地,本发明所述的半导体测试芯片,其中,该每一测试芯片还具有位于该测试电路上方并与该测试电路电连接的重布线路,及覆盖该重布线路并具有至少一开口的介电

层,每一电连接垫与该重布线路电连接并自相应的其中一开口对外裸露。

13.较佳地,本发明所述的半导体测试芯片,其中,该金属层与该测试电路电连接,且该金属化合物层完全覆盖该金属层表面。

14.较佳地,本发明所述的半导体测试芯片,其中,该金属层与该测试电路电连接,且该金属化合物层部分覆盖该电连接垫表面。

15.较佳地,本发明所述的半导体测试芯片,其中,该金属化合物层还延伸覆盖该介电层。

16.本发明的另一目的在于提供一种供用于半导体组件打线可靠度测试的半导体测试芯片制作方法。

17.本发明的半导体测试芯片制作方法,包含以下步骤:

18.提供半导体组件半成品,该半导体组件半成品具有半导体基底及至少一设置于该半导体基底上的芯片,该至少一芯片具有测试电路,及至少一与该测试电路电连接并自该至少一芯片的顶面对外裸露的金属层。

19.利用原子沉积方式于该至少一金属层的至少部分表面沉积形成金属化合物层,而制得该半导体测试芯片。

20.较佳地,本发明所述的半导体测试芯片制作方法,其中,该金属化合物层的材料包括金属氧化物、含卤素金属化合物、含氮金属化合物,及含氧金属化合物的其中至少一者。

21.较佳地,本发明所述的半导体测试芯片制作方法,其中,该金属化合物层厚度介于2nm至50nm。

22.较佳地,本发明所述的半导体测试芯片制作方法,其中,该半导体组件半成品具有多个阵列分布于该半导体基底的芯片,每一芯片具有测试电路,且所述芯片可借由所述测试电路电连接。

23.较佳地,本发明所述的半导体测试芯片制作方法,其中,该每一芯片还具有位于该测试电路上方并与该测试电路电连接的重布线路,及覆盖该重布线路并具有至少一开口的介电层,所述电连接垫与该重布线路电连接并分别自相应的开口对外裸露。

24.本发明的有益的效果在于:利用令半导体测试芯片用于对外电连接的电连接垫的至少部分表面形成一层包括金属氧化物的金属化合物层,而可在利用该半导体测试芯片进行打线的可靠度测试时,通过该金属化合物层的组成、厚度及图样的其中至少一种,仿真半导体组件的电连接垫的表面状态,如粗糙度、氧化状态等,及或于不同环境的氧化及腐蚀破坏状况,而得以加速利用该半导体测试芯片进行可靠度测试时的反应进行,以减少可靠度测试的时间。

附图说明

25.图1是本发明半导体测试芯片的实施例的俯视示意图;

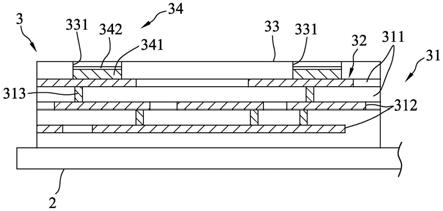

26.图2是说明该实施例的其中一测试芯片的剖视结构示意图;

27.图3是说明该实施例的电连接垫的局部剖视结构示意图;

28.图4是说明于金属层上形成金属化合物层的tem图。

具体实施方式

29.下面结合附图及实施例对本发明进行详细说明。

30.要说明的是,本发明附图仅为表示组件间的结构及/或位置相对关系,与各组件的实际尺寸非直接相关。

31.本发明的半导体测试芯片是供用于打线可靠度测试。

32.参阅图1、2,该半导体测试芯片的一实施例包含一半导体基底2及数个测试芯片3。

33.该半导体基底2可选自硅、化合物半导体如碳化硅(sic),或砷化镓(gaas)、磷化铟(inp)等iii-iv族,或氧化锌(zno)、碲化镉(cdte)等ii-vi族半导体材料。

34.所述测试芯片3以阵列排列方式设置于该半导体基底2上。每一测试芯片3具有一反向该半导体基底2的顶面、一测试电路31、一位于该测试电路31上方并与该测试电路31电连接的重布线路32、一覆盖该重布线路32并具有至少一开口331的介电层33、分别与该重布线路32连接并自该介电层33相应的其中一开口331对外裸露的电连接垫34。

35.详细的说,该测试电路31具有多层交互层迭的设置于该半导体基底2上的介电绝缘层311、金属线路层312,及多数贯穿所述介电绝缘层311以分别将所述金属线路层312做不同电连接的导电贯孔313,通过所述导电贯孔313与不同的金属线路层312电连接,以形成不同的导通回路。其中,为了仿真一般功能芯片的电路,该测试电路31的介电绝缘层311及金属线路层312的层数、厚度、电连接关系等也可完全仿真功能芯片的电路结构,如此,可借由该测试芯片3的电路测试结果反馈至功能完整的芯片,以对应调整功能芯片的电路设计。前述该介电绝缘层311可选自二氧化硅、氮化硅、氮氧化硅、或高分子材料,该金属线路层312及该导电贯孔313则可各别选自钨、铝、铜、铝合金,或铜合金等导电材料。由于该测试电路31的相关制程及使用材料为半导体技术领域者周知,因此不再多加赘述。

36.该重布线路32设于该测试电路31上方并与该测试电路31电连接。该介电层33覆盖该重布线路32并具有多个可令该重布线路32裸露的开口331。其中,该重布线路32选自钨、铝、铜、铝合金或铜合金等导电材料,该介电层33可选自二氧化硅、氮化硅、氮氧化硅或高分子材料。

37.所述电连接垫34与该重布线路32自所述开口331裸露的表面连接并分别自相应的开口331对外裸露,用以供后续打线或形成焊锡或铜凸块,而令所述金属线路层312串接成至少一独立的导电回路。详细的说,每一电连接垫34具有一与该重布线路32自所述开口331裸露的表面连接的金属层341,及一形成于金属层341的至少部分表面的金属化合物层342。该金属层341是由铝、铝合金、铜或铜合金等材料构成,该金属化合物层342的材料包括金属氧化物,以及含卤素金属化合物、含氮金属化合物,及含氧金属化合物的其中至少一者。

38.于一些实施例中,该金属化合物层342的厚度介于2nm至50nm。较佳地,该金属化合物层342的厚度大于5nm。

39.于一些实施例中,该金属化合物层342的厚度介于10nm至50nm。

40.要说明的是,由于该金属化合物层342是由包含金属氧化物,以及含卤素化合物、含氮化合物,及含氧化合物的其中至少一者所构成,因此,会对该电连接垫34的电性造成影响,所以可视该半导体测试芯片的测试要求及目的,通过该金属化合物层342的组成、分布态样(例如可控制该金属化合物层342选择性地全面或部分的覆盖于该金属层341表面,例如,参阅图2、图3,图2是以该金属化合物层342全面覆盖该金属层341的表面且厚度介于2nm

至50nm;图3是以该金属化合物层342以图案化的方式覆盖该金属层341的部分表面且厚度介于2nm至50nm),而令该电连接垫34可被控制成具有不同电性及粗糙度的表面,以更适用模拟不同打线可靠度的测试条件。此外,要再说明的是,于实际实施时该金属化合物层342也可以是以不规则方式覆盖于该金属层341的部分表面,或是可视需求进一步延伸覆盖至该介电层33,并不以图2、3所示结构为限

41.一般而言,形成于该金属层341表面的该金属化合物层342除了会造成电性改变外,还会造成表面粗糙度及表面化学性质的变化,而影响后续打线、焊锡或铜凸块与该电连接垫34的密着性及接合强度。然而,因为一般原生的金属氧化物的厚度极薄(《5nm),因此,当利用将该表面具有极薄的金属氧化物的电连接垫的芯片进行打线,并进行打线的可靠度评估试验时,会需要较长的检测时间才可量测得到金属氧化物对打线的影响。因此,本发明通过该金属化合物层342的组份及该金属化合物层342的分布及厚度,控制该电连接垫34原始的表面性质及粗糙度,而可提供具有不同表面化性/电性及粗糙度条件的电连接垫34的测试芯片3,以供不同条件的打线可靠度测试并得以诱导加速利用该半导体测试芯片于可靠度测试时的反应进行,而可有效减少可靠度试验时间。

42.具体的说,前述该金属化合物层342可利用原子沉积(ald)方式,对设置于该半导体基底上,并具有所述测试电路31、重布线路32、介电层33,及自所述介电层33的开口331裸露的金属层的芯片,沉积形成于该金属层341表面,而可更精确的控制该金属化合物层342的厚度、图案而控制该电连接垫34的表面粗糙度。

43.要再说明的是,因为打线/锡球/铜凸块与该电连接垫34的密着度,除了会受到该电连接垫34的表面粗糙度影响之外,还会受到打线/锡球/铜柱与该电连接垫34的连接界面的化学性质影响,因此,本发明该金属化合物层342除了金属氧化物之外,可再进一步包含群组a的其中一化合物,该群组a的化合物是由该金属层341与非金属元素(如卤素、氮、氧)反应后形成,包括:含卤素化合物、含氮化合物,及含氧化合物。通过该金属化合物层342的组成变化,让该电连接垫34的表面除了粗糙度的变化之外,还可借由表面化学性质的变化先行模拟于不同环境中对该电连接垫34的氧化及腐蚀破坏状况,而得以在对该半导体测试芯片进行可靠度测试时,加速诱导反应进行,以减少可靠度测试的时间。

44.于一些实施例中,当该金属层341是由铝(al)为材料构成,该金属化合物层342的金属氧化物是氧化铝(al2o3),含卤素化合物可以是[alf6]

3-,或alf3,含氮化合物可以是氮化铝(aln)。

[0045]

于另一些实施例中,该金属层341是由铜(cu)为材料构成,该金属化合物层342的金属氧化物是氧化铜(cuo)及/或氧化亚铜(cu2o),该含卤素化合物可以是cucl

x

。

[0046]

又要说明的是,所述测试芯片3后续可通过于其等电连接垫34上形成焊锡凸块,并将其中一电连接垫34的焊锡凸块与其它电连接垫34的焊锡凸块电连接;或是利用打线让不同的电连接垫34彼此电连接,令该测试芯片3的测试电路31的多个独立的电路电导通,或是可据以将不同的测试芯片3串接导通,而为一菊链(daisy chain)。由于所述测试芯片3是以阵列方式分布于半导体基底2,因此,使用时可视所需的测试芯片3数量及电连接态样予以裁切(如图1虚线所示),而可更易于使用。

[0047]

参阅图4,图4是在由al构成的金属层341上形成包含氧化铝的金属化合物层342的tem照片,其中,图4(b)是图4(a)的局部放大图,图4(c)则是包含氧化铝及含氟化合物的金

属化合物层342。由图4可看出,利用该金属化合物层342的厚度可控制该电连接垫34的表面粗糙度,并可配合该金属化合物层342的化学组成变化,而得到具有不同表面粗糙度及化学能态的测试芯片3,进而可供用于评估不同粗糙度及不同表面能态对打线影响的可靠度评估测试。

[0048]

综上所述,本发明利用于该金属层341表面形成包含金属氧化物,或是可进一步再包含由不同的非金属元素与该金属层341的金属反应而得的含卤素化合物、含氮化合物,及含氧化合物的其中至少一者所构成的金属化合物层342,让该电连接垫34的表面性质可借由该金属化合物层342仿真半导体芯片于不同环境中对电连接垫34的表面粗糙度、氧化及腐蚀破坏状况,而得以在可靠度测试中仿真半导体组件制造过程的金属层表面打线可靠度异常可能的态样,加速诱导反应进行,减少可靠度测试的时间,而得以协助研发人员实时掌握问题缩短研发时程,故确实能达成本发明的目的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1