ESD保护电路的制作方法

esd保护电路

技术领域

1.本发明涉及集成电路技术领域,特别是涉及一种esd保护电路。

背景技术:

2.在cmos集成电路中,随着量产工艺的演进,元件的尺寸已经到深亚微米甚至纳米级,在增进集成电路性能、提高运算速度以及缩小芯片面积的同时,引发一些可靠性的问题。cmos元件因为先进的工艺以及缩得更小地元件尺寸,使得cmos集成电路对esd(electro-static discharge,静电释放)的能力下降了很多,并且外界所产生的静电并没有减少,故cmos集成电路因esd而损伤的情形更为严重。esd是造成大多数的电子元件或电子系统受到过度电性应力(eos,electrical overstress)破坏的主要因素。这种破坏给半导体元件以及系统造成永久性破坏,因而影响集成电路的电路功能,使得电子产品失效。

技术实现要素:

3.本发明的主要目的在于提供一种esd保护电路,旨在增强电路的esd能力。

4.为实现上述目的,本发明提供一种esd保护电路,包括模拟电路模块、数字电路模块和隔离单元,所述模拟电路模块与所述数字电路模块通过隔离单元进行隔离;所述模拟电路模块包括多个模拟信号输出单元、多个模拟电源单元和多个模拟地单元,并以n个所述模拟信号输出单元、一个所述模拟电源单元、n个所述模拟信号输出单元、一个所述模拟地单元为一组的形式进行布置;所述数字电路模块包括多个gpio单元、多个数字电源单元和多个数字地单元,并以m个所述gpio单元、一个所述数字电源单元、m个所述gpio单元、一个所述数字地单元为一组的形式进行布置。

5.优选地,各个所述模拟电源单元之间相互连通,各个所述模拟地单元之间相互连通;各个所述数字电源单元之间相互连通,各个所述数字地单元之间相互连通。

6.优选地,所述隔离单元包括并联的第一二极管和第二二极管,所述第一二极管的正极连接于模拟地、负极连接于数字地,所述第二二极管的正极连接于所述数字地、负极连接于所述模拟地。

7.优选地,所述一组n个所述模拟信号输出单元、一个所述模拟电源单元、n个所述模拟信号输出单元、一个所述模拟地单元中的n为2-6。

8.优选地,所述n个模拟信号输出单元为4个模拟信号输出单元。

9.优选地,所述一组m个所述gpio单元、一个所述数字电源单元、m个所述gpio单元、一个所述数字地单元中的m为2-6。

10.优选地,m个gpio单元为4个gpio单元。

11.优选地,所述数字电源单元、所述模拟电源单元、所述数字地单元和所述模拟地单元均为rc clamp结构。

12.优选地,所述模拟信号输出单元和所述gpio单元包括ggpmos和/或ggnmos结构的

驱动管。

13.本发明技术方案将模拟电路模块和数字电路模块通过隔离单元进行隔离的同时,并将模拟电路模块和数字电路模块分别以n个模拟信号输出单元、模拟电源单元、n个模拟信号输出单元、模拟地单元和m个gpio单元、数字电源单元、m个gpio单元、数字地单元的形式结构进行布置,为电路提供了极强的esd能力。

附图说明

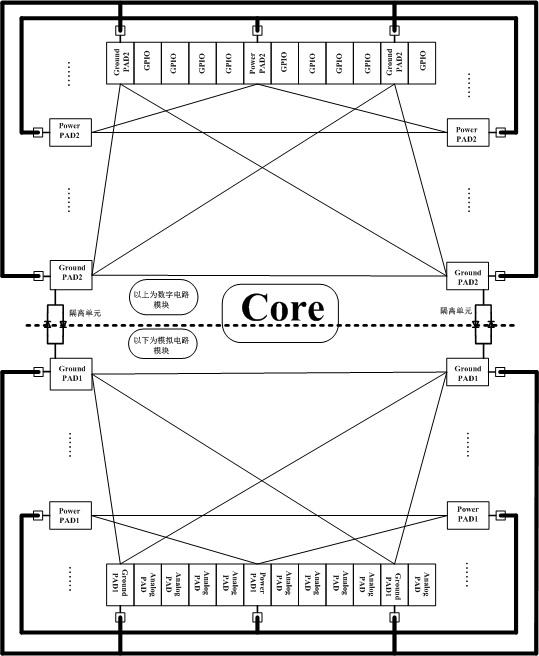

14.图1为本发明esd保护电路的原理示意图;图2为本发明实施例中隔离单元的电路原理示意图;图3为本发明实施例中数字电源单元的电路原理示意图;图4为本发明实施例中模拟信号输出单元的电路原理示意图;图5为本发明实施例中gpio单元的电路原理示意图。

15.本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

16.具体实施方式

17.应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

18.下面结合附图对本发明进一步说明。

19.本发明实施例提供一种esd保护电路,如图1所示,用于增强芯片core的esd能力。该esd保护电路包括模拟电路模块、数字电路模块和隔离单元,所述模拟电路模块与所述数字电路模块通过隔离单元进行隔离;所述模拟电路模块包括多个模拟信号输出单元analog pad、多个模拟电源单元power pad1和多个模拟地单元ground pad1,并以n个所述模拟信号输出单元analog pad、一个所述模拟电源单元power pad1、n个所述模拟信号输出单元analog pad、一个所述模拟地单元ground pad1为一组的形式进行布置;所述数字电路模块包括多个gpio单元gpio、多个数字电源单元power pad2和多个数字地单元ground pad2,并以m个所述gpio单元gpio、一个所述数字电源单元power pad2、m个所述gpio单元gpio、一个所述数字地单元ground pad2为一组的形式进行布置。

20.在一些实施例中,一组n个所述模拟信号输出单元analog pad、一个所述模拟电源单元power pad1、n个所述模拟信号输出单元analog pad、一个所述模拟地单元ground pad1中的n为2-6。一组m个所述gpio单元gpio、一个所述数字电源单元power pad2、m个所述gpio单元gpio、一个所述数字地单元ground pad2中的m为2-6。

21.在优选实施例中,n个模拟信号输出单元analog pad为4个模拟信号输出单元analog pad。具体地,每4个模拟信号输出单元analog pad放置一个模拟电源单元power pad1或模拟地单元ground pad1,可以保证两个临近的模拟电源单元power pad1和模拟地单元ground pad1之间的阻抗不超过1欧姆,以保证电路的阻抗不会过大。

22.在优选实施例中,m个gpio单元gpio为4个gpio单元gpio。具体地,每4个gpio单元gpio放置一个数字电源单元power pad2或数字地单元ground pad2,可以保证两个临近的数字电源单元power pad2和数字地单元ground pad2之间的阻抗不超过1欧姆,以保证电路的阻抗不会过大。

23.在一些实施例中,各个所述模拟电源单元power pad1之间相互连通,各个所述模拟地单元ground pad1之间相互连通;各个所述数字电源单元power pad2之间相互连通,各个所述数字地单元ground pad2之间相互连通。具体地,将各个电源、地分别连接起来,合理规划电源地网络,以保证任意两个电源pad、地pad之间的阻抗不超过1.5欧姆,以保证电路的阻抗不会过大。

24.优选地,如图2所示,所述隔离单元包括并联的第一二极管d1和第二二极管d2,所述第一二极管d1的正极连接于模拟地vssa、负极连接于数字地vssd,所述第二二极管d2的正极连接于所述数字地vssd、负极连接于所述模拟地vssa。隔离单元采用二极管结构,可以隔离模拟地vssa和数字地vssd,以避免数字地vssd的干扰影响到模拟信号输出单元analog pad输出的模拟信号。具体的,模拟地vssa为模拟电路模块的地,数字地vssd为数字电路模块的地。

25.优选地,所述数字电源单元power pad2、所述模拟电源单元power pad1、所述数字地单元ground pad2和所述模拟地单元ground pad1均为rc clamp结构。

26.具体地,如图3所示,以数字电源单元power pad2为例:所述数字电源单元power pad2包括连接于io电源的第一电阻r1、第二电阻r2和第一nmos管mn1,连接于io地的第一电容c1和第三电阻r3;所述第一电阻r1还连接有第一电容c1的一端和反相器p的输入端,所述第一电容c1的另一端连接io地;所述反相器p的电源端通过所述第二电阻r2连接于所述io电源,其地端通过第三电阻r3连接于io地;所述反相器p的输出端连接于所述第一nmos管mn1的栅极,所述第一nmos管mn1的漏极连接于io电源、源极连接于io地。具体地,第一电阻r1和第一电容c1构成rc充放电电路,其充电时间要保证第一nmos管mn1的导通,以便io电源上的esd电流全部泄放到数字地上。反相器p通过第二电阻r2和第三电阻r3连接到io电源和io地上,当io电源和io地上有esd电流来的时候,可以保护反相器p的管子不会损坏,第二电阻r2和第三电阻r3的取值在50~100ω左右。第一nmos管mn1作为主要的esd泄放路径,其通过rc充放电电路控制开启/关闭,为了保证esd电流完全泄放,同时其不能长时间在高压下开启,因此开启时间在200~400ns之间。

27.在具体实施例中,数字电源单元power pad2、模拟电源单元power pad1、数字地单元ground pad2和模拟地单元ground pad1的结构相同,可以减少设计难度、减少后续工作。在另一些实施例中,数字电源单元power pad2、模拟电源单元power pad1、数字地单元ground pad2和模拟地单元ground pad1的结构也可以不同,可根据具体电路设计进行相应修改,以适应不同的电路设计要求。

28.优选地,所述模拟信号输出单元analog pad和所述gpio单元gpio包括ggpmos和/或ggnmos结构的驱动管,其通过ggpmos和/或ggnmos结构进行esd。

29.具体地,如图4所示,模拟信号输出单元analog pad包括连接于io电源的第一pmos管mp1和连接于所述第一pmos管mp1的第二nmos管mn2。第一pmos管mp1的源极和栅极连接于io电源,漏极连接于第二nmos管mn2的漏极以及模拟电源;第二nmos管mn2的栅极和源极连接于io地。

30.具体地,如图5所示,gpio单元gpio包括连接于输入端和输出端的第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第三nmos管mn3、第四nmos管mn4和第五nmos管mn5,以及连接于内部电路的pad端。第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第三nmos管mn3、

第四nmos管mn4和第五nmos管mn5的漏极相互连接并连接于输入端、输出端和pad端;第二pmos管mp2、第三pmos管mp3和第四pmos管mp4的栅极相互连接并连接于输出端,第三nmos管mn3、第四nmos管mn4和第五nmos管mn5的栅极相互连接并连接于输出端。第二pmos管mp2、第三pmos管mp3和第四pmos管mp4的源极连接于数字电源,第三nmos管mn3、第四nmos管mn4和第五nmos管mn5的源极连接于数字地。当需要进行esd的时候, pmos 驱动管为ggpmos结构,可将pad端上的esd大电流泄放到数字电源单元power pad2上;同理,nmos驱动管也为ggnmos结构,可将pad端上的esd大电流泄放到数字地单元ground pad2上。

31.具体地,本发明esd保护电路的实施例中,保护电路使用的器件类型需与被保护器件类型保持一致。

32.在一些实施例中,可在版图设计环节根据工艺的规则加入esd implant,以进一步增强电路的esd能力。

33.应当理解的是,以上仅为本发明的优选实施例,不能因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1