开关电源用平面变压器最优绕法的制作方法

1.本发明涉及开关电源用平面变压器最优绕法。

背景技术:

2.变压器是开关电源中的关键器件,起着隔离和提供变比或充当耦合电感进行电与磁的能连转换和充放功能。平面变压器采用pcb铜箔走线代替传统漆包线作为绕组,这大大减小了变压器的体积和重量。即使如此,传统变压器所存在的问题,即漏感和铜损,在平面变压器中将显得尤其重要值得优化。这是因为,漏感和铜损直接与变压器的损耗相关,由于平面变压器散热面积也相应地小,热累计的问题将显得比较严重。

技术实现要素:

3.本发明目的是解决现有技术中的问题,而提供一种新型的开关电源用平面变压器最优绕法。

4.为了实现这一目的,本发明的技术方案如下:开关电源用平面变压器最优绕法,包含有,获得原副边的电流值;根据pcb层数确定原副边分别做几层并联绕组,并由此确定每层流过的电流值;反复迭代匝数选择,使相邻普遍层与原边层的电流乘以该层匝数之和尽量接近0;经过以上迭代计算便可由此可以获得绕组结构。

5.与现有技术相比,本发明的有益效果至少在于:1.减小变压器体积;2.保证最优漏感或铜损。

附图说明

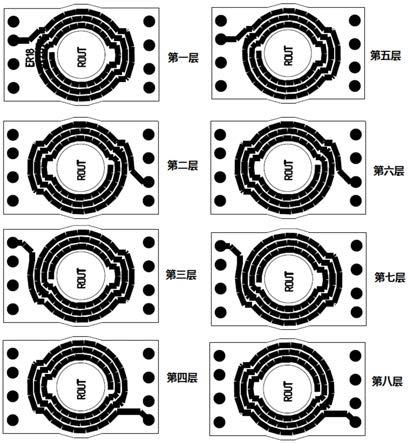

6.图1为本发明中6:8层pcb板原边6匝副边3匝的设计的结构示意图。

具体实施方式

7.下面通过具体的实施方式连接附图对本发明作进一步详细说明。在此需要说明的是,对于这些实施方式的说明用于帮助理解本发明,但不构成对本发明的限定。此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以相互组合。

8.请参见图1,图中示出的是开关电源用平面变压器最优绕法。

9.分别从漏感和铜损角度列举常用匝数设计分别适用于6层pcb板与8层pcb板的最优绕组排布。本专利设计的匝数设计有:原边2匝副边1匝,原边4匝副边2匝,原边6匝副边3匝,原边3匝副边2匝,原边6匝副边4匝,原边3匝副边1匝,原边6匝副边2匝。此专利只涉及绕组的排布顺序和方式,其他参数例如层间距匝间距等应由实际应用而定。

10.漏感是由变压器两边绕组不完全耦合造成的能量累积而在电路中等效表现出的

电路参数,假设原副边流过的电流会产生相反方向的磁场。由于磁芯中磁路完全耦合,方向相反的磁场会互相抵消几乎为0,因此只需要考察磁芯窗口中所累积的磁场能量以等效考察漏感。因此,将漏感降低的原则就是采用所谓的三明治绕组,使原副边相互交错,同时使得相邻绕组间的磁势(可以用安匝乘积表示)尽量相近已达到减小绕组间所储存的磁能。通过简单的计算公式便可以获得绕组设计:步骤1:获得原副边的电流值步骤2:根据pcb层数确定原副边分别做几层并联绕组,并由此确定每层流过的电流值步骤3:反复迭代匝数选择,使相邻普遍层与原边层的电流乘以该层匝数之和尽量接近0经过以上迭代计算便可由此可以获得如下绕组结构。

11.注:2p1s意为原边(用p表示)2匝副边(用s表示)1匝,以此类推。

12.1:6层pcb板原边2匝副边1匝的设计:2p1s2p1s2p1s(其中第1、3、5层并联,第2、4、6层并联)2:8层pcb板原边2匝副边1匝的设计:2p1s2p1s2p1s2p1s(其中第1、3、5、7层并联,第2、4、6、8层并联)3:6层pcb板原边4匝副边2匝的设计:4p2s4p2s4p2s(其中第1、3、5层并联,第2、4、6层并联)4:8层pcb板原边4匝副边2匝的设计:4p2s4p2s4p2s4p2s(其中第1、3、5、7层并联,第2、4、6、8层并联)5:6层pcb板原边6匝副边3匝的设计:2p1s2p1s2p1s(其中第1、3、5层串联,第2、4、6层串联)6:8层pcb板原边6匝副边3匝的设计:3p3s3p3s3p3s3p3s(其中第1与3层串联,第5与7层串联,再相互并联)7:6层pcb板原边3匝副边2匝的设计:3p2s3p2s3p2s(其中第1、3、5层并联,第2、4、6层并联)8:8层pcb板原边3匝副边2匝的设计:3p2s3p2s3p2s3p2s(其中第1、3、5、7层并联,第2、4、6、8层并联)9:6层pcb板原边6匝副边4匝的设计:2p4s2p4s2p4s(其中第1、3、5层串联,第2、4、6层并联)10:8层pcb板原边6匝副边4匝的设计:3p4s3p4s3p4s3p4s(其中第1、3层串联,第5、7层串联,串联绕组再互相并联,第2、4、6、8层并联)11:6层原边3匝副边1匝的设计:3p1s3p1s3p1s(其中第1、3、5层并联,第2、4、6层并联)12:8层原边3匝副边1匝的设计:3p1s3p1s3p1s3p1s(其中第1、3、5、7层并联,第2、4、6、8层并联)13:6层原边6匝副边2匝的设计:2p1s2p1s2p2s(其中第1、3、5层串联,第2、4层串联再与第6层并联)14:8层原边6匝副边2匝的设计:3p2s3p2s3p2s3p2s(其中第1、3、5、7层并联,第2、4、6、8层并联)铜损是电流流过导体时不可避免的造成的损耗,最直观的降低铜损的方式是多层并联

以减小等效电阻,但是在高频应用下,临近效应会使得绕组等效交流电阻不一致而导致分流不均,反而加重了损耗。为了优化损耗,绕组设计同样要采用交错设计,同时要保证绕组排布较为对称。

13.由此可以获得如下绕组结构。

14.注:2p1s意为原边(用p表示)2匝副边(用s表示)1匝,以此类推1:6层pcb板原边2匝副边1匝的设计:2p1s2p1s1s2p(其中第1、3、6层并联,第2、4、5层并联)2:8层pcb板原边2匝副边1匝的设计:2p1s1s2p2p1s1s2p(其中第1、3、5、7层并联,第2、4、6、8层并联)3:6层pcb板原边4匝副边2匝的设计:4p2s4p2s2s4p(其中第1、3、6层并联,第2、4、5层并联)4:8层pcb板原边4匝副边2匝的设计:4p2s2s4p4p2s2s4p(其中第1、4、5、8层并联,第2、3、6、7层并联)5:6层pcb板原边6匝副边3匝的设计:2p1s2p1s1s2p(其中第1、3、6层串联,第2、4、5层串联)6:8层pcb板原边6匝副边3匝的设计:3p3s3s3p3p3s3s3p(其中第1与4层串联,第5与8层串联,再相互并联)7:6层pcb板原边3匝副边2匝的设计:3p2s3p2s2s3p(其中第1、3、6层并联,第2、4、5层并联)8:8层pcb板原边3匝副边2匝的设计:3p2s2s3p3p2s2s3p(其中第1、4、5、8层并联,第2、3、6、7层并联)9:6层pcb板原边6匝副边4匝的设计:2p4s2p4s4s2p(其中第1、3、6层串联,第2、4、5层并联)10:8层pcb板原边6匝副边4匝的设计:3p4s4s3p3p4s4s3p(其中第1、4层串联,第5、8层串联,串联绕组再互相并联,第2、3、6、7层并联)11:6层原边3匝副边1匝的设计:3p1s3p1s1s3p(其中第1、3、6层并联,第2、4、5层并联)12:8层原边3匝副边1匝的设计:3p1s1s3p3p1s1s3p(其中第1、4、5、8层并联,第2、3、6、7层并联)13:6层原边6匝副边2匝的设计:2p1s2p1s2s2p(其中第1、3、6层串联,第2、4层串联再与第5层并联)14:8层原边6匝副边2匝的设计:3p2s2s3p3p2s2s3p(其中第1、4、5、8层并联,第2、3、6、7层并联)而以上仅表达了本发明的实施方式,其描述较为具体和详细,但且不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1