减小芯片电磁噪声的散热组件、芯片封装组件及电子设备的制作方法

1.本技术涉及芯片的技术领域,特别涉及一种减小芯片电磁噪声的散热组件、芯片封装组件及电子设备。

背景技术:

2.随着芯片功耗的激增,裸片封装逐渐成为大功耗芯片封装的主流工艺,以提高芯片的散热收益。但是,经过仿真发现,基于裸片封装工艺的芯片封装组件,其芯片对外的辐射功率也较强,导致芯片封装组件的电磁噪声较大。

技术实现要素:

3.本技术的目的在于提供一种减小芯片电磁噪声的散热组件、芯片封装组件及电子设备,以解决现有芯片封装组件的电磁噪声较大的问题。

4.为了解决上述技术问题,本技术提供了一种减小芯片电磁噪声的散热组件,所述散热组件包括:散热器、封环和抑制环;所述抑制环连接在所述封环、所述散热器之间,并且用于环绕芯片;所述散热组件用于与载有所述芯片的基板共同包围形成封闭空间,并使所述芯片位于所述封闭空间内;所述抑制环用于屏蔽所述芯片辐射的电磁波。应当理解,基于抑制环对电磁波的屏蔽作用,相对现有裸片封装的芯片封装组件,所述散热组件在确保散热收益的同时,可以确保使用所述散热组件的芯片封装组件具有较小的电磁噪声。在20ghz以上的高频范围,对应的芯片封装组件仍保持较好的电磁噪声抑制效果,以使在该高频范围内的电磁波的辐射功率仍然保持在较低的水平,以减少电磁污染,并降低其与射频电路之间串扰的可能。

5.一些实施例中,所述抑制环位于所述封环之朝向所述散热器的一侧。当在芯片封装组件中使用该散热组件时,通过抑制环、散热器和封环的配合,散热组件在满足芯片封装组件的散热需求的同时,还可以抑制芯片向相对芯片封装组件的外部辐射电磁波,以减小芯片封装组件的电磁噪声。

6.一些实施例中,所述散热器包括散热器主体和环形支架,所述环形支架位于散热器主体的一侧并且与所述封环间隔设置;所述抑制环部分或者全部夹设在所述环形支架和所述封环之间。当在芯片封装组件中使用该散热组件时,通过抑制环、散热器和封环的配合,散热组件在满足芯片封装组件的散热需求的同时,还可以抑制芯片向相对芯片封装组件的外部辐射电磁波,以减小芯片封装组件的电磁噪声。

7.一些实施例中,所述抑制环包括第一环形部和第二环形部,所述第一环形部夹设在所述环形支架和所述封环之间,所述第二环形部夹设在所述散热器主体和所述封环之间。

8.一些实施例中,所述抑制环与所述封环、所述散热器无缝连接。基于此,封环、抑制环和散热器之间没有缝隙,以提高散热组件对芯片辐射的电磁波的屏蔽效果。

9.一些实施例中,所述抑制环为柔性的导电衬垫,所述导电衬垫通过弹性形变夹设

在所述封环和所述散热器之间。该抑制环具有一定的弹性,基于此,在屏蔽电磁波的同时,抑制环还可以起到缓冲保护芯片的作用,以减小芯片所承受的压强。

10.一些实施例中,所述导电衬垫包括弹性内芯和导电外层,所述导电外层包裹所述弹性内芯。通过弹性内芯,导电衬垫可以具有一定的弹性,以实现良好搭接。通过导电外层,导电衬垫可以实现与散热器、封环之间的电连接,以确保对芯片辐射的电磁波的屏蔽效果。

11.一些实施例中,所述弹性内芯为发泡材料,所述导电外层为导电纤维布。其中,发泡材料可例如为聚氨酯类等具有一定弹性的材料;导电纤维布可例如为镍/铜类(ni/cu)等具有高导电率的材料。

12.一些实施例中,所述导电衬垫为导电泡棉。应当理解,导电海绵同样具有导电和可压缩的特性,可以实现与封环和散热器的良好搭接、以及实现对电磁波的屏蔽功能。

13.本技术还提供了另一种减小芯片电磁噪声的散热组件,所述散热组件包括:散热器、封环和抑制环;所述抑制环位于所述封环和所述散热器之间,并且用于环绕芯片;所述散热组件用于与载有芯片的基板共同包围形成封闭空间,并使所述芯片位于所述封闭空间内;所述抑制环用于吸收所述芯片辐射的电磁波。应当理解,本实施例的抑制环可以与封环、散热器中至少之一连接,即,在封环、抑制环和散热器之间可以保留一定的缝隙。基于抑制环对电磁波的吸收、衰减作用,相对现有裸片封装的芯片封装组件,芯片辐射的电磁波也难以从缝隙穿透到外部,由此,使用所述散热组件的芯片封装组件可以具有较小的电磁噪声。在20ghz以上的高频范围,所述芯片封装组件仍保持较好的电磁噪声抑制效果,以使在该高频范围内的电磁波的辐射功率仍然保持在较低的水平,以减少电磁污染,并降低其与射频电路之间串扰的可能。

14.一些实施例中,所述抑制环位于所述封环之朝向所述散热器的一侧。当在芯片封装组件中使用该散热组件时,通过抑制环、散热器和封环的配合,散热组件在满足芯片封装组件的散热需求的同时,还可以抑制芯片向相对芯片封装组件的外部辐射电磁波,以减小芯片封装组件的电磁噪声。

15.一些实施例中,所述散热器包括散热器主体和环形支架,所述环形支架位于散热器主体的一侧并且与所述封环间隔设置;所述抑制环部分或者全部位于所述环形支架和所述封环之间。当在芯片封装组件中使用该散热组件时,通过抑制环、散热器和封环的配合,散热组件在满足芯片封装组件的散热需求的同时,还可以抑制芯片向相对芯片封装组件的外部辐射电磁波,以减小芯片封装组件的电磁噪声。

16.一些实施例中,所述抑制环包括第一环形部和第二环形部,所述第一环形部位于所述环形支架和所述封环之间,所述第二环形部位于所述散热器主体和所述封环之间。

17.一些实施例中,所述抑制环为由吸波材料制成的环形结构件。其中,吸波材料可例如为石墨、石墨烯、碳纤维、磁性陶瓷、导电聚合物等。

18.一些实施例中,所述第一环形部为导电衬垫;或者,所述第一环形部为由吸波材料制成的环形结构件。

19.一些实施例中,所述第二环形部为导电衬垫;或者,所述第一环形部为由吸波材料制成的环形结构件。其中,当所述第二环形部为导电衬垫时,该第二环形部还可以降低芯片所承受的压强。

20.本技术还提供了又一种减小芯片电磁噪声的散热组件,所述散热组件包括:散热

器和抑制环;所述抑制环位于所述散热器的一侧,并且用于环绕芯片;所述散热组件用于与载有芯片的基板共同包围形成封闭空间,并使所述芯片位于所述封闭空间内;其中,所述抑制环为导电衬垫,或者,所述抑制环为由吸波材料制成的环形结构件。

21.本技术还提供了一种芯片封装组件,所述芯片封装组件包括:芯片、基板、以及上述各实施例中的减小芯片电磁噪声的散热组件。所述芯片设于所述基板上,所述基板和所述散热组件共同包围形成封闭空间,所述芯片位于所述封闭空间内。

22.本技术还提供了一种电子设备,所述电子设备包括上述各实施例中的减小电磁噪声的芯片封装组件。其中,所述电子设备可以为路由器或者交换机。

23.本技术通过抑制环与相关结构的配合,当散热组件应用到芯片封装组件中时,散热组件在满足散热需求的同时,还可以抑制芯片向相对芯片封装组件的外部辐射电磁波,以减小芯片封装组件的电磁噪声,并且降低其与射频电路之间互相串扰的可能。

附图说明

24.图1是现有的芯片封装组件的示意图。

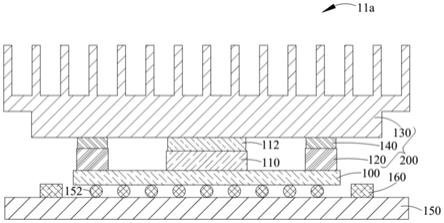

25.图2和图3是本技术一实施例的芯片封装组件的示意图。

26.图4是本技术一实施例的基板、封环和芯片的俯视图。

27.图5是本技术一实施例的芯片封装组件的电磁噪声屏蔽效果仿真测试数据图。

28.图6是现有芯片封装组件中芯片的压强测试数据图。

29.图7为本技术一实施例的芯片封装组件中芯片的压强测试数据图。

30.图8至图10是本技术另一实施例的芯片封装组件的示意图。

31.图11是本技术又一实施例的芯片封装组件的示意图。

32.图12是本技术再一实施例的芯片封装组件的示意图。

33.图13是本技术再一实施例的芯片封装组件的示意图。

具体实施方式

34.下面将结合本技术实施方式中的附图,对本技术实施方式中的技术方案进行清楚、完整地描述。

35.请参考图1,随着芯片的集成度的提高,芯片也具有了更强的处理能力。但相应的,芯片的功耗也会激增。应当理解,功耗越大的芯片在工作时也会产生更多的热量,该些热量需要被及时散出。对此,为了提高芯片的散热收益,近年来业内逐渐采用裸片(die)封装的工艺取代金属盖(lid)封装的工艺,以对芯片进行封装而形成裸片封装的芯片封装组件。

36.应当理解,在裸片封装的芯片封装组件中,芯片110设置在基板100上,在芯片110的周围设置有封环(seal ring)120,并且取消了原先罩在芯片110上的金属盖122。而由于拿掉了位于芯片110上的金属盖122,该芯片110可以通过热界面材料(tim,thermal interface material)112与散热器130连接,并直接将热量传导至散热器130,以实现散热。基于此,裸片封装的芯片封装组件的散热收益提高,可以满足芯片的散热需求。

37.但在拿掉金属盖122后,芯片封装组件中的基板100与散热器130之间也会存在较大的高度差。封环120虽然环绕在芯片110周围,但是由于元件制程公差、封装需求以及后续测试等因素,该封环120并不能良好地遮挡在基板100和散热器130之间。此就导致了在封环

120与散热器130之间形成缝隙;和/或,在基板100与封环120之间也容易形成缝隙。

38.基于该些缝隙,裸片封装的芯片110也更容易向相对芯片封装组件的外部辐射电磁波,该些辐射出的电磁波即为电磁噪声。在通过对裸片封装的芯片封装组件进行仿真后发现,相对金属盖封装的芯片封装组件,裸片封装的芯片封装组件向外辐射的电磁波具有更强的辐射功率;即,裸片封装的芯片封装组件具有较强的电磁噪声。

39.由于电磁波的频率越高,其对应的波长也就越小。相对低频范围的电磁波,高频范围的电磁波更容易通过狭小的缝隙辐射到外部。例如:经过仿真后发现,在20~35ghz的高频范围内,相对金属盖封装的芯片封装组件,裸片封装的芯片封装组件向外辐射的电磁噪声的辐射功率增强了5~10db。基于此,在裸片封装的芯片封装组件中,高频范围内的电磁波更难被抑制,该些辐射出的电磁波在形成电磁噪声的同时,也容易造成电磁污染,并且对外部的电路或者信号造成干扰。

40.应当理解,当裸片封装的芯片封装组件应用到电子设备中时,该芯片封装组件向外辐射的电磁噪声存在干扰射频电路的风险;或者,通过射频电路而向外辐射的电磁波也存在干扰芯片封装组件的风险,此串扰的现象会对电子设备的性能造成一定的不良影响。例如:在5~6ghz的频段范围内,芯片封装组件向外辐射的电磁噪声容易对射频电路造成串扰,影响射频电路的正常工作;或者,经射频电路和对应的天线向外辐射的电磁波也容易对芯片封装组件造成串扰,影响芯片封装组件的正常工作。

41.基于裸片封装的芯片封装组件存在较强电磁噪声以及射频干扰等方面的问题,本技术实施例提供了散热组件、芯片封装组件、以及应用芯片封装组件的电子设备。其中,各实施例的散热组件是整合到芯片封装组件内,以作为芯片封装组件一部分,但不以此作为限制。在其他的一些实施中,散热组件也可以作为相对独立的组件;在组装时,该散热组件配合基板、芯片等结构而组装形成芯片封装组件。

42.一些实施例中,该电子设备可例如为路由器、交换机等。应当理解,电子设备还可以包括射频电路、滤波器等结构,对此不加限制。

43.请参考图2,本技术实施例提供的芯片封装组件11a,该芯片封装组件11a包括基板100、芯片110和散热组件200;其中,该散热组件200又包括封环120、抑制环140和散热器130。一些实施例中,该抑制环140环绕在芯片110周围,其可以屏蔽芯片110辐射的电磁波,由此来减小芯片封装组件11a的电磁噪声,以减少电磁污染。在其他的一些实施例中,抑制环140可以吸收芯片110辐射的电磁波,此同样可以减小电磁噪声,以减少电磁污染。应当理解,本技术各实施例提供的抑制环140可以是柔性的(例如下文将提及的导电衬垫),或者可以是刚性的(例如下文将提及的由吸波材料制成的环形结构件)。该抑制环140具有抑制电磁波辐射的特性;其中,该抑制电磁波辐射的特性可例如屏蔽电磁波或者吸收电磁波。一些实施例中,该抑制环的材料可例如为

44.一些实施例中,抑制环140位于封环120的一侧并且远离基板100;即,该抑制环140连接在封环120和散热器130之间,以减小甚至消除原先封环120和散热器130之间的缝隙。应当理解,基板100和散热组件200共同包围形成一个封闭空间,芯片110则是设置在该封闭空间内。散热器130的材料可例如为金属或者非金属的导热材料。通过抑制环140、散热器130和封环120的配合,可以抑制位于封闭空间内的芯片110向相对芯片封装组件11a的外部辐射电磁波,以减小芯片封装组件11a的电磁噪声并降低其与射频电路之间串扰的可能。

45.应当理解,各实施例的芯片封装组件仅是将射频电路作为例子来进行说明,但是并不限定芯片封装组件仅是针对射频电路。各实施例的芯片封装组件也可以降低与其他芯片封装组件之间串扰的可能,对此不加限制。

46.一些实施例中,抑制环140可以通过背胶来实现固定;或者,抑制环140可以通过点胶来实现固定,对此不加限定。例如:抑制环140通过背胶固定在封环120上,后续散热器130通过螺钉等方式实现锁固,抑制环140则位于封环120和散热器130之间。

47.当抑制环为柔性时,该抑制环可以通过弹性形变而夹持在封环和散热器之间,以遮挡封环和散热器之间的缝隙;当抑制环为刚性时,可以通过控制散热器的安装高度,以使封环、抑制环和散热器三者之间具有较小的缝隙或者没有缝隙,确保对电磁波的抑制效果。

48.应当理解,在本技术各实施例提供的芯片封装组件11a中,通过将抑制环140设置在封环120和散热器130之间,在芯片110辐射的电磁波中,其高频范围内(例如20~35ghz)的部分也难以辐射到外部。因此,各实施例的芯片封装组件11a可以具有更强的电磁噪声抑制效果,在保证芯片110的散热收益的同时,可以减小芯片封装组件11a的电磁噪声,以确保芯片封装组件11a的正常工作。

49.一些实施例中,散热器还可以具有凸台(图未示),该凸台朝向芯片、基板的方向凸起。基于此,具有凸台的散热器可以更容易与芯片接触,以传导芯片散发的热量。

50.应当理解,通过抑制环140、散热器130和封环120的配合,芯片110辐射的电磁波难以穿透到外部,外部的电磁波也难以穿透到该封闭空间内。基于此,可以降低芯片封装组件11a向外辐射的电磁波的辐射功率,以降低芯片110影响射频电路的可能;另外,还可以降低射频电路辐射的电磁波影响芯片110的可能。

51.一些实施例中,该抑制环140为导电衬垫。该导电衬垫具有一定的弹性,可以被一定程度压缩。基于此,通过控制导电衬垫的压缩量,该导电衬垫可以通过弹性形变的方式而保持与封环120和散热器130之间的良好搭接,尽可能消除散热器130和封环120之间的缝隙,以降低芯片110辐射的电磁波穿透至外部的可能。

52.一些实施例中,导电衬垫可以无缝隙地连接在封环120和散热器130之间,以消除原先封环120和散热器130之间的缝隙;并且在基板100、封环120、导电衬垫和散热器130之间形成封闭空间。基于此,芯片110辐射的电磁波更难穿透到外部,以使芯片封装组件11a具有更好的电磁噪声抑制效果。

53.例如:导电衬垫夹设在封环120和散热器130之间并且远离基板100,通过控制散热器130相对基板100的安装距离等方式,将该导电衬垫的压缩量控制在40%,导电衬垫通过弹性形变的方式而稳定地固定在封环120和散热器130之间,由此可以使导电衬垫具有一定回弹力并尽可能地消除封环120和散热器130之间的缝隙。

54.一些实施例中,基于导电衬垫具有一定弹性的特性,在安装散热器130的过程中,该导电衬垫还可以起到缓冲保护芯片110的作用,以减小芯片110所承受的压强。应当理解,当散热器130通过螺钉锁固等方式实现固定时,随着散热器130相对基板100的距离的减小,散热器130会逐渐挤压导电衬垫并使导电衬垫压缩,而由于导电衬垫存在回复初始状态的回弹力,该回弹力可以减小散热器130施加在芯片110上的作用力,由此可以减小芯片受到的压强。

55.一些实施例中,导电衬垫包括弹性内芯和导电外层,导电外层包裹着弹性内芯。通

过弹性内芯,该导电衬垫具有一定的弹性,以实现良好搭接。通过导电外层,该导电衬垫可以实现与散热器130、封环120等结构之间的电连接,以确保对芯片110辐射的电磁波的屏蔽效果。

56.一些实施例中,弹性内芯为发泡材料。该发泡材料可例如为聚氨酯类等具有一定弹性的材料。

57.一些实施例中,导电外层为导电纤维布。该导电纤维布可例如为镍/铜类(ni/cu)等具有高导电率的材料。

58.一些实施例中,该导电衬垫还可以为导电海绵。该导电海绵同样具有导电和可压缩的特性,可以实现与封环120和散热器130的良好搭接、以及实现对电磁波的屏蔽功能。应当理解,相对包括弹性内芯和导电外层的导电衬垫,该导电海绵的压缩范围更大,例如:导电衬垫的压缩范围为30%~50%,导电海绵的压缩范围为40%~60%。在使用导电海绵作为抑制环140时,可以使用更大尺寸的导电海绵,以保证其与封环120、导电海绵和散热器130之间的良好搭接。

59.在其他的一些实施例中,该抑制环140为由吸波材料制成的环形结构件,并且位于封环120和散热器130之间,以吸收、衰减芯片110辐射的电磁波。应当理解,不同于导电衬垫,该环形结构件可以设于封环120的一侧,并且朝向散热器130;或者,该环形结构件也可以设于散热器130的一侧,并且朝向封环120。

60.以该环形结构件位于封环120的一侧,并且朝向散热器130为例来进行说明。请参考图3,本技术实施例提供的一种芯片封装组件11b,与芯片封装组件11a相比,该芯片封装组件11b中,散热组件200的抑制环140为由吸波材料制成的环形结构件。其中,该环形结构件与散热器130之间可以没有接触;即,该环形结构件和散热器130之间可以存在一定的缝隙,并不需要像导电衬垫一样保持与封环120、散热器130之间的连接关系。对应环形结构件与封环120、散热器130之间的位置关系,形成的封闭空间可以保留有一定的缝隙,而不需要完全封闭。

61.应当理解,当环形结构件应用到各实施例的芯片封装组件(11a,11b)中,基于环形结构件对电磁波的吸收、衰减的作用,芯片110辐射的电磁波在穿过该缝隙过程中,会被环形结构件吸收和衰减。而通过吸收、衰减芯片110辐射的电磁波,环形结构件可以将电磁能转换成热能或其他形式的能量而被消耗掉,以减小芯片110向外辐射的电磁波的辐射功率,以减小电磁噪声。

62.在其他的一些实施例中,当环形结构件位于散热器130的一侧,并且朝向封环120时,该环形结构件与封环120之间也可以存在一定的缝隙,对此不加限制。

63.一些实施例中,吸波材料可例如为石墨、石墨烯、碳纤维、磁性陶瓷、导电聚合物等。

64.应当理解,各实施例的芯片封装组件主要是以导电衬垫作为抑制环来举例说明,但是各实施例的抑制环同样也可以是环形结构件,以达到类似的减小电磁噪声的效果。此外,当抑制环为环形结构件时,该环形结构件并不需要完全遮挡封环和散热器之间的缝隙;即,在安装散热器后,散热器、环形结构件和封环之间仍可以存在一定的缝隙;而通过环形结构件对电磁波的吸收和衰减,芯片辐射的电磁波也难以从缝隙穿透到外部,此同样可以减小芯片封装组件的电磁噪声,以确保芯片封装组件的正常工作。

65.一些实施中,抑制环140的形状可例如圆环、六角回字形或者方形回字形等。应当理解,本技术并不限制抑制环140的宽度、厚度等尺寸,抑制环140的形状可以根据芯片封装组件(11a,11b)的实际结构需求而适应性设计,对此不加限制。在其他的一些实施例中,该抑制环140的形状也可以是椭圆环等。

66.一些实施中,沿着抑制环140的径向,该抑制环140的横截面的形状可例如为矩形、半圆形或者圆形等;应当理解,本技术并不限制抑制环140的横截面形状,抑制环140的横截面形状可以根据芯片封装组件(11a,11b)的实际结构需求而适应性设计,对此不加限制。在其他的一些实施例中,抑制环140的横截面形状也可以是梯形、d字形或者割圆形等。其中,割圆是指圆形被直线切掉一部分后,所保留的部分;半圆属于割圆中的特殊情况。

67.一些实施例中,芯片封装组件(11a,11b)还包括电路板150,该电路板150位于基板100的一侧并且远离芯片110;即,芯片110和电路板150分别位于基板100相互背对的两侧。电路板150可以通过导电球152与芯片110电连接,以配合芯片110实现通信、数据处理等功能。其中,导电球152可例如为导电锡球。

68.一些实施例中,芯片封装组件(11a,11b)还包括电子元件160,该电子元件160设于电路板150上并且位于基板100的周围。其中,该电子元件160可例如为电容、电感或者电阻等。

69.请同步参考图2和图4,以下将通过具体的例子来对各实施例的芯片封装组件11a进行说明,芯片封装组件的相关参数如下:

70.芯片110的功耗:soc(system on chip,片上系统)——372w(max),hbm(high bandwidth memory,高带宽存储)——17.7w(max)。

71.tim材料112:炭纤维导热垫或pcm(phase change material,相变材料),覆盖芯片110的面积≥90%,热阻≤0.2kcm2/w。

72.serdes(serializer/deserializer,串行器/解串器):最高速率58gbps pam4(pulse amplitude modulation,脉冲幅度调制)。

73.封装:裸片封装,芯片110的尺寸为29.75x25.45mm,基板100的尺寸为70x72.5mm,封环120的形状与基板100基本一致,封环120的最窄边宽为3mm。

74.抑制环140:抑制环140为导电衬垫,弹性内芯为聚氨脂类发泡材料,导电外层为镍/铜类导电纤维布,表面电阻≤0.1ω,尺寸为72x74.5x4mm,初始厚度为2mm,压缩范围为30~50%。

75.其中,散热器130与封环120之间的最短距离为1.2mm,抑制环140通过弹性形变而夹设在散热器130和封环120之间。抑制环140的压缩量大体上为40%,此可以通过抑制环140的初始厚度(例如2mm)以及散热器130与封环120之间的最短距离(例如1.2mm)之间的比例来进行验证。

76.图5为芯片封装组件的电磁噪声屏蔽效果仿真测试数据图,请参考图5,在激励源功率相同的前提下,相对金属盖封装的芯片封装组件,本技术各实施例的芯片封装组件的辐射功率(或者电磁噪声)与其基本相同。在2~30ghz频段范围内,各实施例的芯片封装组件向外辐射的辐射功率均可以保持较低的水平。

77.相对裸片封装的芯片封装组件,各实施例的芯片封装组件在通过裸片封装确保散热收益的同时,可以确保芯片封装组件的电磁噪声较小。

78.应当理解,在20ghz以上的高频范围,本技术各实施例的芯片封装组件仍保持较好的电磁噪声抑制效果,在该高频范围内的电磁波的辐射功率仍然保持在较低的水平。

79.基于此,当本技术各实施例的芯片封装组件应用到电子设备中,芯片封装组件在宽频段范围内的电磁噪声均可以保持较小的辐射功率,以减小与射频电路互相串扰的可能。

80.图6为现有芯片封装组件中芯片的压强测试数据图,图7为本技术实施例的芯片封装组件中芯片的压强测试数据图。请同步参考图6和图7,比之没有导电衬垫的芯片,通过导电衬垫缓冲保护的芯片在整体上所承受的压强较小。应当理解,基于该导电衬垫的保护,芯片封装组件可以具有更好的承压性能,以确保芯片封装组件在组装、运输等过程中保持结构的稳定性。

81.请参考图8,本技术实施例提供的另一种芯片封装组件12a,其包括基板100、芯片110、封环120、散热器130和抑制环140。但不同于上述各实施例的芯片封装组件(11a,11b),本实施例的散热器130包括散热器主体132和环形支架134,环形支架134位于散热器主体132的一侧并且朝向基板100的方向延伸。散热器130的环形支架134延伸至与封环120相间隔,抑制环140则设置在环形支架134和封环120之间。

82.应当理解,通过将抑制环140设于环形支架134和封环120之间的搭接方式,该抑制环140同样可以减小甚至消除散热器130与封环120之间的缝隙,由此可以抑制芯片110辐射的电磁波,以降低芯片封装组件12a的电磁噪声。此外,芯片封装组件12a与射频电路之间也不容易互相产生干扰,以确保各自的正常工作。

83.在其他的一些实施例中,该抑制环也可以位于散热器主体和封环之间,此同样可以屏蔽芯片辐射的电磁波,以降低芯片封装组件的电磁噪声。

84.请参考图8,一些实施例中,环形支架134位于封环120的外侧,但不以此为限。请参考图9,本技术实施例提供的另一种芯片封装组件12b,与芯片封装组件12a相比,该芯片封装组件12b的环形支架134是位于封环120的内侧。请参考图10,本技术实施例提供的另一种芯片封装组件12c,与芯片封装组件12a相比,该芯片封装组件12c的环形支架134是位于封环120之远离基板100的一侧。

85.应当理解,芯片封装组件(12b,12c)的结构均与芯片封装组件12a的结构类似,并且均可以实现类似芯片封装组件12a的功能,以抑制芯片110辐射的电磁波以及降低芯片封装组件(12b,12c)的电磁噪声,在此不加赘述。

86.请参考图11,本技术实施例提供的又一种芯片封装组件13,相对于上述各实施例中的芯片封装组件(12a,12b,12c),本实施例的抑制环140包括第一环形部142和第二环形部144。第一环形部142和第二环形部144均呈环形,第一环形部142沿着抑制环140的轴向延伸,第二环形部144沿着抑制环140的径向延伸。由此,沿着抑制环140的径向,该抑制环140的横截面大体上呈“l”的形状;其中,第一环形部142设置在环形支架134和封环120之间,第二环形部144设置在散热器主体132和封环120之间,以相互配合来抑制芯片110辐射的电磁波。由此可以降低芯片封装组件的电磁噪声并降低与射频电路相互串扰的可能。

87.一些实施例中,第一环形部142可例如为由吸波材料制成的环形结构件;或者,该第一环形部142可例如为导电衬垫。第二环形部144可例如为导电衬垫。基于此,第二环形部144在实现屏蔽电磁波功能的同时,还可以降低芯片110所承受的压强。

88.在其他的一些实施例中,第一环形部142和第二环形部144可以是由吸波材料制成的一体式的环形结构件;或者,第一环形部142和第二环形部144可以是一体式的导电衬垫。

89.请参考图12,本技术实施例提供的再一种芯片封装组件14,其包括基板100、芯片110、封环120、散热器130和抑制环140。不同于上述各实施例的芯片封装组件(11a,11b,12a,12b,12c,13),本实施例的抑制环140是直接环绕设置在基板100和散热器130之间,并且位于封环120的内侧。基板100、抑制环140和散热器130共同包围形成一个封闭空间,芯片110则位于该封闭空间内。

90.基于此,芯片110辐射的电磁波会直接被抑制环140和散热器130所抑制;类似上述各实施例的芯片封装组件(11a,11b,12a,12b,12c,13),该芯片110辐射的电磁波难以穿透至相对芯片封装组件14的外部,此同样可以降低芯片110向外辐射电磁波的可能,以减小芯片封装组件14的电磁噪声。此外,该芯片封装组件14与射频电路之间也不容易互相串扰。

91.一些实施例中,当该抑制环140为导电衬垫时,由于导电衬垫是直接位于基板100和散热器130之间,相对于上述各实施例的相关结构(例如位于封环120和散热器130之间的导电衬垫),本实施例的导电衬垫的尺寸也会更大。相应的,该导电衬垫的弹性变化范围较大;技术人员可以更方便地控制导电衬垫的回弹力,以提高导电衬垫的兼容性以及更好地保护芯片110。

92.例如:将导电衬垫的压缩范围控制在30%~40%,位于封环120和散热器130之间的导电衬垫的厚度为2mm,则该导电衬垫的弹性变化范围为0.6mm~0.8mm;而位于基板100和散热器130之间的导电衬垫的厚度为6mm,则该导电衬垫的弹性变化范围为1.8mm~2.4mm。由此,相对2mm厚度的导电衬垫,6mm厚度的导电衬垫可以具有较大的调整范围。在后续安装散热器130时,技术人员可以相对方便地调整散热器130与基板100的距离,以调整导电衬垫的压缩量以及实现芯片封装组件14的封装。

93.请参考图13,本技术实施例提供的再一种芯片封装组件15,其包括基板100、芯片110、散热器130和抑制环140。不同于上述各实施例的芯片封装组件14,该芯片封装组件15并没有设置封环120。抑制环140环绕设置在基板100和散热器130之间,以与基板100、散热器130共同包围形成封闭空间。应当理解,在此实施例中,通过基板100、散热器130和抑制环140的配合,同样可以抑制芯片110辐射的电磁波,以减小芯片封装组件15的电磁噪声。此外,该芯片封装组件15与射频电路之间也不容易互相串扰。

94.以上所述是本技术具体的实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本技术原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也视为本技术的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1