铜制程金属沟槽的制作方法与流程

[0001]

本发明涉及一种半导体集成电路制造方法,特别是涉及一种铜制程金属沟槽的制 作方法。

背景技术:

[0002]

随着工艺的发展,在后段工艺(beol)中需要采用铜制程形成铜互联结构,铜互 联结构中包括形成于金属沟槽中的铜连线以及填充于通孔开口中的铜形成的通孔。铜 连线和通孔通常采用大马士革工艺如双大马士革工艺实现,其中,金属沟槽需要采用 金属硬质掩膜层进行定义,金属硬质掩膜层通常采用tin,在tin层的底部和顶部需 要分别形成一层无氮抗反射涂层(nfdarc)。和sion组成的darc不同,nfdarc中不 含氮。

[0003]

现有工艺中,在形成金属沟槽之前,需要先形成金属硬质掩膜层的开口,所以, 金属硬质掩膜层的开口形成工艺很重要,金属硬质掩膜层的开口的关键尺寸偏移时, 会最会使得金属沟槽的关键尺寸产生偏移。随着半导体器件的技术节点缩小如缩小到 14nm以下,金属沟槽的关键尺寸往往达64nm以下,这种尺寸下的金属硬质掩膜层的 开口需要采用2次曝光两次刻蚀(2p2e)形成,现有2p2e工艺容易使得金属硬质掩 膜层的开口的关键尺寸产生偏移。

技术实现要素:

[0004]

本发明所要解决的技术问题是提供一种铜制程金属沟槽的制作方法,能采用2次 曝光两次刻蚀(2p2e)形成金属沟槽的金属硬质掩膜层开口且能避免2次曝光对应的 光刻去胶工艺对金属硬质掩膜层开口的关键尺寸的不利影响,从而能使两次刻蚀形成 的金属硬质掩膜层开口的关键尺寸保持一致,最后能得到关键尺寸较小且均一性较好 的金属沟槽。

[0005]

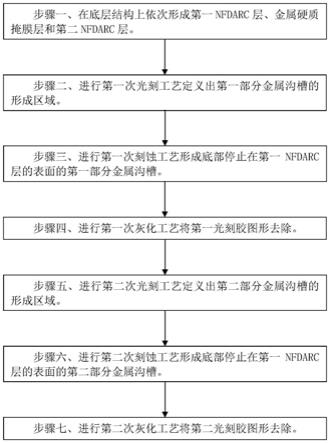

为解决上述技术问题,本发明提供的铜制程金属沟槽的制作方法包括如下步骤:

[0006]

步骤一、提供需要制作金属沟槽的底层结构,在所述底层结构上依次形成第一 nfdarc层、金属硬质掩膜层和第二nfdarc层。

[0007]

步骤二、进行第一次光刻工艺并形成第一光刻胶图形,所述第一光刻胶图形的第 一开口定义出第一部分金属沟槽开口的形成区域。

[0008]

步骤三、进行第一次刻蚀工艺将所述第一开口底部的所述第二nfdarc层和所述 金属硬质掩膜层都去除并形成底部停止在所述第一nfdarc层的表面的第一部分金属 沟槽开口。

[0009]

步骤四、进行第一次灰化工艺将所述第一光刻胶图形去除,利用所述第一部分金 属沟槽开口的底部停止在所述第一nfdarc层的表面特征,防止所述第一次灰化工艺 对所述第一部分金属沟槽开口的形貌产生改变。

[0010]

步骤五、进行第二次光刻工艺并形成第二光刻胶图形,所述第二光刻胶图形的第 二开口定义出第二部分金属沟槽开口的形成区域。

[0011]

步骤六、进行第二次刻蚀工艺将所述第二开口底部的所述第二nfdarc层和所述 金属硬质掩膜层都去除并形成底部停止在所述第一nfdarc层的表面的第二部分金属 沟槽开口。

[0012]

步骤七、进行第二次灰化工艺将所述第二光刻胶图形去除,利用所述第二部分金 属沟槽开口的底部停止在所述第一nfdarc层的表面特征,防止所述第二次灰化工艺 对所述第二部分金属沟槽开口的形貌产生改变。

[0013]

进一步的改进是,所述金属硬质掩膜层的材料为tin。

[0014]

进一步的改进是,所述第一次光刻工艺中,在所述第一光刻胶图形的底部还形成 有第一有机底层和第一硅氧基硬掩模中间层。

[0015]

进一步的改进是,所述第一次刻蚀工艺中会先刻蚀所述第一硅氧基硬掩模中间层 和所述第一有机底层,再刻蚀所述第二nfdarc层和所述金属硬质掩膜层。

[0016]

所述第一次灰化工艺会同时将所述第一硅氧基硬掩模中间层和所述第一有机底 层去除。

[0017]

进一步的改进是,所述第一次灰化工艺采用氧气等离子体刻蚀工艺。

[0018]

进一步的改进是,所述第二次光刻工艺中,在所述第二光刻胶图形的底部还形成 有第二有机底层和第二硅氧基硬掩模中间层。

[0019]

进一步的改进是,所述第二次刻蚀工艺中会先刻蚀所述第二硅氧基硬掩模中间层 和所述第二有机底层,再刻蚀所述第二nfdarc层和所述金属硬质掩膜层。

[0020]

所述第二次灰化工艺会同时将所述第二硅氧基硬掩模中间层和所述第二有机底 层去除。

[0021]

进一步的改进是,所述第二次灰化工艺采用氧气等离子体刻蚀工艺。

[0022]

进一步的改进是,所述第二开口和所述第一开口相互错开,使所述第一部分金属 沟槽开口和所述第二部分金属沟槽开口相互错开。

[0023]

进一步的改进是,步骤一中所述底层结构包括形成于半导体衬底上的层间膜,在 所述第一部分金属沟槽开口和所述第二部分金属沟槽开口的定义下,对所述层间膜进 行刻蚀形成金属沟槽。

[0024]

进一步的改进是,在所述金属沟槽中填充铜层形成铜连线。

[0025]

进一步的改进是,还包括形成通孔的步骤,所述通孔形成于所述金属沟槽的选定 区域的底部。

[0026]

进一步的改进是,采用双大马士革工艺形成所述金属沟槽和所述通孔的开口,之 后在所述金属沟槽和所述通孔的开口中同时填充铜层同时形成所述铜连线和所述通 孔。

[0027]

进一步的改进是,在所述半导体衬底上形成有半导体器件。

[0028]

进一步的改进是,所述半导体器件的工艺节点为14nm以下。

[0029]

所述铜连线为后段工艺,所述金属沟槽的最小宽度达64nm以下。

[0030]

本发明采用2p2e工艺形成定义金属沟槽的金属硬质掩膜层开口即第一部分金属 沟槽开口和第二部分金属沟槽开口,本发明为了消除两侧光刻工艺中的去胶的灰化工 艺对第一部分金属沟槽开口和第二部分金属沟槽开口的影响,本发明对两次刻蚀工艺 做了特别的设置,两次刻蚀工艺都设置为以对应的光刻胶图形为掩膜直接将金属硬质 掩膜层刻穿并停止在底部的nfdarc层即第一nfdarc层上,这样就能消除将两次光刻 工艺后的刻

会影响所述第一部分金属沟槽开口109a的关键尺寸。

[0048]

步骤五、如图1d所示,进行第二次光刻工艺并形成第二光刻胶图形107b,所述 第二光刻胶图形107b的第二开口108b定义出第二部分金属沟槽开口109b的形成区 域。

[0049]

通常,所述第二次光刻工艺中,在所述第二光刻胶图形107b的底部还形成有第 二有机底层105b和第二硅氧基硬掩模中间层106b。

[0050]

第二shb层106b通常采用barc。第二odl层105b采用soc。

[0051]

步骤六、如图1e所示,进行第二次刻蚀工艺将所述第二开口108b底部的所述第 二nfdarc层104去除并形成底部停止在和所述金属硬质掩膜层103的表面的第二部 分金属沟槽开口109b。

[0052]

通常,所述第二次刻蚀工艺中会先刻蚀所述第二硅氧基硬掩模中间层106b和所 述第二有机底层105b,再刻蚀所述第二nfdarc层104。

[0053]

步骤七、如图1f所示,进行第二次灰化工艺将所述第二光刻胶图形107b去除。

[0054]

通常,所述第二次灰化工艺会同时将所述第二硅氧基硬掩模中间层106b和所述 第二有机底层105b去除。

[0055]

所述第二次灰化工艺采用氧气等离子体刻蚀工艺。

[0056]

所述第二开口108b和所述第一开口108a相互错开,使所述第一部分金属沟槽开 口109a和所述第二部分金属沟槽开口109b相互错开。

[0057]

所述第二次灰化工艺容易对所述金属硬质掩膜层103产生不利影响如氧化,由于 所述第二次灰化工艺中所述第一部分金属沟槽开口109a的表面也会受到影响,故所 述第二次灰化工艺会同时影响所述第一部分金属沟槽开口109a和所述第二部分金属 沟槽开口109b的关键尺寸。

[0058]

本发明实施例铜制程金属沟槽的制作方法:

[0059]

如图2所示,是本发明实施例铜制程金属沟槽的制作方法的流程图;如图3a至 图3d所示,是本发明实施例铜制程金属沟槽的制作方法各步骤中的器件结构示意图; 本发明实施例铜制程金属沟槽的制作方法包括如下步骤:

[0060]

步骤一、如图3a所示,提供需要制作金属沟槽的底层结构1,在所述底层结构1 上依次形成第一nfdarc层2、金属硬质掩膜层3和第二nfdarc层4。

[0061]

本发明实施例中,所述金属硬质掩膜层3的材料为tin。

[0062]

步骤二、如图3a所示,进行第一次光刻工艺并形成第一光刻胶图形7a,所述第 一光刻胶图形7a的第一开口8a定义出第一部分金属沟槽开口9a的形成区域。

[0063]

本发明实施例中,所述第一次光刻工艺中,在所述第一光刻胶图形7a的底部还 形成有第一有机底层5a和第一硅氧基硬掩模中间层6a。

[0064]

步骤三、如图3b所示,进行第一次刻蚀工艺将所述第一开口8a底部的所述第二 nfdarc层4和所述金属硬质掩膜层3都去除并形成底部停止在所述第一nfdarc层2 的表面的第一部分金属沟槽开口9a。

[0065]

本发明实施例中,所述第一次刻蚀工艺中会先刻蚀所述第一硅氧基硬掩模中间层 6a和所述第一有机底层5a,再刻蚀所述第二nfdarc层4和所述金属硬质掩膜层3。

[0066]

步骤四、如图3b所示,进行第一次灰化工艺将所述第一光刻胶图形7a去除,利 用所述第一部分金属沟槽开口9a的底部停止在所述第一nfdarc层2的表面特征,防 止所述第

一次灰化工艺对所述第一部分金属沟槽开口9a的形貌产生改变。

[0067]

本发明实施例中,所述第一次灰化工艺会同时将所述第一硅氧基硬掩模中间层6a 和所述第一有机底层5a去除。

[0068]

所述第一次灰化工艺采用氧气等离子体刻蚀工艺。

[0069]

步骤五、如图3c所示,进行第二次光刻工艺并形成第二光刻胶图形7b,所述第 二光刻胶图形7b的第二开口8b定义出第二部分金属沟槽开口9b的形成区域。

[0070]

本发明实施例中,所述第二次光刻工艺中,在所述第二光刻胶图形7b的底部还 形成有第二有机底层5b和第二硅氧基硬掩模中间层6b。

[0071]

步骤六、如图3d所示,进行第二次刻蚀工艺将所述第二开口8b底部的所述第二 nfdarc层4和所述金属硬质掩膜层3都去除并形成底部停止在所述第一nfdarc层2 的表面的第二部分金属沟槽开口9b。

[0072]

本发明实施例中,所述第二次刻蚀工艺中会先刻蚀所述第二硅氧基硬掩模中间层 6b和所述第二有机底层5b,再刻蚀所述第二nfdarc层4和所述金属硬质掩膜层3。

[0073]

步骤七、如图3d所示,进行第二次灰化工艺将所述第二光刻胶图形7b去除,利 用所述第二部分金属沟槽开口9b的底部停止在所述第一nfdarc层2的表面特征,防 止所述第二次灰化工艺对所述第二部分金属沟槽开口9b的形貌产生改变。

[0074]

本发明实施例中,所述第二次灰化工艺会同时将所述第二硅氧基硬掩模中间层6b 和所述第二有机底层5b去除。

[0075]

所述第二次灰化工艺采用氧气等离子体刻蚀工艺。

[0076]

所述第二开口8b和所述第一开口8a相互错开,使所述第一部分金属沟槽开口9a 和所述第二部分金属沟槽开口9b相互错开。

[0077]

步骤一中所述底层结构1包括形成于半导体衬底上的层间膜,在所述第一部分金 属沟槽开口9a和所述第二部分金属沟槽开口9b的定义下,对所述层间膜进行刻蚀形 成金属沟槽。

[0078]

后续还包括:在所述金属沟槽中填充铜层形成铜连线。

[0079]

还包括形成通孔的步骤,所述通孔形成于所述金属沟槽的选定区域的底部。

[0080]

采用双大马士革工艺形成所述金属沟槽和所述通孔的开口,之后在所述金属沟槽 和所述通孔的开口中同时填充铜层同时形成所述铜连线和所述通孔。

[0081]

在所述半导体衬底上形成有半导体器件。

[0082]

所述半导体器件的工艺节点为14nm以下。

[0083]

所述铜连线为后段工艺,所述金属沟槽的最小宽度达64nm以下。

[0084]

本发明实施例采用2p2e工艺形成定义金属沟槽的金属硬质掩膜层3开口即第一 部分金属沟槽开口9a和第二部分金属沟槽开口9b,本发明实施例为了消除两侧光刻 工艺中的去胶的灰化工艺对第一部分金属沟槽开口9a和第二部分金属沟槽开口9b的 影响,本发明实施例对两次刻蚀工艺做了特别的设置,两次刻蚀工艺都设置为以对应 的光刻胶图形为掩膜直接将金属硬质掩膜层3刻穿并停止在底部的nfdarc层即第一 nfdarc层2上,这样就能消除将两次光刻工艺后的刻蚀工艺都停止在金属硬质掩膜层 3的表面时灰化工艺如采用氧气等离子体刻蚀工艺的灰化工艺对金属硬质掩膜层3表 面的不利影响,从而能消除对金属硬质掩膜层3开口的关键尺寸的不利影响,防止金 属硬质掩膜层3开口的关键尺

寸产生偏差,能使两次刻蚀形成的金属硬质掩膜层3开 口的关键尺寸保持一致,最后能得到关键尺寸较小且均一性较好的金属沟槽,本发明 实施例特别能适用于14nm以下工艺节点的半导体器件的后段工艺的铜连线的金属沟 槽中,能金属沟槽的最小宽度达64nm以下。

[0085]

以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限 制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这 些也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1