一种基于Flip-chip连接的超薄封装件及其制作工艺的制作方法

一种基于flip-chip连接的超薄封装件及其制作工艺

技术领域

[0001]

本发明属于集成电路封装技术领域,具体涉及一种基于flip-chip连接的超薄封装件及其制作工艺。

背景技术:

[0002]

集成电路扁平无引脚封装(qfn/dfn),在近几年随着通讯设备(如基站、交换机)、智能手机、便携式设备(如平板电脑)、可穿戴设备(如智能手表、智能眼镜、智能手环等)的普及而迅速发展,特别适用于有高频、高带宽、低噪声、高导热、小体积、高速度等电性需求的大规模集成电路的封装,集成电路扁平无引脚封装(qfn/dfn)有效地利用了引线脚的封装空间,从而大幅度地提高了封装效率;该封装由于引线短小、塑封体尺寸小、封装体薄,可以使cpu体积缩小30%-50%;所以它能提供卓越的电性能,同时还提供了出色的散热性能。

[0003]

传统的集成电路扁平无引脚封装封装(qfn/dfn)主要存在以下不足:框架载体的qfn/dfn封装产品需要根据芯片尺寸及电路连通需求设计框架图形,再用腐蚀等方法将框架加工成设计好的图形,设计及制作周期长,成本比较高;并且目前的qfn/dfn封装系列封装件在凸点的排布以及i/o的密集程度上也由于框架设计及框架制造工艺而有所限制。同时,由于框架在腐蚀变薄后,在模具内有滑动的风险,封装可靠性得不到保障;以及传统的qfn/dfn产品厚度仍然比较大,无法满足当前的便携式设备对小体积、高密度封装的需求。

技术实现要素:

[0004]

为了克服上述现有技术存在的问题,本发明提供了一种基于flip-chip连接的超薄封装件及其制作工艺,生产产品前不再需要根据芯片尺寸及电路连通设计框架图形及加工框架,在引线框架制作过程中即可设计图形,使用普通的金属板即可制作产品,无需对金属板进行过多加工,制作周期短,极大降低成本。在很大程度上使目前集成电路扁平无引脚系列封装件不再被框架设计及制作工艺所局限,使得产品凸点的排布以及i/o的密集程度上得到极大的提升。同时,在图形镀银层和框架基板之间增加一层铜倒角互连层,塑封之后形成有效的防拖拉结构,极大地降低了框架在腐蚀变薄后,在模具内滑动的风险,同时降低了塑封料压力,增加了塑封料与金属框架的接合面积,封装可靠性大幅提升。

[0005]

为达此目的,本发明采用以下技术方案:

[0006]

一种基于flip-chip连接的超薄封装件,所述封装件包括:

[0007]

塑封体、芯片、多个金属凸点、镀银层、镀nipdau层、铜倒角连接层以及引线框架;

[0008]

所述镀银层为多段式层结构,且形成相互独立间隔的层段;

[0009]

所述芯片的电气面植有所述金属凸点;所述芯片通过所述金属凸点电气接合于所述所述镀银层上;

[0010]

所述塑封体能够将所述金属凸点、所述芯片、所述镀银层、所述镀nipdau层和所述铜倒角连接层填充包围;

[0011]

所述金属凸点与引线框架通过导线连通;使其所述金属凸点、所述镀银层、所述铜

倒角连接层与所述镀nipdau层构成电路的电源和信号通道。

[0012]

本实施例中,所述塑封体为绝缘材质,填充在整个封装件的空间内部。

[0013]

本发明还包括一种基于flip-chip连接的超薄封装件的制作工艺,具体按照

[0014]

以下步骤进行:

[0015]

步骤1,在所述引线框架的预定位置上镀nipdau,并形成所述镀nipdau层;所述镀nipdau层的厚度为3um~5um;

[0016]

步骤2,在步骤1所述镀nipdau层上形成所述铜倒角连接层,所述铜倒角连接层的厚度为50um~100um;并腐蚀成倒凸台;

[0017]

步骤3,在步骤2所述铜倒角连接层上镀所述镀银层;所述镀银层的厚度为3um~5um;

[0018]

步骤4,进行减薄处理,减薄厚度为50μm~200μm,并控制表面粗糙度为ra0.10mm~0.05mm;

[0019]

步骤5,采用划片机进行划片;

[0020]

步骤6,在所述芯片上用植球的方式作出所述金属凸点,倒装上芯后直接和所述引线框架连通;

[0021]

步骤7,对整体进行塑封,塑封料填充满所述铜倒角连接层的凹槽,形成有效的防拖拉结构,确保封装可靠性;

[0022]

步骤8,用化学溶液腐蚀掉全部所述引线框架,并露出所述镀nipdau层;

[0023]

步骤9,将步骤8形成的封装件进行切割、包装。

[0024]

本实施例中,所述铜倒角连接层的材质为a194。

[0025]

本发明的有益效果为:

[0026]

本发明提供的一种基于flip-chip连接的超薄封装件及其制作工艺,封装件包括:包括塑封体、芯片、多个金属凸点、镀银层、镀nipdau层、铜倒角连接层以及引线框架;镀银层为多段式层结构,且形成相互独立间隔的层段;芯片的电气面植有金属凸点;芯片通过金属凸点电气接合于镀银层上;塑封体能够将金属凸点、芯片、镀银层、镀nipdau层和铜倒角连接层填充包围;金属凸点与引线框架通过导线连通;使其金属凸点、镀银层、铜倒角连接层与镀nipdau层构成电路的电源和信号通道;通过上述设置,使得本发明具备以下技术效果:

[0027]

(1)本发明采用普通框架即可进行产品制作流程,无需过多加工框架载体,缩短设计周期,降低成本;

[0028]

(2)镀银层和镀nipdau层厚度仅3~5um,大大降低了qfn/dfn封装产品的厚度(qfn产品厚度可控制在0.35mm以内),而传统的qfn/dfn产品厚度在0.7mm以上。本发明提供的技术可使封装体厚度减小100%;

[0029]

(3)在凸点排布及i/o数不受框架设计及制作限制的前提下,实现了凸点排布可任意定义,更好地实现芯片与载体的互连;

[0030]

(4)在图形镀银层和框架基板之间增加一层铜倒角互连层,塑封之后形成有效的防拖拉结构,极大地降低了框架在腐蚀变薄后,在模具内滑动的风险;同时,降低了塑封料压力,增加了塑封料与金属框架的接合面积,封装可靠性大幅提升;

[0031]

(5)本发明提供的封装件将镀nipdau层作为与外部电路的信号连接通道,相当于

普通封装的“管脚”,可以省去电镀环节;

[0032]

(6)传统的qfn/dfn框架,为了防止塑封时发生“溢胶”,在框架背面贴有一层膜;而本发明由于框架上面镀了一层nipdau,可以起到隔离塑封料的作用,塑封后腐蚀掉框架,同样可以起到防止“溢胶”的作用,这样就可以省去框架厂商“贴膜”的过程;由于本发明提供的封装件可以免电镀、免贴膜,生产成本可以大幅降低,产品更有竞争力。

附图说明

[0033]

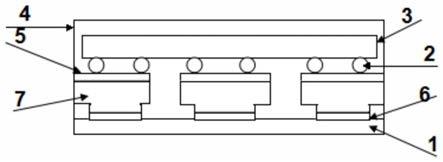

图1为引线框架剖面图;

[0034]

图2为引线框架镀nipdau后剖面图;

[0035]

图3为引线框架的镀nipdau层上生长铜层(a194)并腐蚀出倒角后的剖面图;

[0036]

图4为铜倒角连接层上镀银后的剖面图;

[0037]

图5为芯片减薄划片后的剖面图;

[0038]

图6为芯片植金属凸点后的剖面图;

[0039]

图7为倒装上芯后的剖面图;

[0040]

图8为产品塑封后的剖面图;

[0041]

图9为产品腐蚀框架后的剖面图;

[0042]

图10为产品成品剖面图。

[0043]

图中:

[0044]

1、引线框架;2、金属凸点;3、芯片;4、为塑封体;5、镀银层;6、镀nipdau层;7、铜倒角连接层。

具体实施方式

[0045]

下面结合附图并通过具体实施方式来进一步说明本发明的技术方案。

[0046]

如图1-10所示,一种基于flip-chip连接的超薄封装件,封装件包括:

[0047]

塑封体4、芯片3、多个金属凸点2、镀银层5、镀nipdau层6、铜倒角连接层7以及引线框架1;

[0048]

镀银层5为多段式层结构,且形成相互独立间隔的层段;

[0049]

芯片3的电气面植有金属凸点2;芯片3通过金属凸点2电气接合于镀银层5上;

[0050]

塑封体4能够将金属凸点2、芯片3、镀银层5、镀nipdau层6和铜倒角连接层7填充包围;

[0051]

金属凸点2与引线框架1通过导线连通;使其金属凸点2、镀银层5、铜倒角连接层7与镀nipdau层6构成电路的电源和信号通道。

[0052]

进一步地,塑封体4为绝缘材质,填充在整个封装件的空间内部。

[0053]

本实施例还公开了一种基于flip-chip连接的超薄封装件的制作工艺,具

[0054]

体按照以下步骤进行:

[0055]

步骤1,在引线框架1的预定位置上镀nipdau,并形成镀nipdau层6;镀nipdau层6的厚度为3um~5um;

[0056]

步骤2,在步骤1镀nipdau层6上形成铜倒角连接层7,铜倒角连接层7的厚度为50um~100um;并腐蚀成倒凸台;

[0057]

步骤3,在步骤2铜倒角连接层7上镀镀银层5;镀银层5的厚度为3um~5um;

[0058]

步骤4,进行减薄处理,减薄厚度为50μm~200μm,并控制表面粗糙度为ra0.10mm~0.05mm;

[0059]

步骤5,采用划片机进行划片;

[0060]

步骤6,在芯片3上用植球的方式作出金属凸点2,倒装上芯后直接和引线框架1连通;

[0061]

步骤7,对整体进行塑封,塑封料填充满铜倒角连接层7的凹槽,形成有效的防拖拉结构,确保封装可靠性;

[0062]

步骤8,用化学溶液腐蚀掉全部引线框架1,并露出镀nipdau层6;

[0063]

步骤9,将步骤8形成的封装件进行切割、包装。

[0064]

进一步地,铜倒角连接层7的材质为a194。

[0065]

以上实施,具体来说,传统的qfn/dfn工艺流程为:框架镀银

→

晶圆减薄

→

划片

→

做金属凸点

→

倒装上芯

→

塑封

→

腐蚀框架

→

电镀

→

切割

→

包装。

[0066]

本实施例公开的一种基于flip-chip连接的超薄封装件的制作工艺,框架镀nipdau

→

生长铜倒角连接层(通过腐蚀,在铜层和镀nipdau层之间形成图附图3所示的倒角凹槽)

→

铜倒角连接层上镀银

→

晶圆减薄

→

划片

→

芯片做金属凸点

→

倒装上芯

→

塑封

→

腐蚀框架

→

切割

→

包装。

[0067]

更为具体来说,在引线框架1的预定位置上镀nipdau,并形成镀nipdau层6;镀nipdau层6的厚度为3um~5um;之后生长铜倒角连接层7,在nipdau层6上生长一层50~100um的铜层,并腐蚀成倒角形状(铜层采用a194);其次在步骤2铜倒角连接层7上镀镀银层5;镀银层5的厚度为3um~5um。在框架制作厂家制作过程中,先设计好框架的图形,然后镀银层5形成图形。采用普通框架,在完成步骤1和2之后再镀银即可进行产品制作流程,无需过多加工框架载体,即可实现电路连通,缩短设计及制作周期,节约成本。之后再进行晶圆减薄,进行减薄处理,减薄厚度为50μm~200μm,并控制表面粗糙度ra为0.10mm~0.05mm。完成之后进行划片工艺,此处需要说明的是,针对厚度150μm以上晶圆同普通集成电路扁平封装件划片工艺,但厚度在150μm以下晶圆,使用双刀划片机及其工艺。而后在芯片3上做金属凸点2;在芯片3上用植球的方式作出金属凸点2,倒装上芯后直接和引线框架1连通。之后再进入塑封工艺,其采用现有技术的方法,塑封料填充满铜倒角层的凹槽,形成有效的防拖拉结构,封装可靠性大幅提高。之后再进行框架腐蚀:产品塑封后用化学溶液腐蚀掉全部引线框架1,露出镀nipdau层6即可实现线路导通。此方法可缩短设计及制作周期,降低成本。最后进行进行切割、包装,其方式同常规方法。

[0068]

通过上述设置可以看出,本发明带来的实质效果为:在金属凸点2排布及i/o数不受框架设计及制作限制的前提下,本发明通过电镀银之后倒装上芯的方法,实现了框架图形设计可在框架制作时期就完成,缩短了制作周期,更好得实现芯片与载体的互联,使i/o更加密集,成本更低;同时,增加了一层3~5um的nipdau层,使生产时免电镀;增加了一层铜(a194)倒角连接层,塑封之后,塑封料填充满铜倒角层的凹槽,形成有效的防拖拉结构,同时降低了塑封料压力,增加了塑封料与金属框架的接合面积,提高了封装的可靠性。

[0069]

本发明提供的封装件将镀nipdau层作为与外部电路的信号连接通道,相当于普通封装的“管脚”,可以省去电镀环节。传统的qfn/dfn框架,为了防止塑封时发生“溢胶”,在框

架背面贴有一层膜;而本发明由于框架上面镀了一层nipdau,可以起到隔离塑封料的作用,塑封后腐蚀掉框架,同样可以起到防止“溢胶”的作用,这样就可以省去框架厂商“贴膜”的过程。由于本发明提供的封装件免电镀、免贴膜,生产成本可以大幅降低,产品更有竞争力。

[0070]

本发明是通过优选实施例进行描述的,本领域技术人员知悉,在不脱离本发明的精神和范围的情况下,可以对这些特征和实施例进行各种改变或等效替换。本发明不受此处所公开的具体实施例的限制,其他落入本申请的权利要求内的实施例都属于本发明保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1