半导体存储器结构的形成方法与流程

1.本发明实施例是关于一种半导体存储器结构的形成方法,且特别是有关于快闪存储器的形成方法。

背景技术:

2.为了增加快闪存储器装置内的元件密度以及改善其整体表现,目前快闪存储器装置的制造技术持续朝向元件尺寸的微缩化而努力。然而,当最小元件(例如接触件)的尺寸持续缩小时,许多挑战随之而生。因此,业界仍需要改进快闪存储器装置的制造方法,以克服元件尺寸缩小所产生的问题。

技术实现要素:

3.本发明实施例提供半导体存储器结构的形成方法,此方法包含依序形成主动层、硬遮罩层、以及核心层于基底之上、以及刻蚀核心层以形成核心图案。核心图案包含第一长条、第二长条、以及抵接第一长条和第二长条的多个支撑部件。此方法还包含形成间隔物层于核心图案旁边、移除核心图案、形成光阻图案于间隔物层上方、使用光阻图案和间隔物层,刻蚀硬遮罩层以形成硬遮罩图案、以及将硬遮罩图案转移至主动层以形成栅极堆迭。

4.本发明实施例提供半导体存储器结构的形成方法,此方法包含依序形成主动层、硬遮罩层、以及核心层于基底之上、以及形成第一光阻图案和第二光阻图案于核心层之上。第二光阻图案包含第一长条、第二长条、以及自第一长条延伸至第二长条的多个连接部件。此方法还包含将第一光阻图案和第二光阻图案转移至核心层,以分别形成第一核心图案和第二核心图案、形成一对第一间隔物于第一核心图案两侧、以及一对第二间隔物于第二核心图案两侧、移除第一核心图案和第二核心图案、形成第三光阻图案于第二间隔物之上、以及使用第三光阻图案、第一间隔物、和第二间隔物,刻蚀硬遮罩层和主动层。

附图说明

5.为了让本发明的特征和优点能更明显易懂,下文特举不同实施例,并配合所附图式作详细说明如下:

6.图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i是根据本发明的一些实施例,绘示形成半导体存储器结构在不同阶段的剖面示意图。

7.图1a-1、图1b-1、图1c-1、图1d-1、图1e-1、图1f-1、图1g-1、图1h-1、图1i-1是根据本发明的一些实施例,分别绘示图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i的半导体存储器结构的平面示意图。

8.图2a、图2b、图2c是根据本发明的一些实施例,绘示形成半导体存储器结构在不同阶段的剖面示意图。

9.图2a-1是根据本发明的一些实施例,绘示图2a的半导体存储器结构的平面示意图。

10.图3a和图3b是根据本发明的一些实施例,绘示形成半导体存储器结构在不同阶段的剖面示意图。

11.图3b-1是根据本发明的一些实施例,绘示图3b的半导体存储器结构的平面示意图。

12.图4a-1、图4b-1、图4c-1是根据本发明的一些实施例,绘示形成半导体存储器结构在不同阶段的平面示意图。

13.附图标记:

14.50:存储器单元预定区

15.60:选择晶体管预定区

16.100:半导体存储器结构

17.102:半导体基底

18.103:穿隧氧化物

19.104:第一多晶硅层

20.105第二多晶硅层

21.106:栅极介电层

22.107:第三多晶硅层

23.108:第四多晶硅层

24.110:主动层

25.115:栅极堆迭

26.116:栅极堆迭

27.120:介电硬遮罩层

28.120’:图案化介电硬遮罩层

29.125:硬遮罩图案

30.126:硬遮罩图案

31.130:半导体硬遮罩层

32.130’:图案化半导体硬遮罩层

33.135:硬遮罩图案

34.136:硬遮罩图案

35.140:核心层

36.140’:图案化核心层

37.145:第二核心图案

38.146:第二核心图案

39.1471:长条

40.1472:长条

41.148:支撑部件

42.1481:支撑部

43.1482:支撑部

44.149;开口

45.150:抗反射层

46.150’:图案化抗反射层

47.160:图案化光阻层

48.165:第一光阻图案

49.166:第二光阻图案

50.1671:长条

51.1672:长条

52.168:连接部件

53.169:开口

54.170:顺应层

55.170’:间隔物层

56.175:第一间隔物

57.1761:第二间隔物

58.1762:第二间隔物

59.177:第三间隔物

60.180:填充层

61.180’:填充层

62.182:抗反射层

63.190:图案化光阻层

64.192:光阻图案

65.192a:侧壁

66.192b:侧壁

67.200:半导体存储器结构

68.202:缺口

69.300:半导体存储器结构

70.302:开口

71.a1:第一方向

72.a2:第二方向

73.d1:宽度

74.d2:宽度

75.d3:长度

76.d4:宽度

77.d5:宽度

78.d6:宽度

79.d7:宽度

80.d8:宽度

81.d9:距离

82.d10:距离

83.e1:延伸线

84.e2:延伸线

具体实施方式

85.以下参照本发明实施例的图式以更全面地阐述本揭露。然而,本揭露亦可以各种不同的实施方式实现,而不应限于本文中所述的实施例。图式中的层与区域的厚度可能会为了清楚起见而放大,并且在各图式中相同或相似的参考号码表示相同或相似的元件。

86.图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i和图1a-1、图1b-1、图1c-1、图1d-1、图1e-1、图1f-1、图1g-1、图1h-1、图1i-1是根据本发明的一些实施例,绘示形成半导体存储器结构在不同阶段的示意图,其中图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i分别是沿着图1a-1、图1b-1、图1c-1、图1d-1、图1e-1、图1f-1、图1g-1、图1h-1、图1i-1的平面示意图中的线i-i撷取的剖面示意图。

87.图1a绘示半导体存储器结构100的剖面示意图,半导体存储器结构100包含存储器单元预定区50及邻近存储器单元预定区50的选择晶体管预定区60,存储器单元及其字元线将形成于存储器单元预定区50中,而选择晶体管(例如,位线选择晶体管或源极线选择晶体管)将形成于选择晶体管预定区60中。尽管图1a显示了一个存储器单元预定区50和与其相邻的一个选择晶体管预定区60,然而一个存储器单元预定区50可设置于两个选择晶体管预定区60之间。在一些实施例中,选择晶体管预定区60靠近存储器单元预定区50的部分是图案密集(pattern-dense)区,而选择晶体管预定区60远离存储器单元预定区50的部分是图案稀疏(pattern-sparse)区。

88.半导体存储器结构100的形成包括提供半导体基底102。在一些实施例中,半导体基底102可以是元素半导体基底,例如硅基底、或锗基底;或化合物半导体基底,例如碳化硅基底、或砷化镓基底。在一些实施例中,半导体基底102可以是绝缘体上的半导体(semiconductor-on-insulator,soi)基底。

89.形成主动层110于半导体基底102之上。根据一些实施例,主动层110是多层堆迭,其包含依序形成于半导体基底102之上的穿隧氧化物(tunneling oxide)层103、第一多晶硅层104、第二多晶硅层105、栅极介电层106、第三多晶硅层107、以及第四多晶硅层108。穿隧氧化物层103可由氧化硅形成。第一多晶硅层104及第二多晶硅层105可以掺杂的,并且用以形成存储器单元的浮置栅极。栅极介电层106可以是包含氧化物-氮化物-氧化物(oxide-nitride-oxide,ono)的三层结构。第三多晶硅层107及第四多晶硅层108可以掺杂的,并且用以形成存储器单元的控制栅极,且可兼作为字元线。

90.形成介电硬遮罩层120于主动层110之上。在一些实施例中,介电硬遮罩层120由介电材料形成,例如,氧化硅(silicon oxide,sio)、氮氧化硅(silicon oxynitride,sion)、氮化硅(silicon nitride,sin)、及/或其他适合的介电材料。在一实施例中,介电硬遮罩层120由四乙氧基硅烷(tetraethyl orthosilicate,teos)氧化物形成。

91.形成半导体硬遮罩层130于介电硬遮罩层120之上。在一些实施例中,半导体硬遮罩层130由半导体材料形成,例如,多晶硅。

92.形成核心层140于半导体硬遮罩层130之上。在一些实施例中,核心层140由富碳材料形成,例如,碳层或旋涂碳(spin-on coating,soc)。

93.形成抗反射层150于核心层140之上。在一些实施例中,抗反射层150由富硅材料形成,例如,氮氧化硅(sion)。

94.使用光刻工艺形成图案化光阻层160于抗反射层150之上,如图1a和图1a-1所示。

图案化光阻层160包含设置于存储器单元预定区50的多个第一光阻图案165、以及设置于选择晶体管预定区60的第二光阻图案166。

95.这些第一光阻图案165是在第一方向a1上平行排列并且沿着第二方向a2延伸的长条,如图1a-1所示。第一方向a1和第二方向a2是水平方向,并且第一方向a1大致垂直于第二方向a2。第一光阻图案165在一个存储器单元预定区50中的数目可以在约6至约10个,例如8个。

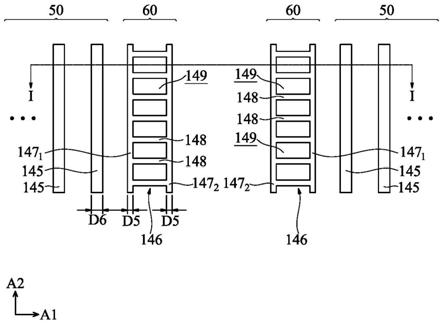

96.第二光阻图案166具有铁轨形轮廓。具体而言,第二光阻图案166包含长条1671、长条1672、以及介于长条1671与长条1672之间的多个连接部件168,如图1a-1所示。长条1671比长条1672靠近存储器单元预定区50。长条1671和长条1672在第一方向a1上平行排列,并且沿着第二方向a2延伸。这些连接部件168在第二方向a2上平行排列,并且沿着第一方向a1延伸。连接部件168自长条1671连续地延伸至长条1672,以连接长条1671与长条1672。长条1671、长条1672、与连接部件168界定出多个开口169,开口169暴露出抗反射层150。连接部件168在一个选择晶体管预定区60的数目可取决于长条1671和长条1672的长度,例如约5至约1000个。

97.在一些实施例中,第二光阻图案166的长条1671和长条1672沿着第一方向a1具有宽度d1,第一光阻图案165沿着第一方向a1具有宽度d2,宽度d1对宽度d2的比值为约0.8至约1.0。若宽度d1对宽度d2的比值太小,则增加后续形成于选择晶体管预定区60的核心图案倒塌的风险。若宽度d1对宽度d2的比值太大,则无法增加后续形成选择栅极图案的光刻工艺的迭对容许度(overlay window)。

98.在一些实施例中,开口169沿着第二方向a2具有长度d3(即,相邻的连接部件168之间的距离),并且沿着第一方向a1具有宽度d4(即,长条1671与长条1672之间的距离),长度d3对宽度d4的比值为约1.0至约4.0。

99.使用图案化光阻层160,对半导体存储器结构100进行刻蚀工艺,以依序刻蚀移除抗反射层150和核心层140未被图案化光阻层160覆盖的部分,直到暴露出半导体硬遮罩层130的上表面,如图1b和图1b-1所示。在一些实施例中,刻蚀工艺是干刻蚀。图案化光阻层160可以在刻蚀工艺中被完全消耗,或是通过额外的灰化工艺移除。

100.刻蚀工艺之后的抗反射层150和核心层140分别标示为图案化反射层150’和图案化核心层140’。图案化光阻层160的光阻图案165和166转移至核心层140,使得核心层140形成对应于第一光阻图案165的多个第一核心图案145、以及对应于第二光阻图案166的第二核心图案146。根据一些实施例,在刻蚀工艺之后,可对图案化核心层140’进行修整工艺,从而降低形成于半导体存储器结构100表面上的缺陷。修整工艺可以是例如使用o2的刻蚀工艺。

101.这些第一核心图案145是在第一方向a1上平行排列并且沿着第二方向a2延伸的长条。第二核心图案146包含长条1471、长条1472、以及介于长条1471与长条1472之间的多个支撑部件148。长条1471比长条1472靠近存储器单元预定区50。长条1471和长条1472在第一方向a1上平行排列,并且沿着第二方向a2延伸。这些支撑部件148在第二方向a2上平行排列,并且沿着第一方向a1延伸。支撑部件148抵接长条1471与长条1472,并且自长条1471连续地延伸至长条1472。长条1471、长条1472、与支撑部件148界定出多个开口149,开口149暴露出半导体硬遮罩层130。

102.抵接长条1471和1472的多个支撑部件148配置以支撑长条1471与长条1472,从而防止长条1471与长条1472倒塌。由于刻蚀工艺在图案稀疏区中产生较大的刻蚀量,在没有形成支撑部件148的情况下,形成于选择晶体管预定区中的核心图案的宽度需要比形成于存储器单元预定区中的核心图案的宽度大,以避免在例如修整工艺期间或之后,选择晶体管预定区中的核心图案发生倒塌。由此,形成于选择晶体管预定区60中的第二核心图案146的长条1471与长条1472可形成具有与形成于存储器单元预定区50中的第一核心图案145相同的宽度,或者是比第一核心图案145更窄的宽度,这可增加后续形成选择栅极图案的光刻工艺的迭对容许度。

103.在一些实施例中,第二核心图案146的长条1471与长条1472沿着第一方向a1具有宽度d5,第一核心图案145沿着第一方向a1具有宽度d6,宽度d5对宽度d6的比值为约0.8至约1.0。若宽度d5对宽度d6的比值太小,则增加核心图案146倒塌的风险。若宽度d5对宽度d6的比值太大,则无法增加后续形成选择栅极图案的光刻工艺的迭对容许度。此外,在一些实施例中,由于刻蚀负载效应(loading effect),靠近图案稀疏区的长条1472的宽度d5可能会小于位于图案密集区的长条1471的宽度d5。

104.形成顺应层170沿着半导体硬遮罩层130的上表面、图案化核心层140’的侧壁、图案化抗反射层150’的侧壁及上表面,如图1c和图1c-1所示。顺应层170过量填充开口149。在一些实施例中,顺应层170由介电材料形成,例如,氧化硅、氮氧化硅、氮化硅、及/或其他适合的介电材料。

105.对半导体存储器结构100进行刻蚀工艺。刻蚀工艺移除顺应层170沿着半导体硬遮罩层130的上表面及图案化抗反射层150’上表面的部分,从而形成间隔物层170’于图案化核心层140’旁边,如图1d和图1d-1所示。在一些实施例中,刻蚀工艺是干刻蚀。图案化抗反射层150’可以在刻蚀工艺中被完全消耗,或是通过额外的刻蚀工艺移除。

106.间隔物层170’包含设置于第一核心图案145两侧的多对第一间隔物175、设置于第二核心图案146两侧的一对第二间隔物176、以及填充开口149的多个第三间隔物177。沿着长条1471形成的第二间隔物层以符号1761表示,而沿着长条1472形成的第二间隔物层以符号1762表示。根据一些实施例,由于刻蚀工艺的特性,第一间隔物175和第二间隔物176具有向上渐减的宽度。

107.第一间隔物175在第一方向a1上平行排列,并且沿着第二方向a2延伸。第二间隔物1761和1762在第一方向a1上平行排列,并且沿着第二方向a2延伸。第三间隔物层177彼此被支撑部件148隔开,并且在第二方向a2上排列。

108.在一些实施例中,第一间隔物175和第二间隔物1761和1762具有宽度d7,第三间隔物层177具有宽度d8。在一些实施例中,宽度d7对宽度d8的比值范围在约0.1至约1.0。

109.移除图案化核心层140’直到暴露出半导体硬遮罩层130,如图1e和图1e-1所示。在一些实施例中,刻蚀工艺是干刻蚀。由于长条1471/1472形成具有较窄的宽度,第二间隔物1761/1762与第三间隔物177之间的距离d9(即,第二核心图案1471/147的宽度d5)等于或小于第一间隔物175之间的距离d10(即,第一核心图案145的宽度d6),这可增加后续形成选择栅极图案的光刻工艺的迭对容许度。在一些实施例中,距离d9对距离d10的比值范围在约0.8至约1.0。若距离d9对距离d10的比值太大,则无法增加后续形成选择栅极图案的光刻工艺的迭对容许度。

110.依序形成填充层180、抗反射层182、以及图案化光阻层190于半导体存储器结构100之上,如图1f和图1f-1所示。填充层180覆盖间隔物层170’,并且填充移除图案化核心层140’所形成的间隙。在一些实施例中,填充层180由富碳材料形成,例如,旋涂碳(soc)或碳层。在一些实施例中,抗反射层182由富硅材料形成,例如,氮氧化硅(sion)。

111.图案化光阻层190包含设置于选择晶体管预定区60中的光阻图案192。光阻图案192设置于第二间隔物1761和1762以及第三间隔物177的正上方,且将其覆盖。在一些实施例中,光阻图案192在图案密集区处的侧壁(边缘)192a的延伸线e1-e1对准(例如,通过)第二间隔物1761。也就是说,在图1f-1的平面图中,光阻图案192的侧壁192a位于第二间隔物1761的区域内。在一些实施例中,光阻图案192在图案稀疏区处的另一侧壁(边缘)192b的延伸线e2-e2对准(例如,通过)第二间隔物1762。也就是说,在图1f-1的平面图中,光阻图案192的侧壁192b位于第二间隔物1762的区域内。

112.通过形成第二核心图案146的支撑部件148(图1b-1),使第二核心图案146的长条1471与长条1472能形成具有较窄的宽度d5,从而降低第二间隔物1761/1762与第三间隔物177之间的距离d9(图1e-1)。由此,第二核心图案146(包含第二间隔物1761/1762与第三间隔物177)在选择晶体管预定区60中的覆盖率(即,面积占比)得以提高,这降低了光阻图案192与第二间隔物1761/1762的错位的可能性,例如,光阻图案192侧壁192a(或192b)的延伸线e1-e1(或e2-e2)未通过第二间隔物1761(或1762)。若光阻图案192与第二间隔物1761/1762错位,可能会造成后续形成的选择栅极遭遇图案失效(pattern fail)问题。

113.因此,本发明实施例利用形成第二核心图案146的支撑部件148来增加形成图案化光阻层190的光刻工艺的迭对容许度。光刻工艺迭对的规格/管制限制(specification/control limit)得以舒缓,进而降低生产成本且提高产品良率。

114.使用图案化光阻层190以及间隔物层170’,对半导体存储器结构100进行刻蚀工艺,以依序刻蚀移除抗反射层182、填充层180、以及半导体硬遮罩层130未被图案化光阻层190与间隔物层170’覆盖的部分,直到暴露出介电硬遮罩层120的上表面,如图1g和图1g-1所示。在一些实施例中,刻蚀工艺是干刻蚀。刻蚀工艺之后的半导体硬遮罩层130标示为图案化半导体硬遮罩层130’。第一间隔物175的图案转移至半导体硬遮罩层130,以形成硬遮罩图案135,图案化光阻层190的光阻图案192与第二间隔物1761/1762的图案共同转移至半导体硬遮罩层130,以形成硬遮罩图案136。图案化光阻层190和抗反射层182也可在刻蚀工艺中被完全消耗,或是通过额外的工艺移除。填充层180的剩余部分标示为填充层180’。此外,未被光阻图案192覆盖的第一间隔物175在刻蚀工艺中可能会被部分消耗。

115.使用图案化半导体硬遮罩层130’,对半导体存储器结构100进行刻蚀工艺,以刻蚀介电硬遮罩层120未被图案化半导体硬遮罩层130’覆盖的部分,直到暴露出主动层110的上表面,如图1h和图1h-1所示。在一些实施例中,刻蚀工艺是干刻蚀。刻蚀工艺之后的介电硬遮罩层120标示为图案化介电硬遮罩层120’。图案化半导体硬遮罩层130’的硬遮罩图案135和136转移至介电硬遮罩层120,使得介电硬遮罩层120分别形成硬遮罩图案125和126。填充层180’以及间隔物层170’也可在刻蚀工艺中被移除,或者可通过额外刻蚀工艺移除。

116.使用图案化介电硬遮罩层120’,对半导体存储器结构100进行刻蚀工艺,以刻蚀主动层110未被图案化介电硬遮罩层120’覆盖的部分,直到暴露出穿隧氧化物层103,如图1i所示。刻蚀工艺包含针对各种材料层的多道刻蚀步骤。刻蚀工艺之后的介电硬遮罩层120标

示为介电硬遮罩层120’。图案化介电硬遮罩层120’的硬遮罩图案125和硬遮罩图案126转移至主动层110,使得主动层110分别形成栅极堆迭115于存储器单元预定区50中、以及栅极堆迭116于选择晶体管预定区60中。在一些实施例中,可形成额外的部件(例如,源极/漏极区)于半导体存储器结构100之上,以制得半导体存储器装置,例如反及型快闪存储器(nand flash memory)。

117.栅极堆迭115用于形成快闪存储器装置的存储器单元,其中,第一多晶硅层104和第二多晶硅层105配置为存储器单元的浮置栅极;第三多晶硅层107和第四多晶硅层108配置为存储器单元的控制栅极,并且兼作为存储器单元的字元线。栅极堆迭116用于形成选择晶体管。

118.本发明实施例利用形成第二核心图案146的支撑部件148来增加形成图案化光阻层190的光刻工艺的迭对容许度。因此,可舒缓光刻工艺迭对的规格/管制限制,进而降低生产成本且提高产品良率。

119.图2a、图2b、图2c和图2a-1是根据本发明的一些实施例,绘示形成半导体存储器结构200在不同阶段的示意图,其中图2a是沿着图2a-1的平面示意图中的线i-i撷取的剖面示意图。相同于前述图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i的实施例的部件使用相同的标号并省略其说明。图2a、图2b、图2c的半导体存储器结构200与图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i的半导体存储器结构100大致相似,除了光阻图案192与第二间隔物1761/1762的错位。

120.接续图1e,依序形成填充层180、抗反射层182、以及图案化光阻层190于半导体存储器结构200之上,如图2a和图2a-1所示。图案化光阻层190包含设置于选择晶体管预定区60中的光阻图案192。光阻图案192覆盖第二间隔物1761,但未覆盖第二间隔物1762。在一些实施例中,光阻图案192的侧壁192a的延伸线e1-e1未通过第二间隔物1761。也就是说,在图2a-1的平面图中,光阻图案192的侧壁192a位于第二间隔物1761的区域外。在一些实施例中,光阻图案192的另一侧壁192b的延伸线e2-e2未通过第二间隔物1762。也就是说,在图2a-1的平面图中,光阻图案192的侧壁192b位于第二间隔物1762的区域外。

121.对半导体存储器结构200进行前述图1g所述的步骤,从而形成图案化半导体硬遮罩层130’,如图2b所示。由于光阻图案192未覆盖第二间隔物1762,在填充层180’与第二间隔物1762之间,形成缺口202于硬遮罩图案136的上表面处。根据本发明实施例,通过形成第二核心图案146的支撑部件148(图1b-1),使第二核心图案146的长条1471与长条1472能形成具有较窄的宽度d5,从而降低第二间隔物1761与第三间隔物177之间的距离d9(第1e-1图)。由此,形成于硬遮罩图案136的上表面处的缺口202也可具有较小的尺寸。

122.对半导体存储器结构200进行前述图1h所述的刻蚀工艺,从而形成图案化介电硬遮罩层120’,如图2c所示。因为较小的尺寸的缺口202,降低刻蚀工艺将缺口202延伸至遮罩图案126的可能性。若缺口延伸至介电硬遮罩层的遮罩图案,可能会造成后续形成的选择栅极遭遇图案失效(pattern fail)问题。因此,光刻工艺迭对的规格/管制限制得以舒缓,进而降低生产成本且提高产品良率。

123.图3a和图3b以及图3b-1是根据本发明的一些实施例,绘示形成半导体存储器结构300在不同阶段的示意图,其中图3b是沿着图3b-1的平面示意图中的线i-i撷取的剖面示意图。相同于前述图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i的实施例的部件使用相

同的标号并省略其说明。图3a和图3b的半导体存储器结构300与图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i的半导体存储器结构100大致相似,除了第三间隔物177。

124.接续图1b,形成顺应层170于半导体存储器结构300之上,如图3a所示。顺应层170形成于开口149的侧壁和底面,以部分填充开口149。

125.对半导体存储器结构300进行前述图1d和图1e所述的步骤,从而形成间隔物层170’并移除图案化核心层140’,如图3b和图3b-1所示。根据一些实施例,间隔物层170’包含第二间隔物1761和1762、以及部分填充开口149的多个第三间隔物177。由于顺应层170形成于开口149底面的部分被移除,第三间隔物177具有暴露出半导体硬遮罩层130的开口302。由此,在图3b-1的平面图中,第三间隔物177呈封闭环形轮廓。

126.图4a-1、图4b-1、图4c-1是根据本发明的一些实施例,绘示形成半导体存储器结构400在不同阶段的平面示意图。相同于前述图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i的实施例的部件使用相同的标号并省略其说明。图4a-1、图4b-1、图4c-1的半导体存储器结构400与图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i的半导体存储器结构100大致相似,除了第三间隔物177。

127.根据一些实施例,图4a-1显示图案化光阻层160的第一光阻图案165和第二光阻图案166,第二光阻图案166的连接部件168在第二方向d2的宽度自长条1671和1672朝向连接部件168的中心渐减,使得开口169可具有似六角形轮廓。

128.对半导体存储器结构400进行图1b所述的步骤,从而形成图案化核心层140’,如图4b-1所示。在经过修整工艺之后,图案化核心层140’的支撑部件148在中心处会断开,并且成为彼此隔开的支撑部1481与支撑部1482。支撑部1481抵接长条1471,而支撑部1482抵接长条1472。开口149彼此连接。

129.对半导体存储器结构400进行前述图3b所述的步骤,从而形成间隔物层170’并移除图案化核心层140’,如图4c-1所示。间隔物层170’包含设置于第二间隔物1761和1762、以及部分填充开口149的多个第三间隔物177,这些第三间隔物177彼此连接,并且各自具有暴露出半导体硬遮罩层130的开口302。

130.根据前述,本发明实施例利用形成第二核心图案的支撑部件,来增加形成选择栅极图案的光刻工艺的迭对容许度。因此,光刻工艺迭对的规格/管制限制得以舒缓,进而降低生产成本且提高产品良率。

131.以上概述数个实施例的部件,以便在本领域技术人员可以更加理解本发明实施例的观点。本领域技术人员应理解,他们能轻易地以本发明实施例为基础,设计或修改其他工艺和结构,以达到与在此介绍的实施例相同的目的及/或优势。本领域技术人员也应理解,此类等效的结构并无悖离本发明的精神与范围,且他们能在不违背本发明的精神和范围下,做各式各样的改变、取代和替换。因此,本发明的保护范围当视前附的权利要求书所界定为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1