功率半导体元件及其制造方法与流程

1.本技术涉及一种功率电子元件及其制造方法,特别是一种功率半导体元件及其制造方法。

背景技术:

2.日常生活中,各行各业所使用的家电用品和机械设备都具有供应其运转的电力系统,而在电力的传输和使用过程中必须使用功率电子元件进行功率转换,以控制电力系统中瞬间加压的电流稳定度。

3.功率半导体元件由于具备较高的输入阻抗、较低的驱动功率、较低的导通电阻值、较快的切换速度、较低的切换损耗及较宽的安全操作区间(safe of operation area,soa),且适合与集成电路制程整合形成功率集成电路,因此常被应用于消费电子产品(例如,mp3播放器、数码相机、笔记本电脑、智能手机等便携式电子产品)的功率传换系统中。

4.功率半导体元件,例如功率金属氧化物-半导体晶体管元件(power metal-oxide-semiconductor transistor),以根据电流流通路径来加以分类,可区分为平面式结构和垂直式结构。由于平面式结构在承受高电压与高电流的操作环境时,需要较宽的通道来容纳较多的电流以降低导通电阻(on-resistance),会相对地占据较多的集成电路面积。而垂直式结构因为通道宽度为外延层的厚度,可通过增加外延层的厚度来增加单位集成电路面积的可导通电流。随着集成电路的微缩化,目前已成为功率金属氧化物-半导体晶体管元件的主流。

5.典型的垂直式结构功率金属氧化物-半导体晶体管元件(例如,n型通道的垂直式双扩散(vertical double-diffused)功率金属氧化物-半导体晶体管元件)包括基材(漏极)、位于基材上方的n型外延层、两个位于n型外延层中且彼此分离的p型阱区,两个分别由n型外延层的上表面向下延伸进入两个p型阱区的两个n型源极掺杂区,以及位于n型外延层上且邻接n型源极掺杂区的栅极结构。

6.由于垂直式结构的功率金属氧化物-半导体晶体管元件的漏极和源极之间存在一个寄生的接面场效晶体管(junction gate field-effect transistor,jfet)。当进行顺向操作而对漏极施予正电压时,顺向偏压使大量的空穴穿过p型阱区和n型外延层之间的pn接面注入n型外延层。当进行反向操作而对漏极施予反向偏压时,由于电子不再由源极射入,累积在pn接面的少数载子(空穴),需要先与相反电荷(电子)复合(recombination),方能使元件关闭。因此电流不会立即降至零值,而需要一段反向恢复时间(reverse recovery)才能进行功率转换,造成垂直式结构的功率金属氧化物-半导体晶体管元件在高频操作环境的限制。

7.因此,有需要提供一种先进的功率半导体元件及其制造方法,来解决现有技术所面临的问题。

技术实现要素:

8.本说明书的一实施例,是公开一种功率半导体元件,此功率半导体元件包括:具有第一电性的外延层、第一阱区、第二阱区、浮置(floating)掺杂区、第一掺杂区、第二掺杂区和栅极结构。第一阱区和第二阱区具有第二电性,分别由外延层的表面延伸进入该外延层,且第一阱区和第二阱区彼此分离。浮置掺杂区具有第二电性,位于外延层中,第一阱区和第二阱区之间,且与第一阱区和第二阱区分离。第一掺杂区和第二掺杂区具有第一电性,分别由外延层的表面延伸进入第一阱和第二阱区之中。栅极结构位于外延层上,邻接第一掺杂区和第二掺杂区,且与浮置掺杂区至少部分重叠。

9.本说明书的另一实施例,是公开一种功率半导体元件,此功率半导体元件包括:具有第一电性的外延层、第一阱区、第二阱区、浮置掺杂区和金属电极。第一阱区和第二阱区具有第二电性,分别由外延层的表面延伸进入该外延层,且第一阱区和第二阱区彼此分离。浮置掺杂区具有第二电性,位于外延层中,第一阱区和第二阱区之间,且与第一阱区和第二阱区分离。金属电极位于外延层上,与第一阱区和第二阱区分别形成一个成金属-半导体接面。

10.本说明书的又一实施例,是公开一种功率半导体元件的制作方法,此功率半导体元件的制作方法包括下述步骤:首先提供一个具有第一电性的外延层;并于外延层中形成一个具有第二电性的浮置掺杂区。之后,于外延层上形成一个栅极结构,并与浮置掺杂区至少部分重叠。于外延层中形成彼此分离且具有第二电性的第一阱区和第二阱区,由外延层的表面延伸进入外延层,使浮置掺杂区位于第一阱区和第二阱区之间,且与第一阱区和第二阱区分离。再形成具有第一电性的第一掺杂区和第二掺杂区,分别由外延层的表面延伸进入第一阱区和第二阱区,并且邻接栅极结构。

11.根据上述实施例,本说明书是提供一种功率半导体元件及其制造方法,是在具有第一电性的外延层中形成至少一个具有垂直通道和npn寄生双极性接面的晶体管单元或金属-半导体接面二极管单元。并在外延层中配置具有第二电性的浮置掺杂区来改变晶体管/二极管单元中的垂直电场分布。当晶体管单元/二极管进行反向操作时,能促进电子自漏极注入漏极和源极之间存的寄生pn接面,使电子与累积在pn接面的少数载子复合。可在不改变额定的操作电压的情况下,缩短关闭场效晶体管单元所需要的反向恢复时间,利于功率半导体元件的高频操作。

附图说明

12.为让本发明的上述特征和优点能更明显易懂,下文特举实施例作详细说明如下。但必须注意的是,这些特定的实施案例与实施方式,并非用以限定本发明。本发明仍可采用其他特征、元件、方法及参数来加以实施。优选实施例的提出,仅是用以例示本发明的技术特征,并非用以限定本发明的权利要求。

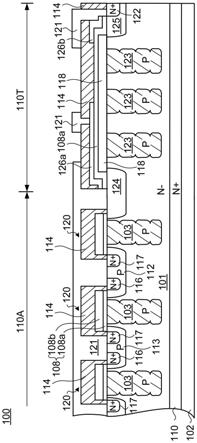

13.图1a至图1f是根据本说明书的一实施例所示出的制作功率半导体元件的一系列制程结构剖面示意图;

14.图2是根据本说明书的另一实施例所示出的功率半导体元件结构剖面示意图;

15.图3a至图3f是根据本说明书的多个实施例所分别示出具有不同结构的浮置掺杂区的功率半导体元的结构剖面示意图;

16.图4a至图4d是根据本说明书的又一实施例所示出的制作功率半导体元件的部分制程结构剖面示意图;

17.图5a至图5e是根据本说明书的再一实施例所示出的制作功率半导体元件的部分制程结构剖面示意图;

18.图6是根据本说明书的又另一实施例所示出的功率半导体元件的结构剖面示意图;

19.图7a至图7d是根据本说明书的又另一实施例所示出的功率半导体元件的结构剖面示意图;

20.图8是根据本说明书的又再一实施例所示出的功率半导体元件的结构剖面示意图;以及

21.图9是针对图4d所提供的功率半导体元件以及现有的超接面金属氧化物-半导体晶体管单元进行反向恢复测试所得到的反向截止电流与反向截止时间的关系曲线图。

具体实施方式

22.本说明书是提供一种功率半导体元件及其制作方法,可在不改变额定的操作电压的情况下,可有效缩短元件切换操作时的反向电流与功率耗损,且有助于在元件因切换而关闭时提高元件的临界电压。以下将提出多个实施例,并参考后附附图来进行说明。在附图中,相同或相似的元件符号用来表示相似或均等的元件。且附图仅是为了例示,其并未按照比例示出。以下实施方式仅针对本发明的有限的范围和实施方式进行例示说明。

23.在一些实施例中,步骤的进行或构件的组装顺序,可以与例示的实施例相同或不同。此外,并非所有例示的步骤或构件都是实施本发明所必需的。

24.请参照图1a至图1f,图1a至图1f是根据本说明书的一实施例所示出的制作功率半导体元件100的一系列制程结构剖面示意图。制作功率半导体元件100的方法包括下述步骤:首先,提供一个具有第一电性的外延层101,并于外延层101中形成至少一个具有第二电性的浮置掺杂区103。

25.在本说明书的一些实施例之中,外延层101的形成,可以包括以外延沉积制程,在具有n型掺质的半导体基底层110上成长具有n型掺质(例如,砷、磷、锑等五价原子)的半导体外延层101,然后再形成浮置掺杂区103。而在本说明书的一些实施例之中,浮置掺杂区103与外延层101可以通过一个多层外延制程同时形成于半导体基底层110之上。

26.在本实施例中,半导体基底层110可以是碳化硅层。半导体基底层110可以区分为至少一个主动区110a以及一个位于主动区外侧的终端区110t(但不以此为限,例如,在一些实施例中,可以不包含终端区110t)。

27.制作外延层101和浮置掺杂区103的多层外延制程,包括下述步骤:首先,于半导体基底层110上方形成一个具有n电性的第一外延薄膜101a;再以图案化光阻(未示出)遮罩一部分的第一外延薄膜101a,并进行离子植布制程104,将具有p型电性的掺质(例如,铝、硼、镓等三价原子)植入第一外延薄膜101a,借此在主动区110a上方的第一外延薄膜101a中形成多个具有p型电性的第一离子植布区域103a;且在主终端区110t上方的第一外延薄膜101a中形成多个具有p型电性的离子植布区域123a(如图1a所示)。

28.接着,于第一外延薄膜101a上方形成一个具有n电性的第二外延薄膜101b;再以图

案化光阻(未示出)遮罩一部分的第二外延薄膜101b,并进行离子植布制程105,将具有p型电性的掺质植入第二外延薄膜101b中,借此在主动区110a上方的第二外延薄膜101b中形成具有p型电性的第二离子植布区域103b,使第二离子植布区域103b与第一离子植布区域103a至少部分重叠,但彼此分离;且在终端区110t上方的第二外延薄膜101b中形成具有p型电性的离子植布区域123b,使离子植布区域123b分别与离子植布区域123a至少部分重叠,但彼此分离。

29.后续,重复用来形成第二离子植布区域103b和离子植布区域123b的步骤,借此于多晶硅基底层110上形成多个相互堆叠的外延薄膜,并在这些外延薄膜中形成多个彼此重叠的离子植布区域,以完成浮置掺杂区103与外延层101的制备。在本说明书的一些实施例中,构成外延层101的材料可以与构成半导体基底层110的材料相同或不同。在本实施例中,构成外延层101中n型掺质的掺杂浓度(n-),实质上低于半导体基底层的材料都包括碳化硅110中n型掺质的掺杂浓度(n+)。

30.在本实施例中,外延层101中可以包括(但不以此为限)相互重叠的第一外延薄膜101a、第二外延薄膜101b、第三外延薄膜101c和第四外延薄膜101d;且位于主动区110a上方的第一外延薄膜101a、第二外延薄膜101b、第三外延薄膜101c和第四外延薄膜101d的每一者中,分别包括尺寸和掺杂浓度相同或不同,且彼此分离的第一离子植布区域103a、第二离子植布区域103b、第三离子植布区域103c和第四离子植布区域103d。位于终端区110t上方的第一外延薄膜101a、第二外延薄膜101b、第三外延薄膜101c和第四外延薄膜101d的每一者中,分别包括尺寸和掺杂浓度相同或不同,且彼此分离的多组离子植布区域123a、123b、123c和123d)(如图1b所示出)。

31.值得注意的是,在本说明书的一些实施例中,形成每一个外延薄膜之后,并不一定要在该层外延薄膜中形成离子植布区域。制作外延层101和浮置掺杂区103的过程中,可以视需要省略至少一次离子植布制程。另外,每一次离子植布制程所植入掺质浓度和掺质的植入深度以及所形成的离子植布区域的面积并无限制。换言之,在形成每一次离子植布制程所形成的离子植布区域,其深度、宽度、面积范围以及掺杂浓度可以相等或不相同,且上下相邻的二离子植布区域可以彼此分离或者彼此接触。

32.然后,以一热氧化制程106外延层101上形成一硅氧化物层118,并加以图案化,使其覆盖于终端区110t的外延层101上。借此进一步驱动第一离子植布区域103a、第二离子植布区域103b、第三离子植布区域103c、第四离子植布区域103d中的p型电性的掺质,向外扩散以扩大范围,进一步彼此连接,以于主动区110a上的外延层101中形成多个浮置掺杂区103;并且驱动离子植布区域123a、123b、123c和123d中的p型电性的掺质,向外扩散以扩大范围,进一步彼此连接,以于终端区110t上的外延层101中形成多个浮置掺杂区123(如图1c所示出)。

33.接着,于主动区110a上方的外延层101上形成多个栅极结构108,使栅极结构108与浮置掺杂区103至少部分重叠。在本实施例中,栅极结构108的形成包括:先外延层101的表面101s形成一个介电层之后再于主动区110a上方依续形成另一个介电层和一个导电层(未示出),并以光阻蚀刻制程106图案化于主动区110a上方的介电层和导电层,进而在主动区110a上方的外延层101的表面101s上形成一个由介电层108a(包含一部分的介电层118)和闸电极108b所组成的堆叠结构,并对准浮置掺杂区103。在本说明书的一些实施例中,栅极

结构108可以只和浮置掺杂区103部分重叠。

34.另外,形成多个栅极结构108的同时,也可以在终端区110t和过渡区之中形成至少一个内连线126a或焊垫126b,并且使内连线126a或焊垫126b通过硅氧化物层118和介电层108a与外延层101电性隔离。

35.再以栅极结构108为罩幕,进行离子植入制程109,于主动区110a上的外延层101中形成彼此分离且具有p型电性的第一阱区112和第二阱区113,由外延层101的表面101s延伸进入外延层101中,使浮置掺杂区103位于第一阱区112和第二阱区113之间,且与第一阱区112和第二阱区113分离;在终端区110t和主动区110a之间的过渡区(transition region)上方的外延层101中形成具有p型电性的掺杂阱区124;并且在终端区110t的边缘形成一个具有p型电性,环绕功率半导体元件100的掺杂阱区125(如图1c所示出)。

36.形成第一阱区112、第二阱区113掺杂阱区124和125之后,以一个图案化的光阻层107,覆盖于一部分的终端区110t以及一部分的第一阱区112和第二阱区113上;再以光阻层107和栅极结构108为罩幕,进行另一次离子植入制程115,借此在主动区110a中形成具有n型电性的第一掺杂区116和第二掺杂区117,分别由外延层101的表面101s向下延伸进入第一阱区112和第二阱区113,并且邻接于栅极结构108;并在终端区110t中形成具有n型电性的掺杂区122由外延层101的表面101s向下延伸进入掺杂阱区125(如图1e所示出)。在本说明书的一些实施例中,第一掺杂区116和第二掺杂区117中n型掺质的掺杂浓度(n+),实质上高于外延层101中n型掺质的掺杂浓度(n-)。

37.在本实施例中,邻接于每一个栅极结构108的第一阱区112、第二阱区113、第一掺杂区116和第二掺杂区117,以及位栅极结构108下方的浮置掺杂区103、一部分的外延层101和一部分的半导体基底层110,可以组成一个具有垂直式结构的功率金属氧化物-半导体晶体管单元120(晶胞(cell))。其中,邻接于栅极结构108的第一掺杂区116和第二掺杂区117,可以作为功率金属氧化物-半导体晶体管单元120的源极;位于栅极结构108下方的一部分外延层101,可以作为双扩散功率金属氧化物-半导体晶体管单元120的通道层;位于栅极结构108下方的一部分半导体基底层110和漏极金属层102(漏极金属层102此时尚未形成,请参见图1f),可以作为双扩散功率金属氧化物-半导体晶体管单元120的漏极。

38.后续进行后段制程,在外延层101上方形成图案化的介电层114覆盖在终端区110t和栅极结构108上,并于介电层114上形成图案化的金属接触层121,一部分与双扩散功率金属氧化物-半导体晶体管元件120的源极(第一掺杂区116和第二掺杂区117)接触,并将多个功率金属氧化物-半导体晶体管单元120加以并联,以于主动区110a上形成一个双扩散功率金属氧化物-半导体晶体管阵列。之后,再以薄化制程移除一部分的半导体基底层110,并采用例如,沉积或表面键合技术,将漏极金属层102形成在被薄化半的导体基底层110相对于外延层101的另外一侧,完成功率半导体元件100的制备(如图1f所示出)。

39.另外,在本说明书的一些实施例中,一部分的图案化金属接触层121覆盖于终端区110t上,并且分别与内连线126a和掺杂区122电性接触,有利于提高功率半导体元件100的临界电压。在本说明书的一实施例中,和内连线126a电性接触的一部分图案化金属接触层121可以(通过)连接至闸电极108b。另外,和掺杂区122电性接触的一部分图案化金属接触层121,可以通过浮接(floating)而在终端区110t的边缘形成一个通道阻绝(channel stop)板。可以防止功率半导体元件100反向截止时,电场往外延伸扩张,有利于功率半导体

元件100崩溃电压的调控。

40.嵌设于每一个双扩散功率金属氧化物-半导体晶体管单元120的浮置掺杂区103,因为具有与通道(外延层101)相反的电性,并且向下延伸接近功率金属氧化物-半导体晶体管元件120的漏极(漏极金属层102),可以有效分散电场。在功率金属氧化物-半导体晶体管单元120从顺向操作切换成负向操作的过程中,由于电路上其他被动元件所造成的逆向电流会从功率金属氧化物-半导体晶体管单元120的源极往漏极流动,借此关闭功率金属氧化物-半导体晶体管单元120;当功率金属氧化物-半导体晶体管单元120由关闭状态切换成逆向操作时,原本在寄生在功率金属氧化物-半导体晶体管单元120中的二极管内的载子,因电压极性转换而流出形成逆向电流。浮置掺杂区103可让功率金属氧化物-半导体晶体管单元120中的寄生二极管内的载子与逆向电流减少,进而有效缩短反向电流与功率耗损,利于功率金属氧化物-半导体晶体管单元120的切换操作,有效缩短反向恢复时间,利于功率半导体元件100的高频操作。同时,浮置掺杂区103可在元件切换关闭时,在外延层101扩张更多的空乏区,有助于提高功率金属氧化物-半导体晶体管单元120的临界电压。

41.请参照图2,图2是根据本说明书的另一实施例所示出的功率半导体元件200的结构剖面示意图。其中,功率半导体元件200的结构大致与图1f所示出的功率半导体元件100类似。主要差别在于:功率半导体元件200的主动区还包括一个位于外延层101中,具有p型电性的第三掺杂区218和第四掺杂区219,且分别与第一阱区112和第二阱区113连接,使浮置掺杂区103位于第三掺杂区218和第四掺杂区219之间。由于功率半导体元件200终端区的结构与图1f所示出的结构实质相似,且制作方法已详述如上,因此省略不加以赘述。

42.在本实施例中,第三掺杂区218和第四掺杂区219,是与浮置掺杂区103和外延层101采用同一个多层外延制程(如图1a至图1b所示出)所同时形成的。其中,构成第三掺杂区218和第四掺杂区219的离子植布区域,除了掺杂的位置与构成浮置掺杂区103的第一离子植布区域103a、第二离子植布区域103b、第三离子植布区域103c和第四离子植布区域103d有所不同外,其余的制程步骤与参数,与制作浮置掺杂区103的方法相同,因此不再此赘述。

43.但是值得注意的是,虽然在本实施例中,第三掺杂区218和第四掺杂区219中p型掺质的掺杂浓度(p),实质上等于浮置掺杂区103中p型掺质的掺杂浓度(p)。但用来构成第三掺杂区218和第四掺杂区219的各个离子植布区域的位置、尺寸和p型掺质的浓度并不以此为限。在形成第三掺杂区218和第四掺杂区219的过程中,可根据功率半导体元件200的实际制程条件与元件需求,调整多层外延制程中各个离子植入制程的参数,借此改变第三掺杂区218和第四掺杂区219中各个离子植布区域的位置、尺寸和p型掺质的浓度。

44.如图2所示出,每一个栅极结构108与相互邻接的第一阱区112、第二阱区113、第一掺杂区116和第二掺杂区117,以及位于栅极结构108下方的浮置掺杂区103、一部分的外延层101、一部分的、第三掺杂区218和第四掺杂区219可以组成一个具有垂直式结构的超接面(super junction)金属氧化物-半导体晶体管单元220。

45.嵌设于每一个超接面金属氧化物-半导体晶体管单元220的第三掺杂区218、第四掺杂区219和浮置掺杂区103,因为具有与通道(外延层101)相反的电性,并且向下延伸接近超接面金属氧化物-半导体晶体管元件220的漏极(漏极金属层102),可以有效分散电场。在超接面金属氧化物-半导体晶体管单元220从顺向操作切换成负向操作的过程中,由于电路上其他被动元件所造成的逆向电流会从超接面金属氧化物-半导体晶体管单元220的源极

往漏极流动,借此关闭超接面金属氧化物-半导体晶体管单元220。随后,当超接面金属氧化物-半导体晶体管单元220由关闭状态切换成逆向操作时,原本在寄生在超接面金属氧化物-半导体晶体管单元220中的二极管内的载子,因电压极性转换而流出形成逆向电流。浮置掺杂区103可让超接面金属氧化物-半导体晶体管单元220中的寄生二极管内的载子与逆向电流减少,进而有效缩短反向电流与功率耗损,利于超接面金属氧化物-半导体晶体管单元220的切换操作,有效缩短反向恢复时间,利于功率半导体元件200的高频操作。同时,浮置掺杂区103可在元件切换关闭时在外延层101中扩张更多的空乏区,有助于提高超接面金属氧化物-半导体晶体管单元220的临界电压。

46.请参照图3a至图3f,图3a至图3f是根据本说明书的多个实施例所分别示出具有不同结构的浮置掺杂区303的功率半导体元300a、300b、300c、300d、300e和300f的结构剖面示意图。其中,功率半导体元件300a、300b、300c和300d的结构大致与图2所示出的功率半导体元件200类似,主要差别主要在于构成功率半导体元件300a、300b、300c、300d、300e和300f的浮置掺杂区303的第一离子植布区域303a、第二离子植布区域303b、第三离子植布区域303c和第四离子植布区域303d排列方式有所不同。由于功率半导体元件300a、300b、300c、300d、300e和300f终端区的结构与图1f所示出的结构实质相似,且制作方法已详述如上,因此省略不加以赘述。

47.如图3a所示出,在功率半导体元件300a中,构成浮置掺杂区303的第一离子植布区域303a、第二离子植布区域303b、第三离子植布区域303c和第四离子植布区域303d彼此分离,且第四离子植布区域303d与栅极结构108的介电层108a直接接触。在图3b中,功率半导体元件300b省略了第四离子植布区域303d,其余的第一离子植布区域303a、第二离子植布区域303b和第三离子植布区域303c三者彼此分离。

48.在图3c中,下方的第一离子植布区域303a和第二离子植布区域303b彼此连接;且下方的相连区域与上方的第三离子植布区域303c和第四离子植布区域303d三者彼此分离;其中第四离子植布区域303d与介电层108a直接接触。在图3d中,上方的第三离子植布区域303c和第四离子植布区域303d彼此连接,且上方的相连的区域与下方的第一离子植布区域303a和第二离子植布区域303b三者彼此分离;其中第四离子植布区域303d与介电层108a直接接触。

49.在图3e中,下方的第一离子植布区域303a和第二离子植布区域303b彼此连接;上方的第三离子植布区域303c和第四离子植布区域303d彼此连接,但上下两个连接区域彼此分离;其中第四离子植布区域303d与介电层108a直接接触。在图3f中,第一离子植布区域303a、第二离子植布区域303b、第三离子植布区域303c和第四离子植布区域303d四者彼此连接,且四者皆未与介电层108a直接接触。

50.请参照图4a至图4d,图4a至图4d是根据本说明书的又一实施例所示出的制作功率半导体元件400的部分制程结构剖面示意图。制作功率半导体元件400的方法,大致与制作功率半导体元件200的方法类似,主要差别在于制作浮置掺杂区403、第三掺杂区418和第四掺杂区419的方式有所不同。

51.在本实施例中,是采用深沟渠回填制程,在外延层401中制作浮置掺杂区403、第三掺杂区418和第四掺杂区419。所述的深沟渠回填制程包括下述步骤:首先,以外延沉积制程,例如物理气相沉积技术或化学气相沉积,在具有n型掺质(例如,砷、磷、锑等五价原子)

的半导体基底层110上成长一层外延层401(如图4a所示出)。其中,构成半导体基底层110和外延层401的材料可以包括碳化硅;且外延层401中n型掺质的掺杂浓度(n-)实质上低于多晶硅基底层110中n型掺质的掺杂浓度(n+)。半导体基底层110可以区分为至少一个主动区110a以及一个位于主动区外侧的终端区110t。

52.接着,以干式蚀刻制程411,在外延层401中形成多个条深沟渠401a,由外延层401表面401s延伸进入外延层401中(如图4b所示出)。之后,进行沉积制程(例如物理气相沉积技术或化学气相沉积)在多晶硅外延层401表面401s形成具有p型掺质的多晶硅材料,并填满深沟渠401a。再以外延层401表面401s为停止层,进行平坦化,形成如图4c所示出的结构。其中,位于主动区110a深沟渠401a中的p型沉积结构,可以分别作为功率半导体元件400的浮置掺杂区403、第三掺杂区418和第四掺杂区419。位于终端区110t深沟渠401a中的p型沉积结构可以包括位于终端区110t和主动区110a之间的过渡区中的至少一个p型沉积结构412,以及位于终端区110t中的其他p型沉积结构413。其中,p型沉积结构413为浮置。且p型沉积结构412和413的数量并不限制,有助于提升功率半导体元件400的临界电压。

53.后续,于主动区110a上的外延层401上方形成栅极结构108;于主动区110a上的外延层401中形成彼此分离且具有p型电性的第一阱区112和第二阱区113;在终端区110t和主动区110a之间的过渡区上方的外延层101中形成具有p型电性的掺杂阱区124,与一部分p型沉积结构412重叠;并且在终端区110t的边缘形成一个具有p型电性,环绕功率半导体元件100的掺杂阱区125;并且在第一阱区112、第二阱区113和掺杂阱区125中分别形成具有n型电性的第一掺杂区116、第二掺杂区117和掺杂区122。

54.其中,每一个栅极结构108与相互邻接的第一阱区112、第二阱区113、第一掺杂区116和第二掺杂区117,以及位于栅极结构108下方的浮置掺杂区403、一部分的外延层401、一部分的半导体基底层110、一部分的漏极金属层102(漏极金属层102此时尚未形成,请参见图4d)、第三掺杂区418和第四掺杂区419可以组成一个超接面金属氧化物-半导体晶体管单元420。后续,进行后段制程,并以薄化制程移除一部分的半导体基底层110,并在被薄化半的导体基底层110相对于外延层101的另外一侧形成漏极金属层102,完成一个具有超接面金属氧化物-半导体晶体管阵列的功率半导体元件400的制备(如图4d所示出)。

55.嵌设于每一个超接面金属氧化物-半导体晶体管单元420的第三掺杂区418、第四掺杂区419和浮置掺杂区403,因为具有与通道(外延层101)相反的电性,并且向下延伸接近超接面金属氧化物-半导体晶体管元件420的漏极(漏极金属层102),可以有效分散电场。在超接面金属氧化物-半导体晶体管单元420从顺向操作切换成负向操作的过程中,由于电路上其他被动元件所造成的逆向电流会从超接面金属氧化物-半导体晶体管单元420的源极往漏极流动,借此关闭超接面金属氧化物-半导体晶体管单元420。随后,当超接面金属氧化物-半导体晶体管单元420由关闭状态切换成逆向操作时,原本在寄生在超接面金属氧化物-半导体晶体管单420中的二极管内的载子,因电压极性转换而流出形成逆向电流。浮置掺杂区403可让超接面金属氧化物-半导体晶体管单元420中的寄生二极管内的载子与逆向电流减少,进而有效缩短反向电流与功率耗损,利于超接面金属氧化物-半导体晶体管单元420的切换操作,有效缩短反向恢复时间,利于功率半导体元件400的高频操作。同时,浮置掺杂区403可在元件切换关闭时在外延层101中扩张更多的空乏区,有助于提高超接面金属氧化物-半导体晶体管单元420的临界电压。

56.请参照图5a至图5e,图5a至图5e是根据本说明书的再一实施例所示出的制作功率半导体元件500的部分制程结构剖面示意图。制作功率半导体元件500的方法,大致与制作功率半导体元件400的方法类似,主要差别在于制作栅极结构508的方式有所不同。由于功率半导体元件500终端区的结构与图4d所示出的结构实质相似,且制作方法已详述如上,因此省略不加以赘述。

57.制作栅极结构508的方法包括下述步骤:首先在如图4c所示出的外延层401中形成一个沟槽508t由外延层401的表面401s向下延伸进入外延层401中,对准浮置掺杂区403,并与浮置掺杂区403至少部分重叠(如图5a所示出)。之后,形成一个介电层508a,覆盖沟槽508t的侧壁508s和底面508r;并于沟槽的中形成一个闸电极508b,通过介电层508a与外延层401电性隔离(如图5b所示出)。

58.然后,于外延层401中进行离子植入步骤511形成彼此分离且具有p型电性的第一阱区512和第二阱区513(如图5c所示出);并在第一阱区512和第二阱区513中分别形成具有n型电性的第一掺杂区516和第二掺杂区517(如图5d所示出)。

59.在本实施例中,每一个栅极结构508和与其邻接的第一阱区512、第二阱区513、第一掺杂区516和第二掺杂区517,以及位于此一栅极结构508下方的浮置掺杂区403、一部分的外延层101和一部分的半导体基底层110、一部分的漏极金属层102(漏极金属层102此时尚未形成,请参见图5e),可以组成一个具有沟槽式栅极结构(trench gate)的功率金属氧化物-半导体晶体管单元520。其中,邻接栅极结构508的第一掺杂区516和第二掺杂区517,可以作为沟槽式栅极功率金属氧化物-半导体晶体管单元520的源极;位于栅极结构508下方的一部分外延层101,可以作为沟槽式栅极功率金属氧化物-半导体晶体管单元520的通道层;位于栅极结构508下方的一部分半导体基底层110和一部分的漏极金属层102,可以作为沟槽式栅极功率金属氧化物-半导体晶体管单元520的漏极。

60.后续,再进行后段制程,在外延层401表面410s上形成层间介电层514,并在层间介电层514中形成接触金属层521,与沟槽式栅极功率金属氧化物-半导体晶体管单元520的源极(第一掺杂区516和第二掺杂区517)接触,并将多个沟槽式栅极功率金属氧化物-半导体晶体管单元520并联,从而形成一个沟槽式栅极功率金属氧化物-半导体晶体管阵列,并以薄化制程移除一部分的半导体基底层110,并采用例如,沉积或表面键合技术,将漏极金属层102形成在被薄化半的导体基底层110相对于外延层101的另外一侧,完成功率半导体元件500(如图5e所示出)的制备。

61.请参照图6,图6是根据本说明书的又另一实施例所示出的功率半导体元件600的结构剖面示意图。功率半导体元件600的结构,大致与功率半导体元件500类似,主要差别在于栅极结构608还包括一个分离栅极(split gate)。由于功率半导体元件600终端区的结构与图4d所示出的结构实质相似,且制作方法已详述如上,因此省略不加以赘述。

62.栅极结构608的制作包括:在如图5a所示出的沟槽508t中形成一个介电层608a,覆盖沟槽508t的侧壁508s和底部508r。于沟槽508t的底部508r形成一个分离闸电极608p,并通过介电层608a与外延层401电性隔离一个介电隔离层608d。于分离栅极608p的上方形成一个介电隔离层608d。于介电隔离层608d上方形成一个闸电极608b;通过介电隔离层608d使闸电极608b与分离栅极608p电性隔离;同时通过介电层608a使闸电极608b与外延层401电性隔离。

63.然后,于外延层401中进行离子植入步骤511,形成彼此分离且具有p型电性的第一阱区512和第二阱区513(如图5c所示出);并在第一阱区512和第二阱区513中分别形成具有n型电性的第一掺杂区516和第二掺杂区517(如图5d所示出)。后续进行后段制程,在外延层401表面410s上形成层间介电层514,并在层间介电层514中形成接触金属层521,与沟槽式栅极功率金属氧化物-半导体晶体管单元620的源极(第一掺杂区516和第二掺杂区517)接触,并将多个多个沟槽式栅极功率金属氧化物-半导体晶体管单元620并联,从而形成一个沟槽式栅极功率金属氧化物-半导体晶体管阵列,完成如图6所示出的功率半导体元件600的制备。

64.请参照图7a至图7d,图7a至图7d是根据本说明书的又另一实施例所示出的功率半导体元件700的结构剖面示意图。功率半导体元件700的结构,大致与功率半导体元件500类似,主要差别在于浮置掺杂区703、第三掺杂区718和第四掺杂区719的制作方法与结构有所不同。由于功率半导体元件700终端区的结构与图1f所示出的结构实质相似,且制作方法已详述如上,因此省略不加以赘述。

65.其中,浮置掺杂区703、第三掺杂区718和第四掺杂区719的制作方法包括下述步骤:首先,采用如图1a至图1b的步骤,在半导体基底层110上方,形成包含有(但不以此为限)相互重叠的第一外延薄膜101a、第二外延薄膜101b、第三外延薄膜101c和第四外延薄膜101d的外延层101。其中,第一外延薄膜101a、第二外延薄膜101b、第三外延薄膜101c和第四外延薄膜101d的每一者中,分别包括尺寸和掺杂浓度相同或不同,且彼此分离的第一离子植布区域103a、第二离子植布区域103b、第三离子植布区域103c和第四离子植布区域103d(如图1b所示出)。

66.之后,采用热氧化制程705,在外延层101的表面101s上形成一个硅氧化物薄膜701,借此驱动第一离子植布区域103a、第二离子植布区域103b、第三离子植布区域103c和第四离子植布区域103d中的p型电性的掺质进一步向下扩展,彼此连接,而分别在外延层101中形成多个浮置掺杂区703、第三掺杂区718和第四掺杂区719(如图7a所示出)。

67.然后,在外延层101中形成一个沟槽708t由外延层101的表面101s向下延伸进入外延层101中,对准浮置掺杂区703,并与浮置掺杂区703至少部分重叠。之后,形成一个闸介电层708a,覆盖沟槽708t的侧壁和底面;并于沟槽之中形成一个闸电极708b,通过闸介电层708a与外延层101电性隔离,以于每一个沟槽708t中形成栅极结构708(如图7b所示出)。

68.再于外延层101中进行离子植入步骤(未示出)形成彼此分离且具有p型电性的第一阱区712和第二阱区713;并在第一阱区712和第二阱区713中分别形成具有n型电性的第一掺杂区716和第二掺杂区717(如图7c所示出)。

69.在本实施例中,每一个栅极结构708和与其邻接的第一阱区712、第二阱区713、第一掺杂区716和第二掺杂区717,以及位于此一栅极结构708下方的浮置掺杂区703、一部分的外延层101和一部分的半导体基底层110、一部分的漏极金属层102(漏极金属层102此时尚未形成,请参见图7d),可以组成一个具有沟槽式栅极结构的功率金属氧化物-半导体晶体管单元720。其中,邻接栅极结构708的第一掺杂区716和第二掺杂区717,可以作为沟槽式栅极功率金属氧化物-半导体晶体管单元720的源极;位于栅极结构708下方的一部分外延层101,可以作为沟槽式栅极功率金属氧化物-半导体晶体管单元720的通道层;位于栅极结构708下方的一部分半导体基底层110和一部分的漏极金属层102,可以作为沟槽式栅极功

率金属氧化物-半导体晶体管单元520的漏极。

70.后续,再进行后段制程,在外延层101表面110s上形成层间介电层714,并在层间介电层714中形成接触金属层721,与沟槽式栅极功率金属氧化物-半导体晶体管单元720的源极(第一掺杂区716和第二掺杂区717)接触,并将多个沟槽式栅极功率金属氧化物-半导体晶体管单元720并联,从而形成一个沟槽式栅极功率金属氧化物-半导体晶体管阵列,并以薄化制程移除一部分的半导体基底层110,并采用例如,沉积或表面键合技术,将漏极金属层102形成在被薄化半的导体基底层110相对于外延层101的另外一侧,完成功率半导体元件700(如图7d所示出)的制备。

71.请参照图8,图8是根据本说明书的再另一实施例所示出的功率半导体元件800的结构剖面示意图。功率半导体元件800包括:基材110、具有n型电性的外延层801、第一阱区802、第二阱区803、柱状掺杂区807a和807b、浮置掺杂区804和金属电极层805。外延层801形成于基材101之上。第一阱区802和第二阱区803具有p型电性,分别由外延层801的表面801s延伸进入外延层801中,且第一阱区802和第二阱区803彼此分离。柱状掺杂区807a和807b位于外延层801中,第一阱区802和第二阱区803的下方,且分别与第一阱区802和第二阱区803连接。浮置掺杂区804也具有p型电性,位于外延层801中,第一阱区802和第二阱区803之间,且与第一阱区802和第二阱区803分离。金属电极层805位于外延层801上,与第一阱区802和第二阱区803分别形成一个成金属-半导体接面806a和806b。

72.请参照图9,图9是针对图4d所提供的功率半导体元件400,以及现有不具备有浮置掺杂区403的超接面金属氧化物-半导体晶体管单元进行反向恢复测试所得到的反向截止电流(irr)与反向截止时间(trr)的关系曲线图。在具备相同的额定操作电压的条件下,测量功率半导体元件400以及现有超接面金属氧化物-半导体晶体管单元的反向截止电流与反向截止时间。

73.在图9中,曲线902代表功率半导体元件400的反向截止电流与反向截止时间的关系曲线;曲线902代表现有超接面金属氧化物-半导体晶体管单元的反向截止电流与反向截止时间的关系曲线。

74.由图9可以看出,功率半导体元件400的反向截止电流和反向截止时间明显小于现有超接面金属氧化物-半导体晶体管单元的反向截止电流和反向截止时间。可见,配置浮置掺杂区403具有降低功率半导体元件400反向截止电流与减少反向截止时间的显著功能。

75.根据上述实施例,本说明书是提供一种功率半导体元件及其制造方法,是在具有第一电性的外延层中形成至少一个具有垂直通道和npn寄生双极性接面的晶体管单元或金属-半导体接面二极管单元。并在外延层中配置具有第二电性的浮置掺杂区来改变晶体管/二极管单元中的垂直电场分布。当晶体管单元/二极管进行反向操作时,能促进电子自漏极注入漏极和源极之间存的寄生pn接面,使电子与累积在pn接面的少数载子复合。可在不改变额定的操作电压的情况下,缩短关闭场效晶体管单元所需要的反向恢复时间,利于功率半导体元件的高频操作。

76.虽然本发明已以实施例公开如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的变动与润饰,故本发明的保护范围当视权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1