半导体结构及其形成方法、对准方法与流程

[0001]

本发明涉及半导体制造技术领域,尤其涉及一种半导体结构及其形成方法、对准方法。

背景技术:

[0002]

随着平面型闪存存储器的发展,半导体的生产工艺取得了巨大的进步。但是最近几年,平面型闪存的发展遇到了各种挑战:物理极限、现有显影技术极限以及存储电子密度极限等。在此背景下,为解决平面闪存遇到的困难以及追求更低的单位存储单元的生产成本,各种不同的三维(3d)闪存存储器结构应运而生,例如3d nor(3d或非)闪存和3d nand(3d与非)闪存。

[0003]

其中,3d nand存储器以其小体积、大容量为出发点,将存储单元采用三维模式层层堆叠的高度集成为设计理念,生产出高单位面积存储密度、高效存储单元性能的存储器,已经成为新兴存储器设计和生产的主流工艺。

[0004]

在3d nand存储器等三维存储器的制造工艺中,光刻是至关重要的步骤。在当前的光刻制程中,需要先进行扫描,判断待刻蚀的晶圆的位置是否对准。但是,当前的对准方法精确度较差,从而影响后续光刻工艺的实施。

[0005]

因此,如何提高在光刻过程中晶圆对准的精确度,从而改善光刻质量,是当前亟待解决的技术问题。

技术实现要素:

[0006]

本发明提供一种半导体结构及其形成方法、对准方法,用于解决现有的光刻工艺无法对晶圆精确对准的问题,以改善光刻质量。

[0007]

为了解决上述问题,本发明提供了一种半导体结构,包括:

[0008]

衬底,所述衬底包括器件区域和位于所述器件区域外围的外围区域;

[0009]

对准标记,位于所述衬底上的外围区域,所述对准标记包括闪耀光栅结构,用于在刻蚀所述器件区域的过程中对准所述器件区域的位置。

[0010]

可选的,所述闪耀光栅结构包括:

[0011]

光栅面,位于所述衬底表面;

[0012]

多个刻槽,多个所述刻槽沿平行于所述衬底的方向呈锯齿状分布于所述光栅面上,每一所述刻槽的刻槽面相对于所述光栅面倾斜设置。

[0013]

可选的,所述闪耀光栅结构包括:

[0014]

光栅面,位于所述衬底表面;

[0015]

多个阶梯,多个所述阶梯沿平行于所述衬底的方向分布于所述光栅面上,每个所述阶梯包括沿垂直于所述衬底的方向依次叠置的多层台阶。

[0016]

为了解决上述问题,本发明还提供了一种半导体结构的形成方法,其包括如下步骤:

[0017]

提供一衬底,于所述衬底表面定义器件区域和位于所述器件区域外围的外围区域;

[0018]

形成包括闪耀光栅结构的对准标记于所述衬底上的外围区域,所述对准标记用于在刻蚀所述器件区域的过程中对准所述器件区域的位置。

[0019]

可选的,形成包括闪耀光栅结构的对准标记于所述衬底上的外围区域的具体步骤包括:

[0020]

根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底表面。

[0021]

可选的,所述闪耀光栅结构包括位于所述衬底表面的光栅面以及位于所述光栅面上且沿平行于所述衬底的方向呈锯齿状分布的多个刻槽,每一所述刻槽的刻槽面相对于所述光栅面倾斜预设角度;根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底上的外围区域的具体步骤包括:

[0022]

根据对准光的波长和所需闪耀的光谱级数,获取满足如下公式(1)的相邻两个刻槽之间的距离和所述预设角度:

[0023]

2dsinβ=mλ

ꢀꢀ

(1)

[0024]

式中,d表示相邻两个刻槽之间的距离,β表示预设角度,m表示所需闪耀的光谱级数,λ表示对准光的波长。

[0025]

可选的,所述闪耀光栅结构包括位于所述衬底表面的光栅面以及沿平行于所述衬底的方向分布于光栅面上的多个阶梯,每个所述阶梯包括沿垂直于所述衬底的方向依次叠置的多层台阶;根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底表面的具体步骤包括:

[0026]

根据对准光的波长和所需闪耀的光谱级数,获取满足如下公式(2)的所述台阶的宽度和所述台阶的高度:

[0027]

2t-θw=mλ

ꢀꢀ

(2)

[0028]

式中,t表示所述台阶的高度,w表示所述台阶的宽度,θ表示衍射角,m表示所需闪耀的光谱级数,λ表示对准光的波长。

[0029]

为了解决上述问题,本发明还提供了一种半导体结构的对准方法,包括如下步骤:

[0030]

提供一半导体结构,所述半导体结构包括衬底,所述衬底包括器件区域和位于所述器件区域外围的外围区域;

[0031]

形成包括闪耀光栅结构的对准标记于所述衬底上的所述外围区域;

[0032]

对准光源向所述对准标记发射对准光,根据所述对准标记的反射衍射光判断所述器件区域的位置是否对准。

[0033]

可选的,形成包括闪耀光栅结构的对准标记于所述衬底上的所述外围区域的具体步骤包括:

[0034]

根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底表面。

[0035]

可选的,所述闪耀光栅结构包括位于所述衬底表面的光栅面以及位于所述光栅面上且沿平行于所述衬底的方向呈锯齿状分布的多个刻槽,每一所述刻槽的刻槽面相对于所述光栅面倾斜预设角度;根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构

的对准标记于所述衬底上的外围区域的具体步骤包括:

[0036]

根据对准光的波长和所需闪耀的光谱级数,获取满足如下公式(1)的相邻两个刻槽之间的距离和所述预设角度:

[0037]

2dsinβ=mλ

ꢀꢀ

(1)

[0038]

式中,d表示相邻两个刻槽之间的距离,β表示预设角度,m表示所需闪耀的光谱级数,λ表示对准光的波长。

[0039]

可选的,对准光源向所述对准标记发射对准光的具体步骤包括:

[0040]

对准光源沿垂直于所述刻槽面的方向向所述闪耀光栅结构发射对准光。

[0041]

可选的,所述闪耀光栅结构包括位于所述衬底表面的光栅面以及沿平行于所述衬底的方向分布于光栅面上的多个阶梯,每个所述阶梯包括沿垂直于所述衬底的方向依次叠置的多层台阶;根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底表面的具体步骤包括:

[0042]

根据对准光的波长和所需闪耀的光谱级数,获取满足如下公式(2)的所述台阶的宽度和所述台阶的高度:

[0043]

2t-θw=mλ

ꢀꢀ

(2)

[0044]

式中,t表示所述台阶的高度,w表示所述台阶的宽度,θ表示衍射角,m表示所需闪耀的光谱级数,λ表示对准光的波长。

[0045]

可选的,对准光源向所述对准标记发射对准光的具体步骤包括:

[0046]

对准光源沿垂直于所述台阶的台面的方向向所述闪耀光栅结构发射对准光。

[0047]

本发明提供的半导体结构及其形成方法、对准方法,通过在衬底的外围区域中形成包括闪耀光栅结构的对准标记,从而使得单个刻槽的刻槽面(即单缝)的衍射中央极大与刻槽间(即缝间)干涉零级主极大分开,将光强从零级转移到所需要的光谱级数上去,实现对该级数光谱的闪耀,闪耀光的高光强能够有效的提高对准精度,改善后续的光刻质量,提高半导体产品的良率。

附图说明

[0048]

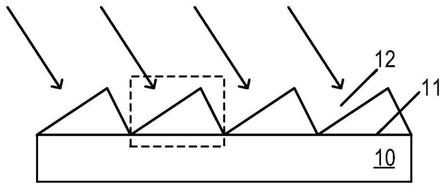

附图1是本发明一具体实施方式中半导体结构的示意图;

[0049]

附图2是附图1中虚线框区域的放大示意图;

[0050]

附图3是本发明另一具体实施方式中半导体结构的示意图;

[0051]

附图4是附图3中虚线框区域的放大示意图;

[0052]

附图5是本发明具体实施方式中半导体结构的形成方法流程图;

[0053]

附图6是本发明具体实施方式中半导体结构的对准方法流程图。

具体实施方式

[0054]

下面结合附图对本发明提供的半导体结构及其形成方法、对准方法的具体实施方式做详细说明。

[0055]

在当前3d nand存储器等半导体器件的光刻工艺中,为了实现对光刻区域的对准,通常会在半导体衬底上形成光栅结构作为对准标记。对准光源发射对准光至所述对准标记上,根据所述对准标记的反射衍射光来确定半导体衬底的位置,从而判断所述光刻区域是

否对准。为了获得更好的对准效果,往往希望所述对准标记反射的衍射光为高阶衍射光。当前,为了实现高阶衍射光的引入,通常是对对准标记进行等分分割,例如将一个连续、完整的矩形条分割为多等份(例如3等份、5等份或者7等份),以获得高阶光(例如3阶光、7阶光或者7阶光)。

[0056]

然而,根据光栅衍射原理可知,单缝衍射的中央极大与缝间干涉的零级主极大(0级光谱)重合,因此,等分分割的方式产生的衍射光中0级衍射光所占的光强比例最高,高阶光的光强相对较少,而且级数越高的光、光强就越小,从而对对准过程中的光强指标造成影响,导致对准精度的下降。

[0057]

为了提高对准过程中的对准精度,本具体实施方式提供了一种半导体结构,附图1是本发明一具体实施方式中半导体结构的示意图,附图2是附图1中虚线框区域的放大示意图。如图1和图2所示,本具体实施方式提供的半导体结构,包括:

[0058]

衬底10,所述衬底10包括器件区域和位于所述器件区域外围的外围区域;

[0059]

对准标记,位于所述衬底20上的外围区域,所述对准标记包括闪耀光栅结构,用于在刻蚀所述器件区域的过程中对准所述器件区域的位置。

[0060]

具体来说,本具体实施方式中所述的衬底10可以为单层结构,也可以为多层结构。所述对准标记可以直接位于所述衬底10表面,也可以在所述对准标记与所述衬底10之间设置其他的半导体层。本具体实施方式是以所述对准标记直接形成于所述衬底10表面为例进行说明。

[0061]

所述闪耀光栅结构中的具体参数,例如闪耀角、光栅常数等,本领域技术人员可以根据实际需要进行调整,例如根据所需要闪耀的光谱的级数。本具体实施方式通过形成具有所述闪耀光栅结构的所述对准标记,当采用激光灯对准光源照射所述对准标记时,可以实现对特定级数光谱的闪耀,从而确保了对准过程中光强指标的准确性,提高了对准精度,为后续光刻工艺的顺利实施奠定了基础,并有助于半导体产品良率以及产率的提高。

[0062]

可选的,所述闪耀光栅结构包括:

[0063]

光栅面11,位于所述衬底10表面;

[0064]

多个刻槽12,多个所述刻槽12沿平行于所述衬底10的方向呈锯齿状分布于所述光栅面11上,每一所述刻槽12的刻槽面121相对于所述光栅面11倾斜设置。

[0065]

图1和图2中的实线箭头方向表示对准光的入射方向。举例来说,如图1和图2所示,所述衬底10表面具有多个沿平行于所述衬底10的方向呈锯齿状排布的所述刻槽12。所述光栅面11平行于所述衬底10的表面,所述刻槽面121相对于所述光栅面11倾斜预设角度β,相邻两个所述刻槽12之间的距离为d。在对准过程中,对准光的波长λ是预先设置的、且在对准过程中固定不变,对准光沿着单缝衍射极大位置入射(即对准光沿着所述刻槽面121的法线方向入射),根据如下式(1)所述的闪耀光栅方程以及对准工艺所需要闪耀的光谱级数m,可以获得所述预设角度和相邻两个所述刻槽12之间的距离d的相对数值。本具体实施方式中所述的多个是指两个及两个以上。本具体实施方式中所述的对准光可以是但不限于激光。

[0066]

2dsinβ=mλ

ꢀꢀ

(1)

[0067]

例如:

[0068]

当m=1时,在确定所述对准光的波长λ之后,通过调整预设角度β和相邻两个所述刻槽12之间的距离d,使之满足上式(1),则1级光谱闪耀,1级光谱具有最大光强;

[0069]

当m=2时,在确定所述对准光的波长λ之后,通过调整预设角度β和相邻两个所述刻槽12之间的距离d,使之满足上式(1),则2级光谱闪耀,2级光谱具有最大光强。

[0070]

附图3是本发明另一具体实施方式中半导体结构的示意图,附图4是附图3中虚线框区域的放大示意图。在其他具体实施方式中,如图3和图4所示,所述闪耀光栅结构包括:

[0071]

光栅面11,位于所述衬底10表面;

[0072]

多个阶梯,多个所述阶梯沿平行于所述衬底10的方向分布于所述光栅面11上,每个所述阶梯包括沿垂直于所述衬底10的方向依次叠置的多层台阶。

[0073]

附图3中的虚线框表示一个阶梯的结构。由于阶梯型光栅是一种特殊的闪耀光栅结构,因此,也可以在所述光栅面11上形成多个沿平行于所述衬底10的方向分布的阶梯。每一层所述阶梯包括沿垂直于所述衬底10的方向依次叠置的多层台阶。一个所述阶梯中相邻的两层台阶中较靠近所述衬底10的一层台阶沿水平方向突出于较远离所述衬底10的一层台阶。在所述阶梯中,多层所述台阶41的高度t均相等,且每一层所述台阶41的台面宽度w均相等。

[0074]

图3和图4中的实线箭头表示对准光的入射方向,图4中的虚线箭头表示衍射光的方向。在对准过程中,对准光的波长λ是预先设置的、且在对准过程中固定不变,对准光沿着单缝衍射极大位置入射(即对准光沿着垂直于所述台阶台面的方向入射),根据如下式(2)所述的闪耀光栅方程以及对准工艺所需要闪耀的光谱级数m,可以获得所述台面41的台面宽度w和所述台面41的台面高度t的相对数值。本具体实施方式中所述的多个是指两个及两个以上,多层是指两层及两层以上。

[0075]

2t-θw=mλ

ꢀꢀ

(2)

[0076]

式中,θ表示衍射角,根据闪耀光栅的闪耀原理,当所需要闪耀的光谱级数m确定后,衍射角θ也就相应确定。

[0077]

不仅如此,本具体实施方式还提供了一种半导体结构的形成方法。附图5是本发明具体实施方式中半导体结构的形成方法流程图,本具体实施方式形成的半导体结构的示意图可参见图1-图4。如图1-图5所示,本具体实施方式提供的半导体结构的形成方法,包括如下步骤:

[0078]

步骤s11,提供一衬底10,于所述衬底10表面定义器件区域和位于所述器件区域外围的外围区域;

[0079]

步骤s12,形成包括闪耀光栅结构的对准标记于所述衬底10上的外围区域,所述对准标记用于在刻蚀所述器件区域的过程中对准所述器件区域的位置。

[0080]

可选的,形成包括闪耀光栅结构的对准标记于所述衬底10上的外围区域的具体步骤包括:

[0081]

根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底10表面。

[0082]

可选的,所述闪耀光栅结构包括位于所述衬底10表面的光栅面11以及位于所述光栅面11上且沿平行于所述衬底10的方向呈锯齿状分布的多个刻槽12,每一所述刻槽12的刻槽面121相对于所述光栅面11倾斜预设角度;根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底10上的外围区域的具体步骤包括:

[0083]

根据对准光的波长和所需闪耀的光谱级数,获取满足如下公式(1)的相邻两个刻

槽12之间的距离和所述预设角度:

[0084]

2dsinβ=mλ

ꢀꢀ

(1)

[0085]

式中,d表示相邻两个刻槽之间的距离,β表示预设角度,m表示所需闪耀的光谱级数,λ表示对准光的波长。

[0086]

在其他具体实施方式中,所述闪耀光栅结构包括位于所述衬底10表面的光栅面11以及沿平行于所述衬底10的方向分布于光栅面11上的多个阶梯,每个所述阶梯包括沿垂直于所述衬底10的方向依次叠置的多层台阶41;根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底10表面的具体步骤包括:

[0087]

根据对准光的波长和所需闪耀的光谱级数,获取满足如下公式(2)的所述台阶的宽度和所述台阶的高度:

[0088]

2t-θw=mλ

ꢀꢀ

(2)

[0089]

式中,t表示所述台阶的高度,w表示所述台阶的宽度,θ表示衍射角,m表示所需闪耀的光谱级数,λ表示对准光的波长。

[0090]

不仅如此,本具体实施方式还提供了一种半导体结构的对准方法。附图6是本发明具体实施方式中半导体结构的对准方法流程图,本具体实施方式中的半导体结构的示意图可参见图1-图4,本具体实施方式中所述的半导体结构可以采用如图5所示的方法形成。如图1-图6所示,本具体实施方式提供的半导体结构的对准方法,包括如下步骤:

[0091]

步骤s61,提供一半导体结构,所述半导体结构包括衬底10,所述衬底10包括器件区域和位于所述器件区域外围的外围区域;

[0092]

步骤s62,形成包括闪耀光栅结构的对准标记于所述衬底10上的所述外围区域;

[0093]

步骤s63,对准光源向所述对准标记发射对准光,根据所述对准标记的反射衍射光判断所述器件区域的位置是否对准。

[0094]

可选的,形成包括闪耀光栅结构的对准标记于所述衬底10上的所述外围区域的具体步骤包括:

[0095]

根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底10表面。

[0096]

可选的,所述闪耀光栅结构包括位于所述衬底10表面的光栅面以及位于所述光栅面11上且沿平行于所述衬底10的方向呈锯齿状分布的多个刻槽12,每一所述刻槽12的刻槽面121相对于所述光栅面11倾斜预设角度;根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底10上的外围区域的具体步骤包括:

[0097]

根据对准光的波长和所需闪耀的光谱级数,获取满足如下公式(1)的相邻两个刻槽之间的距离和所述预设角度:

[0098]

2dsinβ=mλ

ꢀꢀ

(1)

[0099]

式中,d表示相邻两个刻槽12之间的距离,β表示预设角度,m表示所需闪耀的光谱级数,λ表示对准光的波长。

[0100]

可选的,对准光源向所述对准标记发射对准光的具体步骤包括:

[0101]

对准光源沿垂直于所述刻槽面121的方向向所述闪耀光栅结构发射对准光。

[0102]

在其他具体实施方式中,所述闪耀光栅结构包括位于所述衬底10表面的光栅面11以及沿平行于所述衬底10的方向分布于光栅面11上的多个阶梯,每个所述阶梯包括沿垂直

于所述衬底10的方向依次叠置的多层台阶41;根据对准光的波长和所需闪耀的光谱级数形成包括闪耀光栅结构的对准标记于所述衬底10表面的具体步骤包括:

[0103]

根据对准光的波长和所需闪耀的光谱级数,获取满足如下公式(2)的所述台阶的宽度和所述台阶的高度:

[0104]

2t-θw=mλ

ꢀꢀ

(2)

[0105]

式中,t表示所述台阶的高度,w表示所述台阶的宽度,θ表示衍射角,m表示所需闪耀的光谱级数,λ表示对准光的波长。

[0106]

可选的,对准光源向所述对准标记发射对准光的具体步骤包括:

[0107]

对准光源沿垂直于所述台阶的台面的方向向所述闪耀光栅结构发射对准光。

[0108]

本具体实施方式提供的半导体结构及其形成方法、对准方法,通过在衬底的外围区域中形成包括闪耀光栅结构的对准标记,从而使得单个刻槽的刻槽面(即单缝)的衍射中央极大与刻槽间(即缝间)干涉零级主极大分开,将光强从零级转移到所需要的光谱级数上去,实现对该级数光谱的闪耀,闪耀光的高光强能够有效的提高对准精度,改善后续的光刻质量,提高半导体产品的良率。

[0109]

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1