半导体衬底、制备方法以及电子元器件与流程

[0001]

本发明涉及集成电路封装技术领域,尤其涉及半导体衬底、制备方法以及电子元器件。

背景技术:

[0002]

随着集成电路工艺技术的高速发展,微电子封装技术逐渐成为制约半导体技术发展的主要因素,其中,硅通孔结构技术能够使芯片在三维方向堆叠的密度最大、芯片之间的互连线最短、外形尺寸最小,并且大大改善芯片速度和低功耗的性能。

[0003]

作为集成电路中一种重要的无源器件,电感可以用于制作滤波器和震荡器,这些器件都需要具有高电感值。硅通孔结构结构本身具有较大的深宽比和比表面积,是制备高数值电感的良好基底。

[0004]

公开号为cn107611536a的中国专利申请公开了一种运用硅通孔结构结构的新型切皮雪夫滤波器,该滤波器通过改变同轴硅通孔结构中绝缘层的使用材料来增大电容值,并通过垂直互连技术减小互连线的尺寸,从而提高滤波器的整体性能。然而,硅通孔结构绝缘层的厚度以及使用材料种类都是有限的,该滤波器在电感数值方面的调控范围非常有限,进而会限制进一步的应用。

[0005]

因此,有必要设计一种新型的半导体衬底以避免现有技术中存在的上述问题。

技术实现要素:

[0006]

本发明的目的在于提供一种半导体衬底及其制备方法,以及包括所述半导体衬底的电子元器件,以有利于电感数值的调控,从而扩大应用范围。

[0007]

为实现上述目的,本申请的所述半导体衬底包括相对的第一衬底表面和第二衬底表面,以及贯通所述第一衬底表面和所述第二衬底表面的通孔结构,所述通孔结构的内表面开设有凹陷部,所述凹陷部的内表面与所述通孔结构的内表面相接以形成连续内表面;所述半导体衬底还包括堆叠设置的第一隔离层和电感层,所述第一隔离层覆盖所述连续内表面,所述电感层填充所述凹陷部。

[0008]

本申请所述半导体衬底的有益效果在于:所述半导体衬底的通孔结构内表面开设有凹陷部,能够增加所述通孔结构的比表面积,所述凹陷部的内表面与所述通孔结构的内表面相接以形成连续内表面,且所述第一隔离层覆盖所述连续内表面以及所述电感层填充所述凹陷部,有利于通过提高所述电感层的截面积来增加电感值,同时也便于通过改变所述通孔结构的结构以及所述凹陷部的深宽比来调节所述电感值,从而扩大应用范围。

[0009]

优选的,所述电感层包括第一导体层,所述第一导体层包括第一子导体层和第二子导体层,所述第一子导体层靠近所述通孔结构的轴线并朝向所述通孔结构的内表面,所述第二子导体层位于所述凹陷部内,并朝向所述通孔结构的轴线延伸以交汇于所述第一子导体层。其有益效果在于:实现对所述凹陷部的有效填充。

[0010]

进一步优选的,所述电感层还包括顺次堆叠设置的第一扩散阻挡层和第一籽晶

层,所述第一扩散阻挡层和所述第一籽晶层设置于所述第一子导体层和所述第二子导体层的任意一种与所述第一隔离层之间。

[0011]

进一步优选的,所述第一隔离层的厚度为50-100纳米,所述第一扩散阻挡层的厚度为10-20纳米,所述第一籽晶层的厚度为10-20纳米,所述第一导体层的厚度为100-200纳米。其有益效果在于:有利于电感值的调控。

[0012]

进一步优选的,还包括第二隔离层和互连结构,所述第二隔离层覆盖所述第一子导体层的靠近所述通孔结构轴线的表面,所述互连结构设置于所述第二隔离层,并填充所述通孔结构。其有益效果在于:使所述通孔结构和所述电感层之间相互没有影响,并有利于通过所述互连结构实现不同芯片的堆叠互连。

[0013]

进一步优选的,所述第一隔离层、所述第一扩散阻挡层、第一籽晶层、所述第一导体层和所述第二隔离层分别朝向所述第一衬底表面延伸设置,以顺次堆叠设置于所述第一衬底表面。其有益效果在于:有利于增加电感值。

[0014]

进一步优选的,还包括设置于所述第一衬底表面的第一导通部,所述第一导通部的底部贯穿所述第二隔离层以与所述第一导体层实现电接触。

[0015]

进一步优选的,所述第一导通部的数目至少为1。

[0016]

进一步优选的,还包括相对设置于所述互连结构的第二导通部和第三导通部,所述第二导通部与所述第一导通部设置于同一侧,所述第三导通部设置于所述第二衬底表面所在的一侧。

[0017]

进一步优选的,还包括第三隔离层,所述第三隔离层覆盖所述第二衬底表面,并朝向所述通孔结构的轴线延伸以与所述第二隔离层相接,所述互连结构限定于所述第二导通部、所述第三导通部和所述第三隔离层所围成的空间内。其有益效果在于:使所述通孔结构和所述电感层之间相互没有影响。

[0018]

进一步优选的,所述互连结构包括沿所述通孔结构轴线设置的第二导体层,所述第二导体层和所述第一导体层由同一导电材料组成。其有益效果在于:有利于降低所述电感层的寄生电阻并减少工艺复杂度。

[0019]

进一步优选的,所述互连结构还包括顺次堆叠设置的第二扩散阻挡层和第二籽晶层,所述第二扩散阻挡层和所述第二籽晶层设置于所述第二隔离层和所述第二导体层之间。

[0020]

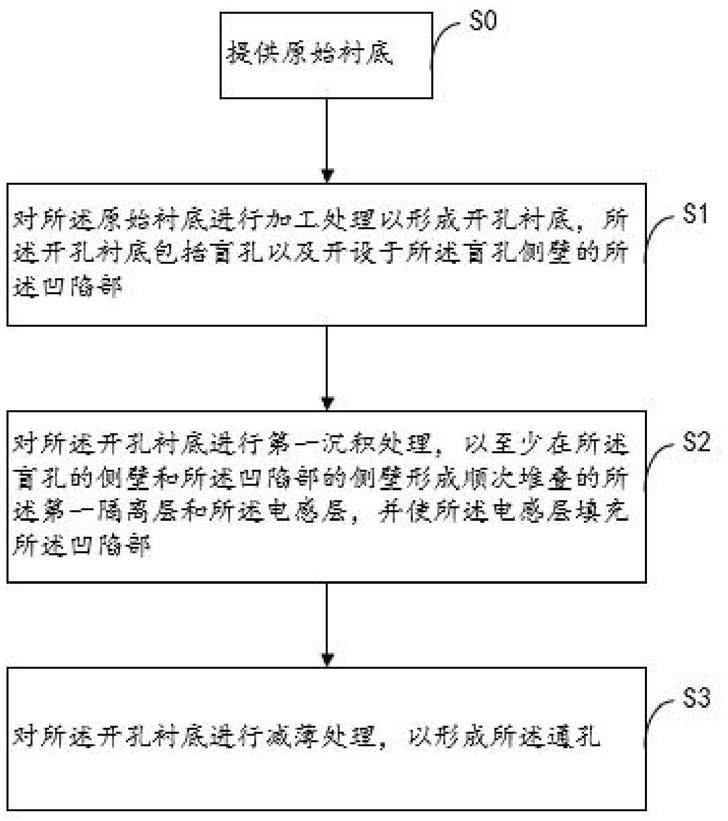

本发明的所述半导体衬底的制备方法包括:

[0021]

s0:提供原始衬底;

[0022]

s1:对所述原始衬底进行加工处理以形成开孔衬底,所述开孔衬底包括盲孔结构以及开设于所述盲孔结构侧壁的所述凹陷部;

[0023]

s2:对所述开孔衬底进行第一沉积处理,以至少在所述盲孔结构的侧壁和所述凹陷部的侧壁形成顺次堆叠的所述第一隔离层和所述电感层,并使所述电感层填充所述凹陷部;

[0024]

s3:对所述开孔衬底进行减薄处理,以形成所述通孔结构。

[0025]

本发明的所述半导体衬底的制备方法的有益效果在于:通过在所述盲孔结构的侧壁开设所述凹陷部,以及在所述盲孔结构的侧壁和所述凹陷部的侧壁形成顺次堆叠的所述第一隔离层和所述电感层,并使所述电感层填充所述凹陷部,有利于通过提高所述电感层

的截面积来增加电感值,同时也便于通过改变所述盲孔结构的结构以及所述凹陷部的深宽比来调节所述电感值,从而扩大应用范围。

[0026]

优选的,所述步骤s1中,所述加工处理包括对所述原始衬底进行离子注入处理以形成贯穿所述盲孔结构侧壁的离子注入层,然后刻蚀所述离子注入层以形成所述凹陷部。其有益效果在于:便于通过所述离子注入处理来调节所述凹陷部的深宽比,进而有利于调节电感值。

[0027]

进一步优选的,所述离子注入处理的次数至少为1,当所述离子注入处理的次数至少为2,相邻的所述离子注入处理的离子注入剂量不同。其有益效果在于:便于调节所述凹陷部的位置和尺寸。

[0028]

进一步优选的,所述离子注入处理的离子注入剂量随所述离子注入处理次数的增加而降低。

[0029]

进一步优选的,单次所述离子注入处理中,离子注入剂量为3

×

10

17-2

×

10

18

离子/平方厘米,退火温度为1000-1350摄氏度,退火时间为1-4小时。

[0030]

本发明的电子元器件包括若干晶片以及所述半导体衬底,所述若干晶片设置于所述半导体衬底,以实现电互连。其有益效果在于:使所述通孔结构不仅能够作为不同晶片之间垂直互连的导电通道,同时还作为电感的基底。

附图说明

[0031]

图1为本发明实施例的半导体衬底的制备方法流程图;

[0032]

图2为本发明实施例的半导体衬底的剖视图;

[0033]

图3为图2所示的第一导通部与部分电感层的装配剖视图;

[0034]

图4为本发明实施例对原始衬底进行刻蚀加工后得到的衬底的剖视图;

[0035]

图5为对图4所示的衬底进行等离子注入处理后得到的衬底的剖视图;

[0036]

图6为对图5所示的衬底进行刻蚀后形成的衬底的剖视图;

[0037]

图7为对图6所示的衬底进行第一沉积处理后形成的衬底的剖视图;

[0038]

图8为对图7所示的衬底进行第二沉积处理后形成的衬底的剖视图;

[0039]

图9为对图8所示的衬底进行第一去除处理后形成的衬底的剖视图;

[0040]

图10为对图9所示的衬底进行第二去除处理后形成的衬底的剖视图;

[0041]

图11为对图10所示的衬底进行第三沉积处理后形成的衬底的剖视图;

[0042]

图12为对图11所示的衬底进行第一顶部处理后形成的衬底的剖视图;

[0043]

图13为对图12所示的衬底进行第二顶部处理后形成的衬底的剖视图;

[0044]

图14为对图13所示的衬底底部进行减薄处理后形成的衬底的剖视图。

具体实施方式

[0045]

为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。除非另外定义,此处使用的技术术语或者科学术语应当为本发明所属领域内具有一般技能的人士所理解的通常

意义。本文中使用的“包括”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。

[0046]

为克服现有技术中存在的问题,本发明实施例提供了一种半导体衬底、所述半导体衬底的制备方法以及包括所述半导体衬底的电子元器件。

[0047]

本发明实施例的所述半导体衬底的制备方法,参照图1,包括:

[0048]

s0:提供原始衬底;

[0049]

s1:对所述原始衬底进行加工处理以形成开孔衬底,所述开孔衬底包括盲孔结构以及开设于所述盲孔结构侧壁的所述凹陷部;

[0050]

s3:对所述开孔衬底进行第一沉积处理,以至少在所述盲孔结构的侧壁和所述凹陷部的侧壁形成顺次堆叠的所述第一隔离层和所述电感层,并使所述电感层填充所述凹陷部;

[0051]

s4:对所述开孔衬底进行减薄处理,以形成所述通孔结构。

[0052]

本发明实施例的所述半导体衬底的制备方法中,通过在所述盲孔结构的侧壁开设所述凹陷部,以及在所述盲孔结构的侧壁和所述凹陷部的侧壁形成顺次堆叠的所述第一隔离层和所述电感层,并使所述电感层填充所述凹陷部,有利于通过提高所述电感层的截面积来增加电感值,同时也便于通过改变所述盲孔结构的结构以及所述凹陷部的深宽比来调节所述电感值,从而扩大应用范围。

[0053]

图2为本发明一些实施例的半导体衬底的剖视图。

[0054]

参照图2,半导体衬底2包括相对的第一衬底表面211、第二衬底表面212、贯通所述第一衬底表面211和所述第二衬底表面212的通孔结构22,以及堆叠设置的第一隔离层241和电感层26。

[0055]

具体的,所述通孔结构22的内表面开设有凹陷部23,所述凹陷部23的内表面与所述通孔结构22的内表面相接以形成连续内表面(图中未标示)。所述第一隔离层241覆盖所述连续内表面(图中未标示)以及所述第一衬底表面211,所述电感层26填充所述凹陷部23。所述凹陷部23具体为环绕所述通孔结构22的中心轴线25设置的沟槽结构。

[0056]

所述凹陷部23的宽度指所述凹陷部23内沿所述中心轴线25方向的垂直距离,所述凹陷部23的深度指所述凹陷部23内沿垂直所述中心轴线25方向延伸的长度。所述凹陷部23的深宽比为所述凹陷部23的深度与宽度的比值。

[0057]

本发明一些实施例中,所述凹陷部23的个数至少为1。具体的,参照图2,所述半导体衬底2具有4个所述凹陷部23。

[0058]

本发明一些实施例中,参照图2,若干所述凹陷部23具有相同的结构,且相邻所述凹陷部23之间沿所述中心轴线25的方向具有同一间隔。

[0059]

本发明一些实施例中,若干所述凹陷部23的结构不完全相同。

[0060]

本发明一些实施例中,相邻所述凹陷部23之间沿所述中心轴线25方向具有的间隔不完全相同。

[0061]

参照图2,所述电感层26包括第一导体层263,所述第一导体层263包括第一子导体层(图中未标示)和第二子导体层(图中未标示)。

[0062]

具体的,所述第一子导体层(图中未标示)靠近所述中心轴线25并朝向所述通孔结构22的内表面。所述第二子导体层(图中未标示)位于所述凹陷部23内,并朝向所述中心轴

线25延伸以交汇于所述第一子导体层(图中未标示),以实现对所述凹陷部23的有效填充。

[0063]

本发明一些实施例中,所述第一导体层263的组成材料为金属铜,厚度为100-200纳米。

[0064]

参照图2,所述电感层26还包括顺次堆叠设置的第一扩散阻挡层261和第一籽晶层262,所述第一扩散阻挡层261和所述第一籽晶层262设置于所述第一子导体层(图中未标示)和所述第二子导体层(图中未标示)的任意一种与所述第一隔离层241之间。

[0065]

具体的,所述第一扩散阻挡层261的相对的两个表面中的一个覆盖所述第一隔离层241的表面,另一个被所述第一籽晶层262的表面所覆盖;所述第一籽晶层262的相对的两个表面中的一个被所述第一扩散阻挡层261所覆盖,另一个被所述第一导体层263所覆盖。

[0066]

本发明一些实施例中,所述第一隔离层241的厚度为50-100纳米,所述第一扩散阻挡层261的厚度为10-20纳米,所述第一籽晶层262的厚度为10-20纳米,以通过厚度的调节来进行电感值的调控。

[0067]

本发明一些实施例中,所述第一隔离层241的组成材料为sio2、si3n4、sion、sicoh和sicofh中的至少一种。

[0068]

本发明一些实施例中,所述第一扩散阻挡层261的组成材料为tin、tan、zrn、tiwn和mnsio3中的至少一种。

[0069]

本发明一些实施例中,所述第一籽晶层262的组成材料为cu、ru、co、ruco、curu和cuco中的至少一种。

[0070]

参照图2,所述半导体衬底2还包括第二隔离层242和互连结构27,所述第二隔离层242覆盖所述第一子导体层(图中未标示)的靠近所述中心轴线25的表面,使所述通孔结构22和所述电感层26之间相互没有影响。所述互连结构27设置于所述第二隔离层242,并填充所述通孔结构22,以有利于通过所述互连结构27实现不同芯片的堆叠互连。

[0071]

进一步的,所述第一隔离层241、所述第一扩散阻挡层261、所述第一籽晶层262、所述第一导体层263和所述第二隔离层242分别朝向所述第一衬底表面211延伸设置,以顺次堆叠设置于所述第一衬底表面211,有利于增加电感值。

[0072]

本发明一些实施例中,所述第二隔离层242的组成材料为sio2、si3n4、sion、sicoh和sicofh中的至少一种。

[0073]

本发明一些实施例中,所述第一隔离层241和所述第二隔离层242具有相同的组成材料。

[0074]

本发明一些实施例中,所述第一隔离层241和所述第二隔离层242具有不同的组成材料。

[0075]

参照图2,所述互连结构27包括沿所述中心轴线25设置的第二导体层273,所述第二导体层273和所述第一导体层263由同一导电材料组成,以有利于降低所述电感层26的寄生电阻并减少工艺复杂度。

[0076]

本发明一些具体的实施例中,所述第二导体层273和所述第一导体层263的组成材料均为金属铜。

[0077]

参照图2,所述互连结构27还包括顺次堆叠设置的第二扩散阻挡层271和第二籽晶层272,所述第二扩散阻挡层271和所述第二籽晶层272设置于所述第二隔离层242和所述第二导体层273之间。

[0078]

具体的,所述第二扩散阻挡层271的相对的两个表面中的一个覆盖所述第二隔离层242的表面,另一个被所述第二籽晶层272的表面所覆盖;所述第二籽晶层272的相对的两个表面中的一个被所述第二扩散阻挡层271所覆盖,另一个被所述第二导体层273所覆盖。

[0079]

本发明一些实施例中,所述第二扩散阻挡层271的组成材料为tin、tan、zrn、tiwn和mnsio3中的至少一种。

[0080]

本发明一些实施例中,所述第二扩散阻挡层271与所述第一扩散阻挡层261具有相同或不同的组成材料。

[0081]

本发明一些实施例中,所述第二籽晶层272的组成材料为cu、ru、co、ruco、curu和cuco中的至少一种。

[0082]

本发明一些实施例中,所述第二籽晶层272与所述第一籽晶层262具有相同或不同的组成材料。

[0083]

图3为图2所示的第一导通部与部分电感层的装配剖视图。

[0084]

参照图2和图3,所述半导体衬底2还包括设置于所述第一衬底表面211的第一导通部281,所述第一导通部281的底部贯穿所述第二隔离层242以与所述第一导体层263实现电接触。

[0085]

具体的,所述第一导通部281由顺次堆叠的第一粘附层31、第三籽晶层32和第一金属接触层33组成。所述第一粘附层31的底部贯穿所述第二隔离层242以与所述第一导体层263实现电接触,顶部被所述第三籽晶层32的底部覆盖;所述第三籽晶层32的顶部被所述第一金属接触层33的底部所覆盖。

[0086]

本发明一些实施例中,所述第一粘附层31的组成材料为ti和ta中的至少一种。

[0087]

本发明一些实施例中,所述第三籽晶层32的组成材料为cu、ru、co、ruco、curu和cuco中的至少一种。

[0088]

本发明一些实施例中,所述第三籽晶层32的组成材料与所述第一籽晶层262的组成材料相同或不同。

[0089]

本发明一些实施例中,所述第一金属接触层33的组成材料为金属铜。

[0090]

本发明一些实施例中,所述第一导通部281的数目至少为1。

[0091]

参照图2,所述半导体衬底2还包括相对设置于所述互连结构27的第二导通部282和第三导通部283,所述第二导通部282与所述第一导通部281设置于同一侧,所述第三导通部283设置于所述第二衬底表面212所在的一侧。

[0092]

本发明一些实施例中,所述第二导通部282与所述第一导通部281具有相同的结构,所述第二导通部282中的各层组成材料与所述第一导通部281的对应各层的组成材料相同。

[0093]

本发明一些实施例中,所述第三导通部283由顺次设置的第二粘附层、第四籽晶层和第二金属接触层组成。所述第二粘附层的顶部覆盖所述互连结构27,底部被所述第四籽晶层的顶部所覆盖;所述第四籽晶层的底部被所述第二金属接触层的顶部所覆盖。

[0094]

本发明一些实施例中,所述第二粘附层的组成材料为ti和ta中的至少一种。

[0095]

本发明一些实施例中,所述第四籽晶层的组成材料为cu、ru、co、ruco、curu和cuco中的至少一种。

[0096]

本发明一些实施例中,所述第四籽晶层的组成材料与所述第二籽晶层272的组成

材料相同或不同。

[0097]

本发明一些实施例中,所述第二金属接触层的组成材料为金属铜。

[0098]

参照图2,所述半导体衬底2还包括第三隔离层243,所述第三隔离层243覆盖所述第二衬底表面212,并朝向所述中心轴线25延伸以与所述第二隔离层242相接;所述互连结构27限定于所述第二导通部282、所述第三导通部283和所述第三隔离层243所围成的空间内。

[0099]

本发明一些实施例中,所述第三隔离层243的组成材料为sio2、si3n4、sion、sicoh和sicofh中的至少一种。

[0100]

本发明一些具体的实施例中,所述第一隔离层241和所述第二隔离层242的组成材料均为sio2,所述第三隔离层243的组成材料为si3n4;所述第一扩散阻挡层261和所述第二扩散阻挡层271的组成材料均为tan;所述第一籽晶层262和所述第二籽晶层272的组成材料均为co,所述第三籽晶层32和所述第四籽晶层的组成材料均为cu;所述第一粘附层31和所述第二粘附层的组成材料均为ti;所述第一导体层263和所述第二导体层273的组成材料均为金属铜;所述第一导通部281、所述第二导通部282和所述第三导通部283的任意一种所具有的金属接触层的组成材料为cu。

[0101]

以下结合图2以及图4至图14详细阐述所述半导体衬底2的制备方法。

[0102]

本发明一些实施例的所述步骤s0中,所述原始衬底为硅衬底。

[0103]

图4为本发明一些实施例对原始衬底进行刻蚀加工后得到的衬底的剖视图。

[0104]

本发明一些实施例的所述步骤s1中,参照图4,自原始衬底41的所述第一衬底表面211朝向所述原始衬底41的底部进行刻蚀加工后形成盲孔结构42。

[0105]

具体的,所述刻蚀加工包括:通过旋涂光刻胶、曝光和显影工艺确定所述盲孔结构42的图形,然后采用深度等离子体刻蚀工艺进行刻蚀以形成所述盲孔结构42。所述刻蚀加工的具体实现方式为本领域技术人员的常规技术手段,在此不做赘述。

[0106]

本发明一些实施例的所述步骤s1中,采用cf4和sf6中的至少一种等离子体进行所述深度等离子体刻蚀工艺。

[0107]

图5为对图4所示的衬底进行等离子注入处理后得到的衬底的剖视图。

[0108]

本发明一些实施例的所述步骤s1中,参照图4和图5,所述加工处理包括对图4所示的衬底进行离子注入处理以形成贯穿所述盲孔结构42侧壁的离子注入层51,所述离子注入层51具体为环绕所述中心轴线25设置的结构。

[0109]

本发明一些实施例的所述步骤s1中,所述离子注入处理的次数至少为1,当所述离子注入处理的次数至少为2,相邻的所述离子注入处理的离子注入剂量不同。具体的,所述离子注入处理的离子注入剂量随所述离子注入处理次数的增加而降低。通过调节离子注入能量和相邻两次的注入能量差,可以调节所述离子注入层51在所述盲孔结构42侧壁的位置以及相邻所述离子注入层51的间隔。所述离子注入处理的具体实现方式为本领域技术人员的常规技术手段,在此不做赘述。

[0110]

本发明一些实施例的所述步骤s1中,单次所述离子注入处理中,离子注入剂量为3

×

10

17-2

×

10

18

离子/平方厘米,能够相应调节形成的所述离子注入层51的厚度为200-400纳米。

[0111]

本发明一些实施例的所述步骤s1中,离子注入完成后,将形成的衬底放入管式炉

中退火,并控制退火温度为1000-1350摄氏度,退火时间为1-4小时,使注入的氧离子与衬底的硅发生反应以形成所述离子注入层51。

[0112]

本发明一些实施例的所述步骤s1中,所述离子注入处理采用的离子为氧离子,所述离子注入层51的组成材料为氧化硅。

[0113]

本发明一些实施例的所述步骤s1中,所述离子注入处理采用的离子为氮离子,所述离子注入层51的组成材料为氮化硅。

[0114]

图6为对图5所示的衬底进行刻蚀后形成的衬底的剖视图。本发明一些实施例的所述步骤s1中,参照图5和图6,所述离子注入处理完成后,刻蚀所述离子注入层51以形成所述凹陷部23,从而得到开孔衬底6。刻蚀的具体实现方式为本领域技术人员的常规技术手段,在此不做赘述。

[0115]

本发明一些实施例中,采用氢氟酸作为刻蚀剂刻蚀组成材料为氧化硅的所述离子注入层51。

[0116]

本发明一些实施例中,采用热磷酸作为刻蚀剂刻蚀组成材料为氮化硅的所述离子注入层51。

[0117]

图7为对图6所示的衬底进行第一沉积处理后形成的衬底的剖视图。

[0118]

本发明一些实施例的所述步骤s2中,参照图6和图7,对所述开孔衬底6的所述第一衬底表面211以及内表面62进行第一沉积处理,以形成顺次堆叠设置的第一原始隔离层71、第一原始扩散阻挡层72、第一原始籽晶层73和第一原始导体层74。

[0119]

具体的,所述第一原始隔离层71的两个相对表面中的一个覆盖所述第一衬底表面211以及所述内表面62,所述第一原始隔离层71、所述第一原始扩散阻挡层72、所述第一原始籽晶层73和所述第一原始导体层74之间的堆叠关系请参见前述所述第一隔离层241、所述第一扩散阻挡层261、所述第一籽晶层262和所述第一导体层263之间的堆叠关系,在此不做赘述。

[0120]

本发明一些实施例的所述步骤s2中,所述第一原始隔离层71、所述第一原始扩散阻挡层72和所述第一原始籽晶层73中任意一种采用物理气相沉积、化学气相沉积、原子层沉积和脉冲激光沉积中的至少一种方法形成,具体的实现方式为本领域技术人员的常规技术手段,在此不做赘述。

[0121]

本发明一些实施例的所述步骤s2中,所述第一原始导体层74采用电镀法形成,具体的实现方式为本领域技术人员的常规技术手段,在此不做赘述。

[0122]

图8为对图7所示的衬底进行第二沉积处理后形成的衬底的剖视图。

[0123]

本发明一些实施例的所述步骤s2中,参照图8,对所述第一原始导体层74的表面进行第二沉积处理,以形成顺次堆叠设置的第二原始隔离层81、第二原始扩散阻挡层82、第二原始籽晶层83以及第二原始导体层84。

[0124]

具体的,所述第二原始隔离层81、所述第二原始扩散阻挡层82、所述第二原始籽晶层83以及所述第二原始导体层84之间的堆叠关系请参见前述所述第二隔离层242、所述第二扩散阻挡层271、所述第二籽晶层272和所述第二导体层273之间的堆叠关系,在此不做赘述。

[0125]

参照图7和图8,所述第二原始隔离层81、所述第二原始扩散阻挡层82、所述第二原始籽晶层83以及所述第二原始导体层84形成的堆叠结构与所述第一原始隔离层71、所述第

一原始扩散阻挡层72、所述第一原始籽晶层73和所述第一原始导体层74形成的堆叠结构填充开孔衬底(图中未标示)的内部。

[0126]

本发明一些实施例的所述步骤s2中,所述第二原始隔离层81、所述第二原始扩散阻挡层82和所述第二原始籽晶层83中任意一种采用物理气相沉积、化学气相沉积、原子层沉积和脉冲激光沉积中的至少一种方法形成,具体的实现方式为本领域技术人员的常规技术手段,在此不做赘述。

[0127]

本发明一些实施例的所述步骤s2中,所述第二原始导体层84采用电镀法形成,具体的实现方式为本领域技术人员的常规技术手段,在此不做赘述。

[0128]

图9为对图8所示的衬底进行第一去除处理后形成的衬底的剖视图。本发明一些实施例的所述步骤s2中,参照图8和图9,通过第一去除处理去除沉积于所述第一衬底表面211的所述第二原始扩散阻挡层82、所述第二原始籽晶层83以及所述第二原始导体层84,以使朝向第一衬底表面211沉积的所述第二原始隔离层81的顶部与形成的第二去除导体层91顶部齐平。

[0129]

本发明一些实施例的所述步骤s2中,采用化学机械抛光的方式进行所述第一去除处理,具体的实现方式为本领域技术人员的常规技术手段,在此不做赘述。

[0130]

图10为对图9所示的衬底进行第二去除处理后形成的衬底的剖视图。本发明一些实施例的所述步骤s2中,参照图9和图10,对所述第二原始隔离层81进行第二去除处理,以形成具有若干第一镂空区域(图中未标示)的第二镂空隔离层101,使所述第一原始导体层74通过所述若干第一镂空区域(图中未标示)暴露出来。

[0131]

本发明一些实施例的所述步骤s2中,采用光刻和刻蚀工艺进行所述第二去除处理,具体的实现方式为本领域技术人员的常规技术手段,在此不做赘述。

[0132]

图11为对图10所示的衬底进行第三沉积处理后形成的衬底的剖视图。本发明一些实施例的所述步骤s2中,参照图11,通过第三沉积处理在所述第二镂空隔离层101的表面形成顺次堆叠的第一原始粘附层111和第三原始籽晶层112。

[0133]

本发明一些实施例的所述步骤s2中,采用物理气相沉积工艺进行所述第三沉积处理。

[0134]

本发明一些实施例的所述步骤s2中,所述第一原始粘附层111和所述第三原始籽晶层112中的任意一种采用化学气相沉积、电子束蒸发和脉冲激光沉积中的任意一种方式形成。

[0135]

图12为对图11所示的衬底进行第一顶部处理后形成的衬底的剖视图。本发明一些实施例的所述步骤s2中,参照图12,采用物理气相沉积工艺在所述第三原始籽晶层112顶部沉积镍薄膜(图中未标示)后,再通过光刻和刻蚀工艺形成具有若干第二镂空区域(图中未标示)的镂空镍薄膜121,以完成所述第一顶部处理。所述第三原始籽晶层112通过所述第二镂空区域(图中未标示)暴露出来。

[0136]

图13为对图12所示的衬底进行第二顶部处理后形成的衬底的剖视图。本发明一些实施例的所述步骤s2中,参照图12和图13,采用电镀工艺在所述第三原始籽晶层112表面电镀导电材料后通过蚀刻去除所述镂空镍薄膜121,部分所述第三原始籽晶层112以及部分所述第一原始粘附层(图中未标示),以形成若干所述第一导通部281以及所述第二导通部282。

[0137]

本发明一些实施例的所述步骤s2中,采用离子铣蚀刻、等离子蚀刻、反应离子蚀刻、激光烧蚀,或者通过使用蚀刻剂溶液的湿法蚀刻去除所述镂空镍薄膜121,部分所述第三原始籽晶层112以及部分所述第一原始粘附层(图中未标示)。

[0138]

图14为对图13所示的衬底底部进行减薄处理后形成的衬底的剖视图。本发明一些实施例的所述步骤s3中,参照图2、图13和图14,采用机械磨削结合化学机械抛光的方法去除图13所示的衬底底部的部分结构,直至获得所需厚度的衬底并形成所述通孔结构22以及所述第二衬底表面212,以完成所述减薄处理。

[0139]

具体的,参照图2、图7至图9以及图14,所述减薄处理去除了所述开孔衬底(图中未标示)底部以及所述第一原始隔离层71、所述第一原始扩散阻挡层72、所述第一原始籽晶层73、所述第一原始导电层74、所述第二原始隔离层81、所述第二原始扩散阻挡层82和所述第二原始籽晶层83中的每一种位于所述开孔衬底(图中未标示)底部的部分,并使所述第二去除导体层91的底部暴露出来,从而形成了所述第一隔离层241、所述第一扩散阻挡层261、所述第一籽晶层262、所述第一导体层263、所述第二隔离层242、所述第二扩散阻挡层271、所述第二籽晶层272以及所述第二导体层273。

[0140]

参照图2和图14,采用化学气相沉积工艺在所述第二衬底表面212沉积隔离膜(图中未标示)后再通过光刻和刻蚀工艺形成所述第三隔离层243,然后再采用与所述第二顶部处理相同的工艺形成所述第三导通部283。

[0141]

本发明实施例还提供了包括若干晶片以及所述半导体衬底2的电子元器件。具体的,所述若干晶片设置于所述半导体衬底2,以实现电互连,使所述通孔结构22不仅能够作为不同晶片之间垂直互连的导电通道,同时还作为电感的基底。

[0142]

虽然在上文中详细说明了本发明的实施方式,但是对于本领域的技术人员来说显而易见的是,能够对这些实施方式进行各种修改和变化。但是,应理解,这种修改和变化都属于权利要求书中所述的本发明的范围和精神之内。而且,在此说明的本发明可有其它的实施方式,并且可通过多种方式实施或实现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1