半导体装置的制作方法

1.本发明涉及半导体装置。

背景技术:

2.作为非易失性的存储装置,公知有通过使电绝缘的浮游电极层亦即浮置栅极内的电荷的积蓄状态变化来进行数据的存储和擦除的非易失性存储器。作为该非易失性存储器的结构,一般是将构成浮置栅极的多晶硅层和构成控制栅极的多晶硅层重叠配置的所谓堆叠型的结构。

3.另一方面,公知有与堆叠型的非易失性存储器不同且使用单层的多晶硅而构成的单层多晶硅型的非易失性存储器(例如,专利文献1)。在单层多晶硅型的非易失性存储器中,例如作为控制栅极发挥功能的第一阱区域、作为读出栅极发挥功能的第二阱区域、以及作为隧道栅极发挥功能的第三阱区域设置在半导体基板的表层部附近。在基板上,以在从第一阱区域到第三阱区域的范围内交叠的方式,形成由栅极绝缘膜和单层的多晶硅构成的浮置栅极。

4.在第一阱区域、第二阱区域和第三阱区域各自的夹着栅极绝缘膜而与浮置栅极对置的部分,形成有与浮置栅极、读出栅极和隧道栅极对应的电容器。而且,通过对控制栅极、读出栅极和隧道栅极分别施加电压,并使浮置栅极的电位变化,来进行数据的写入、擦除等动作。

5.例如,在数据写入时,对控制栅极施加电压vw(vw>0v),对隧道栅极施加0v,对读出栅极施加中间电压vc(0v<vc<vw)。浮置栅极的电位根据施加给控制栅极的电压vw而上升,从第三阱区域(即,隧道栅极)向浮置栅极注入电荷。另一方面,在数据擦除时,对控制栅极施加0v,对隧道栅极施加电压vw,对读出栅极施加中间电压vc。浮置栅极的电位根据施加给控制栅极的电压0v而下降,积蓄于浮置栅极的电荷向第三阱区域移动。

6.专利文献1:日本特开平9-129760号公报。

7.为了高效地进行数据的写入和擦除的动作,优选使控制栅极的电容器的电容相对于读出栅极或隧道栅极的电容器的电容相对地变大,以使浮置栅极的电位接近施加给控制栅极的电压。

8.一般地,平板电容器等电容器的电容与电极的面积成正比。在上述的单层多晶硅型的非易失性存储器中,浮置栅极与控制栅极交叠的部分的面积相当于控制栅极的电容器的电容的“电极的面积”。因此,若要增大控制栅极的电容器的电容,则需要增大与浮置栅极交叠的控制栅极的面积(即,与半导体基板平行的方向上的第一阱区域的面积),结果为存在存储单元的单位面积变大这样的问题。

技术实现要素:

9.本发明是鉴于上述问题点而完成的,目的在于提供小面积且具有充分的电容的非易失性存储器。

10.本发明的半导体装置构成非易失性存储器,其特征在于,具有:第一导电型的半导体部;第二导电型的第一阱,其与上述第一导电型相反极性,形成为从上述半导体部的1个面内的第一区域朝向内部延伸;上述第二导电型的第二阱,其形成为从上述第一区域分离而从上述半导体部的上述1个面内的第二区域朝向内部延伸;绝缘膜,其形成在上述1个面上;以及导电层,其形成为跨越上述绝缘膜上的上述第一阱的上方的区域和上述第二阱的上方的区域而延伸,在上述第一阱形成有从上述1个面向上述第一阱内伸长的沟槽,上述绝缘膜在上述沟槽的内部的表面上延伸,在上述沟槽的内部的上述绝缘膜上以填埋上述沟槽的方式设置有与上述导电层连续地形成的导电部。

11.另外,本发明的半导体装置构成非易失性存储器,其特征在于,具有:第一导电型的半导体部;第二导电型的第一阱,其与上述第一导电型相反极性,形成为从上述半导体部的1个面内的第一区域朝向内部延伸;上述第二导电型的第二阱,其形成为从上述第一区域分离而从上述半导体部的上述1个面内的第二区域朝向内部延伸;绝缘膜,其形成在上述1个面上;以及导电层,其形成为跨越上述绝缘膜上的上述第一阱的上方的区域和上述第二阱的上方的区域而延伸,上述绝缘膜具有:第一区域,其以位于上述第一阱的上方的方式延伸而具有第一膜厚;以及第二区域,其具有比上述第一膜厚厚的第二膜厚。

12.根据本发明的半导体装置,能够在非易失性存储器中维持存储单元的电容,并且减小面积。

附图说明

13.图1是示出本发明的实施例1的半导体装置的结构的俯视图。

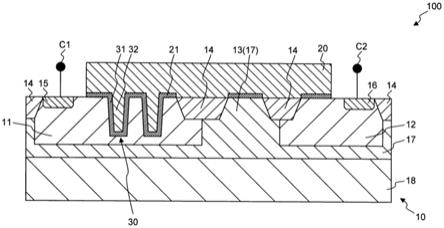

14.图2是图1的半导体装置的沿着x-x线的剖视图。

15.图3是示出半导体装置的制造顺序的流程图。

16.图4a是表示半导体层形成工序中的x-x线的剖面的剖视图。

17.图4b是表示元件分离层形成工序中的x-x线的剖面的剖视图。

18.图4c是表示阱形成工序中的x-x线的剖面的剖视图。

19.图4d是表示蚀刻工序中的x-x线的剖面的剖视图。

20.图5a是表示沟槽形成工序中的x-x线的剖面的剖视图。

21.图5b是表示沟槽内氧化膜形成工序中的x-x线的剖面的剖视图。

22.图5c是表示沟槽内导电部形成工序中的x-x线的剖面的剖视图。

23.图5d是表示栅极氧化膜形成工序中的x-x线的剖面的剖视图。

24.图6a是表示栅极多晶硅形成工序中的x-x线的剖面的剖视图。

25.图6b是表示扩散层形成工序中的x-x线的剖面的剖视图。

26.图6c是表示接触形成工序中的x-x线的剖面的剖视图。

27.图7是示出本发明的实施例2的半导体装置的结构的俯视图。

28.图8是图7的半导体装置的沿着x-x线的剖视图。

29.图9a是表示变形例的半导体基板准备工序中的x-x线的剖面的剖视图。

30.图9b是表示变形例的元件分离层形成工序中的x-x线的剖面的剖视图。

31.图9c是表示变形例的n阱形成工序中的x-x线的剖面的剖视图。

32.图9d是表示变形例的p阱形成工序中的x-x线的剖面的剖视图。

33.图10是实施例1的变形例的半导体装置的沿着x-x线的剖视图。

34.图11是实施例2的变形例的半导体装置的沿着x-x线的剖视图。

35.附图标记的说明

36.100

…

半导体装置;10

…

半导体基板;11

…

第一阱;12

…

第二阱;13

…

第三阱;14

…

元件分离区域;15

…

扩散层;16

…

扩散层;17

…

半导体层;18

…

硅基板;20

…

栅极多晶硅;21

…

栅极氧化膜;23

…

选择晶体管;30

…

沟槽;31

…

沟槽内绝缘膜;32

…

沟槽内导电部;40

…

抗蚀剂膜;200

…

半导体装置;21a

…

第一区域;21b

…

第二区域;300、400

…

半导体装置;50

…

半导体基板。

具体实施方式

37.以下详细地对本发明的优选的实施例进行说明。此外,在以下的各实施例的说明和附图中,对实质上相同或者等价的部分标注相同的参照附图标记。

38.【实施例1】

39.图1是从元件形成面的上方观察本实施例的半导体装置100的俯视图。

40.半导体装置100具有:半导体基板10;以及以在半导体基板10的1个面(即,元件搭载面)露出的方式形成在半导体基板10的内部的第一阱11、第二阱12和第三阱13。另外,在半导体基板10的上述1个面上,以覆盖第一阱11、第二阱12和第三阱13各自的一部分的方式形成栅极多晶硅20。

41.半导体基板10由例如si(硅)基板构成,在俯视观察时具有长方形的形状。

42.第三阱13是第一导电型(例如,p型)的阱区域。另一方面,第一阱11和第二阱12是与第一导电型相反极性的第二导电型(例如,n型)的阱区域。

43.在半导体基板10的1个面露出的第一阱11的表面(以下,简称为第一阱11的表面)在俯视观察时具有矩形的形状。

44.在第一阱11形成有第二导电型的扩散层15。扩散层15在第一阱11的表面露出。由钨等导电体构成的触点c1与扩散层15连接。扩散层15和触点c1形成在第一阱11的表面的未被栅极多晶硅20覆盖的区域。即,扩散层15和触点c1在半导体基板10的1个面露出。

45.在第一阱11的表面形成有沟槽30。第一阱11的表面上的沟槽30(即,沟槽30的开口部)如图1中虚线所示的那样,具有在俯视观察时沿半导体基板10的短边方向具有长边的长方形(即,具有沿半导体基板10的长边方向延伸的短边的长方形)的形状。此外,在本实施例中,以2个沟槽30形成在第一阱11的情况为例而示出。

46.沟槽30形成于第一阱11的表面的被栅极多晶硅20覆盖的部分。即,沟槽30的开口部被栅极多晶硅20覆盖。

47.第二阱12在半导体基板10的长边方向上与第一阱11分离地形成。在半导体基板10的1个面露出的第二阱12的表面(以下,简称为第二阱12的表面)在俯视观察时具有矩形的形状。

48.在第二阱12形成有第二导电型的扩散层16。扩散层16在第二阱12的表面露出。由钨等导电体构成的触点c2与扩散层16连接。扩散层16和触点c2形成于第二阱12的表面的未被栅极多晶硅20覆盖的区域。即,扩散层16和触点c2在半导体基板10的1个面露出。

49.第三阱13形成在第一阱11与第二阱12之间的区域。在半导体基板10的1个面露出

的第三阱13的表面具有在俯视观察时具有沿半导体基板10的短边方向伸长的长边的长方形(即,具有沿半导体基板10的长边方向伸长的短边的长方形)的形状。

50.由钨等导电体构成的触点c3和c4与第三阱13连接。触点c3和c4形成于第三阱13的表面的未被栅极多晶硅20覆盖的区域。即,触点c3和c4在半导体基板10的1个面露出。

51.栅极多晶硅20是由多晶硅膜构成的单层的导电层。栅极多晶硅20形成为跨越第一阱11和第二阱12且使第一阱11和第二阱12各自的一部分露出。在本实施例中,栅极多晶硅20具有:覆盖第一阱11的表面的一部分的矩形部分;以及以覆盖第三阱13和第二阱12的一部分的方式从该矩形部分延伸的带状部分。

52.另外,以覆盖第三阱13的表面的一部分的方式形成选择晶体管23。选择晶体管23例如被配置为,在俯视观察时具有长方形的形状,第三阱13的在半导体基板10的1个面露出的部分与各自的长边方向正交。

53.图2是沿着图1的x-x线的剖视图。

54.第三阱13由在半导体基板10的表层部形成的第一导电型的半导体层17构成。半导体层17形成为从半导体基板10的1个面朝向内部延伸。

55.半导体层17通过向半导体基板10注入第一导电型的离子而形成。此外,在图2中,将半导体基板10的未被离子注入的部分(即,位于半导体层17的下部的区域)作为硅基板18示出。

56.第一阱11形成在半导体层17的表层部。即,第一阱11形成为从半导体基板10的1个面朝向半导体层17的内部延伸。

57.第二阱12在半导体层17的表层部,形成在与第一阱11分离的位置。与第一阱11同样地,第二阱12形成为从半导体基板10的1个面朝向半导体层17的内部延伸。

58.第三阱13通过由半导体层17的第一阱11与第二阱12夹着的区域而构成。

59.在第一阱11、第二阱12和第三阱13各自之间的区域形成有元件分离区域14。元件分离区域14被设置为具有sti(shallow trench isolation:浅沟槽隔离)结构,包围第一阱11、第二阱12和第三阱13各自的周围。此外,在图1中省略元件分离区域14的图示。

60.扩散层15通过向第一阱11的表面注入第二导电型的杂质(例如,在n型的情况下为磷或者砷)而构成。扩散层16通过向第二阱12的表面注入第二导电型的杂质而构成。

61.在栅极多晶硅20与第一阱11、第二阱12和第三阱13的表面之间形成有栅极绝缘膜21。栅极绝缘膜21例如由硅氧化膜构成。栅极绝缘膜21形成为覆盖第三阱13以及第一阱11和第二阱12各自的一部分。

62.此外,栅极多晶硅20的侧壁被由硅氧化膜等绝缘膜构成的侧壁(未图示)覆盖。

63.如图2所示,沟槽30在剖面观察时,从第一阱11的与栅极多晶硅20对置的面朝向第一阱11的内部伸长。例如,沟槽30在剖面观察时具有将第一阱11的深度方向(即,与第一阱11的表面垂直的方向)作为高度方向的梯形的形状。例如,若将半导体基板10的长边方向上的沟槽30的宽度(参照图1)设为几百nm~几μm,则沟槽30形成为在与半导体基板10的1个面垂直的方向上成为约20μm的深度。

64.在沟槽30的内部的表面上,与栅极绝缘膜21连续地形成的沟槽内绝缘膜31沿着沟槽30的形状形成。沟槽内绝缘膜31由与栅极绝缘膜21相同的材料(即,在本实施例中为硅氧化膜)构成。

65.另外,以填埋沟槽30的方式形成有与栅极多晶硅20连续地形成的沟槽内导电部32。沟槽内导电部32由与栅极多晶硅20相同的材料(即,多晶硅)构成。沟槽30、沟槽内绝缘膜31和沟槽内导电部32作为一体而构成沟槽电容器。

66.半导体装置100是构成单层多晶硅型的非易失性的半导体存储器的存储单元。栅极多晶硅20是构成该存储单元的浮置栅极的导电层。

67.另外,第一阱11是作为对该存储单元进行数据的写入和擦除时的控制栅极而发挥功能的阱区域。第二阱12是作为对该存储单元进行数据的写入和擦除时的隧道栅极而发挥功能的阱区域。第三阱13是作为从该存储单元进行数据的读出时的读出栅极而发挥功能的阱区域。

68.例如,在数据写入时对触点c1施加电压vw(vw>0v),对触点c2施加0v。由此,栅极多晶硅20成为接近电压vw的电位,从第二阱12向栅极多晶硅20注入电荷。另一方面,在数据擦除时对触点c1施加0v,对触点c2施加电压vw。由此,栅极多晶硅20成为接近0v的电位,电荷从栅极多晶硅20向第二阱12移动。栅极绝缘膜21作为栅极多晶硅20与第二阱12之间的电荷移动中的隧道氧化膜而发挥功能。

69.此外,在数据写入时和数据擦除时,对与第三阱13连接的触点c3和c4施加中间电压vc(0<vc<vw)。另外,在数据读出时,与栅极多晶硅20中的电荷的积蓄状态对应的读出电流向第三阱13流动。

70.本实施例的半导体装置100中,如上述那样在第一阱11设置有沟槽30,与沟槽内绝缘膜31和沟槽内导电部32一同构成沟槽电容器。因此,半导体装置100与例如控制栅极的电容为相同程度且不具有沟槽电容器的其他的非易失性存储单元相比,存储单元整体的面积较小。对此,以下进行说明。

71.通常,若将电容器电容设为c、将介电常数设为ε、将电极间距离设为d、将电极面积设为a,则平行平板电容器的电容如下面的数学式(数学式1)所示。

72.【数学式1】

[0073][0074]

在本实施例的半导体装置100的单层多晶硅型的存储单元中,若将控制栅极的电容器电容设为c,则作为控制栅极的第一阱11与作为浮置栅极的栅极多晶硅20夹着栅极绝缘膜21而对置的部分的面积相当于电极面积a。因此,第一阱11与栅极多晶硅20夹着栅极绝缘膜21而对置的部分的面积越大,则控制栅极的电容器电容越大。

[0075]

在本实施例的半导体装置100中,在第一阱11的与栅极多晶硅20对置的区域设置有沟槽,该部分为立体结构,因此与未设置沟槽30的情况相比,第一阱11与栅极多晶硅20的对置面积较大。因此,控制栅极的电容器电容相对较大。

[0076]

假设在第一阱11的与栅极多晶硅20对置的区域未设置沟槽的结构中,要想实现与本实施例的半导体装置100同等的控制栅极的电容器电容,则需要将第一阱11和栅极多晶硅20沿水平方向进一步延伸而增加对置的部分的面积。因此,存储单元整体的尺寸会变大。

[0077]

与此相对,根据本实施例的半导体装置100,电极面积a增大了与沟槽30相应的量,不需要增加水平方向的面积,因此能够维持控制栅极的电容器电容,并且将存储器尺寸抑制得小。

[0078]

另外,能够使控制栅极的电容器电容相对于读出栅极或隧道栅极的电容器电容相对较大,因此能够使浮置栅极的电位成为接近施加给控制栅极的电压的值。因此,在数据的写入和擦除的动作中,能够充分地进行浮置栅极与隧道栅极之间(即,栅极多晶硅20与第二阱12之间)的电子的移动。

[0079]

接下来,按照图3所示的制造流程对本实施例的半导体装置100的制造方法进行说明。

[0080]

首先,如图4a所示,通过离子注入法来在半导体基板10的表层部形成第一导电型的半导体区域。由此,形成第一导电型的半导体层17(步骤101)。

[0081]

接下来,如图4b所示,通过蚀刻来在半导体层17的表面形成槽,在包含槽的半导体基板10的表面整体通过cvd(chemical vapor deposition)法形成sio2等绝缘膜。由此,形成元件分离区域14(步骤102)。

[0082]

接下来,如图4c所示,在半导体层17的表面形成通过光刻进行图案化的抗蚀剂膜40。然后,通过离子注入来向半导体层17的表面注入作为第二导电型(在本实施例中为n型)的杂质的例如p+(磷)或者as+(砷)。由此,形成具有第二导电型的第一阱11和第二阱12(步骤103)。

[0083]

接下来,如图4d所示,对表面整体进行蚀刻,除去元件分离区域14以外的半导体基板10的表面的绝缘膜。由此,第一阱11和第二阱12的表面露出(步骤104)。

[0084]

接下来,如图5a所示,对第一阱11的表面进行蚀刻,形成沟槽30(步骤105)。

[0085]

接下来,如图5b所示,通过热氧化法来形成覆盖沟槽30的内部的硅氧化膜(即,沟槽内绝缘膜31)(步骤106)。

[0086]

接下来,如图5c所示,通过cvd法来在沟槽30的内部形成沟槽内导电部32(步骤107)。

[0087]

接下来,通过热氧化法来形成硅氧化膜以覆盖第三阱13以及第一阱11和第二阱12各自的一部分。然后,通过蚀刻来除去沟槽内导电部32的上表面的硅氧化膜。由此,如图5d所示,形成具有与在步骤105中形成的沟槽内绝缘膜31连续的形状的栅极绝缘膜21(步骤108)。

[0088]

接下来,通过cvd法来在栅极氧化膜21的表面形成多晶硅膜。由此,如图6a所示,形成栅极多晶硅20(步骤109)。

[0089]

接下来,如图6b所示,在经过了上述工序的晶片的表面通过光刻来形成图案化的抗蚀剂膜40。然后,通过离子注入,向第一阱11和第二阱12的表面注入作为第二导电型(在本实施例中为n型)的杂质的例如p+(磷)或者as+(砷)。由此,形成第二导电型的扩散层15和扩散层16(步骤110)。

[0090]

接下来,在经过了上述工序的晶片的表面形成接触孔,通过钨等导电体来填埋该接触孔。由此,如图6c所示,形成触点c1和c2(步骤111)。

[0091]

经过以上的工序,制造半导体装置100。

[0092]

像上述那样,在本实施例的半导体装置100中,在构成控制栅极的第一阱11设置有沟槽30,能够使控制栅极与浮置栅极对置的部分的面积增大与沟槽30相应的量。因此,与不具有沟槽30这样的槽的情况相比,能够减小控制栅极和浮置栅极的与基板表面水平的方向的面积。因此,根据本实施例的半导体装置100,能够提供小面积且具有充分的电容的非易

失性存储器。

[0093]

【实施例2】

[0094]

接下来,对本发明的实施例2进行说明。图7是从元件形成面的上方观察本实施例的半导体装置200的俯视图。图8是沿着图7的x-x线的剖视图。

[0095]

本实施例的半导体装置200与图1和图2所示的实施例1的半导体装置100不同,在第一阱11未形成沟槽30。另一方面,在本实施例的半导体装置200中,与实施例1的半导体装置100不同,在栅极绝缘膜21形成有膜厚相对薄的第一区域21a和膜厚相对厚的第二区域21b。

[0096]

第一区域21a形成于第一阱11与栅极多晶硅20夹着栅极绝缘膜21对置的位置。第一区域21a的膜厚比实施例1的半导体装置100的栅极绝缘膜21的膜厚薄。与此相对,第二区域21b具有与实施例1的半导体装置100的栅极绝缘膜21相同程度的膜厚。

[0097]

本实施例的半导体装置100在构成控制栅极的第一阱11与构成浮置栅极的栅极多晶硅20对置的位置设置有栅极绝缘膜21的膜厚薄的第一区域21a,因此与控制栅极的电容为相同程度且不具有这样的膜厚薄的区域的存储单元相比,存储单元整体的面积较小。对此,以下进行说明。

[0098]

如实施例1中说明的那样,若将电容器电容设为c、将介电常数设为ε、将电极间距离设为d、将电极面积设为a,则平行平板电容器的电容如上述的数学式(数学式1)那样表示。

[0099]

在本实施例的半导体装置200这样的单层多晶硅型的存储单元中,若将控制栅极的电容器电容设为c,则构成控制栅极的第一阱11与构成浮置栅极的栅极多晶硅20夹着栅极绝缘膜21对置的部分的距离相当于电极间距离d。因此,第一阱11与栅极多晶硅20的距离越短(即,d值较小),则控制栅极的电容器电容越大。

[0100]

在本实施例的半导体装置100中,在第一阱11与栅极多晶硅20对置的部分,设置有栅极绝缘膜21的膜厚薄的区域即第一区域21a,与不具有这样的区域的情况相比,第一阱11与栅极多晶硅20的距离较短。因此,控制栅极的电容器电容相对较大。

[0101]

假设在栅极绝缘膜21未设置膜厚薄的区域的结构(即,栅极绝缘膜21的整体为与本实施例的第二区域21b同等的膜厚的结构)中,要想实现与本实施例的半导体装置200同等的控制栅极的电容器电容,则需要增加使第一阱11和栅极多晶硅20沿水平方向进一步延伸而对置的部分的面积。因此,存储单元整体的尺寸会变大。

[0102]

与此相对,根据本实施例的半导体装置200,电极间距离d的值较小,不需要增大电极面积a,因此能够维持控制栅极的电容器电容,并且将存储器尺寸抑制得小。

[0103]

本实施例的半导体装置200的栅极绝缘膜21能够通过在形成具有第二区域21b的膜厚的硅氧化膜,并除去该一部分的区域之后,在该一部分的区域重新形成具有第一区域21a的膜厚的硅氧化膜而形成。

[0104]

即,首先通过热氧化法,在第一阱11的表面、第二阱12和第三阱13的表面上以成为比较厚的膜厚(即,第二区域21b的膜厚)的方式形成硅氧化膜。然后,通过蚀刻来除去对该硅氧化膜的第一阱11的表面进行覆盖的部分。然后,通过热氧化法,在该部分以成为比较薄的膜厚(即,第一区域21a的膜厚)的方式重新形成硅氧化膜。

[0105]

如以上那样,在本实施例的半导体装置100中,在构成控制栅极的第一阱11与构成

浮置栅极的栅极多晶硅20对置的部分,形成栅极绝缘膜21的膜厚薄的区域。因此,与不具有膜厚薄的区域的情况相比,能够减小控制栅极和浮置栅极的与基板表面水平的方向的面积。因此,根据本实施例的半导体装置200,能够提供小面积且具有充分的电容的非易失性存储器。

[0106]

此外,本发明不限于上述实施例所示的内容。例如,在上述实施例1中,以沟槽30为在俯视观察时具有长方形的形状的沟槽(即,槽)的情况为例进行了说明,但沟槽30的形状不限于此。例如,也可以形成为在俯视观察时具有圆形或椭圆形等形状的凹坑。另外,沟槽30的剖面观察时的形状或例示的尺寸也不限于上述实施例中示出的内容。总之,只要以使第一阱11与栅极多晶硅20夹着栅极绝缘膜21而对置的部分的面积变大的方式在第一阱11的表面形成立体结构即可。

[0107]

另外,在上述实施例1中,以在第一阱11形成2个沟槽30的情况为例进行了说明,但沟槽的数量不限于此。即,沟槽的数量也可以为1个,也可以为3个以上。另外,在形成多个沟槽的情况下,它们可以是相同的形状也可以是相互不同的形状。

[0108]

另外,第一阱11、第二阱12和第三阱13的俯视观察时的形状不限于上述实施例中示出的内容。

[0109]

另外,在上述实施例中,以使用由多晶硅构成的导电层即栅极多晶硅20而构成浮置栅极的情况为例进行了说明,但也可以使用由多晶硅以外的具有导电性的其他的材料构成的导电层而构成浮置栅极。同样,也可以由多晶硅以外的导电性材料构成沟槽内导电部32。

[0110]

另外,在上述实施例中,以栅极绝缘膜21和沟槽内绝缘膜31由硅氧化膜构成的情况为例进行了说明,但并不限于此,也可以使用具有绝缘性的其他的材料而构成。

[0111]

另外,上述实施例中示出的制造方法是一例,也可以以与上述不同的工序进行制造。例如,在上述实施例中,对如下的例子进行说明,在半导体基板10的表层部形成具有第一导电型的半导体层17,通过离子注入来形成第二导电型的第一阱11和第二阱12,由此使第一阱11与第二阱12之间的区域成为第一导电型的第三阱。但是,也可以与之不同,不形成半导体层17而通过离子注入形成第三阱13。

[0112]

图9a~图9d是这样的第三阱13形成之前的制造方法的变形例的各工序中的半导体基板10的剖视图。

[0113]

首先,如图9a所示,准备第一导电型的半导体基板50(例如,p型的si基板)。然后,如图9b所示,在半导体基板50的表面利用蚀刻形成槽,使用cvd法来在包含槽的半导体基板50的表面整体形成sio2等绝缘膜,由此形成元件分离区域14。

[0114]

接下来,如图9c所示,在半导体基板50的表面形成通过光刻进行图案化的抗蚀剂膜40,通过离子注入来向半导体基板50的表面注入第二导电型(n型)的杂质。由此,形成第一阱11和第二阱12。

[0115]

然后,如图9d所示,在第一阱11和第二阱12的上表面形成抗蚀剂膜40,注入第一导电型(p型)的杂质。由此,形成第三阱13。以下的制造工序与在上述实施例1中说明的蚀刻工序(步骤104,图4d)之后的制造工序相同。

[0116]

根据该制造工序,如图10所示,制造如下的半导体装置300,不具有上述实施例1的半导体装置100这样的半导体层17(参照图2),在第一导电型的半导体基板50分别形成第一

阱11、第二阱12和第三阱13。

[0117]

此外,也可以将图9a~图9d的制造工序应用于实施例2。由此,如图11所示,制造如下的半导体装置400,不具有上述实施例2的半导体装置200这样的半导体层17(参照图8),在第一导电型的半导体基板50分别形成第一阱11、第二阱12和第三阱13。

[0118]

另外,上述实施例1和实施例2能够适当地组合。即,也可以构成为,在第一阱11设置沟槽30,并且在第一阱11与栅极多晶硅20对置的区域设置栅极绝缘膜21的膜厚薄的第一区域21a。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1