基于Nitride斜坡刻蚀的VCSEL芯片及其制备方法与流程

基于nitride斜坡刻蚀的vcsel芯片及其制备方法

技术领域

1.本发明涉及gaas基vcsel芯片制造的技术领域,具体而言,本发明涉及基于nitride斜坡刻蚀的vcsel芯片及其制备方法。

背景技术:

2.垂直腔面发射激光器(vertical cavity surface emitting laser,vcsel)有别于led(light emitting diode,发光二极管)和ld(laser diode,激光二极管)等其他光源,具有体积小、圆形输出光斑、单纵模输出、阈值电流小且易集成大面积阵列等优点,被广泛应用于光通信、光互连和光存储等领域。随着科学技术的不断发展,各种各样的vcsel芯片已广泛应用于人们的日常生活、工作以及工业中,为人们的生活带来了极大的便利。

技术实现要素:

3.本申请是基于发明人对以下事实和问题的发现和认识作出的:

4.由于金属薄膜蒸发自身的局限性,蒸发金与基底(gaas或nitride)的粘附力没有溅射金的优异。发明人发现,在vcsel芯片制造的过程中,p电极蒸发金需经过via钝化层开窗,与p面cap层进行p电极欧姆接触。而正常单次涂胶单次曝光且无reflow工艺的光刻条件与吃胶量较低的刻蚀条件下做出的via钝化层开窗,容易出现一次断层,整体形貌较差,极易致使该区域的蒸发金出现断裂的可能。

5.为此,本发明的目的在于提出基于nitride斜坡刻蚀的vcsel芯片及其制备方法。本发明使钝化层nitride开窗的坡度呈现一个平滑斜坡,有效解决p电极蒸发金在该区域断裂的可能。

6.在本发明的一个方面,本发明提出了一种基于nitride斜坡刻蚀的vcsel芯片结构。根据本发明的实施例,该基于nitride斜坡刻蚀的vcsel芯片结构包括:

7.gaas衬底;

8.在所述gaas衬底上依次生长的n接触层、ndbr层、mqw层、氧化层、pdbr层和p接触层;

9.nitride膜,所述nitride膜设置在所述p接触层的表面上,所述nitride膜在所述p接触层上形成呈斜坡状的via开窗;

10.p电极,所述p电极设置在所述呈斜坡状的via开窗处,所述p电极与所述p接触层直接接触。

11.根据本发明上述实施例的基于nitride斜坡刻蚀的vcsel芯片结构,在vcsel芯片的结构中,设置一个呈平滑斜坡状的via开窗,由此保证良好的芯片外观的情形下,使钝化层nitride开窗的坡度呈现一个平滑斜坡,从而有利于p面蒸镀金属爬台,减少p电极金属断线的可能,增加芯片的可靠性。

12.另外,根据本发明上述实施例的基于nitride斜坡刻蚀的vcsel芯片结构还可以具有如下附加的技术特征:

13.在本发明的一些实施例中,所述呈斜坡状的via开窗的斜坡的角度为30

‑

60度。由此,该角度范围的斜坡有利于p面蒸镀金属更好地爬台,减少p电极金属断线的可能,增加芯片的可靠性。

14.在本发明的一些实施例中,所述呈斜坡状的via开窗的斜坡的角度为40

‑

50度。由此,该角度范围的斜坡进一步有利于p面蒸镀金属更好地爬台,减少p电极金属断线的可能,增加芯片的可靠性。

15.在本发明的一些实施例中,所述呈斜坡状的via开窗的斜坡的角度为45度。由此,该角度的斜坡更进一步有利于p面蒸镀金属更好地爬台,减少p电极金属断线的可能,增加芯片的可靠性。

16.在本发明的一些实施例中,所述nitride膜的厚度为。由此,上述范围的nitride膜厚,使芯片出光呈增透效果。

17.在本发明的另一方面,本发明提出了一种制备基于nitride斜坡刻蚀的vcsel芯片的方法,包括:

18.(1)在gaas衬底上按照层状结构依次生长n接触层、ndbr层、mqw层、氧化层、pdbr层、p接触层和nitride膜;

19.(2)采用灰度光刻方法在所述nitride膜上分别制备2

‑

3层呈同心圆台形貌的环形光刻胶,2

‑

3层的所述光刻胶的交界处呈斜坡趋势;

20.(3)对所述光刻胶采用显影后烘以及o

2 plasma处理,以便形成reflow形貌的光刻胶;

21.(4)采用氟基icp刻蚀所述reflow形貌的光刻胶以及环形光刻胶环内的nitride膜,以便得到呈斜坡状的via开窗;

22.(5)在所述呈斜坡状的via开窗处制备p电极金属,以便得到p电极。

23.本发明实施例所述的制备上述的基于nitride斜坡刻蚀的vcsel芯片的方法,在vcsel芯片的生产过程中,制备出呈斜坡状的via开窗;在保证良好的芯片外观的情形下,使nitride刻蚀去胶后为一平滑的斜坡,这有利于p面蒸镀金属爬台,减少p电极金属断线的可能,增加芯片的可靠性。

24.另外,根据本发明上述实施例的制备上述的基于nitride斜坡刻蚀的vcsel芯片的方法还可以具有如下附加的技术特征:

25.在本发明的一些实施例中,所述呈斜坡状的via开窗的斜坡的角度为30

‑

60度。由此,该角度范围的斜坡有利于p面蒸镀金属更好地爬台,减少p电极金属断线的可能,增加芯片的可靠性。

26.在本发明的一些实施例中,所述呈斜坡状的via开窗的斜坡的角度为40

‑

50度。由此,该角度范围的斜坡进一步有利于p面蒸镀金属更好地爬台,减少p电极金属断线的可能,增加芯片的可靠性。

27.在本发明的一些实施例中,所述呈斜坡状的via开窗的斜坡的角度为45度。由此,该角度的斜坡更进一步有利于p面蒸镀金属更好地爬台,减少p电极金属断线的可能,增加芯片的可靠性。

28.在本发明的一些实施例中,所述nitride膜的厚度为。由此,上述范围的nitride膜厚,使芯片出光呈增透效果。

29.在本发明的一些实施例中,所述nitride膜的材料为sin、sio2或sion。

30.在本发明的一些实施例中,所述环形光刻胶的厚度为4.3um

‑

4.5um。

31.在本发明的一些实施例中,在步骤(2)中,制备2层呈同心圆台形貌的环形光刻胶,通过一次涂胶,使用两片光刻版,进行两次曝光。

32.在本发明的一些实施例中,制备第一层光刻胶的曝光能量为100mj

‑

200mj,所述第一层光刻胶的厚度为2.3um

‑

2.7um。

33.在本发明的一些实施例中,制备第二层光刻胶的曝光能量为800mj

‑

1500mj,所述第二层光刻胶的厚度为1.8um

‑

2.2um。

34.在本发明的一些实施例中,所述第二层光刻胶的的宽度为22um

‑

35um。

35.在本发明的一些实施例中,在步骤(3)中,烘烤温度为95

‑

105摄氏度,烘烤时间为150s

‑

200s。

36.在本发明的一些实施例中,在步骤(4)中,所述氟基icp的反应气体包括:30sccm

‑

70sccm的氟基反应气体、30sccm

‑

70sccm的n2、10sccm

‑

50sccm的o2和10sccm

‑

50sccm的ar。

37.在本发明的一些实施例中,所述氟基反应气体为chf3、cf4或sf6。

38.在本发明的一些实施例中,在步骤(4)中,所述氟基icp的腔体压力为0.5pa

‑

1.0pa。

39.在本发明的一些实施例中,在步骤(4)中,所述光刻胶的消耗量与所述nitride膜的刻蚀量的比值为1:1

‑

9:1。

40.在本发明的一些实施例中,所述nitride膜的刻蚀速度为,所述nitride膜的刻蚀时间为15min

‑

60min。

41.在本发明的一些实施例中,所述光刻胶的刻蚀速度为,所述光刻胶的刻蚀时间为15min

‑

60min。

42.本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

43.本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:

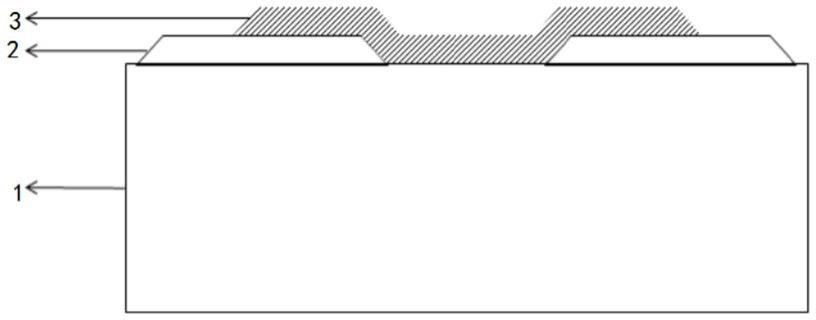

44.图1为本发明实施例的基于nitride斜坡刻蚀的vcsel芯片的结构示意图。

45.图2为本发明实施例1的步骤(b)制备得到的中间vcsel芯片的结构示意图。

46.图3为本发明实施例1的步骤(d)制备得到的中间vcsel芯片的结构示意图。

47.图4为本发明实施例1的步骤(e)制备得到的vcsel芯片p电极欧姆接触区域的结构示意图。

具体实施方式

48.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

49.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

50.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个、四个、五个、六个等,除非另有明确具体的限定。

51.在本发明中,除非另有明确的规定和限定,“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系,除非另有明确的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

52.在本发明中,除非另有明确的规定和限定,第一特征在第二特征“上”或“下”可以是第一和第二特征直接接触,或第一和第二特征通过中间媒介间接接触。而且,第一特征在第二特征“之上”、“上方”和“上面”可是第一特征在第二特征正上方或斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”可以是第一特征在第二特征正下方或斜下方,或仅仅表示第一特征水平高度小于第二特征。

53.在本发明的一个方面,本发明提出了一种基于nitride斜坡刻蚀的vcsel芯片结构。参考图1,根据本发明的实施例,所述基于nitride斜坡刻蚀的vcsel芯片包括gaas基epi外延片1、nitride膜2和p电极3。

54.根据本发明的实施例,参考图1,gaas基epi外延片1包括gaas衬底、n接触层、ndbr层、mqw层、氧化层、pdbr层和p接触层(具体结构在图中均未示出)。所述n接触层、ndbr层、mqw层、氧化层、pdbr层和p接触层按照层状结构依次生长在gaas衬底上。所述ndbr层的作用是形成反射镜,所述mqw层的作用是作为发光区,所述氧化层的作用是限制电流和光,所述pdbr层的作用是形成反射镜,所述p接触层的作用是形成p型欧姆接触。

55.根据本发明的实施例,参考图1,nitride膜2,所述nitride膜2设置在所述p接触层的表面上,所述nitride膜在所述p接触层上形成呈斜坡状的via开窗。所述nitride膜的材料为sin、sio2或sion。

56.进一步地,所述呈斜坡状的via开窗的斜坡的角度为30

‑

60度。由此,该角度范围的斜坡有利于p面蒸镀金属更好地爬台,减少p电极金属断线的可能,增加芯片的可靠性。发明人发现,如果via开窗的斜坡的角度小于30度,则via开窗尺寸会过大,影响芯片设计初衷;如果其斜坡的角度大于60度,则via开窗氮化硅坡度不够,仍有几率出现蒸发金断裂现象。

57.更进一步地,所述呈斜坡状的via开窗的斜坡的角度为40

‑

50度。由此,该角度范围的斜坡进一步有利于p面蒸镀金属更好地爬台,减少p电极金属断线的可能,增加芯片的可靠性。更优选地,所述呈斜坡状的via开窗的斜坡的角度为45度。

58.进一步地,所述nitride膜的厚度为。上述范围的nitride膜厚,使芯片出光呈增透效果。

59.根据本发明的实施例,参考图1,p电极3,所述p电极3设置在所述呈斜坡状的via开窗处,所述p电极与所述p接触层直接接触。

60.根据本发明的实施例,上述基于nitride斜坡刻蚀的vcsel芯片还包括n电极等其他常规部件,该内容属于本领域的常规技术,在此不再赘述。

61.根据本发明上述实施例的基于nitride斜坡刻蚀的vcsel芯片结构,在vcsel芯片的结构中,设置一个呈平滑斜坡状的via开窗,由此保证良好的芯片外观的情形下,使钝化层nitride开窗的坡度呈现一个平滑斜坡,从而有利于p面蒸镀金属爬台,减少p电极金属断线的可能,增加芯片的可靠性。

62.在本发明的另一方面,本发明提出了一种制备上述的基于nitride斜坡刻蚀的vcsel芯片的方法,包括:

63.s1:在gaas衬底上按照层状结构依次生长n接触层、ndbr层、mqw层、氧化层、pdbr层、p接触层和nitride膜。所述nitride膜的材料为sin、sio2或者sion。

64.s2:制备2

‑

3层呈同心圆台形貌的环形光刻胶

65.在该步骤中,采用灰度光刻方法(涂胶+曝光+显影)在所述nitride膜上分别制备2

‑

3层呈同心圆台形貌的环形光刻胶,2

‑

3层的所述光刻胶的交界处呈斜坡趋势。上层光刻胶的宽度略微小于下层光刻胶的宽度,由此形成斜坡趋势。

66.在本发明的实施例中,上述2

‑

3层的所述光刻胶的交界处呈斜坡趋势的角度为40

‑

70度。由此,有利于后续步骤形成30

‑

60度的reflow形貌的光刻胶。

67.在本发明的实施例中,所述环形光刻胶的厚度为4.3um

‑

4.5um。由此,在该厚度范围内,可避免刻蚀过程中,光刻胶消耗殆尽导致的图形受损,亦可避免胶厚过厚导致的光刻线条粗。发明人发现,如果胶厚过低,则刻蚀过程中,高台面区域光刻胶消耗干净,导致图形受损;如果胶厚过厚,则光刻线条会粗,影响产品形貌。

68.根据本发明的一个具体实施例,制备2层呈同心圆台形貌的环形光刻胶,通过一次涂胶,使用两片光刻版,进行两次曝光。进一步地,制备第一层光刻胶的曝光能量为100mj

‑

200mj,所述第一层光刻胶的厚度为2.3um

‑

2.7um,由此,便于形成reflow形貌。进一步地,制备第二层光刻胶的曝光能量为800mj

‑

1500mj,所述第二层光刻胶的厚度为1.8um

‑

2.2um,由此,便于形成reflow形貌。第一层光刻胶的曝光能量(第一层曝光能量)与其所形成的光刻胶的厚度是对应的,光刻胶的曝光能量越大,其对应形成的光刻胶的厚度越大;第二层曝光能量取决于总的胶厚,即初始涂胶厚度。

69.在本发明的实施例中,所述第二层光刻胶的宽度为22um

‑

35um。

70.s3:对所述光刻胶采用显影后烘以及o

2 plasma处理

71.在该步骤中,使用配套的显影后烘条件处理所述光刻胶,使灰度光刻形貌的胶面逐步塌陷,形成reflow形貌斜坡;reflow光刻图形制备完成后,需采用一定功率的o

2 plasma设备打胶,将事先制备完成的reflow形貌光刻胶进行氧处理,去除可能存在的一些棱角,同时去除可能存在的底膜,使整个reflow形貌更为圆滑。

72.在本发明的实施例中,上述reflow形貌的光刻胶的斜坡角度为30

‑

60度,与后续步骤形成的via开窗角度基本一致。

73.根据本发明的一个具体实施例,在该步骤中,烘烤温度为95

‑

105摄氏度,烘烤时间为150s

‑

200s。发明人发现,如果烘烤温度过低或时间过短,都会导致reflow形貌达不到理

想效果;如果烘烤温度过高或时间过久亦会导致reflow形貌达不到理想效果,同时光刻胶收缩过多。

74.s4:采用氟基icp刻蚀所述reflow形貌的光刻胶以及环形光刻胶环内的nitride膜

75.在该步骤中,采用具备氟基反应气体的电感耦合等离子刻蚀设备(icp设备)进行刻蚀所述reflow形貌的光刻胶以及环形光刻胶环内的nitride膜,在nitride刻蚀的同时,快速的消耗光刻胶,使最终nitride刻蚀的形貌与reflow类似,以便得到呈斜坡状的via开窗。

76.根据本发明的一个具体实施例,在该步骤中,上述氟基icp的反应气体包括:30sccm

‑

70sccm的氟基反应气体、30sccm

‑

70sccm的n2、10sccm

‑

50sccm的o2和10sccm

‑

50sccm的ar;其中,氟基反应气体用于刻蚀nitride膜;惰性气体n2用于稀释腔体内氟基反应离子,稳定腔体环境;o2用于消耗光刻胶;ar用于增加物理轰击,增益nitride膜的刻蚀与光刻胶的消耗。进一步地,所述氟基反应气体包括chf3、cf4或者sf6。进一步地,所述氟基icp的腔体压力为0.5pa

‑

1.0pa,其具体数值需要匹配当前机台腔体大小以及总气体量而定。发明人发现,所述氟基icp的腔体压力在上述范围内,可使刻蚀过程中,整个腔体的刻蚀反应更加均匀,整个wafer上nitride与光刻胶的刻蚀深度更加均匀。

77.根据本发明的再一个具体实施例,在该步骤中,所述光刻胶的消耗量与所述nitride膜的刻蚀量的比值为1:1

‑

9:1。由此,在nitride刻蚀的同时,使光刻胶以一定速率被消耗掉,从而制备出与光刻reflow形貌一致的via开窗。在via刻蚀过程中通过光刻胶刻蚀速率、nitride刻蚀速率以及nitride厚度、光刻胶胶厚,精准计算刻蚀量,以减少对gaas基底的损伤。工艺导入阶段前将最终版刻蚀制程的光刻胶刻蚀速率、nitride刻蚀速率经过多次重复试验得到可重复的准确范围,之后:

78.通过公式(1)精准计算出刻蚀时间并适当给出过刻时间(约5%);

79.确认公式(2)光刻胶消耗量=刻蚀时间+过刻时间)

×

光刻胶刻蚀速率,计算出的光刻胶消耗量要低于现有胶厚2um

‑

3um;以避免刻蚀过程中,pia等高台阶区域台面光刻胶胶厚不够,致使pia被刻蚀,影响外观。

80.进一步地,所述nitride膜的刻蚀速度为所述nitride膜的刻蚀时间为15min

‑

60min。所述光刻胶的刻蚀速度为所述光刻胶的刻蚀时间为15min

‑

60min。需要说明书的是,nitride膜的刻蚀时间与光刻胶的刻蚀时间相同,两者同时在腔体内进行刻蚀。

81.s5:在所述呈斜坡状的via开窗处制备p电极金属,以便得到p电极。

82.本发明实施例所述的制备上述的基于nitride斜坡刻蚀的vcsel芯片的方法具有如下优点:

83.(1)在vcsel芯片的生产过程中,制备出呈斜坡状的via开窗;在保证良好的芯片外观的情形下,使nitride刻蚀去胶后为一平滑的斜坡,这有利于p面蒸镀金属爬台,减少p电极金属断线的可能,增加芯片的可靠性。

84.(2)本发明在via刻蚀过程中通过光刻胶刻蚀速率、nitride刻蚀速率以及nitride厚度、光刻胶胶厚,精准计算刻蚀量,减少对gaas基底的损伤。

85.下面详细描述本发明的实施例,需要说明的是下面描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。另外,如果没有明确说明,在下面的实施例中所采用的所有试剂均为市场上可以购得的,或者可以按照本文或已知的方法合成的,对于没有列出的反应条件,也均为本领域技术人员容易获得的。

86.实施例1

87.本实施例提供一种制备基于nitride斜坡刻蚀的vcsel芯片的方法,包括:

88.(a)在gaas衬底上按照层状结构依次生长n接触层(2um)、ndbr层(3.9um)、mqw层(0.5um)、氧化层(0.15um)、pdbr层(3.5um)、p接触层(80nm)和nitride膜(0.6um)。

89.(b)使用一种灰度光刻技术的涂胶+曝光+显影流程,制备出有两层约呈同心圆状圆台的光刻胶4,如图2所示。最上层胶块约2.0um,其光刻胶的曝光能量为150mj;第二层胶块约2.5um,其曝光能量为1200mj;两者交界处非垂直状态,有一斜坡趋势,角度为45度。

90.(c)之后使用配套的显影后烘条件,使灰度光刻形貌的胶面逐步塌陷,形成reflow形貌斜坡,该斜坡的角度为50度。烘烤温度为100摄氏度,烘烤时间为175s。

91.(d)reflow光刻图形制备完成后,需采用功率为350w的o

2 plasma设备,将事先制备完成的reflow形貌光刻胶进行氧处理,去除可能存在的一些棱角,使整个reflow形貌更为圆滑,如图3所示,5为reflow形貌的光刻胶。

92.(e)最后,采用具备氟基反应气体的电感耦合等离子刻蚀设备(icp设备)进行刻蚀所述reflow形貌的光刻胶以及环形光刻胶环内的nitride膜,在nitride刻蚀的同时,快速的消耗光刻胶,使最终nitride刻蚀的形貌与reflow类似,得到呈斜坡状的via开窗,如图4所示。nitride膜经过氟基icp刻蚀后,剩余的光刻胶保护住未被刻蚀到的nitride膜;经过氟基icp刻蚀,表层大部分光刻胶被均匀且快速的吃掉,剩余的一部分reflow光刻胶,在后续的去胶流程中被去除干净。上述氟基icp的反应气体包括:50sccm的氟基反应气体、50sccm的n2、30sccm的o2和30sccm的ar。所述氟基反应气体包括chf3、cf4和sf6。所述氟基icp的腔体压力为0.75pa。

93.(f)在所述呈斜坡状的via开窗处制备p电极金属,以便得到p电极。

94.该实施例在vcsel芯片的生产过程中,制备出呈斜坡状的via开窗;在保证良好的芯片外观的情形下,使nitride刻蚀去胶后为一45度角的斜坡,这有利于p面蒸镀金属爬台,减少p电极金属断线的可能,增加芯片的可靠性。

95.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

96.尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1