一种包含双缓冲层的低电流长寿命忆阻器及其制备方法与流程

1.本发明属于微电子材料器件领域,涉及忆阻器,更具体地,涉及一种包含双缓冲层的低电流长寿命忆阻器及其制备方法。

背景技术:

2.随着当今信息时代的快速发展,高密度、高速度的存储器受到广泛关注。目前主流的商用非易失性存储器主要是闪存(flash)存储器,具有存储容量大、运行速度快、无复杂机械结构的优势,但受自身尺寸的限制,随着工艺尺寸不断缩小将引起漏电流的问题,这限制了其未来的发展,未来信息存储的高容量需求将无法满足。目前看来,有望替代闪存的非易失性存储器主要包括相变存储器、铁电存储器、磁存储器以及忆阻器。其中,忆阻器因其结构简单、擦写速度快、功耗小以及高存储密度的特点被认为是新一代非易失性存储器的候选人之一。

3.目前,人们普遍地认为忆阻的开启和关闭是由电场诱导导电细丝的形成和断裂引起的,实现器件在高阻态与低阻态之间的转变,即分别代表二进制中的“1”和“0”状态,从而完成信息存储功能。然而,由于受器件开启过程中寄生电容的影响,较大过冲电流会使得活性金属离子在介质层内积累,导电通道过度生长,使得器件只能在较大电流下运行。同时循环开关运行,金属离子的过量积累也会导致介质层电阻大幅降低,器件失效,即器件使役寿命降低。如果能解决过冲电流问题以及低限制电流与保持之间的困境,不仅能抑制导电细丝的过度生长而且可以形成稳定的导电细丝,最终达到提高器件阻变性能的目的。

技术实现要素:

4.为了解决以上的问题,本发明在于提出一种包含双缓冲层的低电流长寿命忆阻器及其制备方法。

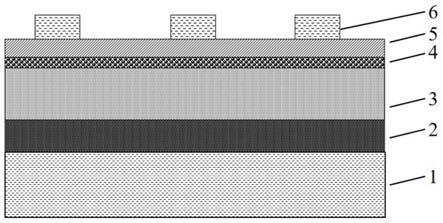

5.所述忆阻器由下至上依次为基片、底电极、介质层、双缓冲层、活性金属顶电极;所述双缓冲层由下至上依次为含有缺陷的二维层状材料和碲基硫系化合物。

6.所述的含有缺陷的二维层状材料为石墨烯、硫化钼、碳化钨、金属碳氮化物(ti3c2t

x

)中的一种,厚度在0.1

‑

2nm;所述的碲基硫系化合物为银铟锑碲、银铟锑碲、锗锑碲、锑化碲中的一种,厚度在5

‑

50nm。

7.所述基片为sio2/si基片,sio2在si上的沉积厚度为300nm左右;所述底电极为惰性金属pt、w、au中的一种;所述介质层为非晶碳、非晶硅、二氧化硅、氧化铪、氧化钽、氧化锌、氧化铝、氮化铝中的一种;所述活性金属顶电极为银、铜、镁中的一种。

8.所述底电极厚度10

‑

100nm;所述介质层厚度20

‑

100nm;所述顶电极厚度10

‑

50nm。

9.所述忆阻器的制备方法,包括:在所述基片依次沉积所述底电极、介质层、双缓冲层、活性金属电极,得到所述忆阻器。所述底电极和顶电极制备方法为热蒸发和磁控溅射中的一种;所述介质层制备方法为磁控溅射、脉冲激光沉积、原子层沉积中的一种;所述双缓冲层中二维层状材料采用湿法或干法转移,所述的碲基硫系化合物采用磁控溅射、脉冲激

光沉积中的一种。

10.与现有技术相比,本发明的有益效果:

11.1.本发明所述的插入双缓冲层提升忆阻器阻变可靠性,其中引入银的双缓冲层,极大抑制了寄生电容导致的过冲电流和导电细丝的过度生长,提高了器件的均一性和耐久性。

12.2.本发明所述的另一缓冲层为带缺陷的不渗透层,二维石墨烯材料具有原子离子不渗透性,离子只能通过缺陷处迁移,局域了导电细丝的位置,形成了稳定的导电细丝,解决了低电流与保持之间的困境。

附图说明

13.图1为本发明的一种包含双缓冲层的低电流长寿命忆阻器结构图;

14.图中:1基片;2底电极;3介质层;4缺陷的二维层状材料;5碲基硫系化合物;6活性金属顶电极。

15.图2为实施例忆阻器的电子扫描显微镜截面图;

16.图3中(a)和(b)分别为有、无缓冲层的两种实施例忆阻器阻变曲线对比;

17.图4中(a)和(b)分别为有、无双缓冲层的实施例忆阻器的使役寿命对比。

具体实施方式

18.下面结合附图对本发明的实施例作详细说明:本实施例在以本发明技术方案为前提下进行实施,但本发明的保护范围不限于下述的实施例。

19.本实施例提供一种包含双缓冲层的低电流长寿命忆阻器及其制备方法。如图1、图2所示,为本实施例中采用的忆阻器si/sio2/pt/a

‑

c/aist/ag结构示意图,本实施例中所述非晶碳忆阻器包含底电极pt、非晶碳(a

‑

c)介质层、双缓冲层为aginsbte和缺陷石墨烯(dg)、顶电极ag。

20.本发明所述的制备方法,包括:

21.所述底电极pt和顶电极ag采用热蒸镀方法制备;

22.更具体的,热蒸镀条件如下:腔室本底真空度大于10

‑4pa;pt丝和ag丝蒸镀材料纯度为99.99%;加热电流分别为90a(pt)和60a(ag);

23.所述a

‑

c层采用磁控溅射方法制备;

24.更具体的,磁控溅射条件如下:腔室本底真空度大于10

‑4pa;石墨靶材纯度为99.99%;工作氛围为纯氩气;溅射气压为1pa;溅射功率为90w;

25.所述dg层采用等离子体轰击制备并利用湿化学法转移至a

‑

c层;

26.更具体的,等离子体轰击条件如下:采用ar等离子体轰击;轰击功率30w;轰击时间6s;湿化学法条件如下:在cu基底上经等离子体轰击后的dg上旋涂质量分数为4%的聚甲基丙烯酸甲酯丙酮溶液,旋涂条件为3600rpm,时间8s,110℃加热15分钟后将其放入质量分数为16.7%的fecl3溶液中去除cu基底,并用去离子水冲洗干净放置a

‑

c层自然风干,将其在130℃加热30min,放入50℃丙酮溶液中去除pmma;

27.所述aginsbte层采用磁控溅射方法制备;

28.更具体的,磁控溅射条件如下:腔室本底真空度大于10

‑4pa;aist靶材纯度为

99.99%;工作氛围为纯氩气;溅射气压为0.5pa;溅射功率为100w。

29.与现有技术相比,本发明的优点在于将包括含有缺陷的二维层状材料和碲基硫系化合物作为双缓冲层插入到活性金属电极银和介质层之间,能够抑制活性离子的过量注入,实现导电通道局域化,有利于降低器件运行电流,提升器件使役寿命。

30.将限制电流设置为10μa,通过源表分别对有无双缓冲层的忆阻器施加正向偏压和反向偏压。如图3中的(a)和(b)所示,在电压扫描过程中,没有双缓冲层器件低电阻态无法保持,显示出易失性。加入双缓冲层器件低阻态能够保持,显示出非易失性存储能力。如图4中的(a)和(b)所示,利用本发明方法测试对比得到循环耐受性得到明显提高,经过2500次循环依旧保持良好的窗口值。

31.以上所述具体实施例,进一步阐明了本发明测试方法操作简便、兼容性好、优化效果显著的优势。本发明适用于忆阻器性能优化,有利于突破忆阻器件集成应用技术壁垒,利于商业化推广实用。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1