一种半导体结构及栅极的制作方法与流程

1.本发明涉及半导体生产工艺领域,特别涉及一种半导体结构及栅极的制作方法。

背景技术:

2.栅极是晶体管中很重要的结构,栅极可以通过制造或者消除源极和漏极之间的沟道,从而允许或者阻碍电子流过。以npn型mos管为例,在半导体硅衬底上,用半导体光刻、扩散工艺制作两个高掺杂浓度的n区,并用金属引出两个电极,分别作为漏极d和源极s。然后在漏极和源极之间的p型半导体表面覆盖一层很薄的介质层(通常为sio2),在这个介质层膜上制作栅极g,这就构成了一个nmos管。目前栅极广泛采用堆叠结构,以增加对沟道的控制或提高驱动电流,堆叠结构包括在栅介质层上形成的多晶硅和多层金属,顶层还覆盖有盖层。在多晶硅的沉积过程中会对底部栅介质层产生应力,引起漏电或栅极金属层结合不稳定等问题。

3.为此,提出本发明。

技术实现要素:

4.本发明的主要目的在于提供一种栅极的制作方法,该方法采用非掺杂多晶硅硅层和c&ge掺杂的多晶硅层复合成的材料作为栅极底部的电阻连接,能控制多晶硅晶粒的生长,细化晶粒,降低对底部介质层的机械应力,从而改善器件电特性。

5.本发明的另一目的在于提供一种半导体结构,该结构中的栅极底部的多晶硅采用掺杂和非掺杂复合而成,具有更优异的电特性,并且耗尽问题更轻。

6.为了实现以上目的,本发明提供了以下技术方案。

7.一种半导体结构,包括:

8.半导体衬底,所述半导体衬底设置有源区;所述半导体衬底的有源区设置栅极,所述栅极由栅介质层、第一多晶硅层、第二多晶硅层和金属层依次堆叠而成,并且所述第二多晶硅层掺杂有碳和锗。

9.一种栅极的制作方法,包括:

10.在半导体衬底上形成浅槽隔离,然后在半导体衬底的表面沉积栅介质层;

11.在所述栅介质层表面沉积第一多晶硅层;

12.在所述第一多晶硅层的表面沉积第二多晶硅层,并向所述第二多晶硅层掺杂碳和锗;

13.然后对第二多晶硅层进行n型和/或p型掺杂;

14.沉积金属层和盖层;

15.对所述盖层、金属层、第二多晶硅层、第一多晶硅层和栅介质层进行光刻和刻蚀形成栅极。

16.与现有技术相比,本发明达到了以下技术效果:

17.(1)细化栅极多晶硅晶粒,降低对介质层的机械应力;

18.(2)降低漏电现象,减小耗尽问题;

19.(3)提高栅极金属与多晶硅的接合稳定性。

附图说明

20.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。

21.图1为本发明提供的栅极的堆叠结构示意图;

22.图2为不同碳掺杂量的多晶硅的x射线分析结果;

23.图3为锗硅的晶粒电镜图;

24.图4为锗硅掺杂碳的晶粒电镜图;

25.图5为不同掺杂的多晶硅及非晶硅的拉应力大小比较示意图;

26.图6至13为本发明实施例1提供的cmos晶体管制作过程中每步工序得到的形貌图。

具体实施方式

27.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

28.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

29.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

30.以cmos晶体管为例,其栅极为如图1所示的堆叠结构(图1截取了器件的部分结构)。

31.cmos晶体管可用于计算机信息存储、数字影像、集成电路等领域,组成的器件包括典型的dram、闪存、pcram、mram、3d nand、图像传感器等。这些器件中的cmos晶体管都包含栅极、源漏极等基本结构。

32.图1所示栅极制成的cmos晶体管可用于上述的任意器件。该栅极制作于硅衬底101的有源区(各个有源区通过浅沟槽隔离),硅衬底101可以是用以承载半导体集成电路组成元件的底材,例如绝缘体上硅(silicon-on-insulator,soi)、体硅(bulk silicon)(包括单抛片或双抛片,双抛片更有助于降低晶圆后续应力变化)、锗硅等。

33.在硅衬底101的表面形成有栅介质层102。栅介质层102用于隔离栅极和衬底,可采用氧化硅sio2或金属氧化物(例如ta2o5、tio2、tin、al2o3、pr2o3、la2o3、laalo3、hfo2、zro2等高k介质材料),优选采用氧化硅,典型的形成方法是将硅衬底101的浅表层热氧化成氧化

硅,作为栅介质层。

34.栅介质层102的表面形成有第一多晶硅层103。第一多晶硅层103的沉积方式包括但不限于lpcvd、rtcvd或者pecvd;第二层多晶硅要同步掺杂碳c和锗ge,优选采用lpcvd沉积,更合适的沉积温度为400~550℃(更优选400~500℃),硅源可以是甲硅烷、二氯甲硅烷、乙硅烷、二异丙基氨基硅烷,双(叔丁基氨基)硅烷,双(二乙基胺基)硅烷,六氯乙硅烷,三(二甲基氨基)硅烷,丁基氨基硅烷、二乙基氨基硅烷、二丙基氨基硅烷、六乙基胺基乙硅烷等典型硅源,优选甲硅烷sih4或乙硅烷si2h6。

35.第一多晶硅层103的表面形成有第二多晶硅层104。第二多晶硅层104中掺杂有碳和锗,这样可以减小对栅介质层的应力。如图2所示的x射线分析结果(四条曲线的碳掺杂量由上至下增加),随着碳掺杂量增加,晶粒逐渐细化。在柱状晶粒的锗硅(如图3所示)中注入碳后,晶粒变化为如图4所示的细小晶粒,对栅介质层(指氧化硅)的应力变化如图5所示,大大减小。可见,向多晶硅中掺杂碳和锗可以细化晶粒,从而减少其对栅介质层的应力,改善绝缘性。

36.第二多晶硅层104中掺杂碳和锗的方式是多样的,例如离子注入、高温分解吸附等,可以同步或分步掺杂,优选同步掺杂。同步掺杂时,考虑多晶硅沉积和碳、锗掺杂的多种化学反应要同步进行,需要选择更合适的工艺条件。具体地,掺杂所用的碳源优选选用c2h4或sih3ch3,这些原料在高温下课分解生产碳、硅,以c2h4为例,其反应式如下:

37.c2h4→

2c+2h2。

38.所用的锗源包括geh4或ge2h6,在硅沉积的同时,锗源高温分解生产锗。

39.第二多晶硅层104的沉积方式包括但不限于lpcvd、rtcvd或者pecvd;第二层多晶硅要同步掺杂碳c和锗ge,优选采用lpcvd沉积,更合适的沉积温度为400~550℃(更优选400~500℃),硅源可以是甲硅烷、二氯甲硅烷、乙硅烷、二异丙基氨基硅烷,双(叔丁基氨基)硅烷,双(二乙基胺基)硅烷,六氯乙硅烷,三(二甲基氨基)硅烷,丁基氨基硅烷、二乙基氨基硅烷、二丙基氨基硅烷、六乙基胺基乙硅烷等典型硅源,优选甲硅烷sih4或乙硅烷si2h6。

40.第二多晶硅层104中锗和碳的掺杂量对电特性也有显著影响,为获得良好的电特性,第二多晶硅层104中碳的掺杂量优选为多晶硅的2~7%(摩尔比)(以第二多晶硅层中的多晶硅为基准),锗的掺杂量优选为多晶硅的20~40%(摩尔比)。

41.另外,为了提高栅极各层见的结合力,以及减小应力,所述第一多晶硅层的厚度优选为所述第二多晶硅层的厚度优选为

42.还可以对第二多晶硅层104进行n型或p型掺杂,以改良电阻。如果在后续多晶硅的n型或p型掺杂之后进行快速热处理(rtn),除了能激活掺杂离子外,还能改善掺杂元素的分布均匀性,进一步细化晶粒,改善电特性。rtn适宜的温度范围为850~950℃。

43.第二多晶硅层104的表面依次堆叠有第一金属层105、第二金属层106、第三金属层107和盖层108。

44.栅介质层102、盖层108包括典型的氧化硅sio2或金属氧化物(例如ta2o5、tio2、tin、al2o3、pr2o3、la2o3、laalo3、hfo2、zro2等高k介质材料)。其中,栅介质层102典型的形成方法是将硅衬底101的浅表层热氧化成氧化硅,作为栅介质层。

45.第一金属层105用于与多晶硅的欧姆连接,可选用钛、铝、铝铜合金等金属材料。第

二金属层106用来阻止第三金属层渗透,常采用氮化金属,例如氮化钨、氮化钛等,并且可以是单层结构或多层复合结构。第三金属层107多采用金属钨。

46.图1所示的栅极为柱体状,其制作方法通常是:先分步沉积或氧化等手段形成多层,得到堆叠结构,然后光刻和刻蚀成柱状。但本发明的栅极堆叠结构并不仅限于图1所示的栅极,还适用于掩埋式栅极,即在栅极沟槽中形成上文所述的堆叠结构。另外,本发明的栅极也不仅限于cmos中的栅极,还可以是nmos栅极或pmos栅极。

47.本发明提供了以下优选实施例。

48.实施例1

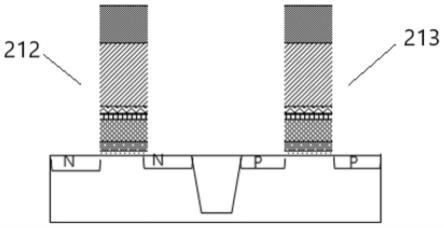

49.制作cmos晶体管:

50.第一步,在硅衬底201上形成浅槽隔离202,然后沉积栅介质层203,得到如图6所示的形貌,栅介质层膜的形成方法包括但不限于lpcvd、rtcvd、pecvd或热氧化法。

51.第二步,供应硅源sih4,在栅介质层203上采用lpcvd手段沉积第一多晶硅层204(沉积温度控制在400~500℃);之后继续沉积第二多晶硅层205,在沉积第二多晶硅层205时供应c2h4、geh4,沉积温度控制在400~500℃,得到碳和锗掺杂的多晶硅,如图7所示的形貌。

52.第三步,以光刻胶为掩膜,对部分第二多晶硅层205进行n型掺杂(例如磷p),如图8所示,去除光刻胶,清洁;

53.第四步,以光刻胶为掩膜,对部分第二多晶硅层205进行p型掺杂(例如硼b),如图9所示,去除光刻胶,清洁;这一步和第三步可以调换先后顺序。

54.第五步,进行快速热退火处理,处理温度控制在850~950℃范围内,在第二多晶硅层上形成掺杂均匀好的p型掺杂区域205b和n型掺杂区域205a,如图10所示。

55.第六步,在掺杂后的多晶硅上依次形成第一金属层206(例如钛)、第二金属层207(例如氮化钛)、第三金属层208(例如w)和盖层209,如图11所示。

56.第七步,结合光刻胶和刻蚀工艺对上述形成的堆叠结构刻蚀,形成nmos栅极210和pmos栅极211,如图12所示。

57.第八步,进行源漏区域掺杂、引出电极等,形成nmos和pmos的源漏极,得到互补的nmos晶体管212和pmos晶体管213,如图13所示。

58.经检测,该实施例得到的cmos晶体管相比非co离子注入的器件具有更优异的电特性。

59.实施例2

60.制作nmos晶体管:

61.第一步,在硅衬底201上形成浅槽隔离,然后沉积栅介质层202,栅介质层的形成方法包括但不限于lpcvd、rtcvd、pecvd或热氧化法。

62.第二步,采用甲硅烷,利用lpcvd手段在栅介质层上依次沉积第一多晶硅层203和第二多晶硅层204,第一多晶硅层为非掺杂,第二多晶硅层沉积时供应c2h4、geh4。

63.第三步,以光刻胶为掩膜,对第二多晶硅层进行n型(例如磷p)或p型掺杂(例如硼b),去除光刻胶,清洁。

64.第四步,进行快速热退火处理,处理温度控制在850~950℃范围内。

65.第五步,在掺杂后的多晶硅上依次形成第一金属层(例如钛)、第二金属层(例如氮

化钛)、第三金属层(例如w)和盖层。

66.第六步,结合光刻胶和刻蚀工艺对上述形成的堆叠结构刻蚀,形成nmos栅极。

67.第八步,进行源漏区域掺杂、引出电极等,形成nmos的源晶体管。

68.经检测,该实施例得到的nmos晶体管相比非co离子注入的器件具有更优异的电特性。

69.实施例3

70.制作pmos晶体管:

71.第一步,在硅衬底上形成浅槽隔离,然后沉积栅介质层,栅介质层的形成方法包括但不限于lpcvd、rtcvd、pecvd或热氧化法。

72.第二步,采用甲硅烷,利用lpcvd手段在栅介质层上依次沉积第一多晶硅层和第二多晶硅层,第一多晶硅层为非掺杂,第二多晶硅层沉积时供应c2h4、geh4。

73.第三步,以光刻胶为掩膜,对部分第二多晶硅层进行n型(例如磷p)或p型掺杂(例如硼b),去除光刻胶,清洁;

74.第四步,进行快速热退火处理,处理温度控制在850~950℃范围内。

75.第五步,在掺杂后的多晶硅上依次形成第一金属层(例如钛)、第二金属层(例如氮化钛)、第三金属层(例如w)和盖层。

76.第六步,结合光刻胶和刻蚀工艺对上述形成的堆叠结构刻蚀,形成nmos栅极和pmos栅极。

77.第七步,进行源漏区域掺杂、引出电极等,形成pmos的源漏极,得到晶体管。

78.经检测,该实施例得到的pmos晶体管相比非co离子注入的器件具有更优异的电特性。

79.以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1