用于改善图像传感器串扰的方法和结构与流程

1.本公开总体上涉及图像传感器,尤其涉及具有分裂像素结构的图像传感器。

背景技术:

2.图像传感器无处不在。图像传感器在数码静态摄像头、蜂窝式电话、监控摄像头、以及医疗、汽车及其它应用中广泛使用。具有分裂像素结构的图像传感器具有不同尺寸的光电二极管,这有利地实现了改善的成像,例如,高动态范围(hdr)感测。

技术实现要素:

3.本公开的一个方面提供了一种图像传感器,其中所述图像传感器包括:衬底材料,其中所述衬底材料包含设置在其中的多个小光电二极管(spd)和多个大光电二极管(lpd),每个lpd具有第一全井容量,所述第一全井容量大于每个spd的第二全井容量;多个像素隔离器,所述多个像素隔离器形成在所述衬底材料中,每个像素隔离器设置在所述spd中的一个与所述lpd中的一个之间;钝化层,所述钝化层设置在所述衬底材料上;缓冲层,所述缓冲层设置在所述钝化层上;多个第一金属元件,所述多个第一金属元件设置在所述缓冲层中,每个第一金属元件设置在所述像素隔离器中的一个的上方;以及多个第二金属元件,所述多个第二金属元件设置在所述多个第一金属元件上方。

4.本公开的另一方面提供了一种制造图像传感器的方法,其中所述方法包括:在具有多个大光电二极管(lpd)和多个小光电二极管(spd)的衬底材料中形成多个像素隔离器,每个lpd具有第一全井容量,所述第一全井容量大于每个spd的第二全井容量,每个像素隔离器设置在所述spd中的一个与所述lpd中的一个之间;在所述衬底材料上形成钝化层;在所述钝化层上形成缓冲层;通过从所述缓冲层中去除材料而在所述缓冲层中形成多个开口,所述开口中的每一个设置在所述像素隔离器中的一个的上方;形成多个第一金属元件,包含通过将第一金属层沉积到所述缓冲层中的所述多个开口中;以及形成多个第二金属元件,包含通过将第二金属层沉积在所述第一金属层上方。

附图说明

5.参考以下图式描述本发明的非限制且非详尽实施例,其中除非另有说明,否则相同的附图标记在各个视图中指代相同部件。

6.图1示出了根据本公开的教导的代表性图像传感器。

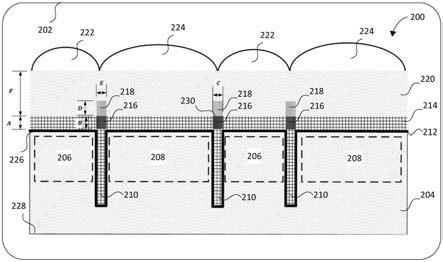

7.图2示出了根据本公开的教导的代表性图像传感器的示例性横截面视图。

8.图3示出了根据本公开的教导的另一个代表性图像传感器的示例性横截面视图。

9.图4示出了根据本公开的教导的另一个代表性图像传感器的示例性横截面视图。

10.图5示出了根据本公开的教导的另一个代表性图像传感器的示例性横截面视图。

11.图6是示出根据本公开的教导的具有像素阵列的代表性成像系统的图式。

12.图7至图13示出了根据本公开的教导的制造代表性图像传感器的代表性方法。

13.图14示出了根据本公开的教导的制造代表性图像传感器的方法的代表性流程图。

具体实施方式

14.本公开提供了图像传感器、装置以及用于制造图像传感器的方法。在以下描述中,陈述众多特定细节以提供对实例的详尽理解。然而,所属领域的技术人员将认识到,可在没有所述具体细节中的一或多种的情况下实施或以其它方法、部件、材料等等实践本文中描述的技术。在其它实例中,未展示或详细描述众所周知的结构、材料或操作以避免模糊某些方面。

15.贯穿本说明书对“实施例”或“一些实施例”的参考意味着结合实施例描述的特定特征、结构或特性包含在本发明的至少一个实施例中。因此,在贯穿本说明书的各个地方出现短语“在一些实施例中”或“在实施例中”不一定都指代同一实例。此外,实施例的特定特征、结构或特性可以在一或多个实例中以任何合适方式组合。

16.为了便于描述,可以在本文使用诸如“下面”、“下方”、“下部”、“以下”、“上方”、“上部”等空间相对术语来如图中所说明般描述一个元件或特征与另一个元件或特征的关系。应当理解,所述空间相对术语旨在涵盖除图中所描绘的取向之外的使用或操作中的装置的不同取向。例如,如果图中的装置翻转,则被描述为在其它元件或特征“下方”或“下面”或“以下”的元件将被取向在其它元件或特征“上方”。因此,示例性术语“下方”和“以下”可以涵盖上方和下方这两个取向。装置可以其它方式取向(旋转九十度或其它取向),且相应地解释本文所使用的空间相对描述符。另外,还应当理解,当一层被称为在两层“之间”时,其可以是这两层之间的唯一层,或也可以存在一个或多个中间层。

17.本公开涉及关于不同实施例(包含设备和方法)的多个术语。除非明确指出,否则具有相似名称的术语对于不同的实施例具有相同的含义。类似地,本公开利用了大量技术术语。这些术语具有其所来源于的领域中的一般含义,除非本文中具体定义或其使用背景清楚地以其它方式指示。应当注意,贯穿本文档,元件名称及符号可互换使用(例如,si和硅);然而,这两者均具有相同意义。

18.在本公开中,术语“半导体衬底”或“衬底”是指用于在其上形成半导体装置的任何类型的衬底,包含单晶衬底、硅、硅锗、锗、砷化镓绝缘体上半导体(semiconductor on insulator,soi)衬底以及它们的组合。术语半导体衬底也可以指代由一或多种半导体形成的衬底,所述衬底经历了在衬底中形成区域和/或结的先前工艺步骤。半导体衬底还可以包含各种特征,诸如掺杂和未掺杂半导体、硅的外延层以及形成在衬底上的其它半导体结构。此外,尽管将主要关于与硅基半导体材料(例如,硅以及硅与锗和/或碳的合金)兼容的材料和工艺来描述各种实施例,但是本技术不限于此。而是,可以使用任何类型的半导体材料来实施各种实施例。

19.在一些实施例中,图像传感器包含一或多个滤色器和微透镜以分别过滤和聚焦入射光。在包含光电二极管的衬底与滤色器之间可以存在缓冲层。图像传感器可以包含用于较低强度的光感测的一或多个大光电二极管以及用于较高强度的光感测的一或多个小光电二极管,例如,以实现高动态范围(hdr)感测。大光电二极管可以被布置在小光电二极管附近和/或周围。在具有大光电二极管和小光电二极管的实施例中,大光电二极管通常具有大于小光电二极管的全井容量的全井容量。

20.在一些情况下,来自相邻的大光电二极管的高角度光(例如,由于高强度光或其它原因引起的内部反射所引起的)可能会串扰到小光电二极管,并且被小光电二极管吸收,甚至使小光电二极管饱和(即,光学串扰)。这可能对图像传感器对高强度光(例如,花瓣状杂散光)的感测能力产生有害影响。

21.本公开的图像传感器具有改善图像传感器中的高强度光感测的性能的架构。在小光电二极管与大光电二极管之间提供金属栅格,以减少从附近的大光电二极管进入小光电二极管的高角度光的量,即,减少光学串扰。这防止来自相邻的大光电二极管的高角度光串扰激活小光电二极管。这些优点在诸如大光电二极管/小光电二极管(lpd/spd)图像传感器之类的分裂像素结构中特别有用,而且也适用于其它像素结构。下面描述代表性图像传感器的多个实施例。除非另有说明,否则不同实施例的一或多个特征可以组合以形成在本公开的范围内的附加实施例。

22.图1示出了根据本公开的教导的代表性图像传感器100的一个实例。图像传感器100包含大像素阵列(例如,大像素102)和小像素阵列(例如,小像素104)。大像素被布局在栅格中,而小像素设置在大像素之间和周围。此外,图像传感器100具有lpd/spd布局,其包含多个大光电二极管(lpd)和多个小光电二极管(spd)。每个lpd位于大像素中的一个(例如,大像素102)中,而每个spd位于小像素中的一个中。在图1的代表性且非限制性实例中,小像素是正方形的,并且与六边形的大像素的栅格的方向成45度角。在一些实施例中,小像素和/或大像素具有不同于图1所示的的形状和/或尺寸。

23.小像素和大像素均被金属栅格106包围,所述金属栅格由下面将详细描述的多个第一金属元件和多个第二金属元件构成。金属栅格106通过反射或吸收具有高角度光的入射光以及增强lpd的光敏度来改善spd和lpd的隔离。在图1中,图像传感器100具有4

×

4的大像素阵列和5

×

5的小像素阵列;然而,在其它实施例中,图像传感器100可以具有任何尺寸的阵列。本文描述的概念适用于其中光电二极管的分离有利的其它像素和光电二极管布局,而不仅仅适用于具有lpd和spd的那些。

24.图2示出了根据本公开的教导的代表性图像传感器200的一个实例。图像传感器200被体现在装置202(例如,摄像头、智能手机摄像头、车辆摄像头等)中。图像传感器200包含具有多个小光电二极管(spd)(诸如spd 206)和多个大光电二极管(lpd)(诸如lpd 208)的衬底材料204。图像传感器200还包含形成在衬底材料204中的多个像素隔离器210,每个像素隔离器210设置在spd 206中的一个与lpd 208中的一个之间。钝化层212设置在衬底材料204上,并且缓冲层214设置在钝化层212上。多个第一金属元件216设置在像素隔离器210上方的钝化层212上方,并且多个第二金属元件218至少部分地设置在第二金属元件218上方,这两者均减小了像素串扰,如下所述。代表性图像传感器200还包含设置在第一金属元件216和第二金属元件218上方的任选的滤色器层220,以及设置在spd 206和lpd 208上方的任选微透镜阵列,其包含小微透镜222和大微透镜224。

25.衬底材料204是诸如硅衬底之类的半导体衬底、诸如n型掺杂硅衬底或p型掺杂衬底之类的掺杂硅衬底、绝缘体上硅衬底等。衬底材料204具有背侧226和相对的前侧228。在图2中,图像传感器200被配置为通过背侧226接收入射光。因此,背侧226可以被称为图像传感器200的照明侧,而前侧228可以被称为图像传感器200的非照明侧。

26.spd 206和lpd 208将入射光转换为电荷。如本文所使用的,每个lpd 208具有比每

个spd 206更大的全井容量。spd 206和lpd 208可以例如通过在前侧228上进行离子注入而形成在衬底材料204中。在一些实施例中,spd 206和lpd 208是形成在p型硅衬底材料204中的n型光电二极管。在一些实施例中,极性可以相反;例如,spd 206和lpd 208是形成在n型硅衬底材料204中的p型光电二极管。lpd 208各自具有比每个spd 206更大的全井容量,即,每个lpd 208比每个spd 206存储更多的光生电荷。在一些实施例中,每个lpd 208的像素尺寸至少是每个spd 206的像素尺寸的两倍。在一些实施例中,每个lpd 208具有比每个spd 206更大的曝光面积。在一些实施例中,每个spd 206被两或更多个lpd 208围绕。每个spd 206不需要具有与其它所有spd 206相同的全井容量、像素尺寸或曝光面积。同样,每个lpd 208不需要具有与其它所有lpd 208相同的全井容量、像素尺寸或曝光面积。在一些实施例中,对于波长为530nm的入射光,每个lpd 208的量子效率在0.4至0.9之间。在一些实施例中,对于波长为530nm的入射光,每个spd 206的量子效率小于0.5。

27.在代表性图像传感器200中,lpd 208具有更大的曝光面积和对入射光的更高灵敏度,并且因此可以被配置为用于较低的光强度感测。另一方面,与lpd 208相比,spd 206具有较小的曝光面积并且对高强度光较不敏感,并且因此被配置为用于较高的光强度感测。在图像传感器200中利用spd 206和lpd 208的阵列有利地实现了高动态范围(hdr)成像感测。

28.像素隔离器210形成在衬底材料204的背侧226上,并且从背侧226向下延伸(相对于图示,所述装置可以沿任何方向取向)到衬底材料204中。每个像素隔离器210设置在spd 206中的一个与lpd 208中的一个之间,例如,以防止相邻的光电二极管之间的电和/或光学串扰。在一个实施例中,每个像素隔离器210是填充有钝化材料(诸如高k氧化物材料)、电介质材料(诸如硅氧化物)、反射金属材料或它们的组合的深沟槽隔离(dti)结构。在图2中,每个像素隔离器210均填充有钝化层212和缓冲层214的一部分,如在下文中描述。在一些实施例中,每个像素隔离器210是浅沟槽隔离(sti)沟槽结构或另一沟槽结构。

29.钝化层212沉积在衬底材料204的背侧226上并进入像素隔离器210中。钝化层212包括电介质材料,诸如氧化物或高k材料,例如,介电常数大于大约3.9的材料(例如,al2o3或hfo2)。在一些实施例中,钝化层212的厚度为约0.005um至约0.10um,例如,约0.01um至约0.05um。在一些实施例中,钝化层212含有负固定电荷,从而形成围绕像素隔离器210的空穴累积层,其使像素隔离器210的侧壁和底部钝化并防止在像素隔离器210的形成期间在边界(例如,硅

‑

氧化硅界面)上形成缺陷/陷井。这防止捕获电子和/或空穴从而产生暗电流,所述暗电流可能影响spd 206或lpd 208的灵敏度。钝化层212中所含有的负固定电荷的量或所形成的空穴累积层的空穴密度取决于高k材料和钝化层212的厚度。在一些实施例中,钝化层212由具有介于缓冲层214(例如,对于氧化硅为1.4)与衬底材料204(例如,对于硅衬底为3.9)之间的折射率并且具有被配置为用作抗反射涂层以减少入射光的反射量的厚度,并增强spd 206和lpd 208的光吸收的材料形成。

30.在一些实施例中,可以例如通过沉积或热氧化在钝化层212与背侧226表面之间形成薄氧化物层,并且所述薄氧化物层用作钝化层212与硅表面之间的应力消除层。

31.缓冲层214设置在钝化层212上,即,在衬底材料204的背侧226上和上方。在一些实施例中,缓冲层214包含诸如二氧化硅之类的电介质材料,并且为蚀刻和化学机械抛光工艺提供工艺裕度,以便防止损坏衬底材料204和钝化层212。例如,缓冲层214有助于固定第一

金属元件216,如下所述。在一些实施例中,缓冲层214的厚度a为约0.025um至约1.000um,例如,约0.05um至约0.50um。在一些实施例中,缓冲层214具有低于钝化层212的介电常数,即,钝化层212具有大于缓冲层214的介电常数。

32.第一金属元件216和第二金属元件218一起形成金属栅格(例如,图1的金属栅格106)。金属栅格以减少从附近的lpd 208进入(和激活)spd 206的高角度入射光的量的配置设置在spd 206与lpd 208之间。在一些实施例中,缓冲层214对于入射光(诸如相对于指向lpd 208的背侧226表面的表面法线具有高入射角的光)是可透射的。此类高入射角光可以穿透缓冲层214并串扰到被相应的lpd 208包围的spd 206,并且由第一金属元件216和第二金属元件218形成的金属栅格结构可以有效地阻止此类高入射角光串扰到spd 206,并且同时还可以改善相应的lpd 208的光吸收。因此,金属栅格减少了光学串扰及其有害影响,例如,花瓣状杂散光。在一些实施例中,倾斜于背侧226的表面法线的入射光的至少一部分可以被由第一金属元件216和第二金属元件218形成的金属栅格结构反射到单独的大光电二极管208中,以用于增强大光电二极管208的光敏性。

33.第一金属元件216中的每一个至少部分地由诸如铝或钨之类的金属形成,并且至少部分地设置在缓冲层214中,所述缓冲层至少部分地在像素隔离器210中的一个的上方(即,之上)。在此重申,第一金属元件216中的每一个至少部分地设置在缓冲层214中,并且位于相邻的spd 206和lpd 208上方和之间。在图2中,每个第一金属元件216均设置在缓冲层214中,例如,整个设置在缓冲层214中。在一些实施例中,一或多个第一金属元件216部分地设置在缓冲层214中。例如,在一些实施例中,一或多个第一金属元件216从缓冲层214(例如,从缓冲层214的上表面)突出。在图2中,每个第一金属元件216设置在像素隔离器210中的一个的正上方;然而,在一些实施例中(如下所述),每个第一金属元件216横向地移位,使得其不设置在对应的像素隔离器210的正上方。如图2所示,在一些实施例中,第一金属元件216未延伸到多个像素隔离器210中。在一些实施例中,第一金属元件216和第二金属元件218可以横向地移位到相应的像素隔离器210的中心线的左侧或右侧,这取决于其在像素阵列中的位置,以适应入射光的主光线角度(chief ray angle,cra)以获得更好的光学串扰性能。

34.每个第一金属元件216具有厚度b和宽度c。厚度b可以为约0.025um至约1.000um,例如,约0.05um至约0.50um。在一些实施例中,厚度b对应于缓冲层214的厚度a。在一些实施例中,第一金属元件216的厚度b比缓冲层214的厚度a小约0.005um至约0.010um,并且每个第一金属元件216的上表面与缓冲层214的上表面齐平,使得缓冲层214将每个第一金属元件216与钝化层212隔离(即,第一金属元件216不接触钝化层212)。在一些实施例中,每个第一金属元件216的上表面与缓冲层214的上表面齐平(例如,作为诸如下面描述的化学机械处理步骤之类的处理步骤的结果)。宽度c为约0.05um至约0.25um,例如,约0.09um至约0.20um。在一些实施例中,宽度c约等于或小于其上方设置有第一金属元件216的对应的像素隔离器210的宽度。在一些实施例中,不同的第一金属元件216具有不同的厚度b和/或宽度c。

35.有利的是,通过在缓冲层214中包含第一金属元件216,与相对于离spd 206更远的位置(例如,在滤色器层220中,或在spd 206的上方超过约0.05um至约0.50um)相比,每个第一金属元件216更好地定位以防止入射光激活spd 206。在此重申,入射光很难通过第一金

属元件216下方并激活spd 206,否则将在图像传感器的积分时段期间使spd 206饱和。

36.第二金属元件218进一步提高了金属栅格的遮光能力。类似于第一金属元件216,第二金属元件218各自至少部分地由诸如铝或钨之类的金属形成,并且至少部分地设置在像素隔离器210中的一个的上方(即,之上)并且至少部分地设置在第一金属元件216中的至少一个的上方。在此重申,每个第二金属元件218的下表面在界面230处至少部分地与第一金属元件216的上表面对接。有利的是,这防止入射光在对应的第一金属元件216与第二金属元件218之间行进。第一金属元件216设置在缓冲层214中,而第二金属元件218设置在第一金属元件216上。在图2中,第二金属元件218也设置在缓冲层214上,即,每个第二金属元件218的下表面与缓冲层214的上表面齐平。在图2中,每个第二金属元件218与其设置在其上的第一金属元件216对齐。在一些实施例中,每个第二金属元件218例如由于光致抗蚀剂掩模的覆盖移位或为了改善光学串扰性能而相对于其设置在其上的第一金属元件216和/或相对于其设置在其上的像素隔离器210移位。在一些实施例中,一或多个第二金属元件218由与一或多个第一金属元件216不同的材料形成。在一些实施例中,每个第二金属元件218设置在两或更多个滤色器之间。

37.每个第二金属元件218具有厚度d和宽度e。厚度d可以为约0.050um至约1.000um,例如,约0.10um至约0.50um。在一些实施例中,厚度d可以超过第一金属元件216的厚度b。宽度e为约0.05um至约0.25um,例如,约0.09um至约0.20um。在一些实施例中,宽度e约等于或小于其上方设置有第二金属元件218的对应的第一金属元件216的宽度c。在一些实施例中,宽度e约等于或小于其上方设置有第二金属元件218的对应的像素隔离器210的宽度。在一些实施例中,不同的第二金属元件218具有不同的厚度d和/或宽度e。

38.因此,第一金属元件216和第二金属元件218一起共同地形成金属栅格,所述金属栅格以减少光学串扰的配置设置在缓冲层214中和缓冲层214上方。

39.任选的滤色器层220吸收可见光的一或多个波长范围,使得一或多个光电二极管响应于可见光的一或多个选定波长带,例如,红色、绿色、蓝色、青色、品红色和黄色。在图2中,第二金属元件218设置在滤色器层220中。滤色器层220在图2中被示为设置在第二金属元件218上方和周围的层。在一些实施例中,滤色器层220包含离散滤色器阵列,例如,小滤色器和大滤色器,其中一或多个可以被配置为过滤与另一滤色器不同的颜色的波长。在此类实施例中,每个离散的小滤色器可以设置在spd 206上方并与其对齐。同样,每个离散的大滤色器可以设置在lpd 208上方并与其对齐。在一些实施例中,一或多个滤色器设置在缓冲层214上。在一些实施例中,一或多个滤色器至少部分地设置在缓冲层214中。在一些实施例中,一或多个滤色器设置在多个第二金属元件218之间的间隙中。在此重申,第二金属元件218围绕一或多个滤色器,从而形成埋藏式滤色器阵列。在一些实施例中,滤色器阵列的厚度f大于第二金属元件218的厚度。

40.任选的小微透镜222和大微透镜224分别将入射光聚集、引导并聚焦在spd 206和lpd 208上。因此,每个小微透镜222和每个大微透镜224分别形成在spd 206和lpd 208上方并且与它们对齐。例如,在spd 206上方形成小微透镜222,其每个边缘与spd 206的每一侧上的相应的第一金属元件216和第二金属元件218的中心对齐,使得其被配置为将入射光引导到spd 206的曝光区域上。这对于每个大微透镜224是类似的。在一些实施例中,一或多个小微透镜222和/或大微透镜224可以具有不同的高度,即,微透镜的顶部与滤色器层220中

的相应滤色器之间的距离。例如,小微透镜222可以具有小于大微透镜224的第二高度的第一高度,即,大微透镜224比小微透镜222高,例如,以补偿曲率差,使得小微透镜222和大微透镜224具有基本相同的焦距。

41.有利的是,上述图像传感器200的结构限制了可以激活spd 206的入射光(特别是高角度入射光)的量,由此限制了光学串扰并改善了图像传感器200的性能,特别是hdr感测。

42.图3示出了被体现在装置302中的替代图像传感器300的实例。类似于图像传感器200,图像传感器300包含具有spd 306和lpd 308的衬底材料304。图像传感器300还包含设置在spd 306与lpd 308之间的多个像素隔离器310。钝化层312设置在衬底材料304上,并且缓冲层314设置在钝化层312上。多个第一金属元件316设置在像素隔离器310上方的钝化层312中,并且多个第二金属元件318至少部分地设置在第一金属元件316上方。滤色器层320设置在第一金属元件316上方和第二金属元件318之间,并且小微透镜222和大微透镜224分别设置在spd 306和lpd 308上方。图像传感器300被配置为通过背侧326而不是通过前侧328接收入射光。

43.图像传感器300基本上类似于图2的图像传感器200,不同的是第二金属元件318相对于第一金属元件316横向地移位,即,在平行于缓冲层314的上表面的平面中移位。在某些应用中,例如,由于入射光的折射角,该移位改善了图像传感器300的光学性能。每个第二金属元件318至少部分地设置在对应的第一金属元件316上方,使得每个第二金属元件318的下表面在界面330处至少部分地与第一金属元件316的上表面对接。在一些实施例中,小微透镜322和/或大微透镜324的一或多个边缘也可以移位,例如,以使其边缘与第二金属元件318对齐。

44.图4示出了被体现在装置402中的替代图像传感器400的另一个实例。类似于图像传感器200,图像传感器400包含具有spd 406和lpd 408的衬底材料404。图像传感器400还包含设置在spd 406与lpd 408之间的多个像素隔离器410。钝化层412设置在衬底材料404上,并且缓冲层414设置在钝化层412上。多个第一金属元件416设置在像素隔离器410上方的钝化层412中,并且多个第二金属元件418至少部分地设置在第一金属元件416上方。滤色器层420设置在第一金属元件416上方和第二金属元件418之间,并且小微透镜222和大微透镜224分别设置在spd 406和lpd 408上方。图像传感器400被配置为通过背侧426而不是通过前侧428接收入射光。

45.图像传感器400基本上类似于图2的图像传感器200,不同的是第一金属元件416和第二金属元件418均相对于像素隔离器410横向地移位,即,在平行于缓冲层414的上表面的平面中移位。在某些应用中,例如,由于入射光的折射角,该移位改善了图像传感器400的光学性能。每个第二金属元件418设置在对应的第一金属元件416的正上方,使得每个第二金属元件418的下表面在界面430处与第一金属元件416的上表面对接。在一些实施例中,第一金属元件416和第二金属元件418均相对于像素隔离器410移位,但是移位了不同的距离。因此,在此类实施例中,每个第二金属元件418在界面430处与其对应的第一金属元件416部分重叠。在图4中,小微透镜422和大微透镜424的边缘也相对于像素隔离器410移位,以便将其边缘与第一金属元件416和/或第二金属元件418对齐。

46.图5示出了被体现在装置502中的替代图像传感器500的另一个实例。类似于图像

传感器200,图像传感器500包含具有spd 506和lpd 508的衬底材料504。图像传感器500还包含设置在spd 506与lpd 508之间的多个像素隔离器510。钝化层512设置在衬底材料504上,并且缓冲层514设置在钝化层512上。多个第一金属元件516设置在像素隔离器510上方的钝化层512中,并且多个第二金属元件518至少部分地设置在第一金属元件516上方。滤色器阵列520设置在第一金属元件516上方和第二金属元件518之间,并且小微透镜222和大微透镜224分别设置在spd 506和lpd 508上方。图像传感器500被配置为通过背侧526而不是通过前侧528接收入射光。每个第二金属元件518设置在对应的第一金属元件516的正上方,使得每个第二金属元件518的下表面在界面530处与第一金属元件516的上表面对接。此外,每个第一金属元件516和对应的第二金属元件518设置在对应的像素隔离器510的正上方。在一些实施例中,第一金属元件516和/或第二金属元件518中的一或多个可以相对于彼此和/或相对于像素隔离器510移位,如上文关于图2至图4所描述的。

47.图像传感器500基本上类似于图2的图像传感器200,并且进一步包含如下所述的设置在每个spd 506上方的衰减层532。而且,图5的滤色器阵列520阐明了图2的滤色器层220可以如何形成,即,形成为小滤色器534和大滤色器536的阵列,它们中的每一个可以被配置为过滤相同或不同波长的入射光。

48.衰减层532被配置为衰减每个spd 506的光敏度,并且被布置为形成spd 506并与其对齐以衰减被引导到其上的入射光。例如,在一些实施例中,衰减层532被配置为(例如,通过吸收)减少到达spd 506的入射光的量,由此防止spd 506在积分时段期间变得饱和。衰减层532形成在缓冲层514和第二金属元件518上。此外,每个衰减层532设置在缓冲层514与对应的小滤色器534之间,例如,使得小滤色器534不与缓冲层514直接接触。衰减层532可以在平行于缓冲层514的上表面的平面中沿远离spd 506的所有方向延伸。

49.衰减层532可以是单层或多层堆叠结构,其厚度被配置为调整入射光对所述对应spd 506的透射率,并且可以由钛、氮化钛、钽、铝、钨等或它们的组合形成。在一些实施例中,每个衰减层532不仅覆盖整个spd 506,而且覆盖一或多个相邻lpd 508的一部分。

50.图6是示出带有具有根据本公开的教导形成的多个图像传感器的像素阵列602的代表性成像系统600的一个实例的图式。如图所示,像素阵列602耦合到控制电路604和读出电路606,所述读出电路耦合到功能逻辑608。

51.在一个实例中,像素阵列602是像素610的二维(“2d”)阵列(例如,像素p1、p2

……

、pn)。在一个实施例中,每个像素610是互补金属氧化物半导体(“cmos”)成像像素。像素610可以被实施为前侧照明图像传感器阵列或背侧照明图像传感器阵列。在一个实施例中,像素610包含如图2至图5所描绘的一或多个图像传感器。如图所示,像素610被布置成行(例如,行r1至ry)和列(例如,列c1至cx)以获取人、地点或物体的图像数据,然后可以将所述图像数据用于渲染人、地点或物体的2d图像。

52.在一个实施例中,在一个像素610(或多个像素610)已获取其图像数据或图像电荷之后,读出电路606读出图像数据并且将所述图像数据转移到功能逻辑608。读出电路606可以包含放大电路,例如,差分放大器电路、模数(“adc”)转换电路或其它。在一些实施例中,读出电路606可以沿着读出列线一次读出一行图像数据(已示出),或可以使用例如串行读出或同时全并行读出所有像素的多种其它技术(未示出)来读出所述图像数据。

53.功能逻辑608可以包含用于存储图像数据或甚至通过施加后期图像效果(例如,剪

裁、旋转、去除红眼、调整亮度、调整对比度或其它)来操纵图像数据的逻辑和存储器。

54.控制电路604耦合到像素610,并且可以包含用于控制像素610的操作特性的逻辑和存储器。例如,控制电路604可以产生用于控制图像获取的快门信号。在一个实施例中,快门信号是全局快门信号,其用于同时启用所有像素610以在单个获取窗期间同时俘获其相应的图像数据。在替代实施例中,快门信号是滚动快门信号,由此在连续获取窗期间循序地启用像素610的每一行、列或群组。

55.图7至图13示出了根据本公开的教导的制造图像传感器700的代表性方法的一个实例,所述图像传感器700实质上类似于图2的图像传感器200。关于该代表性方法而利用的并且具有与用于描述图2至图6的代表性图像传感器的结构术语共有的名称的术语具有与那些术语共有的含义。根据对上文提供的那些元件的描述,代表性方法可以包含或可以被修改为包含一或多个步骤,以赋予结构元件一或多个特性(例如,大小)。

56.参考图7,提供了衬底材料704。多个小光电二极管(spd)(诸如spd 706)和多个大光电二极管(lpd)(诸如lpd 708)例如通过离子注入而形成在衬底材料704中。形成spd 706和lpd 708,使得每个lpd 708具有第一全井容量,所述第一全井容量大于每个spd 706的第二全井容量。多个像素隔离器710形成在衬底材料704中,每个像素隔离器710设置在spd 706中的一个与lpd 708中的一个之间。在图7中,每个像素隔离器710是深沟槽隔离(dti)沟槽结构。在形成像素隔离器710之后,钝化层712例如由电介质材料形成在衬底材料上。钝化层712设置在每个像素隔离器710中,使得其在相邻的spd 706与lpd 708之间延伸。在形成钝化层712之后,例如通过电介质沉积或热氧化工艺在钝化层712上形成厚度为a的缓冲层714。钝化层712设置在每个像素隔离器710中,使得其在相邻的spd 706与lpd 708之间延伸。

57.参考图8,代表性方法进一步包含通过从缓冲层714中去除材料而在缓冲层714中形成开口726,使得每个开口726具有厚度b和宽度c,如上所述。厚度b可以小于缓冲层714的厚度。开口726可以通过一或多种光刻工艺、蚀刻工艺等形成。例如,可以将掩模放置在缓冲层714上方,然后可以使用干式蚀刻工艺和湿式蚀刻工艺从缓冲层714中去除与开口726相对应的材料。例如,可以利用干式刻蚀工艺从缓冲层714中去除材料直到第一深度,所述第一深度小于开口726的最终期望厚度b。然后,例如,可以利用湿式蚀刻工艺从缓冲层714中去除材料直到开口726的最终厚度b,以便防止损坏钝化层712。在图8中,每个开口726设置在像素隔离器710中的一个的正上方。在一些实施例中,根据上面的教导,每个开口726可以相对于像素隔离器710移位。在一些实施例中,每个开口726的厚度小于缓冲层714的厚度,如上所述,例如,比缓冲层214的厚度小约0.005um至约0.010um。在一些实施例中,每个开口726的宽度c等于或小于其设置在其上方的像素隔离器710的宽度g。在一些实施例中,每个开口726具有约0.05um至约0.25um的宽度c。

58.参考图9,代表性方法进一步包含形成多个第一金属元件716,包含通过将第一金属层728(例如,钨或铝层)沉积到缓冲层714上,使得第一金属层728填充先前形成在缓冲层中的开口(即,图8中所示的开口726)。在一些实施例中,第一金属元件716被形成为使得它们不与钝化层712接触,即,图8中所示的开口726并未一直向下延伸到钝化层712。这样,缓冲层714将第一金属元件716与钝化层712隔离。任选地,可以在沉积第一金属层728之前将阻挡层和粘合剂层沉积到开口中,以防止金属扩散到半导体衬底704中并增加第一金属层

728与钝化层712之间的结合强度。可以在第一金属元件716的形成期间对阻挡层和粘合剂层进行图案化和蚀刻,使得阻挡层和粘合剂层的其余部分形成在第一金属元件716与钝化层712之间。阻挡层和粘合剂层可以包含诸如钛(ti)、氮化钛(tin)或它们的组合之类的材料。

59.参考图10,代表性方法进一步包含从第一金属层中去除多余的材料部分(即,图9中的628所指向的部分),使得第一金属元件716保留在先前形成于缓冲层714中的开口中。在一些实施例中,抛光工艺(例如,化学机械抛光工艺)用于从第一金属层中去除多余的材料部分。从第一金属层中去除材料,直到露出缓冲层714,并且第一金属元件716基本上是第一金属层中剩余的全部。在该步骤之后,每个第一金属元件716的上表面可以与缓冲层714的上表面齐平。

60.参考图11,代表性方法进一步包含形成多个第二金属元件718,包含通过首先将第二金属层730(例如,钨或铝层)沉积在第一金属元件716上方和缓冲层714上方来形成多个第二金属元件。由于第二金属层730的沉积,在第二金属层730与第一金属元件716之间形成多个界面734。可以将掩模732施加到第二金属层730以覆盖第二金属层730的在后续步骤中将不被去除的部分。可以利用光刻工艺来形成掩模732。

61.参考图12,代表性方法进一步包含从第二金属层中去除的材料多余部分(即,图11中的630所指向的部分),以便在图11所示的掩模732下面形成离散的第二金属元件718。可以利用蚀刻工艺从第二金属层中去除材料。多余部分位于相邻的第一金属元件716与第二金属元件718之间。在图12中,第二金属元件718中的每一个设置在第一金属元件716中的一个的正上方。在一些实施例中,每个第二金属元件718可以相对于第一金属元件716移位,诸如图3所示。

62.参考图13,代表性方法进一步包含在缓冲层714上形成任选的滤色器层720,以及形成包含小微透镜722和大微透镜724的任选微透镜阵列。在图13中,滤色器层720被形成为设置在第二金属元件718上方和周围的单层。在一些实施例中,滤色器层720包含离散滤色器阵列,例如,小滤色器和大滤色器,其中一或多个可以被配置为过滤与另一滤色器不同的颜色的波长。在此类实施例中,每个离散的小滤色器设置在spd 706上方并与其对齐。同样,每个离散的大滤色器设置在lpd 708上方并与其对齐。在一些实施例中,相邻的滤色器设置在相邻的第二金属元件718之间。在一个实例中,可以通过根据诸如拜耳图案之类的滤色器图案在第二金属元件718之间的间隙中沉积滤色器材料来形成单独的滤色器。在此类实例中,第二金属元件718中的每一个被布置在单独的滤色器之间,并且由第二金属元件718形成的栅格围绕单独的滤色器。

63.因此,图7至图13示出了形成本公开的图像传感器的一种代表性方法。

64.图14是总结了图7至图13的方法的代表性方法1400的流程图。尽管以下描述涉及多个离散步骤,但是所描述的动作可以在更多或更少的步骤内执行。

65.在步骤1402处,如上文关于图7所描述的,提供半导体衬底材料,并且在其中形成多个lpd和spd。

66.在步骤1404处,如上文关于图7所描述的,在lpd与spd之间的衬底材料中形成多个像素隔离器。

67.在步骤1406处,如上文关于图7所描述的,在衬底材料上和像素隔离器中形成钝化

层。例如,钝化层可以为每个单独的像素隔离器的沟槽结构的侧壁和底部加衬里,并且在覆盖背侧表面的衬底材料的背侧上连续延伸。

68.在步骤1408处,如上文关于图7所描述的,在钝化层上形成缓冲层。

69.在步骤1410处,如上文关于图8所描述的,在缓冲层中形成多个开口。

70.在步骤1412处,如上文关于图8至图10所描述的,在缓冲层中形成多个第一金属元件。

71.在步骤1414处,如上文关于图11至图12所描述的,形成多个第二金属元件。

72.在可选步骤1416处,如上文关于图13所描述的,在缓冲层上和在第二金属元件上形成覆盖spd的衰减层、滤色器(例如,滤色器阵列)和微透镜阵列。

73.关于前述代表性方法而利用的并且具有与用于描述图2至图5的代表性图像传感器和图7至图13的代表性方法的结构术语共有的名称的术语具有与那些术语共有的含义。根据对上文提供的那些元件的描述,代表性方法可以包含或可以被修改为包含一或多个步骤,以赋予结构元件一或多个特性(例如,大小)。

74.因此,本公开的图像传感器具有金属栅格,所述金属栅格包括设置在缓冲层中的第一金属元件和设置在第一金属元件上的第二金属元件。第一金属元件和第二金属元件形成金属栅格,所述金属栅格被配置为减少从附近的大光电二极管进入小光电二极管的高角度入射光的量,即,减少光学串扰及其相关联的影响(例如,花瓣状杂散光)。

75.对本发明的所说明的实例的以上描述(包含在说明书摘要中描述的内容)不希望为穷举性的或将本发明限于所揭示的精确形式。如本领域的技术人员将认识到,虽然出于说明目的在本文中描述了本发明的特定实例,但各种修改在本发明的范围内是可能的。

76.在以上详细描述的启示下可对本发明做出修改。所附权利要求书中使用的术语不应被解释为将本发明限于说明书中揭示的特定实例。而是,本发明的范围将完全由根据沿用已久的权利要求解释规则来解释的所附权利要求书确定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1