显示基板和显示装置的制作方法

[0001]

本公开涉及显示技术领域,具体涉及一种显示基板和显示装置。

背景技术:

[0002]

通常,显示基板中用于与驱动芯片连接的引脚被设计为多层结构,以使引脚垫高,增大与驱动芯片上对应引脚的粘结力。在制作过程中会在引脚上覆盖有机层,然后去除引脚表面的有机层以使引脚外露。但是传统显示基板在进行高温高湿信赖性测试时,驱动芯片ic容易脱落。

技术实现要素:

[0003]

本公开实施例提供了一种显示基板,包括:

[0004]

衬底基板,包括显示区、位于所述显示区至少一侧的邦定区和位于所述显示区至少另一侧的侧边区;

[0005]

多个子像素,位于所述显示区中;

[0006]

栅极驱动电路,位于所述侧边区,所述栅极驱动电路与所述多个子像素连接,并且被配置为向所述多个子像素提供栅极驱动信号;

[0007]

多个输入接触垫,位于所述邦定区,用于与外部电路电连接;

[0008]

多个输出接触垫,位于所述邦定区,且位于所述多个输入接触垫与所述显示区之间,所述多个输出接触垫与所述多个子像素和所述栅极驱动电路电连接;

[0009]

接触垫绝缘层,位于所述邦定区,且位于所述多个输入接触垫中相邻输入接触垫之间的间隙、所述多个输出接触垫中相邻输出接触垫之间的间隙、以及所述多个输入接触垫与所述多个输出接触垫之间的区域,所述多个输入接触垫和所述多个输出接触垫的背离所述衬底基板的表面从所述接触垫绝缘层外露,其中所述接触垫绝缘层包括具有第一厚度的第一部分和具有第二厚度的第二部分,所述第二厚度小于所述第一厚度,所述多个输入接触垫和所述多个输出接触垫的边缘被所述接触垫绝缘层的第一部分覆盖,所述接触垫绝缘层的第二部分位于所述多个输入接触垫与所述多个输出接触垫之间的区域中。

[0010]

例如,所述显示基板还包括:多个第一虚拟接触垫,位于所述邦定区,且位于所述多个输入接触垫与所述多个输出接触垫之间的区域中,其中,

[0011]

所述多个第一虚拟接触垫的边缘被所述接触垫绝缘层的第一部分覆盖,所述多个第一虚拟接触垫的背离所述衬底基板的表面从所述接触垫绝缘层的第一部分外露;并且

[0012]

所述接触垫绝缘层的第二部分包括第一子部分和第二子部分,所述第一子部分位于所述多个第一虚拟接触垫与所述多个输入接触垫之间的区域,所述第二子部分位于所述多个第一虚拟接触垫与所述多个输出接触垫之间的区域。

[0013]

例如,所述显示基板还包括:多个阵列测试接触垫,位于所述邦定区,且位于所述多个第一虚拟接触垫与所述多个输入接触垫之间的区域中,所述多个阵列测试接触垫与所述多个子像素和所述栅极驱动电路电连接,其中,

[0014]

所述接触垫绝缘层的第一部分包括第一子部分和第二子部分,所述多个输入接触垫的边缘、所述多个输出接触垫的边缘和所述第一虚拟接触垫的边缘被所述接触垫绝缘层的第一部分的第一子部分覆盖,所述多个阵列测试接触垫的边缘被所述接触垫绝缘层的第一部分的第二子部分覆盖,所述多个阵列测试接触垫的背离所述衬底基板的表面从所述接触垫绝缘层的第一部分外露;并且

[0015]

所述接触垫绝缘层的第一部分的第二子部分在所述衬底基板上的投影位于所述接触垫绝缘层的第二部分的第一子部分在所述衬底基板的投影之内。

[0016]

例如,所述多个输入接触垫和所述多个输出接触垫中的每一个在所述衬底基板上的投影与所述接触垫绝缘层的第二部分在所述衬底基板的投影之间的间距在3微米至100微米的范围内。

[0017]

例如,所述第二厚度为0。

[0018]

例如,所述多个输入接触垫沿第一方向排列成至少第一行,所述第一方向为所述显示区的面向所述邦定区的侧边的延伸方向;

[0019]

所述多个输出接触垫沿第一方向排列成至少第二行;

[0020]

所述多个第一虚拟接触垫沿第一方向排列成至少第三行;

[0021]

所述多个阵列测试接触垫沿第一方向排列成至少第四行。

[0022]

例如,所述显示基板还包括:多个第二虚拟接触垫,位于所述邦定区,沿垂直于所述第一方向的第二方向排列成至少第一列和第二列,其中第一列和第二列分别位于所述多个第一虚拟接触垫在第一方向上的两侧,其中,

[0023]

所述多个第二虚拟接触垫的边缘被所述接触垫绝缘层的第一部分覆盖,所述多个第二虚拟接触垫的背离所述衬底基板的表面从所述接触垫绝缘层的第一部分外露;并且

[0024]

所述多个第二虚拟接触垫中的每一个在所述衬底基板上的投影与所述接触垫绝缘层的第二部分在所述衬底基板的投影之间的间距在3微米至100微米的范围内。

[0025]

例如,所述多个输入接触垫和所述多个输出接触垫中的至少一个包括:

[0026]

第一引线连接部,位于所述衬底基板上,其中输入接触垫的第一引线连接部通过设置在所述邦定区的第一引线与用于连接到外部电路的连接接触垫电连接,输出接触垫的第一引线连接部通过设置在所述邦定区的第二引线与所述栅极驱动电路或者与所述多个子像素中的至少一个电连接;

[0027]

第一导体部,位于所述第一引线连接部背离所述衬底基板的一侧,与所述第一引线连接部电连接;

[0028]

第二导体部,位于所述第一导体部背离所述衬底基板的一侧,与所述第一导体部电连接,所述第二导体部的边缘被被所述接触垫绝缘层的第一部分覆盖。

[0029]

例如,所述显示基板还包括:

[0030]

邦定区第一栅绝缘层,位于所述邦定区,覆盖所述衬底基板,所述第一引线连接部位于所述邦定区第一栅绝缘层背离所述衬底基板的一侧;

[0031]

邦定区第二栅绝缘层,位于所述邦定区,位于所述邦定区第一栅绝缘层背离所述衬底基板的一侧并且覆盖所述第一引线连接部;

[0032]

邦定区层间绝缘层,位于所述邦定区,且位于所述邦定区第二栅绝缘层背离所述衬底基板的一侧,所述第一导体部通过设置在所述邦定区第二栅绝缘层中的过孔和设置在

所述邦定区层间绝缘层中的过孔与所述第一引线连接部电连接;

[0033]

邦定区钝化层,位于邦定区,位于所述邦定区层间绝缘层背离所述衬底基板的一侧并且覆盖所述第一导体部,所述第二导体部通过设置在所述邦定区钝化层中的过孔与所述第一导体部电连接。

[0034]

例如,所述邦定区钝化层位于所述接触垫绝缘层的第二部分与所述邦定区第二栅绝缘层之间的部分厚度大于或等于0。

[0035]

例如,显示基板还包括:

[0036]

邦定区第一栅绝缘层,位于所述邦定区,覆盖所述衬底基板,所述第一引线连接部位于所述邦定区第一栅绝缘层背离所述衬底基板的一侧;

[0037]

邦定区第二栅绝缘层,位于所述邦定区,位于所述邦定区第一栅绝缘层背离所述衬底基板的一侧并且覆盖所述第一引线连接部;

[0038]

邦定区层间绝缘层,位于所述邦定区,且位于所述邦定区第二栅绝缘层背离所述衬底基板的一侧,所述第一导体部通过设置在所述邦定区第二栅绝缘层中的过孔和设置在所述邦定区层间绝缘层中的过孔与所述第一引线连接部电连接,所述第二导体部位于所述第一导体部背离所述衬底基板的一侧并且覆盖所述第一导体部。

[0039]

例如,所述多个输入接触垫和所述多个输出接触垫中的所述至少一个还包括:

[0040]

第三导体部,位于所述第二导体部背离所述衬底基板的一侧,与所述第二导体部电连接。

[0041]

例如,所述显示基板还包括:

[0042]

邦定区阻挡层,位于所述邦定区,覆盖所述第二导体层和所述接触垫绝缘层的第一部分,

[0043]

邦定区无机层,位于所述邦定区,覆盖所述邦定区阻挡层,所述第三导体部通过设置在所述邦定区阻挡层中的过孔和设置在所述邦定区无机层中的过孔与所述第二导体部电连接。

[0044]

例如,所述多个第一虚拟接触垫中的至少一个包括第四导体部,所述第四导体部位于所述衬底基板面向所述多个输入接触垫和所述多个输出接触垫的一侧,所述第四导体部的边缘被所述接触垫绝缘层的第一部分覆盖,

[0045]

其中所述多个输入接触垫和所述多个输出接触垫中的至少一个包括第一引线连接部、第一导体部和第二导体部,所述第四导体部与所述第二导体部同层设置。

[0046]

例如,所述多个第一虚拟接触垫中的至少一个还包括第五导体部,所述第五导体部位于所述第四导体部与所述衬底基板之间并且与所述第四导体部电连接,所述第五导体部与所述第一导体部同层设置。

[0047]

例如,所述多个阵列测试接触垫中的至少一个包括:

[0048]

第二引线连接部,位于所述衬底基板面向所述多个输入接触垫和所述多个输出接触垫的一侧;

[0049]

第六导体部,位于所述第二引线连接部背离所述衬底基板的一侧,与所述第二引线连接部电连接;

[0050]

第七导体部,位于所述第六导体部背离所述衬底基板的一侧,与所述第六导体部电连接,所述第七导体部的边缘被所述接触垫绝缘层的第一部分覆盖,

[0051]

其中所述多个输入接触垫和所述多个输出接触垫中的至少一个包括第一引线连接部、第一导体部和第二导体部,所述第二引线连接部、所述第六导体部和所述第七导体部分别与所述第一引线连接部、所述第一导体部和所述第二导体部同层设置。

[0052]

例如,所述多个第二虚拟接触垫中的至少一个包括第八导体部,所述第八导体部位于所述衬底基板面向所述多个输入接触垫和所述多个输出接触垫的一侧,所述第八导体部的边缘被所述接触垫绝缘层的第一部分覆盖,

[0053]

其中所述多个输入接触垫和所述多个输出接触垫中的至少一个包括第一引线连接部、第一导体部和第二导体部,所述第八导体部与所述第二导体部同层设置。

[0054]

例如,所述多个第二虚拟接触垫中的至少一个还包括第九导体部,所述第九导体部位于所述第八导体部与所述衬底基板之间并且与所述第八导体部电连接,所述第九导体部与所述第一导体部同层设置。

[0055]

例如,所述多个子像素中至少一个包括像素驱动电路、第一平坦化层、第一转接电极、第二平坦化层以及发光元件,

[0056]

所述第一平坦化层在所述像素驱动电路远离所述衬底基板的一侧以提供第一平坦化表面;

[0057]

所述第一转接电极在所述第一平坦化表面上,且通过设置在所述第一平坦化层中的过孔与所述像素驱动电路电连接;

[0058]

所述第二平坦化层在所述第一转接电极远离所述衬底基板的一侧以提供第二平坦化表面;

[0059]

所述发光元件在所述第二平坦化表面上且通过设置在所述第二平坦化层中的过孔与所述第一转接电极电连接;

[0060]

其中,所述接触垫绝缘层与所述第二平坦化层同层设置。

[0061]

例如,所述像素驱动电路包括薄膜晶体管,所述薄膜晶体管包括栅极、源极和漏极,所述多个输入接触垫和所述多个输出接触垫中的至少一个包括第一引线连接部、第一导体部和第二导体部,其中,

[0062]

所述第一引线连接部与所述栅极同层设置;

[0063]

所述第一导体部与所述源极和漏极同层设置,

[0064]

所述第二导体部与所述第一转接电极同层设置。

[0065]

例如,所述显示基板还包括显示区钝化层,所述显示区钝化层位于所述像素驱动电路和所述第一平坦化层之间,所述像素驱动电路和所述第一转接电极还通过设置在所述显示区钝化层中的过孔电连接;

[0066]

所述显示基板还包括邦定区钝化层,所述邦定区钝化层和所述显示区钝化层同层设置。

[0067]

例如,所述显示基板还包括位于显示区的封装层、显示区阻挡层、第一触控电极层、第二触控电极层和触控绝缘层,所述封装层位于所述发光元件的远离所述衬底基板的一侧,所述显示区阻挡层位于所述封装层的远离所述衬底基板的一侧,所述第一触控电极层位于所述显示区阻挡层背离所述衬底基板的一侧,所述触控绝缘层位于所述第一触控电极层背离所述衬底基板的一侧并且覆盖所述第一触控电极层,所述第二触控电极层位于所述触控绝缘层背离所述衬底基板的一侧;

[0068]

所述显示基板还包括位于邦定区的邦定区阻挡层和邦定区无机层,所述多个输入接触垫和所述多个输出接触垫中的至少一个还包括第三导体部,所述邦定区阻挡层、所述邦定区无机层和所述第三导体部分别与所述显示区阻挡层、所述触控绝缘层和所述第二触控电极层位于同层。

[0069]

例如,所述多个子像素中至少一个还包括显示区层间绝缘层、显示区第一栅绝缘层以及显示区第二栅绝缘层,所述显示区层间绝缘层位于所述栅极与所述源极和所述漏极之间,所述显示区第一栅绝缘层位于所述显示区层间绝缘层面向所述衬底基板的一侧,所述显示区第二栅绝缘层位于所述显示区层间绝缘层与所述显示区第一栅绝缘层之间;

[0070]

所述显示基板还包括邦定区层间绝缘层、邦定区第一栅绝缘层和所述邦定区第二栅绝缘层,所述邦定区层间绝缘层、所述邦定区第一栅绝缘层和所述邦定区第二栅绝缘层分别与所述显示区层间绝缘层、所述显示区第一栅绝缘层和所述显示区第二栅绝缘层同层设置。

[0071]

例如,所述多个子像素中至少一个还包括存储电容器,所述存储电容器的第一极与所述栅极同层设置,所述存储电容器的第二极设置在所述显示区层间绝缘层与所述显示区第二栅绝缘层之间。

[0072]

例如,所述衬底基板包括:

[0073]

第一柔性层,

[0074]

第二柔性层,位于所述第一柔性层面向所述多个输入接触垫和所述多个输出接触垫的一侧;

[0075]

第一衬底阻挡层,位于所述第一柔性层和所述第二柔性层之间;

[0076]

第二衬底阻挡层,位于所述第二柔性层背离所述第一柔性层的一侧;

[0077]

缓冲层,位于所述第二衬底阻挡层背离所述第一柔性层的一侧。

[0078]

本公开的实施例还提供了一种显示装置,包括上述显示基板。

附图说明

[0079]

图1a示出了根据本公开实施例的显示基板的示意图。

[0080]

图1b示出了图1a的显示基板的显示区的示意图。

[0081]

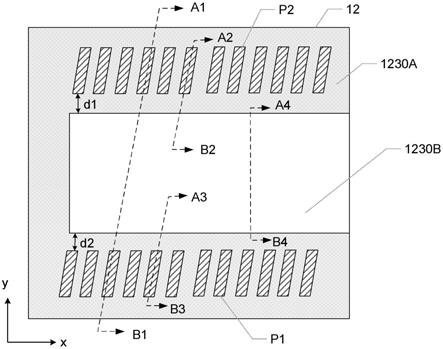

图2示出了根据本公开实施例的显示基板的邦定区的局部平面图。

[0082]

图3示出了图2的显示基板沿a1-b1的截面的示意图。

[0083]

图4a示出了图2的显示基板的一个示例沿a2-b2的截面图。

[0084]

图4b示出了图2的显示基板的一个示例沿a3-b3的截面图。

[0085]

图4c示出了图2的显示基板的一个示例沿a4-b4的截面图。

[0086]

图5示出了根据本公开一实施例的显示基板的显示区的截面图。

[0087]

图6a和图6b分别示出了图2的显示基板的另一个示例沿a2-b2和沿a3-b3的截面图。

[0088]

图7a和图7b分别示出了图2的显示基板的又一个示例在邦定区沿 a2-b2和沿a3-b3的截面图。

[0089]

图8a和图8b分别示出了图2的显示基板的再一个示例在邦定区沿 a2-b2和沿a3-b3的截面图。

[0090]

图9示出了根据本公开另一实施例的显示基板的显示区的截面图。

[0091]

图10示出了根据本公开另一实施例的显示基板的邦定区的局部平面图。

[0092]

图11示出了图10的显示基板沿c1-d1的截面的示意图。

[0093]

图12a示出了图11的显示基板的一个示例沿c2-d2的截面图。

[0094]

图12b示出了图11的显示基板的另一个示例沿c2-d2的截面图。

[0095]

图12c示出了图11的显示基板的又一个示例沿c2-d2的截面图。

[0096]

图13示出了根据本公开又一实施例的显示基板的邦定区的局部平面图。

[0097]

图14示出了图13的显示基板沿e1-f1的截面的示意图。

[0098]

图15a示出了图13的显示基板的一个示例沿e2-f2的截面图。

[0099]

图15b示出了图13的显示基板的一个示例沿e3-f3的截面图。

[0100]

图15c示出了图13的显示基板的另一个示例沿e3-f3的截面图。

[0101]

图15d示出了图13的显示基板的又一个示例沿e3-f3的截面图。

[0102]

图16a示出了根据本公开另一实施例的显示基板的显示区的截面图。

[0103]

图16b示出了图16a的显示基板的邦定区的截面图。

[0104]

图17a至图17g示出了根据本公开实施例的显示基板的制造过程的示意图。

具体实施方式

[0105]

虽然将参照含有本公开的较佳实施例的附图充分描述本公开,但在此描述之前应了解本领域的普通技术人员可修改本文中所描述的公开,同时获得本公开的技术效果。因此,须了解以上的描述对本领域的普通技术人员而言为一广泛的揭示,且其内容不在于限制本公开所描述的示例性实施例。

[0106]

另外,在下面的详细描述中,为便于解释,阐述了许多具体的细节以提供对本披露实施例的全面理解。然而明显地,一个或多个实施例在没有这些具体细节的情况下也可以被实施。在其他情况下,公知的结构和装置以图示的方式体现以简化附图。

[0107]

图1a示出了根据本公开实施例的显示基板的示意图。图1b示出了图1a的显示基板的显示区的示意图。

[0108]

如图1a和图1b所示,显示基板包括衬底基板10,衬底基板10包括显示区11、位于显示区11至少一侧的邦定区12和位于显示区至少另一侧的侧边区13。在图1a中,邦定区12沿y方向位于显示区11的一侧,侧边区13沿x方向位于显示区11的两侧。显示区11中设有多个子像素 pix。多个子像素pix可以布置成阵列的形式。在图1b中,x表示子像素阵列的行方向,y表示子像素阵列的列方向。显示区11还设有多条栅极线g1至gn以及多条数据线d1至dm,每条栅极线g1至gn与至少一行子像素pix连接,以向该行子像素pix提供栅极驱动信号,每条数据线 d1至dm与至少一列子像素pix连接以向该列子像素pix提供数据信号。每个子像素pix可以在与之连接的栅极线上的栅极驱动信号的控制下开启,开启的子像素pix可以在与之连接的数据线上的数据信号的驱动下发光。

[0109]

栅极驱动电路130位于侧边区13,在图1a中栅极驱动电路130有两个,分别位于显示区11两侧的侧边区13。栅极驱动电路130与所述多个子像素pix连接。在图1a和图1b中,栅极驱动电路130通过多条栅极线g1至gn连接至多行子像素pix,以分别向各行子像素pix提供栅极驱动信号。如图1a所示,栅极驱动电路130还连接各种驱动控制信号线,例如用于提

供第一时钟信号的第一时钟信号线ck1、用于提供第二时钟信号的第二时钟信号线ck2以及用于提供启动信号的启动信号线stv。栅极驱动电路130可以包括多级级联的移位寄存器goa0至goan,各级移位寄存器goa0至goan连接相应的驱动控制信号线,以在驱动控制信号的控制下产生栅极驱动信号并提供至显示区11的子像素pix。

[0110]

多个输入接触垫p1和多个输出接触垫p2位于邦定区12,所述多个输出接触垫p2位于所述多个输入接触垫p1与显示区11之间。在图1a 中,所述多个输入接触垫p1沿第一方向排列成至少第一行,所述第一方向为所述显示区11的面向所述邦定区12的侧边的延伸方向,即x方向。所述多个输出接触垫p2沿第一方向排列成至少第二行。

[0111]

所述多个输入接触垫p1用于与外部电路电连接,所述多个输出接触垫p2与显示区11中的子像素pix和栅极驱动电路130电连接。例如多个输入接触垫p1可以通过多条第一引线w1分别连接至区域1220中用于连接柔性电路板的多个连接接触垫。多个输出接触垫p2可以通过多条第二引线w2分别连接至显示区11中的子像素pix和栅极驱动电路13。例如图1a中左右两侧的多个输出接触垫p2分别通过多条第二引线w2连接至第一时钟信号线ck1、第二时钟信号线ck2和启动信号线stv,从而连接至栅极驱动电路13;图1a中位于中间的多个输出接触垫p2分别通过多条第二引线w2连接至显示区11中的数据线d1至dm,从而连接至显示区11中的子像素pix。在一些实施例中,邦定区12中可以设置例如单元测试(ct,cell test)电路、静电防护(esd,electro-static discharge) 电路、多路复用电路等结构。例如单元测试电路可以设置在多个输出接触垫p2与显示区11之间的区域中,单元测试电路可以连接至多条测试信号线和显示区中的多个子像素。例如多路复用电路可以设置在单元测试电路与所述多个输出接触垫p2之间的区域,多路复用电路可以与至少一个输出接触垫p2以及显示区的数据线链接,以将输出接触垫p2提供的数据信号进行多路复用之后提供至显示区的数据线。当然本公开的实施例不限于此。在一些实施例中,单元测试电路、静电防护电路、多路复用电路以及其他辅助电路中的至少之一可以设置在输入接触垫p1与输出接触垫 p2之间的区域中,在另一些实施例中可以位于输出接触垫p2与以下描述的第一虚拟接触垫p3之间的区域中。

[0112]

在将控制芯片连接到显示基板时,输入接触垫p1与控制芯片的输入引脚连接,输出接触垫p2与控制芯片的输出引脚连接。柔性电路板提供的信号(例如但不限于电源信号、控制信号等)通过输入接触垫p1提供给控制芯片,使得控制芯片产生驱动信号(例如但不限于时钟信号、启动信号、数据信号等等)。控制芯片产生的驱动信号通过输出接触垫p2提供至显示区11的子像素pix和/或栅极驱动电路,例如控制芯片产生的数据信号通过位于中间部分的输出接触垫p2提供至数据线d1至dm,从而提供给显示区11中的子像素;控制芯片产生的第一时钟信号、第二时钟信号和启动信号stv分别通过位于两侧的输出接触垫p2提供给第一时钟信号线ck1、第二时钟信号线ck2和启动信号线stv,从而提供给栅极驱动电路130。

[0113]

在邦定区12中,位于所述多个输入接触垫p1与所述多个输出接触垫p2之间的区域1210中的接触垫绝缘层被至少部分地去除,从而缓解由于该区域1210中的接触垫绝缘层而导致的与控制芯片接触不良。下面将参考图2至图15c来对此进行详细说明。

[0114]

图2示出了根据本公开实施例的显示基板的邦定区的局部平面图,图 3示出了图2的邦定区沿a1-b1的截面的示意图。需要说明的是,图2 为了便于描述仅示出了图1a的邦定

区的一侧部分(图2中为左侧部分),邦定区的另一侧部分可以具有类似结构,例如相对于左侧部分而对称的结构。另外需要说明的是,图3的截面图仅仅是为了说明接触垫绝缘层的第一部分和第二部分的位置关系以及厚度的区别,邦定区的层结构的更多细节将在下文进一步详细说明。

[0115]

如图2和图3所示,在邦定区12中,接触垫绝缘层1230位于所述多个输入接触垫p1中相邻输入接触垫p1之间的间隙、所述多个输出接触垫p2中相邻输出接触垫p2之间的间隙、以及所述多个输入接触垫p1与所述多个输出接触垫p2之间的区域。输入接触垫p1和输出接触垫p2的背离衬底基板10的表面从接触垫绝缘层1230外露。根据本公开的实施例,接触垫绝缘层1230包括具有第一厚度的第一部分1230a和具有第二厚度的第二部分1230b,第二厚度小于第一厚度。输入接触垫p1和输出接触垫p2的边缘被接触垫绝缘层1230的第一部分1230a覆盖,接触垫绝缘层1230的第二部分1230b位于所述多个输入接触垫p1与所述多个输出接触垫p1之间的区域中。如图2所示,输入接触垫p1在衬底基板10上的投影与接触垫绝缘层1230的第二部分1230b在衬底基板10的投影之间存在间距d1,输出接触垫p2在衬底基板10上的投影与接触垫绝缘层 1230的第二部分1230b在衬底基板10的投影之间存在间距d2,d1和d2 可以在3微米至100微米的范围内。在一些实施例中,d1可以等于d2。

[0116]

图4a示出了图2的显示基板的一个示例在邦定区沿a2-b2的截面图。

[0117]

如图4a所示,输出接触垫p2包括第一引线连接部1241、第一导体部1242和第二导体部1243。第一引线连接部1241位于衬底基板10上。参考图1a,输出接触垫p2的第一引线连接部1241可以连接至邦定区的第二引线w2,从而与栅极驱动电路130或者与显示区11中的多个子像素中的至少一个电连接。

[0118]

第一导体部1242位于所述第一引线连接部1241背离衬底基板10的一侧,并且与第一引线连接部1241电连接。第二导体部1243位于第一导体部1242背离衬底基板10的一侧,并且与第一导体部1242电连接。

[0119]

显示基板的邦定区还设置有邦定区第一栅绝缘层1251、邦定区第二栅绝缘层1252、邦定区层间绝缘层1253和邦定区钝化层1254。邦定区第一栅绝缘层1251覆盖衬底基板10,第一引线连接部1241位于邦定区第一栅绝缘层1251背离衬底基板10的一侧。邦定区第二栅绝缘层1252位于邦定区第一栅绝缘层1251背离衬底基板10的一侧并且覆盖第一引线连接部1241。邦定区层间绝缘层1253位于邦定区第二栅绝缘层1252背离衬底基板10的一侧。邦定区钝化层1254位于邦定区层间绝缘层1253背离衬底基板10的一侧并且覆盖第一导体部1242。

[0120]

如图4a中的虚线框所示,第一导体部1242通过设置在邦定区第二栅绝缘层1252中的过孔和设置在邦定区层间绝缘层1253中的过孔与第一引线连接部1241电连接,第二导体部1243通过设置在邦定区钝化层1254 中的过孔与第一导体部1242电连接。在图4a中,邦定区第二栅绝缘层 1252、邦定区层间绝缘层1253和邦定区钝化层1254中均设置有多个过孔,例如3个。然而本公开的实施例不限于此,在本公开的其它示例中,过孔的数量也可以根据需要来设置,例如,2个或4个。

[0121]

如图4a所示,输出接触垫p2的第二导体部1243的边缘被接触垫绝缘层1230的厚度为h1的第一部分1230a覆盖,接触垫绝缘层1230的厚度为h2的第二部分1230b位于输入接触垫p1与输出接触垫p1之间的区域中,其中h2小于h1。这里所谓厚度可以指的是接触垫绝缘

层1230面相衬底基板10一侧的表面到背离衬底基板10一侧表面的距离。通过使厚度h2小于厚度h1,可以使接触垫绝缘层1230的第二部分1230b背离衬底基板10一侧的表面低于接触垫绝缘层1230的第一部分1230a背离衬底基板10一侧的表面,从而缓解接触垫绝缘层1230对于输出接触垫p2 与控制芯片的引脚之间的连接可靠性的影响,同时厚度较大的第一部分 1230a能够实现对输出接触垫p2的边缘进行包封,从而起到保护作用。

[0122]

图4b示出了图2的显示基板的一个示例在邦定区沿a3-b3的截面图。

[0123]

如图4b所示,输入接触垫p1的结构与输出接触垫p2可以基本相同,输出接触垫p2同样包括第一引线连接部1241、第一导体部1242和第二导体部1243,第一导体部1242通过邦定区第二栅绝缘层1252中的过孔和邦定区层间绝缘层1253中的过孔与第一引线连接部1241电连接,第二导体部1243通过邦定区钝化层1254中的过孔与第一导体部1242电连接。参考图1a,输入接触垫p1的第一引线连接部1241可以连接至邦定区12 中的第一引线w1,从而与区域1220中用于连接到外部电路的连接接触垫电连接。

[0124]

在一些实施例中,接触垫绝缘层1230的材料可以包括氧化硅、氮化硅、氮氧化硅等无机绝缘材料,或者可以包括聚酰亚胺、聚酞亚胺、聚酞胺、丙烯酸树脂、苯并环丁烯或酚醛树脂等有机绝缘材料。本公开的实施例对接触垫绝缘层的材料不做具体限定。第一导体部1242和第二导体部 1243的材料可以包括金属材料或者合金材料,例如由钼、铝及钛等形成的金属单层或多层结构。

[0125]

图4c示出了图2的显示基板的一个示例在邦定区沿a4-b4的截面图。

[0126]

本公开实施例的衬底基板10可以包括有机材料,例如聚酰亚胺、聚碳酸酯、聚丙烯酸酯、聚醚酰亚胺、聚醚砜、聚对苯二甲酸乙二醇酯和聚萘二甲酸乙二醇酯等树脂类材料中的一种或多种,衬底基板10可以为柔性基板或非柔性基板。在图4c中衬底基板10为柔性基板,衬底基板10 可以包括第一柔性层1010、第二柔性层1020、第一衬底阻挡层1030、第二衬底阻挡层1040和缓冲层1050。第二柔性层1020位于第一柔性层1010 面向所述多个输入接触垫p1和所述多个输出接触垫p2的一侧。第一衬底阻挡层1030位于所述第一柔性层1020和第二柔性层1020之间。第二衬底阻挡层1040,位于第二柔性层1020背离第一柔性层1010的一侧。缓冲层1050,位于第二衬底阻挡层1040背离第一柔性层1010的一侧。例如,缓冲层1050的材料可以包括氧化硅、氮化硅、氮氧化硅等绝缘材料。缓冲层1050即可以防止衬底基板10中的有害物质侵入显示基板的内部,又可以增加显示基板中的膜层在衬底基板10上的附着力。

[0127]

缓冲层1050背离第一柔性层1010一侧的表面上依次堆叠邦定区第一栅绝缘层1251、邦定区第二栅绝缘层1252、邦定区层间绝缘层1253、邦定区钝化层1254和接触垫绝缘层1230。接触垫绝缘层1230包括具有第一厚度的第一部分1230a和具有第二厚度的第二部分1230b,第二厚度小于第一厚度。输入接触垫p1和输出接触垫p2的边缘被接触垫绝缘层 1230的第一部分1230a覆盖,接触垫绝缘层1230的第二部分1230b位于所述多个输入接触垫p1与所述多个输出接触垫p1之间的区域中。

[0128]

图5示出了根据本公开一实施例的显示基板的显示区的截面图。

[0129]

如图5所示,显示区中的子像素可以包括像素驱动电路1120、第一平坦化层1130、第一转接电极1180、第二平坦化层1190以及发光元件 1140。

[0130]

像素驱动电路1120包括位于衬底基板10上的有源层1122、位于有源层1122远离衬

底基板1000一侧的显示区第一栅绝缘层1128、位于显示区第一栅绝缘层1128上的栅极11211,位于栅极11211远离衬底基板10一侧的显示区第二栅绝缘层1129,位于显示区第二栅绝缘层1129上的显示区层间绝缘层11210以及位于显示区层间绝缘层11210上的源极 1125及漏极1126。栅极11211可以与邦定区12中的第一引线连接部1241 同层设置。源极1125及漏极1126可以与邦定区12中的第一导体部1242 同层设置。因此,栅极11211和第一引线连接部1241可以在制备工艺中同层形成,例如采用同一材料层通过构图工艺形成。源极1125及漏极1126 与邦定区12中的第一导体部1242可以在制备工艺中同层形成,例如采用同一材料层通过构图工艺形成。显示区中的显示区第一栅绝缘层1128与邦定区中的邦定区第一栅绝缘层1251同层设置,显示区中的显示区第二栅绝缘层1129与邦定区中的邦定区第二栅绝缘层1252同层设置,显示区中的显示区层间绝缘层11211与邦定区层间绝缘层1253同层设置。

[0131]

在本公开上述实施例一些示例中,有源层1122可以包括源极区1123 和漏极区1124,以及包括位于源极区1123和漏极区1124之间的沟道区。显示区层间绝缘层11210、显示区第二栅绝缘层1129及显示区第一栅绝缘层1128具有过孔,以暴露源极区1123和漏极区1124。源极1125及漏极1126分别通过过孔与源极区1123和漏极区1124电连接。栅极11211 在垂直于衬底基板1000的方向上与有源层1122中位于源极区1123和漏极区1124之间的沟道区重叠。第一平坦化层1130位于源极1125及漏极 1126的上方,用于平坦化像素驱动电路1120远离衬底基板一侧的表面。第一平坦化层1130中形成过孔1131,以暴露源极1125或漏极1126(图中示出的情况)。在像素驱动电路1120和第一平坦化层1130之间形成显示区钝化层11110且显示区钝化层11110包括过孔11111。显示区钝化层 11110可以保护像素驱动电路的源极和漏极不被水汽腐蚀。显示区的邦定区钝化层1254可以与显示区钝化层11110同层设置。因此显示区的邦定区钝化层1254与显示区钝化层11110可以在制备工艺中同层形成,例如采用同一材料层通过构图工艺形成。

[0132]

第一平坦化层1130上形成第一转接电极1180。第一转接电极1180 通过过孔1131以及过孔11111与漏极1126电连接,该第一转接电极1180 可以避免直接在第一平坦化层1130和第二平坦化层1190中形成孔径过大的直通过孔,从而改善过孔电连接的质量,同时第一转接电极1180还可以与其他信号线(例如电源线等)等同层形成,由此不会导致工艺步骤增加。第一转接电极1180与接触垫1210的第二导体部1243同层设置,因此,第一转接电极1180与第二导体部1243可以在制备工艺中同层形成,例如采用同一材料层通过构图工艺形成,从而简化制备工艺。

[0133]

例如,第一转接电极1180的材料可以包括金属材料或者合金材料,例如钼、铝及钛等形成的金属单层或多层结构。

[0134]

例如,有源层1122的材料可以包括多晶硅或氧化物半导体(例如,氧化铟镓锌)。栅极11211的材料可以包括金属材料或者合金材料,例如钼、铝及钛等形成的金属单层或多层结构,例如,该多层结构为多金属层叠层(如钛、铝及钛三层金属叠层(ti/al/ti)。源极1125及漏极1126的材料可以包括金属材料或者合金材料,例如由钼、铝及钛等形成的金属单层或多层结构,例如,该多层结构为多金属层叠层(如钛、铝及钛三层金属叠层(ti/al/ti)。本公开的实施例对各功能层的材料不做具体限定。

[0135]

例如,显示区钝化层11110的材料可以包括有机绝缘材料或无机绝缘材料,例如,

氮化硅材料,由于其具有较高的介电常数且具有很好的疏水功能,能够很好的保护像素驱动电路不被水汽腐蚀。

[0136]

在本公开的一些示例中,如图5所示,像素驱动电路1120还可以包括第一显示金属层1127,第一显示区金属层1127与第一导体部1242同层设置。第一显示金属层1127包括像素驱动电路中上述薄膜晶体管的源极1125和漏极1126。源极1125和漏极1126与第一导体部1242同层设置。

[0137]

在本公开的一些示例中,如图5所示,第二平坦化层1190设置在第一转接电极1180远离衬底基板10的一侧,用以在第一转接电极1180远离衬底基板10一侧提供平坦化表面。在第二平坦化层1190中形成过孔 1191。第二平坦化层1190与邦定区1200中的接触垫绝缘层1230同层形成,因此第二平坦化层1190与接触垫绝缘层1230可以在制备工艺中同层形成,例如采用同一材料层通过构图工艺形成,从而简化制备工艺。

[0138]

例如,在第二平坦化层上形成发光元件1140,即发光元件1140设置在第二平坦化层1190远离衬底基板一侧。发光元件1140包括第一电极 1141、发光层1142及第二电极1143。发光元件的第一电极1141通过第二平坦化层1140中的第二过孔1191与第一转接电极1180电连接。第一电极1141上形成像素限定层1144,像素限定层1144包括多个开口,以限定多个像素单元。多个开口的每个暴露对应的第一电极1141;之后,发光层1142设置在像素限定层1144的多个开口中,第二电极1143设置在像素限定层1144以及发光层1142上,例如该第二电极1143可以设置在部分或整个显示区域中,从而在制备工艺中可以整面形成。

[0139]

例如,第二平坦化层1190的材料可以包括括氧化硅、氮化硅、氮氧化硅等无机绝缘材料,也可以包括聚酰亚胺、聚酞亚胺、聚酞胺、丙烯酸树脂、苯并环丁烯或酚醛树脂等有机绝缘材料,本公开的实施例对此不做限定。

[0140]

例如,第一电极1141可以包括反射层,第二电极1143可以包括透明层或半透明层。由此,第一电极1141可以反射从发光层1142发射的光,该部分光通过第二电极1143发射到外界环境中,从而可以提供光出射率。当第二电极1143包括半透射层时,由第一电极1141反射的一些光通过第二电极1143再次反射,因此第一电极1141和第二电极1143形成共振结构,从而可以改善光出射效率。

[0141]

例如,第一电极1141的材料可以包括至少一种透明导电氧化物材料,包括氧化铟锡(ito)、氧化铟锌(izo)、氧化锌(zno)等。此外,第一电极 1141可以包括具有高反射率的金属作为反射层,诸如银(ag)。

[0142]

例如,对于oled,发光层1142可以包括小分子有机材料或聚合物分子有机材料,可以为荧光发光材料或磷光发光材料,可以发红光、绿光、蓝光,或可以发白光;并且,根据需要发光层还可以进一步包括电子注入层、电子传输层、空穴注入层、空穴传输层等功能层。对于qled,发光层可以包括量子点材料,例如,硅量子点、锗量子点、硫化镉量子点、硒化镉量子点、碲化镉量子点、硒化锌量子点、硫化铅量子点、硒化铅量子点、磷化铟量子点和砷化铟量子点等,量子点的粒径为2-20nm。

[0143]

例如,第二电极1143可以包括各种导电材料。例如,第二电极1143 可以包括锂(li)、铝(al)、镁(mg)、银(ag)等金属材料。

[0144]

例如,像素限定层1144的材料可以包括聚酰亚胺、聚酞亚胺、聚酞胺、丙烯酸树脂、苯并环丁烯或酚醛树脂等有机绝缘材料,或者包括氧化硅、氮化硅等无机绝缘材料,本公开

的实施例对此不做限定。

[0145]

此外,显示基板还包括存储电容器1160,存储电容器1160可以包括第一极1161和第二极1162。存储电容器1160的第一极1161设置在显示区第一栅绝缘层1128与显示区第二栅绝缘层1129之间,存储电容器1160 的第二极1162设置在显示区第二栅绝缘层1129与显示区层间绝缘层 11210之间。第一极1161和第二极1162叠置,在垂直于衬底基板10的方向上至少部分重叠。第一极1161和第二极1162使用显示区第二栅绝缘层1129作为介电材料来形成存储电容器。第一极1161与像素驱动电路 1120中的栅极11211、邦定区1200中的引线1220同层设置。同样地,如上所述,在上述示例的变型中,存储电容器1160的第一极和第二极还可以位于其他层中,从而得到不同结构的子像素。

[0146]

在另一示例中,作为图5所示示例的变型,存储电容器的第一极仍然与栅极11211同层设置,而存储电容器的第二极与薄膜晶体管中的源极 1125和漏极1126同层设置(即也位于第一显示金属层1127中),由此存储电容器的第一极和第二极使用显示区第二栅绝缘层1129以及显示区层间绝缘层11210的叠层来作为介电材料来形成存储电容器。

[0147]

在再一示例中,作为图5所示示例的变型,存储电容器的第一极不再与栅极11211同层设置,而是位于在显示区第二栅绝缘层1129与显示区层间绝缘层11210之间,而存储电容器的第二极与薄膜晶体管中的源极 1125和漏极1126同层设置(即也位于第一显示金属层1127中),由此存储电容器的第一极和第二极使用显示区层间绝缘层11210来作为介电材料来形成存储电容器。

[0148]

在本公开的一些示例中,如图5所示,显示基板还可以包括设置在发光元件1140上的封装层1150。封装层1150将发光元件1140密封,从而可以减少或防止由环境中包括的湿气和/或氧引起的发光元件1140的劣化。封装层1150可以为单层结构,也可以为复合层结构,该复合层结构包括无机层和有机层堆叠的结构,例如,封装层1150可以包括依次设置的第一无机封装层1151、第一有机封装层1152、第二无机封装层1153。封装层1150可以延伸至邦定区,在上述示例中,该封装层未覆盖接触垫。

[0149]

例如,该封装层的材料可以包括氮化硅、氧化硅、氮氧化硅、高分子树脂等绝缘材料。氮化硅、氧化硅、氮氧化硅等无机材料的致密性高,可以防止水、氧等的侵入;有机封装层的材料可以为含有干燥剂的高分子材料或可阻挡水汽的高分子材料等,例如高分子树脂等以对显示基板的表面进行平坦化处理,并且可以缓解第一无机封装层和第二无机封装层的应力,还可以包括干燥剂等吸水性材料以吸收侵入内部的水、氧等物质。

[0150]

图6a和图6b分别示出了图2的显示基板的另一个示例沿a2-b2和沿a3-b3的截面图。图6a和图6b的邦定区域图4a和图4b相比区别至少在于输入接触垫p1和输出接触垫p2还包括第三导体部,为了简明起见,下面将主要对区别部分进行详细说明。

[0151]

如图6a所示,输出接触垫p2除了包括上述第一引线连接部1241、第一导体部1242和第二导体部1243之外还包括第三导体部1244。显示基板还包括邦定区阻挡层1255和邦定区无机层1256。第三导体部1244 位于所述第二导体部1243背离衬底基板10的一侧,邦定区阻挡层1255 和邦定区无机层1256位于第三导体部1244与第二导体部1243之间。邦定区阻挡层1255覆盖第二导体层1243和接触垫绝缘层1230的第一部分 1230a,邦定区无机层1256覆盖邦定区阻挡层1255。第三导体部1244 通过设置在邦定区阻挡层1255中的过孔和设置在邦定区无机层1256中的过孔(如图6a中的虚线框所示)与第二导体部1243电连接。

[0152]

如图6b所示,输入接触垫p1具有与输出接触垫p2基本相同的结构,这里不再赘述。

[0153]

图7a和图7b分别示出了图2的显示基板的又一个示例沿a2-b2和沿a3-b3的截面图。图7a和图7b的邦定区域图6a和图6b相比区别至少接触垫绝缘层的第二部分被去除,即,第二厚度为0。如图7a和7b 所示,接触垫绝缘层1230’的第二部分1230b的厚度为0,即接触垫绝缘层1230’的第二部分1230b被去除,而保留第一部分1230a。邦定区钝化层1254位于第二部分1230b与邦定区第二栅绝缘层1254之间的部分厚度大于0,即被至少部分保留。

[0154]

图8a和图8b分别示出了图2的显示基板的再一个示例沿a2-b2和沿a3-b3的截面图。图8a和图8b的邦定区域图7a和图7b相比区别至少钝化层也被部分地去除。如图8a和8b所示,接触垫绝缘层1230’的第二部分1230b及其下方的邦定区钝化层1254部分均被去除,使得第二部分1230b厚度为0,且邦定区钝化层1254位于接触垫绝缘层1230’的第二部分1230b与邦定区第二栅绝缘层1254之间的部分厚度也为0。

[0155]

图9示出了根据本公开另一实施例的显示基板的显示区的截面图。图 9的显示区结构与图5相比区别至少在于显示基板还包括显示区阻挡层、第一触控电极层、第二触控电极层和触控绝缘层,为了简明起见,下面将主要对区别部分进行详细说明。

[0156]

如图9所示,封装层1150位于发光元件1140的远离衬底基板10的一侧,显示区阻挡层1171位于封装层1150的远离衬底基板10的一侧,第一触控电极层1172位于显示区阻挡层1171背离衬底基板10的一侧,触控绝缘层1174位于第一触控电极层1172背离衬底基板10的一侧并且覆盖第一触控电极层1172,第二触控电极层1173位于触控绝缘层1174 背离衬底基板10的一侧。在图9中,第二触控电极层1173通过触控绝缘层1174中的过孔与第一触控电极层1172电连接,当然本公开实施例不限于此,第一触控电极层1172和第二触控电极层1173可以根据需要而设置成其他图案。第一触控电极层1172和第二触控电极层1173可以用于实现电容型触控结构,该电容型触控结构为自电容型或互电容型。

[0157]

上述位于邦定区的第三导体部1244可以与显示区的第二触控电极层 1173同层设置,上述位于邦定区的邦定区阻挡层1255可以与显示区的显示区阻挡层1171同层设置,上述位于邦定区的邦定区无机层1256可以与显示区的触控绝缘层1174同层设置。

[0158]

图10示出了根据本公开另一实施例的显示基板的邦定区的局部平面图。图11示出了图10的邦定区沿c1-d1的截面的示意图。图10和图11 的显示基板与图2和图3的显示基板相比区别至少在于邦定区12还设置有多个第一虚拟接触垫p3,为了简明起见,下面将主要对区别部分进行详细说明。

[0159]

如图10和图11所示,显示基板还包括多个第一虚拟接触垫p3,所述多个第一虚拟接触垫p3位于邦定区12,且位于多个输入接触垫p1与多个输出接触垫p2之间的区域中。第一虚拟接触垫p3可以不连接引线,其可以在控制芯片邦定到显示基板的邦定区时,第一虚拟接触垫p3与控制芯片上的对应引脚对接,从而起到支撑作用。第一虚拟接触垫p3的边缘被所述接触垫绝缘层1230的第一部分1230a覆盖,第一虚拟接触垫 p3的背离衬底基板10的表面从接触垫绝缘层1230的第一部分1230a外露。接触垫绝缘层1230第二部分1230b包括第一子部分1230b1和第二子部分1230b2,第一子部分1230b1位于所述多个第一虚拟接触垫p3与所述多个输入接触垫p1之间的区域,所述第二子部分1230b2位于所述多个第一虚拟接触垫p3与所述多个输出接触垫p2之间的区域。

[0160]

图12a示出了图10的显示基板的一个示例沿c2-d2的截面图。

[0161]

如图12a所示,第一虚拟接触垫p3包括第四导体部1245。衬底基板10上依次叠置邦定区第一栅绝缘层1251、邦定区第二栅绝缘层1252、邦定区层间绝缘层1253和邦定区钝化层1254。第四导体部1245位于邦定区钝化层1254背离衬底基板10的一侧,即位于衬底基板10面向所述多个输入接触垫p1和所述多个输出接触垫p2的一侧。接触垫绝缘层1230 的第一部分1230a覆盖第四导体部1245的边缘,接触垫绝缘层1230的第二部分1230b包括第一子部分1230b1和第二子部分1230b2,其厚度小于第一部分1230a的厚度。第四导体部1245可以与上述的第二导体部 1243同层设置,例如第四导体部1245和第二导体部1243可以均与显示区的第一转接电极1180同层设置。

[0162]

图12b示出了图11的显示基板的另一个示例沿c2-d2的截面图。图 12b的显示基板与图12a的显示基板相比区别至少在于接触垫绝缘层的第二部分和邦定区钝化层的一部分被去除。如图12b所示,接触垫绝缘层1230’的第二部分1230b及其下方的邦定区第一栅绝缘层1251的一部分被去除,即,二者厚度均为0。

[0163]

图12c示出了图11的邦定区的又一个示例在邦定区沿c2-d2的截面图。图12c的显示基板与图12a的显示基板相比区别至少在于第一虚拟接触垫p3除了包括第四导体部1245’之外还包括第五导体部1246,第五导体部1246位于第四导体部1245与衬底基板10之间。

[0164]

在图12c中,衬底基板10上依次叠置邦定区第一栅绝缘层1251、邦定区第二栅绝缘层1252和邦定区层间绝缘层1253。第五导体部1246位于邦定区层间绝缘层1253背离衬底基板10的一侧。邦定区钝化层1254 位于邦定区层间绝缘层1253背离衬底基板10的一侧并且覆盖第五导体部 1246的边缘。第四导体部1245’位于第五导体部1246背离衬基板10的一侧,第四导体部的边缘被所述接触垫绝缘层的第一部分覆盖。第五导体部 1246通过邦定区钝化层1254中的过孔与第四导体部1245电连接。第四导体部1245’可以与上述第二导体部1243同层设置,第五导体部1246可以与上述的第一导体部1242同层设置。例如第四导体部1245’可以与上述第二导体部1243和显示区的第一转接电极1180同层设置,第五导体部 1246可以与上述第一导体部1242和显示区的第一显示金属层1127同层设置。

[0165]

图13示出了根据本公开又一实施例的显示基板的邦定区的局部平面图,图14示出了图13的显示基板沿e1-f1的截面的示意图。与图2和图 10的单侧示意不同,图13的平面图示出了显示基板的邦定区沿x方向的左右两侧部分。图13和图14的显示基板与图10和图11的显示基板相比区别至少在于邦定区12还设置有多个阵列测试接触垫p4和多个第二虚拟接触垫p5,为了简明起见,下面将主要对区别部分进行详细说明。

[0166]

如图13和图14所示,显示基板的邦定区还设置有还多个阵列测试接触垫p4,多个阵列测试接触垫p4位于所述多个第一虚拟接触垫p1与所述多个输入接触垫p2之间的区域中。多个阵列测试接触垫p4用于在显示基板制作过程中的阵列测试。阵列测试接触垫p4可以与所述多个子像素。例如阵列测试接触垫p4中的至少一个可以通过邦定区的引线连接到显示区的子像素,例如通过引线连接到多路复用电路,以经由多路复用电路连接到显示区的多条数据信号线,从而实现与子像素的电连接。

[0167]

如图13和图14所示,接触垫绝缘层1230的第一部分1230a包括第一子部分1230a1和第二子部分1230a2。所述多个输入接触垫p1的边缘、所述多个输出接触垫p2的边缘和所述第一虚拟接触垫p3的边缘被所述接触垫绝缘层1230的第一部分1230a的第一子部分

1230a1覆盖。多个阵列测试接触垫p4的边缘被所述接触垫绝缘层1230的第一部分1230a 的第二子部分1230a2覆盖,所述多个阵列测试接触垫p4的背离衬底基板10的表面从所述接触垫绝缘层1230的第一部分1230a的第二子部分 1230a1外露。在一些实施例中,如图13所示,接触垫绝缘层1230的第一部分1230a的第二子部分1230a2在衬底基板10上的投影位于所述接触垫绝缘层1230的第二部分1230b的第一子部分1230b1在衬底基板10 的投影之内。接触垫绝缘层1230的这种设置使得可以在提高接触垫连接稳固性的同时,实现对输入接触垫p1、输出接触垫p2、第一虚拟接触垫 p3和阵列测试接触垫p4的边缘的保护,避免后续的构图工艺中的刻蚀液刻蚀裸露的接触垫的边缘,进而提高显示基板的产品良率和可靠性。

[0168]

在上述实施例中,多个输入接触垫p1沿第一方向排列成第一行,所述第一方向为显示区的面向邦定区的侧边的延伸方向(x方向);多个输出接触垫p2沿第一方向排列成第二行;多个第一虚拟接触垫沿第一方向排列成第三行;所述多个阵列测试接触垫沿第一方向排列成第四行。当然本公开的实施例不限于此,输入接触垫p1、输出接触垫p2、第一虚拟接触垫p3和阵列测试接触垫p4中的任意一者可以根据需要呈多行排列或者以其他形式排列。

[0169]

在一些实施例中,如图13所示,显示基板的邦定区还可以设置有多个第二虚拟接触垫p5。第二虚拟接触垫p5可以具有与第一虚拟接触垫 p4相似的结构,可以同样起到支撑作用。多个第二虚拟接触垫p5沿垂直于所述第一方向的第二方向(y方向)排列成第一列和第二列,其中第一列和第二列分别位于所述多个第一虚拟接触垫p1在第一方向上的两侧。当然本公开的实施例不限于此,多个第二虚拟接触垫p5可以根据需要呈多列排列或者以其他形式排列,也可以位于多个第一虚拟接触垫p1的一侧(例如左侧或右侧)。

[0170]

在图13中,多个第二虚拟接触垫p5的边缘被接触垫绝缘层1230的第一部分1230a覆盖,所述多个第二虚拟接触垫p5的背离衬底基板10 的表面从所述接触垫绝缘层1230的第一部分1230a外露。在一些实施例中,如图13所示,输入接触垫p1、输出接触垫p2、第一虚拟接触垫p3、阵列测试接触垫p4和第二虚拟接触垫p5各自在衬底基板10上的投影与接触垫绝缘层1230的第二部分1230b在衬底基板10的投影之间均具有一定的间距,该间距可以在3微米至100微米的范围内。输入接触垫p1、输出接触垫p2、第一虚拟接触垫p3、阵列测试接触垫p4和第二虚拟接触垫p5各自与接触垫绝缘层1230的第二部分1230b的间距可以相同或不同。例如输入接触垫p1、输出接触垫p2和第二虚拟接触垫p5与接触垫绝缘层1230的第二部分1230b的间距可以相等,但是大于第一虚拟接触垫p3和阵列测试接触垫p4与接触垫绝缘层1230的第二部分1230b的间距。

[0171]

在上述实施例中,输入接触垫p1、输出接触垫p2、第一虚拟接触垫 p3、阵列测试接触垫p4和第二虚拟接触垫p5各自在衬底基板10上的投影被示出为具有特定的形状,例如输入接触垫p1和输出接触垫p2在衬底基板10上的投影为平行四边形,阵列测试接触垫p4和第二虚拟接触垫p5在衬底基板10上的投影为矩形,第一虚拟接触垫p3在衬底基板10 上的投影基本上为正方形。在图13中,输入接触垫p1、输出接触垫p2、第一虚拟接触垫p3、阵列测试接触垫p4和第二虚拟接触垫p5各自均沿着显示基板在y方向上的对称轴y而对称设置。然而本公开的实施例不限于此,各个接触垫的形状和排列方式可以根据需要来设置。

[0172]

图15a示出了图13的显示基板的一个示例沿e2-f2的截面图。

[0173]

如图15a所示,阵列测试接触垫p5具有类似于图4a的输出接触垫和图4b的输入接

触垫的结构。阵列测试接触垫p5包括第二引线连接部 1247、第六导体部1248和第七导体部1249。第二引线连接部1247、所述第六导体部1248和所述第七导体部1249可以分别与所述第一引线连接部 1241、所述第一导体部1242和所述第二导体部1243同层设置。

[0174]

第二引线连接部1247位于衬底基板10面向所述多个输入接触垫p1 和所述多个输出接触垫p2的一侧,用于与引线连接,所述引线连接到数据线,从而实现第二引线连接部1247与显示区的子像素的电连接。第六导体部1248位于第二引线连接部1247背离所述衬底基板10的一侧,与第二引线连接部1247电连接。第七导体部1249位于第六导体部1247背离所述衬底基板10的一侧,与所述第六导体部1248电连接。

[0175]

第二虚拟接触垫p5可以具有与上述第一虚拟接触垫p4相似的结构,下面将参考图15b至图15d来进行说明。

[0176]

图15b示出了图13的显示基板的一个示例沿e3-f3的截面图。如图 15b所示,第二虚拟接触垫p5具有与图12a的第一虚拟接触垫p4类似的结构,第二虚拟接触垫p5包括第八导体部12410,第八导体部12410 位于衬底基板面10向所述多个输入接触垫p1和所述多个输出接触垫p2 的一侧。第八导体部12410可以与上述第二导体部1243同层设置。第八导体部12410’的边缘被接触垫绝缘层1230的第一部分1230a覆盖,在图15d中接触垫绝缘层1230的第一部分1230a的第一子部分1230a1覆盖。

[0177]

图15c示出了图13的显示基板的另一个示例沿e3-f3的截面图。图 15c的显示基板与图15b的显示基板相比区别至少在于接触垫绝缘层 1230的第二部分1230b和邦定区钝化层1241的一部分被去除。如图15c 所示,接触垫绝缘层1230’的第二部分1230b及其下方的邦定区第一栅绝缘层1251的厚度均为0。

[0178]

图15d示出了图13的显示基板的另一个示例沿e3-f3的截面图。如图15d所示,第二虚拟接触垫p5具有类似于图12c的第一虚拟接触垫 p4的结构,第二虚拟接触垫p5除了包括第八导体部12410’之外还包括第九导体部12411,第九导体部12411位于第八导体部12410’与衬底基板10 之间并且与第八导体部12410’电连接。第八导体部12410’可以与上述第二导体部1243同层设置,第九导体部可以与上述第一导体部1242同层设置。第八导体部12410’的边缘被接触垫绝缘层1230的第一部分1230a 覆盖,在图15d中接触垫绝缘层1230的第一部分1230a的第一子部分 1230a1覆盖。

[0179]

虽然以上结合特定的接触垫结构说明了接触垫绝缘层的第二部分及其下方的邦定区钝化层被减薄或去除的实施例,然而本公开的实施例不限于此,接触垫绝缘层的第二部分及其下方的邦定区钝化层的减薄或去除适用于其他接触垫结构,例如在一些实施例中,图4a至图4c、图12c以及图15a和图15d中至少一个的接触垫绝缘层的第二部分和/或其下方的邦定区钝化层可以根据需要被减薄或去除。

[0180]

图16a示出了根据本公开另一实施例的显示基板的显示区的截面图图16b示出了图16a的显示基板的邦定区的截面图。图16a和图16b的显示基板与前述实施例的显示基板区别至少不具有钝化层。

[0181]

如图16a所示,显示基板的显示区具有类似于图9的显示区的结构,区别在于不具有显示区钝化层11110。如图16b所示,显示基板的邦定区具有类似于图7a和8a的邦定区的结构,区别在于不具有邦定区钝化层 1245、1245’,第二导体部1243位于第一导体部1242背离衬底基板10的一侧并且覆盖第一导体部1242,接触垫绝缘层1230’设置在邦定区层间绝

缘层1253背离衬底基板10的一侧且覆盖第二导体部1243的边缘。

[0182]

为了简明起见在图16b中仅示出了输出接触垫p2及其周围区域的邦定区结构,邦定区的其他部分可以与图4a至图4c、图6a至图8b、图 12a至图12c以及图15a至图15d描述的结构类似,区别在于从这些结构中去除了邦定区钝化层。

[0183]

本公开至少一个实施例提供一种显示装置,该显示装置可以包括上述任一实施例的显示基板。

[0184]

例如,在一些示例中,显示装置还可以包括柔性电路板及控制芯片。例如,柔性电路板邦定到显示基板的邦定区,而控制芯片安装在柔性电路板上,由此与显示区电连接;或者,控制芯片直接邦定到邦定区,由此与显示区电连接。

[0185]

例如,控制芯片可以为中央处理器、数字信号处理器、系统芯片(soc) 等。例如,控制芯片还可以包括存储器,还可以包括电源模块等,且通过另外设置的导线、信号线等实现供电以及信号输入输出功能。例如,控制芯片还可以包括硬件电路以及计算机可执行代码等。硬件电路可以包括常规的超大规模集成(vlsi)电路或者门阵列以及诸如逻辑芯片、晶体管之类的现有半导体或者其它分立的元件;硬件电路还可以包括现场可编程门阵列、可编程阵列逻辑、可编程逻辑设备等。

[0186]

例如,本公开至少一个实施例提供的显示装置可以为手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件。

[0187]

本公开至少一个实施例还提供一种显示基板的制备方法,该方法包括:提供衬底基板,所述衬底基板包括显示区、位于所述显示区至少一侧的邦定区和位于所述显示区至少另一侧的侧边区;在所述显示区中形成多个子像素;在所述侧边区形成栅极驱动电路,所述栅极驱动电路与所述多个子像素连接,并且被配置为向所述多个子像素提供栅极驱动信号;在所述邦定区形成用于与外部电路电连接的多个输入接触垫;在所述邦定区中形成多个输出接触垫,所述多个输出接触垫位于所述多个输入接触垫与所述显示区之间,所述多个输出接触垫与所述多个子像素和所述栅极驱动电路电连接;在所述邦定区形成接触垫绝缘层,所述接触垫绝缘层位于所述多个输入接触垫中相邻输入接触垫之间的间隙、所述多个输出接触垫中相邻输出接触垫之间的间隙、以及所述多个输入接触垫与所述多个输出接触垫之间的区域,所述多个输入接触垫和所述多个输出接触垫的背离所述衬底基板的表面从所述接触垫绝缘层外露,其中所述接触垫绝缘层包括具有第一厚度的第一部分和具有第二厚度的第二部分,所述第二厚度小于所述第一厚度,所述多个输入接触垫和所述多个输出接触垫的边缘被所述接触垫绝缘层的第一部分覆盖,所述接触垫绝缘层的第二部分位于所述多个输入接触垫与所述多个输出接触垫之间的区域中。

[0188]

下面结合图8a和图9的显示基板,参考图17a至图17g来说明本公开实施例的显示基板的制造过程。

[0189]

如图17a所示,提供衬底基板10,该衬底基板10包括显示区和位于显示区周边的周边区,该周边区包括位于显示区至少一侧的至少一个邦定区和位于所述显示区至少另一侧的侧边区。在衬底基板10的显示区形成像素驱动电路1120、存储电容器1160、第一平坦化层1130和第一转接电极1180,在显示基板10的邦定区形成邦定区第一栅绝缘层1251、第一引线连接部1231、第二栅绝缘层1252、邦定区层间绝缘层1253、第一导体部1242、邦定区钝化层1254’和第二导体部1243。第二导体部1243覆盖第一导体部1242的边缘,以避免第一导体

部1242被腐蚀。在该实施例中,第一导体部1242和第二导体部1243层叠。

[0190]

如图17b所示,在衬底基板上沉积绝缘材料层1710,在绝缘材料层 1710上沉积光刻胶1720。绝缘材料层1710可以包括氧化硅、氮化硅、氮氧化硅等绝缘材料。

[0191]

如图17c所示,提供掩膜版1610对光刻胶1720进行曝光,掩膜版 1610包括完全透光区、部分透光区及不透光区。掩膜版1610在邦定区包括与要形成接触垫绝缘层1230的第二部分1230b的区域重叠的第一透光图案1611及与输出接触垫p2重叠的第二透光图案1612。掩膜版1610在显示区包括与第二透光图案1612及非透光图案1613。第一透光图案1611 位于部分透光区,第二透光图案1612位于完全透光区,非透光图案1613 位于不透光区。即,掩膜版1610为灰色掩膜版或半色调掩膜版。光刻胶为正性光刻胶,对应地,第一透光图案1611的透光率小于第二透光图案 1612的透光率。在曝光过程中,可以在使得光刻胶1720中与第二透光图案1612对应的部分被完全曝光的情况下,光刻胶1720中与第一透光图案 1611对应的部分被部分曝光。光刻胶1720在显示区与非透光图案1613 对应的部分未被曝光。

[0192]

又例如,在上述构图工艺中,也可以采用负性光刻胶,那么所采用的掩模板例如是与上述掩模板1610互补的掩模板,由此在曝光、显影后得到上述光刻胶图案1721及光刻胶图案1722。

[0193]

如图17d所示,对光刻胶1720进行显影,光刻胶1720的被完全曝光的部分去除,即,在邦定区中,与输出接触垫p2以及要设置接触垫绝缘层的第二部分1230b的区域重叠的光刻胶1720被去除,光刻胶1720 的被部分曝光的部分被减薄,而光刻胶1720的未被曝光的部分的厚度例如基本未改变。显影后,光刻胶1720在邦定区形成为光刻胶图案1721。同样地,在显示区中,与漏极1126重叠的光刻胶1720被去除。显影后,光刻胶1720在显示区形成为光刻胶图案1722。

[0194]

如图17e所示,对邦定区及显示区中的绝缘材料层1710进行刻蚀以去除在邦定区域与输出接触垫p2和要设置接触垫绝缘层的第二部分 1230b的区域重叠的绝缘材料层,以及在显示区形成第二过孔1191。

[0195]

如图17f所示,进行灰化工艺去除邦定区的光刻胶图案1721和减薄显示区的光刻胶图案1722,这里显示区的光刻胶图案1722被保留。然后,利用当前的光刻胶图案,对邦定区中剩余的绝缘材料层1710进行刻蚀并控制刻蚀厚度以形成接触垫绝缘层1230,并且使得刻蚀后形成的接触垫绝缘层1230具有第一部分1230a以及厚度小于第一部分1230a的第二部分1230b,在图17f中第二部分1230b厚度为0,即该部分的绝缘材料被去除。这使得接触垫绝缘层的第二部分1230b相对于衬底基板10的表面的高度低于第一部分1230b相对于衬底基板1000的表面的高度。去除显示区的光刻胶图案1722。在显示区形成第二平坦化层1190以提供平坦化表面。在显示区的第二平坦化1190上形成发光元件1140。在显示区的发光元件1140上形成封装层1150。封装层1150将发光元件1140密封,从而可以减少或防止由环境中包括的湿气和/或氧引起的发光元件1140的劣化。

[0196]

如图17g所示,在显示区的封装层1150上形成显示区阻挡层1171,在邦定区形成邦定区阻挡层1255。然后,在显示区的显示区阻挡层1171 上形成第一触控电极层1172。在显示区的第一触控电极层1172上形成触控绝缘层1174,在邦定区的邦定区阻挡层1255上形成邦定区无机层1256。然后在显示区的触控绝缘层1174上形成第二触控电极层1173,在邦定

区的邦定区无机层1256上形成第三导体部1244。

[0197]

本领域的技术人员可以理解,上面所描述的实施例都是示例性的,并且本领域的技术人员可以对其进行改进,各种实施例中所描述的结构在不发生结构或者原理方面的冲突的情况下可以进行自由组合。

[0198]

在详细说明本公开的较佳实施例之后,熟悉本领域的技术人员可清楚的了解,在不脱离随附权利要求的保护范围与精神下可进行各种变化与改变,且本公开亦不受限于说明书中所举示例性实施例的实施方式。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1