分栅沟槽MOSFET的制作方法

分栅沟槽mosfet

技术领域

1.实用新型涉及一种分栅沟槽mosfet栅源漏电改善的工艺制造方法,属于半导体功率器件技术领域。

背景技术:

2.分栅沟槽mosfet利用氧化层电荷耦合原理,打破了传统沟槽功率mosfet的理论硅极限,使得n型漂移区即使在高掺杂浓度的条件下也能实现器件较高的击穿电压,从而获得低导通电阻,同时附加优良的开关特性,逐步取代了传统沟槽器件。而分栅沟槽mosfet结构中,栅源多晶硅之间隔离氧化层(inter

‑

poly oxide,简称ipo)的制作是分栅沟槽器件工艺中非常重要的部分,其制作工艺对器件性能以及成本有非常大的影响。

3.现有技术中分栅沟槽mosfet的ipo常规制作方法如下:

4.–

在n型外延层上利用光刻和刻蚀工艺制作深沟槽;

5.–

利用炉管在深沟槽侧壁及表面生长氧化层并填充源极多晶硅;

6.–

对源极多晶硅及侧壁氧化层回刻形成栅极沟槽;

7.–

利用hdp cvd工艺在栅极沟槽内填充氧化硅;

8.–

通过氧化硅cmp工艺将表面hdp氧化硅磨平;

9.–

利用湿法刻蚀对hdp氧化硅进行回刻,并在源极多晶硅上保留一定的厚度作为ipo;

10.该方法的ipo通过hdp回填及cmp研磨工艺实现,如图1所示。hdp填充工艺难度大,填充不好容易形成空洞1,湿法回刻时导致ipo厚度不均匀,引起栅源漏电发生,特别对于小尺寸元胞的器件问题尤为严重。另外,cmp研磨工艺成本高,不利于器件成本控制。

技术实现要素:

11.为解决上述问题,实用新型提供了一种分栅沟槽mosfet栅源漏电改善的工艺方法。本技术方案中,ipo通过bpsg淀积及高温回流,然后湿法腐蚀去除表面及沟槽侧壁多余氧化层而形成。

12.为了实现上述目的,实用新型的技术方案如下:一种分栅沟槽mosfet,该mosfet结构中栅源多晶硅间的隔离氧化层是通过在栅极沟槽内淀积一层氧化膜,再经高温退火回流形成。

13.作为实用新型的一种改进,所述氧化膜是硼磷硅玻璃bpsg。

14.一种分栅沟槽mosfet的工艺制造方法,制作过程包含如下步骤:

15.步骤一:在si衬底表面生长n型外延层;

16.步骤二:利用沟槽光刻版进行光刻工艺,对沟槽位置曝光,再通过干法刻蚀,将曝光位置刻蚀出深沟槽;

17.步骤三:在沟槽内及硅片表面生长氧化硅;

18.步骤四:沟槽内填充源极多晶硅并进行回刻;

19.步骤五:利用湿法腐蚀对表面及侧壁氧化硅回刻;

20.步骤六:源极多晶硅上淀积bpsg氧化膜;

21.步骤七:bpsg高温回流;

22.步骤八:利用湿法腐蚀对硅片表面及沟槽侧壁多余bpsg氧化膜进行移除,形成栅极沟槽;

23.步骤九:利用干法热氧化工艺生长栅氧化硅;

24.步骤十:淀积栅极多晶硅并进行回刻;

25.步骤十一:进行体区、源区注入并退火;

26.步骤十二:淀积介质氧化硅,进行孔光刻及刻蚀;

27.步骤十三:进行表面金属工艺,制作器件电极,完成最终器件结构。

28.作为实用新型的一种改进,根据器件耐压不同,所述步骤二中干法刻蚀形成的深沟槽其深度在2微米至20微米之间,宽度在0.2微米至3微米之间。

29.作为实用新型的一种改进,所述步骤三中沟槽内及硅片表面生长氧化硅可以通过直接热氧化或者淀积工艺实现。

30.作为实用新型的一种改进,所述步骤五中湿法回刻时侧壁保留300埃至1000埃,防止后续bpsg材料中杂质与si之间接触而发生严重扩散。

31.作为实用新型的一种改进,所述步骤七中硼磷硅玻璃bpsg高温退火回流的温度在800℃至1000℃之间,退火过程中按比例通入氮气与氧气的混合气体。

32.作为实用新型的一种改进,退火回流时通入氮气与氧气的比例在10:1至20:1之间。

33.作为实用新型的一种改进,退火回流时通入纯氮气.

34.相对于现有技术,实用新型具体以下优点:该技术方案采用该mosfet结构及工艺制造方法,利用了bpsg良好的高温回流特性,采用bpsg填充沟槽不易出现空洞,而且bpsg的设备与现有制程完全兼容,不需要增加额外设备投入。该方案在有效改善栅源漏电的同时,降低了工艺实现的难度,利于更小元胞尺寸器件的加工生产,同时可以节省一道cmp研磨工艺,极大的降低了器件生产成本,增强市场竞争力。

附图说明

35.图1为hdp cvd填充空洞的示意图;

36.图2为实用新型步骤一的示意图;

37.图3为实用新型步骤二的示意图;

38.图4为实用新型步骤三的示意图;

39.图5为实用新型步骤四的示意图;

40.图6为实用新型步骤五的示意图;

41.图7为实用新型步骤六的示意图;

42.图8为实用新型步骤七的示意图;

43.图9为实用新型步骤八的示意图;

44.图10为实用新型步骤九的示意图;

45.图11为实用新型步骤十的示意图;

46.图12为实用新型步骤十一的示意图;

47.图13为实用新型步骤十二的示意图;

48.图14为实用新型步骤十三的示意图;

具体实施方式

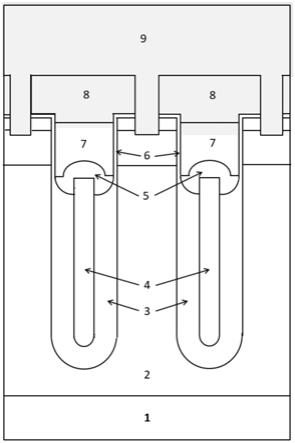

49.为了使实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释实用新型,并不用于限定实用新型。

50.实施例1:该实施例所述的分栅沟槽mosfet栅极漏电改善的工艺方法通过以下步骤实现:

51.步骤一:在si衬底片1表面生长n型外延层2,外延层厚度根据器件所需源漏耐压制定,范围从2微米至20微米,如图2所示。

52.步骤二:外延层表面淀积一层氧化硅,通过光刻工艺在氧化硅表面定义出沟槽区,然后以氧化硅为硬掩模,对硅衬底进行刻蚀,形成深沟槽并移除表面氧化硅,所述步骤二中干法刻蚀形成的深沟槽其深度在2微米至20微米之间,宽度在0.2微米至3微米之间,如图3示;

53.步骤三:在沟槽内及硅片表面生长氧化硅3,厚度根据器件源漏耐压制定,范围从1000埃至10000埃,可以使用淀积或者热氧化工艺,如图4示;

54.步骤四:沟槽内填充源极多晶硅4并进行回刻,如图5示;

55.步骤五:利用湿法腐蚀对表面及侧壁氧化硅回刻,侧壁剩余300埃至1000埃,防止后续bpsg材料中杂质与si之间接触而发生严重扩散,如图6示;

56.步骤六:源极多晶硅上淀积bpsg材料5,具体淀积厚度根据沟槽宽度确定,如图7示;

57.步骤七:bpsg高温回流,退火温度范围800℃至1000℃之间。退火回流的气体可以是纯氮气,也可以是氮气与氧气的混合气体,其气流比例在10:1至20:1之间,如图8所示。

58.步骤八:利用湿法腐蚀对硅片表面及沟槽侧壁多余bpsg进行移除,形成栅极沟槽,如图9示;

59.步骤九:利用干法热氧化工艺生长栅氧化硅6,如图10示;

60.步骤十:淀积栅极多晶硅7并进行回刻,如图11示;

61.步骤十一:进行体区、源区注入并退火,如图12示;

62.步骤十二:淀积介质氧化硅8,进行孔光刻及刻蚀,如图13示;

63.步骤十三:进行表面金属9工艺,制作器件电极,完成后最终器件结构如图14示;

64.以上所述,仅为实用新型的较佳实施例而已,并非用于限定实用新型的保护范围。

65.实用新型所述的分栅沟槽mosfet栅源多晶硅间的隔离氧化层通过在栅极沟槽内填充bpsg材料,再由炉管高温退火,利用bpsg良好的回流特性来增加栅极沟槽底部的氧化层厚度形成,而非通过hdp淀积及cmp技术形成。采用实用新型所述的工艺制造方法制作的分栅沟槽mosfet在有效改善栅源漏电的同时,降低了工艺实现的难度,利于更小元胞尺寸器件的加工生产,并能够显著降低芯片加工成本。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1