半导体封装结构的制作方法

1.本技术实施例涉及半导体领域,特别是涉及半导体封装结构。

背景技术:

2.随着半导体封装技术的发展,半导体封装的应用场景变得原来越多样化和复杂化,仍然期望可以更好地提高半导体封装的性能和小型化以适应这些多样化的应用场景。

3.例如,在一个场景中,当半导体封装被制造为具有高的裸片栈(例如,mnand,pop(package on package,封装上封装),lpdram(low power dynamic random access memory,低功耗动态随机存储器))或小的技术节点(例如,3d nand)时,具有有效散热的封装结构是至关重要的。在另一个场景中,当移动应用设备需要半导体封装结构更薄时,具有足够封装强度(package strength)、断裂韧性(fracture toughness)和抗冲击性(shock resistance)的封装结构是至关重要的。上述的封装结构的特点也可能具有简易的制造工艺,成熟的材料,且适用于多种封装结构(例如,线接合封装(wire bond package)或芯片直接贴装封装(direct chip attach package,dca package))。

技术实现要素:

4.本技术实施例的目的之一在于提供一种半导体封装结构,其可以提高半导体封装结构的热耗散、封装强度、断裂韧性以及抗冲击性。

5.本技术的实施例提供了一种半导体封装结构,其包括:基板;一个或多个裸片,其安置于所述基板上;在所述基板上的密封体,且所述密封体密封所述一个或多个裸片;以及散热

‑

强度加强结构,其与所述密封体接触。

6.在本技术的一些实施例中,所述散热

‑

强度加强结构包括一个或多个碳化硅层。

7.在本技术的一些实施例中,一个或多个碳化硅层包括在所述一个或多个裸片的顶部表面上的第一碳化硅层。所述一个或多个碳化硅层包括并排布置的两个裸片,且所述第一碳化硅层是在所述两个裸片的顶部表面上。

8.在本技术的一些实施例中,所述一个或多个裸片包括裸片栈,且所述第一碳化硅层是在所述裸片栈的顶部裸片的顶部表面上。

9.在本技术的一些实施例中,所述一个或多个裸片包括并排布置的多个裸片栈,且其中所述第一碳化硅层是在所述多个裸片栈的顶部裸片的顶部表面上。

10.在本技术的一些实施例中,所述第一碳化硅层是在所述顶部裸片下方的裸片的顶部表面的部分上。

11.在本技术的一些实施例中,半导体封装结构进一步包括接合线,所述接合线连接所述一个或多个裸片的顶部表面和所述基板。

12.在本技术的一些实施例中,半导体封装结构进一步包括接合结构,所述接合结构位于所述一个或多个裸片的底部表面和所述基板之间

13.在本技术的一些实施例中,所述一个或多个碳化硅层是在所述密封体的顶部表面

上。

14.在本技术的一些实施例中,所述碳化硅层包括第二碳化硅层,所述第二碳化硅层在所述密封体的顶部表面上。

15.在本技术的一些实施例中,所述一个或多个碳化硅层包括碳化硅簇。

16.在本技术的一些实施例中,所述一个或多个碳化硅层的厚度的范围是从约70μm到约90μm。

17.本技术的实施例提供了一种半导体封装结构,其包括:基板;一个或多个裸片,其安置于所述基板上;散热体,其在所述基板上且与所述一个或多个裸片耦合;以及散热

‑

强度加强结构,其与所述散热体接触。

18.在本技术的一些实施例中,所述散热

‑

强度加强结构包括一个或多个碳化硅层,所述一个或多个碳化硅层位于所述一个或多个裸片的顶部表面和所述散热体之间。

19.在本技术的一些实施例中,所述散热

‑

强度加强结构包括一个或多个碳化硅层,所述一个或多个碳化硅层是在所述散热体的顶部表面上。

附图说明

20.在下文中将简要地说明为了描述本技术实施例或现有技术所必要的附图以便于描述本技术实施例。显而易见地,下文描述中的附图仅只是本技术中的部分实施例。对本领域技术人员而言,在不需要创造性劳动的前提下,依然可根据这些附图中所例示的结构来获得其他实施例的附图。

21.图1a

‑

1d为本技术的一些实施例的半导体封装结构的截面结构示意图。

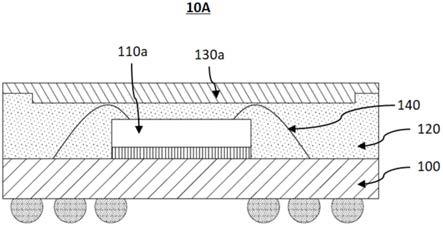

22.图2a

‑

2e为本技术的一些实施例的半导体封装结构的截面结构示意图。

23.图3a

‑

3e为本技术的一些实施例的半导体封装结构的截面结构示意图。

24.图4a

‑

4d为本技术的一些实施例的半导体封装结构的截面结构示意图。

25.图5a

‑

5c为本技术的一些实施例的半导体封装结构的截面结构示意图。

26.图6a

‑

6f为本技术的一些实施例中的制造半导体封装结构的流程示意图。

27.图7a

‑

7e为本技术的一些实施例中的制造半导体封装结构的流程示意图。

28.图8a

‑

8f为本技术的一些实施例中的制造半导体封装结构的流程示意图。

具体实施方式

29.本技术的实施例将会被详细的描示在下文中。在本技术说明书全文中,将相同或相似的组件以及具有相同或相似的功能的组件通过类似附图标记来表示。在此所描述的有关附图的实施例为说明性质的、图解性质的且用于提供对本技术的基本理解。本技术的实施例不应被解释为对本技术的限制。

30.整个说明书中对“一些实施例”、“部分实施例”、“一个实施例”、“另一举例”、“举例”、“具体举例”或“部分举例”的引用,其所代表的意思是在本技术中的至少一个实施例或举例包含了该实施例或举例中所描述的特定特征、结构或特性。因此,在整个说明书中的各处所出现的描述,例如:“在一些实施例中”、“在实施例中”、“在一个实施例中”、“在另一个举例中”,“在一个举例中”、“在特定举例中”或“举例“,其不必然是引用本技术中的相同的实施例或示例。

31.如本文中所使用,空间相对术语,例如,“之下”、“下方”、“下部”、“上方”、“上部”、“下部”、“左侧”、“右侧”及类似者可在本文中用于描述的简易以描述如图中所说明的一个元件或特征与另一元件或特征的关系。应理解,当一元件被称为“连接到”或“耦合到”另一元件时,其可直接连接或耦合到另一元件,或可存在中间元件。

32.除非另外规定,否则例如“上方”、“下方”、“上”、“左”、“右”、“下”、“顶部”、“底部”、“垂直”、“水平”、“侧面”、“高于”、“低于”、“上部”、“在

……

上”、“在

……

下”、“向下”等等的空间描述是相对于图中所示的定向来指示的。应理解,本文中所使用的空间描述仅出于说明的目的,且本文中所描述的结构的实际实施方案可以任何定向或方式在空间上布置,其前提是本技术的实施例的优点是不会因此类布置而有偏差。

33.如本文中所使用,术语“约”、“大体上”、“实质上”用以描述及说明小的变化。当与事件或情形结合使用时,术语可指代其中事件或情形精确发生的例子以及其中事件或情形极近似地发生的例子。举例来说,当结合数值使用时,术语可指代小于或等于数值的

±

10%的变化范围,例如小于或等于

±

5%、小于或等于

±

0.5%、或小于或等于

±

0.05%。举例来说,如果两个数值之间的差值小于或等于值的平均值的

±

10%,那么可认为两个数值“大体上”相同。

34.再者,为便于描述,“第一”、“第二”、“第三”等等可在本文中用于区分一个图或一系列图的不同组件。“第一”、“第二”、“第三”等等不意欲描述对应组件。

35.在本技术中,除非经特别指定或限定之外,“设置”、“连接”、“耦合”、“固定”以及与其类似的用词在使用上是广泛地,而且本领域技术人员可根据具体的情况以理解上述的用词可是,比如,固定连接、可拆式连接或集成连接;其也可是机械式连接或电连接;其也可是直接连接或通过中介结构的间接连接;也可是两个组件的内部通讯。

36.本技术的一些实施例提供了一种半导体封装结构,该半导体封装结构包括基板(substrate)、一个或多个裸片(dies)、密封体(encapsulant)以及散热

‑

强度增强结构(thermal

‑

and strength

‑

enhancing structure)。其中,一个或多个裸片安置于基板上,密封体安置于基板上且密封一个或多个裸片,散热

‑

强度加强结构(thermal

‑

and strength

‑

enhancing structure)与密封体接触。该散热

‑

强度加强结构可以有效提高半导体封装结构的热耗散、封装强度、断裂韧性以及抗冲击性。

37.在本技术的一些实施例中,散热

‑

强度加强结构包括一个或多个碳化硅(sic)层。当散热

‑

强度结构包括一个或多个碳化硅层时,对应的半导体封装结构将在下述实施例中被进一步描述。

38.图1a为本技术的一些实施例的半导体封装结构10a的截面结构示意图。半导体封装结构10a包括基板100、裸片110a、密封体120和碳化硅层130a。其中裸片110a安置于基板100上,密封体120安置于所述基板100上且用于密封裸片110a,且碳化硅层130a安置于密封体120的顶部表面上且与密封体120接触。基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130a可以有效提高半导体封装结构10a的热耗散、封装强度、断裂韧性以及抗冲击性。

39.需要说明的是,在一些实施例中,碳化硅层130a的侧边与密封体120的侧边对齐且碳化硅层130a不覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a延伸覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a仅覆盖密封体120的顶部表面的部分区域,其

中所述部分区域与裸片110a的顶部表面对应。另外,碳化硅层130a的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130a的厚度可以为约80μm。碳化硅层130a中可观察到碳化硅簇(sic clusters)。

40.在图1a中,半导体封装结构10a还包括接合线(bonding wire)140。其中,接合线140连接裸片110a的顶部表面和基板100。需要说明是,在线接合封装中,裸片110的顶部表面相对于底部表面(无源(passive)表面)是有源(active)表面。另外,密封体120为环氧树脂塑封组合物(epoxy molding compound)。

41.图1b为本技术的一些实施例的半导体封装结构10b的截面结构示意图。半导体封装结构10b与图1a中的半导体封装结构10a的区别在于:半导体封装结构10b包括两个裸片110a和110b,且裸片110a和110b并排(side by side)布置于基板100上。其中,裸片110a和110b的顶部表面均通过接合线140与基板100电连接。在图1b中,由于有两个用于工作的裸片110a和110b,半导体封装结构10b产生的热量和尺寸相较于半导体封装10a均变大,通过半导体封装结构10b中的碳化硅层130a可以明显的提高半导体封装结构10b的热耗散、封装强度、断裂韧性以及抗冲击性。

42.图1c为本技术的一些实施例的半导体封装结构10c的截面结构示意图。半导体封装结构10c与图1b中的半导体封装结构10b均具有两个裸片110a和110b,不同之处在于:半导体封装结构10c中的两个裸片110a和110b堆叠布置形成裸片栈1101。

43.具体地,在图1c中,裸片110a安置于基板100上,裸片110b安置于所述裸片110a上,密封体120密封裸片110a和110b。在一些实施例中,裸片110b覆盖裸片110a的部分区域以使裸片110a的顶部表面的部分区域暴露并与密封体120接触,裸片110a、裸片110b和基板100通过接合线140电连接,裸片110a与接合线140连接的接合点位于暴露区域。

44.由于采用堆叠的方式,相对于裸片110a产生的热量可以通过基板110中导电迹线释放而言,裸片110b离基板100较远,因此,裸片110b产生的热量可以通过密封体120上的碳化硅层130a进行释放,有效提高半导体封装结构10c的热耗散。另外,由于两个裸片堆叠导致的半导体封装结构的尺寸变大,通过碳化硅层130a可以有效提高半导体封装结构10c的封装强度、断裂韧性以及抗冲击性。

45.图1d为本技术的一些实施例的半导体封装结构10d的截面结构示意图。相对于图1a

‑

1c中的半导体封装结构10a、10b和10c而言,区别之处在于:半导体封装结构10d具有两个并排布置的裸片栈1101和1102。其中,裸片栈1101由两个裸片110a和110b堆叠形成,裸片栈1102由裸片110c和110d堆叠形成。密封体120密封裸片栈1101和1102。在一些实施例中,裸片110b覆盖裸片110a的部分区域以使裸片110a的顶部表面的部分区域暴露并与密封体120接触,裸片110d覆盖裸片110c的部分区域以使裸片110c的顶部表面的部分区域暴露并与密封体120接触。裸片110a、裸片110b和基板100通过接合线140电连接,裸片110c、裸片110d和基板100通过接合线140电连接。裸片110a与接合线140连接的接合点位于暴露区域,裸片110c与接合线140连接的接合点位于暴露区域。

46.由于半导体封装结构10d产生的热量和/或尺寸相较于半导体封装10a、10b和10c均变大,通过半导体封装结构10d中的碳化硅层130a可以有效的改善和提高半导体封装结构10d的热耗散、封装强度、断裂韧性以及抗冲击性。

47.图2a为本技术的一些实施例的半导体封装结构20a的截面结构示意图。

48.半导体封装结构20a包括基板100、裸片110a、密封体120和碳化硅层130b1。其中裸片110a安置于基板100上,密封体120安置于基板100上且用于密封裸片110a,且碳化硅层130b1安置于裸片110a的顶部表面上且与密封体120接触。密封体120与基板100结合以密封裸片110a和碳化硅层130b1。

49.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130b1可以有效提高半导体封装结构20a的热耗散、封装强度、断裂韧性以及抗冲击性。

50.此外,半导体封装结构20a还包括接合线140。其中,接合线140连接裸片110a的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a的顶部表面相对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

51.需要说明的是,由于接合线140的形成早于形成碳化硅层130b1的步骤,在一些实施例中,碳化硅层130b1不覆盖裸片110a的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。例如,在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的部分区域。在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的除了用于接合线140的连接点外的部分区域,并与裸片110a的侧边对齐。在一些实施例中,碳化硅层130b1覆盖在裸片110a的侧边上。在一些实施例中,碳化硅层130b1与裸片110a的侧边对齐且碳化硅层130b1不覆盖到裸片110a的侧边。另外,碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。

52.值得注意的是,裸片110a上的碳化硅层130b1可延伸裸片110a附近基板100的上表面(未绘示出)。

53.图2b为本技术的一些实施例的半导体封装结构20b的截面结构示意图。

54.半导体封装结构20b包括基板100、裸片110a和110b、密封体120以及碳化硅层130b1和130b2。其中裸片110a和裸片110b并排布置于基板100上,密封体120安置于基板100上且用于密封裸片110a和裸片110b,碳化硅层130b1安置于裸片110a的顶部表面上且与密封体120接触,碳化硅层130b2安置于裸片110b的顶部表面上且与密封体120接触。密封体120与基板100结合以密封裸片110a、110b和碳化硅层130b1、130b2。

55.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130b1和碳化硅层130b2可以有效提高半导体封装结构20b的热耗散、封装强度、断裂韧性以及抗冲击性。

56.此外,半导体封装结构20b还包括接合线140。其中,接合线140连接裸片110a和110b的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a和110b的顶部表面相对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

57.需要说明的是,在一些实施例中,由于接合线140的形成早于形成碳化硅层130b1的步骤,碳化硅层130b1不覆盖裸片110a的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。例如,在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的部分区域。在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的除了用于接合线140的连接点外的部分区域,并与裸片110a的侧边对齐。在一些实施例中,碳化硅层130b1覆盖在裸片110a的侧边上。在一些实施例中,碳化硅层130b1与裸片

110a的侧边对齐且碳化硅层130b1不覆盖到裸片110a的侧边。

58.在一些实施例中,由于接合线140的形成早于形成碳化硅层130b2的步骤,碳化硅层130b2不覆盖裸片110b的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。在一些实施例中,碳化硅层130b2覆盖裸片110b的顶部表面的部分区域。在一些实施例中,碳化硅层130b2覆盖裸片110b的顶部表面的除了用于接合线140的连接点外的部分区域。在一些实施例中,碳化硅层130b2覆盖在裸片110b的侧边上。在一些实施例中,碳化硅层130b2与裸片110b的侧边对齐且碳化硅层130b2不覆盖到裸片110b的侧边。

59.另外,碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。在一些实施例中,碳化硅层130b2的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b2的厚度可以为约80μm。碳化硅层130b2中可观察到碳化硅簇。

60.在图2b中,由于有两个用于工作的裸片110a和110b,半导体封装结构20b产生的热量和尺寸相较于半导体封装20a均变大,通过半导体封装结构20b中的碳化硅层130b1和130b2可以有效提高半导体封装结构20b的热耗散、封装强度、断裂韧性以及抗冲击性。

61.值得注意的是,裸片110a和110b上的碳化硅层130b1和130b2可延伸裸片110a和110b附近基板100的上表面(未绘示出)。

62.图2c为本技术的一些实施例的半导体封装结构20c的截面结构示意图。

63.半导体封装结构20c包括基板100、裸片110a和110b、密封体120以及碳化硅层130b1。其中,裸片110a和裸片110b堆叠形成为裸片栈1101,裸片110a安置于基板100上,裸片110b安置于裸片110a上。密封体120安置于基板100上且用于密封裸片110a和裸片110b,碳化硅层130b1安置于裸片110b的顶部表面上且与密封体120接触。密封体120与基板100结合以密封裸片栈1101和碳化硅层130b1。

64.此外,半导体封装结构20c还包括接合线140。其中,接合线140连接裸片110a和110b的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a和110b的顶部表面相对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

65.在一些实施例中,碳化硅层130b1覆盖裸片栈1101的顶部裸片(即裸片110b)的顶部表面的除了用于接合线140的连接点外的部分区域。在一些实施例中,碳化硅层130b1覆盖在部分接合线140区段上以及连接点周围。在一些实施例中,碳化硅层130b1覆盖在裸片110b的侧边上。在一些实施例中,碳化硅层130b1与裸片110b的侧边对齐且碳化硅层130b1不覆盖到裸片110b的侧边。

66.另外,碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。

67.由于采用叠瓦(shingle)方式堆叠,相对于裸片110a产生的热量可以通过基板110中导电迹线释放而言,裸片110b离基板100较远,因此,裸片110b产生的热量可以通过裸片110b上的碳化硅层130b1进行释放,有效提高半导体封装结构20c的热耗散。另外,由于两个裸片堆叠导致的半导体封装结构的尺寸变大,通过碳化硅层130b1可以有效提高半导体封装结构20c的封装强度、断裂韧性以及抗冲击性。

68.值得注意的是,以叠瓦方式堆叠的裸片栈1101,裸片110b上的碳化硅层130b1可延

伸至裸片110a的上表面(未绘示出),甚至是裸片栈1101附近基板100的上表面(未绘示出)。

69.图2d为本技术的一些实施例的半导体封装结构20d的截面结构示意图。

70.半导体封装结构20d包括基板100、裸片栈1101和1102、密封体120以及碳化硅层130b1和130b2。其中,裸片栈1101和1102并排布置在基板100上,裸片栈1101由两个裸片110a和110b堆叠形成,裸片110a安置于基板100上,裸片110b安置于裸片110a上。裸片栈1102由两个裸片110c和110d堆叠形成,裸片110c安置于裸片110d上。碳化硅层130b1安置于裸片栈1101的顶部裸片(即,裸片110b)的顶部表面上且与密封体120接触。碳化硅层130b2安置于裸片栈1102的顶部裸片(即,裸片110b)的顶部表面上且与密封体120接触。密封体120与基板100结合以密封裸片栈1101和1102以及碳化硅层130b1和130b2。

71.此外,半导体封装结构20b还包括接合线140。其中,接合线140连接裸片110a和110b的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a和110b的顶部表面相对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

72.需要说明的是,由于接合线140的形成早于形成碳化硅层130b1的步骤,在一些实施例中,碳化硅层130b1不覆盖裸片110b的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。例如,在一些实施例中,碳化硅层130b1覆盖裸片110b的顶部表面的部分区域。在一些实施例中,碳化硅层130b1覆盖裸片110b的顶部表面的除了用于接合线140的连接点外的部分区域。在一些实施例中,碳化硅层130b1覆盖在裸片110b的侧边上。在一些实施例中,碳化硅层130b1与裸片110b的侧边对齐且碳化硅层130b1不覆盖到裸片110b的侧边。

73.在一些实施例中,由于接合线140的形成早于形成碳化硅层130b2的步骤,碳化硅层130b2不覆盖裸片110d的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。在一些实施例中,碳化硅层130b2覆盖裸片110d的顶部表面的部分区域。在一些实施例中,碳化硅层130b2覆盖裸片110d的顶部表面的除了用于接合线140的连接点外的部分区域,并与裸片110d的侧边对齐。在一些实施例中,碳化硅层130b2覆盖在裸片110d的侧边上。在一些实施例中,碳化硅层130b2与裸片110d的侧边对齐且碳化硅层130b2不覆盖到裸片110d的侧边。

74.另外,碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。在一些实施例中,碳化硅层130b2的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b2的厚度可以为约80μm。碳化硅层130b2中可观察到碳化硅簇。

75.在图2d中,由于有两个用于工作的裸片栈1101和1102,半导体封装结构20d产生的热量和尺寸相较于半导体封装20a、20b和20c均变大,通过半导体封装结构20d中的碳化硅层130b1和130b2可以有效提高半导体封装结构20d的热耗散、封装强度、断裂韧性以及抗冲击性。

76.值得注意的是,以叠瓦方式堆叠的裸片栈1101、裸片栈1102,裸片110b上的碳化硅层130b1可延伸至裸片110a的上表面(未绘示出),裸片110d上的碳化硅层130b2可延伸至裸片110c的上表面(未绘示出),甚至是裸片栈1101、裸片栈1102附近基板100的上表面(未绘示出)。

77.图2e为本技术的一些实施例的半导体封装结构20e的截面结构示意图。

78.在图2e中,半导体封装结构20e包括基板100、裸片栈1103、密封体120、碳化硅层130b1和碳化硅层130b2。其中裸片栈1103包括裸片110a、110b、110c和110d,裸片110a、110b、110c和110d依次由下到上堆叠形成裸片栈1103并安置于基板100上。裸片110a、110b、110c和110d与基板100通过接合线140相互电连接。密封体120安置于基板100上且用于密封裸片栈1103。碳化硅层130b1安置于裸片110b的顶部表面的部分区域,该部分区域并没有被裸片110c覆盖。碳化硅层130b2安置于裸片栈1103的顶部裸片(即,裸片110d)的顶部表面上,且与密封体120接触。

79.半导体封装结构20e还包括接合线140。其中,接合线140连接裸片110a、110b、110c、110d的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a、110b、110c、110d的顶部表面相对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

80.在一些实施例中,碳化硅层130b2覆盖裸片栈1103的顶部裸片(即,裸片110d)的顶部表面的除了用于接合线140的连接点外的部分区域。在一些实施例中,碳化硅层130b2覆盖在裸片110d用于接合线140的连接点的区域周围和部分接合线140区段上。在一些实施例中,碳化硅层130b2覆盖在裸片110d的侧边上。在一些实施例中,碳化硅层130b2与裸片110d的侧边对齐且碳化硅层130b1不覆盖到裸片110b的侧边。

81.在一些实施例中,碳化硅层130b1安置于所述裸片栈1103的顶部裸片(即,裸片110d)之下的裸片(即,裸片110b)的顶部表面的部分区域上。其中,该部分区域为裸片110b上的裸片(即,裸片110c、110d)没有遮挡的区域,且该部分区域的用于提供接合线的连接点。在一些实施例中,由于接合线140的形成早于形成碳化硅层130b1的步骤,碳化硅层130b1不覆盖该部分区域的连接点和接合线,但仍有可能沉积于部分接合线140区段以及连接点周围。

82.另外,碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。在一些实施例中,碳化硅层130b2的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b2的厚度可以为约80μm。碳化硅层130b2中可观察到碳化硅簇。

83.相对于图2a

‑

2d中的半导体封装结构20a、20b、20c和20d而言,区别之处在于:半导体封装结构20e中的裸片栈1103采用四个裸片110a、110b、110c和110d以反向叠瓦(reversed shingle)方式堆叠形成,从而,半导体封装结构20e相较于上述实施例中的半导体封装结构20a、20b、20c和20d而言具有更高的高度。

84.由于高度的增加,远离基板110的裸片110b、110c和110d,其中尤其是顶部裸片110d,通过基板110的散热会变差,而通过碳化硅层130b1和130b2的良好的导热性能,可以有效提高裸片110b、110c和110d,尤其是顶部裸片110d,的热耗散,从而提高半导体封装20e整体的热耗散。

85.此外,裸片堆叠高度的增加会导致半导体封装结构20e的性能,比如封装强度、断裂韧性以及抗冲击性,变差。但通过碳化硅层130b1和130b2的设置,基于碳化硅的材料属性,可以有效提高半导体封装结构20e的封装强度、断裂韧性以及抗冲击性等性能。

86.值得注意的是,以反向叠瓦方式堆叠的裸片栈1103,裸片110d上的碳化硅层130b1亦可延伸至裸片110c、裸片110a的上表面(未绘示出),甚至是裸片栈1103附近基板100的上

表面(未绘示出)。

87.图3a为本技术的一些实施例的半导体封装结构30a的截面结构示意图。

88.半导体封装结构30a包括基板100、裸片110a、密封体120和碳化硅层130a和130b1。其中裸片110a安置于基板100上,密封体120安置于基板100上且用于密封裸片110a,且碳化硅层130b1安置于裸片110a的顶部表面上且与密封体120接触,碳化硅层130a安置于密封体120上且与密封体120接触。密封体120与基板100结合以密封裸片110a和碳化硅层130b1。

89.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130a和130b1可以有效提高半导体封装结构30a的热耗散、封装强度、断裂韧性以及抗冲击性。

90.此外,半导体封装结构30a还包括接合线140。其中,接合线140连接裸片110a的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a的顶部表面相对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

91.需要说明的是,由于接合线140的形成早于形成碳化硅层130b1的步骤,在一些实施例中,碳化硅层130b1不覆盖裸片110a的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。例如,在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的部分区域。在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的除了用于接合线140的连接点外的部分区域,并与裸片110a的侧边对齐。在一些实施例中,碳化硅层130b1覆盖在裸片110a的侧边上。在一些实施例中,碳化硅层130b1与裸片110a的侧边对齐且碳化硅层130b1不覆盖到裸片110a的侧边。

92.在一些实施例中,碳化硅层130a的侧边与密封体120的侧边对齐且碳化硅层130a不覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a延伸覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a仅覆盖密封体120的顶部表面的部分区域,其中该部分区域与裸片110a的顶部表面对应。

93.在一些实施例中,碳化硅层130a的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130a的厚度可以为约80μm。碳化硅层130a中可观察到碳化硅簇。在一些实施例中,碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。

94.图3b为本技术的一些实施例的半导体封装结构30b的截面结构示意图。

95.半导体封装结构30b包括基板100、裸片110a和110b、密封体120以及碳化硅层130a、130b1和130b2。其中裸片110a和裸片110b并排布置于基板100上,密封体120安置于基板100上且用于密封裸片110a和裸片110b。碳化硅层130a安置于密封体120的顶部表面上且与密封体120接触,碳化硅层130b1安置于裸片110a的顶部表面上且与密封体120接触,碳化硅层130b2安置于裸片110b的顶部表面上且与密封体120接触。密封体120与基板100结合以密封裸片110a、110b和碳化硅层130b1、130b2。

96.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130a、130b1和130b2可以有效提高半导体封装结构30b的热耗散、封装强度、断裂韧性以及抗冲击性。

97.此外,半导体封装结构30b还包括接合线140。其中,接合线140连接裸片110a和110b的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a和110b的顶部表面相

对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

98.需要说明的是,碳化硅层130a的侧边与密封体120的侧边对齐且碳化硅层130a不覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a延伸覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a仅覆盖密封体120的顶部表面的部分区域,其中所述部分区域与裸片110a的顶部表面对应。

99.在一些实施例中,由于接合线140的形成早于形成碳化硅层130b1的步骤,碳化硅层130b1不覆盖裸片110a的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的部分区域。在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的除用于接合线140的连接点外的部分区域,并与裸片110a的侧边对齐。在一些实施例中,碳化硅层130b1覆盖在裸片110a的侧边上。在一些实施例中,碳化硅层130b1与裸片110a的侧边对齐且碳化硅层130b1不覆盖到裸片110a的侧边。

100.在一些实施例中,由于接合线140的形成早于形成碳化硅层130b2的步骤,碳化硅层130b2不覆盖裸片110b的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。在一些实施例中,碳化硅层130b2覆盖裸片110b的顶部表面的部分区域。在一些实施例中,碳化硅层130b2覆盖在裸片110b的顶部表面的包括用于接合线140的连接点的区域和接合线140上。在一些实施例中,碳化硅层130b2覆盖在裸片110b的侧边上。在一些实施例中,碳化硅层130b2与裸片110b的侧边对齐且碳化硅层130b2不覆盖到裸片110b的侧边。

101.另外,碳化硅层130a的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130a的厚度可以为约80μm。碳化硅层130a中可观察到碳化硅簇。碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。在一些实施例中,碳化硅层130b2的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b2的厚度可以为约80μm。碳化硅层130b2中可观察到碳化硅簇。

102.在图3b中,由于有两个用于工作的裸片110a和110b,半导体封装结构30b产生的热量和尺寸相较于半导体封装30a均变大,通过半导体封装结构30b中的碳化硅层130a、130b1和130b2可以有效提高半导体封装结构30b的热耗散、封装强度、断裂韧性以及抗冲击性。

103.图3c为本技术的一些实施例的半导体封装结构30c的截面结构示意图。

104.半导体封装结构30c包括基板100、裸片110a和110b、密封体120以及碳化硅层130a和130b1。其中,裸片110a和裸片110b堆叠形成为裸片栈1101,裸片110a安置于基板100上,裸片110b安置于裸片110a上。密封体120安置于基板100上且用于密封裸片110a和裸片110b。碳化硅层130a安置于密封体120上且与密封体接触,碳化硅层130b1安置于裸片110b的顶部表面上且与密封体120接触。密封体120与基板100结合以密封裸片栈1101和碳化硅层130b1。

105.此外,半导体封装结构20c还包括接合线140。其中,接合线140连接裸片110a和110b的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a和110b的顶部表面相对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

106.在一些实施例中,碳化硅层130a的侧边与密封体120的侧边对齐且碳化硅层130a

不覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a延伸覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a仅覆盖密封体120的顶部表面的部分区域,其中所述部分区域与裸片110a的顶部表面对应。

107.在一些实施例中,碳化硅层130b1覆盖裸片栈1101的顶部裸片(即裸片110b)的顶部表面的除用于接合线140的连接点外的部分区域。在一些实施例中,碳化硅层130b1覆盖在裸片110b的部分接合线140区段上。在一些实施例中,碳化硅层130b1覆盖在裸片110b的侧边上。在一些实施例中,碳化硅层130b1与裸片110b的侧边对齐且碳化硅层130b1不覆盖到裸片110b的侧边。

108.另外,碳化硅层130a的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130a的厚度可以为约80μm。碳化硅层130a中可观察到碳化硅簇。碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。

109.由于采用叠瓦方式堆叠,相对于裸片110a产生的热量可以通过基板110中导电迹线释放而言,裸片110b离基板100较远,因此,裸片110b产生的热量可以通过裸片110b上的碳化硅层130b1以及密封体120上的碳化硅层130a进行释放,有效提高半导体封装结构30c的热耗散。另外,由于两个裸片堆叠导致的半导体封装结构的尺寸变大,通过碳化硅层130a和130b1可以有效提高半导体封装结构30c的封装强度、断裂韧性以及抗冲击性。

110.值得注意的是,以叠瓦方式堆叠的裸片栈1101,裸片110b上的碳化硅层130b1可延伸至裸片110a的上表面(未绘示出),甚至是裸片栈1101附近基板100的上表面(未绘示出)。

111.图3d为本技术的一些实施例的半导体封装结构30d的截面结构示意图。

112.半导体封装结构30d包括基板100、裸片栈1101和1102、密封体120以及碳化硅层130a、130b1和130b2。其中,裸片栈1101和1102并排布置在基板100上,裸片栈1101由两个裸片110a和110b堆叠形成,裸片110a安置于基板100上,裸片110b安置于裸片110a上。裸片栈1102由两个裸片110c和110d堆叠形成,裸片110c安置于裸片110d上。碳化硅层130a安置于封装体120上且与密封体120接触,碳化硅层130b1安置于裸片栈1101的顶部裸片(即,裸片110b)的顶部表面上且与密封体120接触。碳化硅层130b2安置于裸片栈1102的顶部裸片(即,裸片110b)的顶部表面上且与密封体120接触。密封体120与基板100结合以密封裸片栈1101和1102以及碳化硅层130b1和130b2。

113.此外,半导体封装结构20b还包括接合线140。其中,接合线140连接裸片110a和110b的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a和110b的顶部表面相对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

114.需要说明的是,在一些实施例中,碳化硅层130a的侧边与密封体120的侧边对齐且碳化硅层130a不覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a延伸覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a仅覆盖密封体120的顶部表面的部分区域,其中所述部分区域与裸片110a的顶部表面对应。

115.在一些实施例中,由于接合线140的形成早于形成碳化硅层130b1的步骤,碳化硅层130b1不覆盖裸片110b的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。例如,在一些实施例中,碳化硅层130b1覆盖裸片110b的顶部表面的部分区域。在一些实施例中,碳化硅层130b1覆盖裸片110b的顶部表面的除用于

接合线140的连接点外的部分区域。在一些实施例中,碳化硅层130b1覆盖在裸片110b的侧边上。在一些实施例中,碳化硅层130b1与裸片110b的侧边对齐且碳化硅层130b1不覆盖到裸片110b的侧边。

116.在一些实施例中,由于接合线140的形成早于形成碳化硅层130b2的步骤,碳化硅层130b2不覆盖裸片110d的顶部表面的用于连接接合线140的连接点,但仍有可能沉积于部分接合线140区段以及连接点周围。在一些实施例中,碳化硅层130b2覆盖裸片110d的顶部表面的部分区域。在一些实施例中,碳化硅层130b2覆盖裸片110d的顶部表面的除用于接合线140的连接点外的部分区域,并与裸片110d的侧边对齐。在一些实施例中,碳化硅层130b2覆盖在裸片110d的侧边上。在一些实施例中,碳化硅层130b2与裸片110d的侧边对齐且碳化硅层130b2不覆盖到裸片110d的侧边。

117.另外,碳化硅层130a的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130a的厚度可以为约80μm。碳化硅层130a中可观察到碳化硅簇。碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。在一些实施例中,碳化硅层130b2的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b2的厚度可以为约80μm。碳化硅层130b2中可观察到碳化硅簇。

118.在图3d中,由于有两个用于工作的裸片栈1101和1102,半导体封装结构30d产生的热量和尺寸相较于半导体封装30a、30b和30c均变大,通过半导体封装结构30d中的碳化硅层130a、130b1和130b2可以有效提高半导体封装结构30d的热耗散、封装强度、断裂韧性以及抗冲击性。

119.值得注意的是,以叠瓦方式堆叠的裸片栈1101、裸片栈1102,裸片110b上的碳化硅层130b1可延伸至裸片110a的上表面(未绘示出),裸片110d上的碳化硅层130b2可延伸至裸片110c的上表面(未绘示出),甚至是裸片栈1101、裸片栈1102附近基板100的上表面(未绘示出)。

120.图3e为本技术的一些实施例的半导体封装结构30e的截面结构示意图。

121.在图3e中,半导体封装结构30e包括基板100、裸片栈1103、密封体120、碳化硅层130a、碳化硅层130b1、和碳化硅层130b2。其中裸片栈1103包括裸片110a、110b、110c和110d,裸片110a、110b、110c和110d依次由下到上以反向叠瓦方式堆叠形成裸片栈1103并安置于基板100上。裸片110a、110b、110c和110d与基板100通过接合线140相互电连接。密封体120安置于基板100上且用于密封裸片栈1103。碳化硅层130a安置于密封体120上且与密封体120接触。碳化硅层130b1安置于裸片110b的顶部表面的部分区域,该部分区域并没有被裸片110c覆盖。碳化硅层130b2安置于裸片栈1103的顶部裸片(即,裸片110d)的顶部表面上,且与密封体120接触。

122.半导体封装结构30e还包括接合线140。其中,接合线140连接裸片110a、110b、110c、110d的顶部表面和基板100。需要说明是,在线接合封装中,裸片110a、110b、110c、110d的顶部表面相对于底部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

123.在一些实施例中,碳化硅层130a的侧边与密封体120的侧边对齐且碳化硅层130a不覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a延伸覆盖到密封体120的侧边。

在一些实施例中,碳化硅层130a仅覆盖密封体120的顶部表面的部分区域,其中该部分区域与裸片110a的顶部表面对应。

124.在一些实施例中,碳化硅层130b2覆盖裸片栈1103的顶部裸片(即,裸片110d)的顶部表面的除用于接合线140的连接点外的部分区域。在一些实施例中,碳化硅层130b2覆盖在裸片110d的部分接合线140区段上。在一些实施例中,碳化硅层130b2覆盖在裸片110d的侧边上。在一些实施例中,碳化硅层130b2与裸片110d的侧边对齐且碳化硅层130b1不覆盖到裸片110b的侧边。

125.在一些实施例中,碳化硅层130b1安置于所述裸片栈1103的顶部裸片(即,裸片110d)之下的裸片(即,裸片110b)的顶部表面的部分区域上。其中,该部分区域为裸片110b上的裸片(即,裸片110c、110d)没有遮挡的区域,且该部分区域的用于提供接合线的连接点。在一些实施例中,碳化硅层130b1不覆盖该部分区域的连接点和接合线。在一些实施例中,碳化硅层130b1覆盖该部分区域的连接点和接合线。

126.在一些实施例中,碳化硅层130a的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130a的厚度可以为约80μm。碳化硅层130a中可观察到碳化硅簇。碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。在一些实施例中,碳化硅层130b2的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b2的厚度可以为约80μm。碳化硅层130b2中可观察到碳化硅簇。

127.相对于图3a

‑

3d中的半导体封装结构30a、30b、30c和30d而言,区别之处在于:半导体封装结构30e中的裸片栈1103采用四个裸片110a、110b、110c和110d依反向叠瓦方式形成,从而,半导体封装结构30e相较于上述实施例中的半导体封装结构30a、30b、30c和30d而言具有更高的高度。

128.由于高度的增加,远离基板110的裸片110b、110c和110d,其中尤其是顶部裸片110d,通过基板110的散热会变差,而通过碳化硅层130a、130b1和130b2的良好的导热性能,可以有效提高裸片110b、110c和110d,尤其是顶部裸片110d,的热耗散,从而提高半导体封装30e整体的热耗散。

129.此外,裸片堆叠高度的增加会导致半导体封装结构30e的性能,比如封装强度、断裂韧性以及抗冲击性,变差。但通过碳化硅层130a、130b1和130b2的设置,基于碳化硅的材料属性,可以有效提高半导体封装结构30e的封装强度、断裂韧性以及抗冲击性等性能。

130.值得注意的是,以反向叠瓦方式堆叠的裸片栈1103,裸片110d上的碳化硅层130b1亦可延伸至裸片110c、裸片110a的上表面(未绘示出),甚至是裸片栈1103附近基板100的上表面(未绘示出)。

131.图4a为本技术的一些实施例的半导体封装结构40a的截面结构示意图。

132.半导体封装结构40a包括基板100、裸片110a、密封体120和碳化硅层130a。其中裸片110a安置于基板100上,密封体120安置于基板100上且用于密封裸片110a,碳化硅层130a安置于密封体120上且与密封体120接触。密封体120与基板100结合以密封裸片110a。

133.需要说明的是,在一些实施例中,碳化硅层130a的侧边与密封体120的侧边对齐且碳化硅层130a不覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a延伸覆盖到密封体120的侧边。在一些实施例中,碳化硅层130a仅覆盖密封体120的顶部表面的部分区域,其

中所述部分区域与裸片110a的顶部表面对应。另外,碳化硅层130a的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130a的厚度可以为约80μm。碳化硅层130a中可观察到碳化硅簇。

134.在图4a中,半导体封装结构40a还包括接合结构150。其中,接合结构150电连接裸片110a的底部表面和基板100。需要说明是,在芯片直接贴合(dca)封装或倒装芯片(flip

‑

chip)封装中,裸片110的底部表面相对于顶部表面(无源(passive)表面)是有源(active)表面。另外,密封体120为环氧树脂塑封组合物。

135.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130a可以有效提高半导体封装结构40a的热耗散、封装强度、断裂韧性以及抗冲击性。

136.图4b为本技术的一些实施例的半导体封装结构40b的截面结构示意图。

137.半导体封装结构40b包括基板100、裸片110a、密封体120和碳化硅层130b1。其中裸片110a安置于基板100上,密封体120安置于基板100上且用于密封裸片110a,碳化硅层130b1安置于裸片110a的顶部表面(无源表面)上且与密封体120接触。密封体120与基板100结合以密封裸片110a和碳化硅层130b1。

138.在图4b中,半导体封装结构40b还包括接合结构150。其中,接合结构150电连接裸片110a的底部表面和基板100。需要说明是,在芯片直接贴合封装或倒装芯片封装中,裸片110的底部表面相对于顶部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

139.在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的部分区域。在一些实施例中,碳化硅层130b1与裸片110a的侧边对齐且碳化硅层130b1不延伸到裸片110a的侧边。在一些实施例中,碳化硅层130b1安置于裸片110a的顶部表面上且延伸到裸片110a的侧边上。在一些实施例中,碳化硅层130b1可覆盖于裸片110a附近的被动组件180上方。另外,碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。

140.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130b1可以有效提高半导体封装结构40b的热耗散、封装强度、断裂韧性以及抗冲击性。

141.图4c为本技术的一些实施例的半导体封装结构40c的截面结构示意图。

142.半导体封装结构40c包括基板100、裸片110a和110b、密封体120以及碳化硅层130b1和130b2。其中裸片110a和裸片110b并排布置于基板100上,密封体120安置于基板100上且用于密封裸片110a和裸片110b,碳化硅层130b1安置于裸片110a的顶部表面(无源表面)上且与密封体120接触,碳化硅层130b2安置于裸片110b的顶部表面(无源表面)上且与密封体120接触。密封体120与基板100结合以密封裸片110a、110b和碳化硅层130b1、130b2。

143.在图4c中,半导体封装结构40c还包括接合结构150。其中,接合结构150电连接裸片110a和110b的底部表面和基板100。需要说明是,在芯片直接贴合封装或倒装芯片封装中,裸片110a和110b的底部表面相对于顶部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

144.在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的部分区域。在一些实

施例中,碳化硅层130b1与裸片110a的侧边对齐且碳化硅层130b1不延伸到裸片110a的侧边。在一些实施例中,碳化硅层130b2安置于裸片110b的顶部表面上且延伸到裸片110b的侧边上。在一些实施例中,碳化硅层130b2覆盖裸片110b的顶部表面的部分区域。在一些实施例中,碳化硅层130b2与裸片110b的侧边对齐且碳化硅层130b2不延伸到裸片110b的侧边。在一些实施例中,碳化硅层130b2安置于裸片110b的顶部表面上且延伸到裸片110a的侧边上。在一些实施例中,碳化硅层130b1可覆盖于裸片110a和裸片110b附近的被动组件180上方。

145.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130b1和130b2可以有效提高半导体封装结构40c的热耗散、封装强度、断裂韧性以及抗冲击性。

146.图4d为本技术的一些实施例的半导体封装结构40d的截面结构示意图。

147.半导体封装结构40d包括基板100、裸片110a、密封体120以及碳化硅层130a和130b1。其中裸片110a安置于基板100上,密封体120安置于基板100上且用于密封裸片110a,且碳化硅层130b1安置于裸片110a的顶部表面(无源表面)上且与密封体120接触,碳化硅层130a安置于密封体120上且与密封体120接触。密封体120与基板100结合以密封裸片110a和碳化硅层130b1。

148.在图4d中,半导体封装结构40d还包括接合结构150。其中,接合结构150电连接裸片110a的底部表面和基板100。需要说明是,在芯片直接贴合封装或倒装芯片封装中,裸片110a的底部表面相对于顶部表面(无源表面)是有源表面。另外,密封体120为环氧树脂塑封组合物。

149.在一些实施例中,碳化硅层130a覆盖密封体120的顶部表面的部分区域。在一些实施例中,碳化硅层130a与密封体120的侧边对齐且碳化硅层130a不延伸到密封体120的侧边。在一些实施例中,碳化硅层130a安置于密封体120的顶部表面上且延伸到密封体120的侧边上。

150.在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的部分区域。在一些实施例中,碳化硅层130b1与裸片110a的侧边对齐且碳化硅层130b1不延伸到裸片110a的侧边。在一些实施例中,碳化硅层130b1安置于裸片110a的顶部表面上且延伸到裸片110a的侧边上。

151.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130a和130b1可以有效提高半导体封装结构40d的热耗散、封装强度、断裂韧性以及抗冲击性。

152.图5a为本技术的一些实施例的半导体封装结构50a的截面结构示意图。

153.半导体封装结构50a包括基板100、裸片110a、散热体(heat sink)160和碳化硅层130b1。其中裸片110a安置于基板100上,散热体160安置于基板100上且与裸片110a耦合,碳化硅层130b1安置于裸片110a的顶部表面(无源表面)上且与散热体160接触。

154.需要说明的是,在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的部分区域。在一些实施例中,碳化硅层130b1与裸片110a的侧边对齐且碳化硅层130b1不延伸到裸片110a的侧边。在一些实施例中,碳化硅层130b1安置于裸片110a的顶部表面上且延伸到裸片110a的侧边上。另外,碳化硅层130b1的厚度范围是从约70μm到约90μm。在一些实施例

中,碳化硅层130b1的厚度可以为约80μm。碳化硅层130b1中可观察到碳化硅簇。

155.在图5a中,半导体封装结构50a还包括接合结构150。其中,接合结构150电连接裸片110a的底部表面和基板100。需要说明是,在芯片直接贴合(direct chip attachment)封装或倒装芯片(flip

‑

chip)封装中,裸片110的底部表面相对于顶部表面(无源(passive)表面)是有源(active)表面。

156.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130b1可以有效提高半导体封装结构50a的热耗散、封装强度、断裂韧性以及抗冲击性。

157.图5b为本技术的一些实施例的半导体封装结构50b的截面结构示意图。

158.半导体封装结构50b包括基板100、裸片110a、散热体160和碳化硅层130a。其中裸片110a安置于基板100上,散热体160安置于基板100上且与裸片110a耦合,碳化硅层130a安置于散热体160上。

159.需要说明的是,在一些实施例中,碳化硅层130a的侧边与散热体160的侧边对齐且碳化硅层130a不覆盖到散热体160的侧边。在一些实施例中,碳化硅层130a延伸覆盖到散热体160的侧边。在一些实施例中,碳化硅层130a仅覆盖散热体160的顶部表面的部分区域,其中所述部分区域与裸片110a的顶部表面对应。另外,碳化硅层130a的厚度范围是从约70μm到约90μm。在一些实施例中,碳化硅层130a的厚度可以为约80μm。碳化硅层130a中可观察到碳化硅簇。

160.在图5b中,半导体封装结构50b还包括接合结构150。其中,接合结构150电连接裸片110a的底部表面和基板100。需要说明是,在芯片直接贴合(direct chip attachment)封装或倒装芯片(flip chip)封装中,裸片110a的底部表面相对于顶部表面(无源(passive)表面)是有源(active)表面。

161.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130a可以有效提高半导体封装结构50b的热耗散、封装强度、断裂韧性以及抗冲击性。

162.图5c为本技术的一些实施例的半导体封装结构50c的截面结构示意图。

163.半导体封装结构50c包括基板100、裸片110a、散热体160以及碳化硅层130a和130b1。其中裸片110a安置于基板100上,散热体160安置于基板100上且与裸片110a耦合,且碳化硅层130b1安置于裸片110a的顶部表面(无源表面)上且与散热体160接触,碳化硅层130a安置于散热体160上且与散热体160接触。

164.在图5c中,半导体封装结构50c还包括接合结构150。其中,接合结构150电连接裸片110a的底部表面和基板100。需要说明是,在芯片直接贴合封装或倒装芯片封装中,裸片110a的底部表面相对于顶部表面(无源表面)是有源表面。

165.在一些实施例中,碳化硅层130a覆盖散热体160的顶部表面的部分区域。在一些实施例中,碳化硅层130a与散热体160的侧边对齐且碳化硅层130a不延伸到散热体160的侧边。在一些实施例中,碳化硅层130a安置于散热体160的顶部表面上且延伸到散热体160的侧边上。

166.在一些实施例中,碳化硅层130b1覆盖裸片110a的顶部表面的部分区域。在一些实施例中,碳化硅层130b1与裸片110a的侧边对齐且碳化硅层130b1不延伸到裸片110a的侧

边。在一些实施例中,碳化硅层130b1安置于裸片110a的顶部表面上且延伸到裸片110a的侧边上。

167.基于碳化硅的材料属性,比如,高强度、低热扩散系数、高热导率、高弹性模量、优秀的抗冲击性以及断裂韧性,碳化硅层130a和130b1可以有效提高半导体封装结构50c的热耗散、封装强度、断裂韧性以及抗冲击性。

168.需要说明的是,针对上述图1a

‑

图5c中的半导体封装结构的实施例,碳化硅层130a、130b1或130b2分别可以为单层结构或多层结构,此外,碳化硅层130a、130b1或130b2的表面是平坦的。但碳化硅层的形状和结构可以根据具体封装工艺中的磨具的结构和要求确定,并不限定于此。

169.针对图1b、2b、3b和4c中的半导体封装结构,在其他实施例中,除了裸片110a和110b外,可以有更多个裸片并排布置在基板上,例如,三个裸片、四个裸片等等。

170.针对图1c、1d、2c、2d、2e、3c、3d、3e中具有裸片栈的半导体封装结构,裸片栈中的裸片除了包括2个裸片、4个裸片之外,还可以包括其他数量的裸片。并且,裸片栈的数量除了两个并排布置的裸片栈之外,还可以包括多个并排布置的裸片栈。

171.对于,上述实施例中的接合线140为常用的导电线材料,例如,但不限于,铜、铅锡合金、或其组合。上述实施例中的接合结构150为半导体封装中常用的导电结构材料,例如,但不限于,铜、铅锡合金、或其组合。上述实施例中的基板可包括多个层,层可包括介电层、金属层、及连接单层或多层的电性连通(via)等本领域常见的基板组成。在某些实施例中,基板可由任意合适类型的基板材料构成。

172.图6a、图6b、图6c、图6d、图6e和图6f是本技术的一些实施例的制造半导体封装结构的流程图,可制造图1a

‑

1d所示的半导体封装结构。

173.如图6a所示,对半导体封装结构60a在进行预塑封前的等离子清洗(plasma clean)。

174.半导体封装结构60a为部分结构,包括基板100、位于基板100上的裸片栈1103、以及将裸片栈1103上的裸片110a、110b、110c、110d与基板110电连接的接合线。在一些实施中,裸片栈1103中的裸片可以为一个,也可以为多个,这样可以形成本文上述实施例中的半导体封装结构。

175.如图6b所示,对半导体封装结构60a进行塑封(molding)已形成封装体120。其中,封装体120形成于基板100上且密封裸片栈1103。

176.如图6c所示,对半导体封装结构60a进行塑封后固化(post mold cure)工艺。

177.如图6d所示,采用常温真空喷涂工艺(room temperature vacuum spray coating)在封装体120上表面形成碳化硅层130a。由于接合线140的形成早于碳化硅层130a的形成,利用常温真空喷涂工艺相较于现有技术用的高温介质沉积方式(例如化学气相沉积),能够免除高温活化前驱物的过程,而在较低的温度下形成碳化硅层130a,从而不会对接合线140等先形成的金属结构产生不良影响。

178.具体地,常温真空喷涂工艺为在常温为25度至35度的真空环境中将碳化硅粉末喷涂到封装体120的表面上形成为碳化硅层130a。其中,碳化硅粉末的尺寸为0.1μm~1.0μm。因此在成品中碳化硅层130a可观察到由碳化硅粉末聚集而成的碳化硅簇(sic clusters)。

179.如图6e所示,对半导体封装结构60a进行激光打标(laser marking)工艺。

180.如图6f所示,对激光打标后的半导体封装结构60a进行焊球安装(solder ball mount)工艺以形成焊球。

181.图7a、图7b、图7c、图7d和图7e是本技术的一些实施例的制造半导体封装结构的流程图,可制造图2a

‑

2e所示的半导体封装结构。

182.如图7a所示,采用常温真空喷涂工艺(room temperature vacuum spray coating)在裸片栈1103上表面形成碳化硅层130b1。由于接合线140的形成早于碳化硅层130b1的形成,利用常温真空喷涂工艺相较于现有技术用的高温介质沉积方式(例如化学气相沉积),能够免除高温活化前驱物的过程,而在较低的温度下形成碳化硅层130b1,从而不会对接合线140等先形成的金属结构产生不良影响。

183.具体地,常温真空喷涂工艺为在常温为25度至35度的真空环境中将碳化硅粉末喷涂到封装体120的表面上形成为碳化硅层130b1。其中,碳化硅粉末的尺寸为0.1μm~1.0μm。因此在成品中碳化硅层130b1可观察到由碳化硅粉末聚集而成的碳化硅簇(sic clusters)。

184.半导体封装结构70a为部分结构,包括基板100、位于基板100上的裸片栈1103、以及将裸片栈1103上的裸片110a、110b、110c、110d与基板110电连接的接合线。在一些实施中,裸片栈1103中的裸片可以为一个,也可以为多个,这样可以形成本文上述实施例中的半导体封装结构。

185.如图7b所示,对半导体封装结构70a进行塑封(molding)以形成封装体120。其中,封装体120安置于基板100上且密封裸片栈1103和碳化硅层130b1。

186.如图7c所示,对半导体封装结构70a进行塑封后固化(post mold cure)工艺。

187.如图7d所示,对半导体封装结构70a进行激光打标(laser marking)工艺。

188.如图7e所示,对激光打标后的半导体封装结构70a进行焊球安装(solder ball mount)工艺以形成焊球。

189.图8a、图8b、图8c、图8d、图8e和图8f是本技术的一些实施例的制造半导体封装结构的流程图,可制造图3a

‑

3e所示的半导体封装结构。

190.如图8a所示,采用常温真空喷涂工艺(room temperature vacuum spray coating)在裸片栈1103上表面形成碳化硅层130b1。由于接合线140的形成早于碳化硅层130b1的形成,利用常温真空喷涂工艺相较于现有技术用的高温介质沉积方式(例如化学气相沉积),能够免除高温活化前驱物的过程,而在较低的温度下形成碳化硅层130b1,从而不会对接合线140等先形成的金属结构产生不良影响。

191.具体地,常温真空喷涂工艺为在常温为25度至35度的真空环境中将碳化硅粉末喷涂到封装体120的表面上形成为碳化硅层130b1。其中,碳化硅粉末的尺寸为0.1μm~1.0μm。因此在成品中碳化硅层130b1可观察到由碳化硅粉末聚集而成的碳化硅簇(sic clusters)。

192.半导体封装结构80a为部分结构,包括基板100、位于基板100上的裸片栈1103、以及将裸片栈1103上的裸片110a、110b、110c、110d与基板110电连接的接合线。在一些实施中,裸片栈1103中的裸片可以为一个,也可以为多个,这样可以形成本文上述实施例中的半导体封装结构。

193.如图8b所示,对半导体封装结构80a进行塑封(molding)以形成封装体120。其中,

封装体120安置于基板100上且密封裸片栈1103和碳化硅层130b1。

194.如图8c所示,对半导体封装结构80a进行塑封后固化(post mold cure)工艺。

195.如图8d所示,采用常温真空喷涂工艺在封装体120上形成碳化硅层130a。

196.具体地,常温真空喷涂工艺为在常温为25度至35度的真空环境中将碳化硅粉末喷涂到封装体120的表面上形成为碳化硅层130a。其中,碳化硅粉末的尺寸为0.1μm~1.0μm。因此在成品中碳化硅层130a可观察到由碳化硅粉末聚集而成的碳化硅簇(sic clusters)。

197.如图8e所示,对半导体封装结构80a的碳化硅层130a进行激光打标(laser marking)工艺。

198.如图8f所示,对激光打标后的半导体封装结构80a进行焊球安装(solder ball mount)工艺以形成焊球。

199.在本技术的一些实施例中,可以通过常温真空喷涂工艺形成本文上述实施例中的图4a

‑

5c的具有碳化硅层的半导体封装结构。在本技术的一些实施例中,可以通过常温真空喷涂工艺形成具有碳化硅层的其他半导体封装结构。

200.本技术的技术内容及技术特点已揭示如上,然而熟悉本领域的技术人员仍可能基于本技术的教示及揭示而作种种不背离本技术精神的替换及修饰。因此,本技术的保护范围应不限于实施例所揭示的内容,而应包括各种不背离本技术的替换及修饰,并为本技术的权利要求书所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1