用于复杂逻辑单元的紧凑3D堆叠CFET架构的制作方法

用于复杂逻辑单元的紧凑3d堆叠cfet架构

1.相关申请的交叉引用

2.本技术根据35u.s.c.

§

119(e)要求于2019年5月31日提交的名称为“compact 3d stacked cfet architecture for complex logic cells[用于复杂逻辑单元的紧凑3d堆叠cfet架构]”的美国临时专利申请号62/855,374以及于2020年4月15日提交的名称为“compact 3d stacked cfet architecture for complex logic cells[用于复杂逻辑单元的紧凑3d堆叠cfet架构]”的美国专利申请号16/849,630的优先权,这些美国专利申请的全部披露内容通过援引并入本文。

技术领域

[0003]

本披露内容涉及包括半导体器件、晶体管、和集成电路的微电子器件,包括这种器件的设计和微制造方法。

背景技术:

[0004]

本文提供的背景描述是为了总体上呈现本披露内容的环境。当前发明人的工作在本背景部分中所描述的程度上、以及在提交时间时可能不被认定为现有技术的本说明的方面,既没有明确地也没有隐含地承认是针对本披露内容的现有技术。

[0005]

集成电路广泛用于电子行业,以提供诸如智能电话、计算机等电子设备。集成电路(ic)包括通过半导体衬底上的布线而互连的许多半导体器件,诸如晶体管、电容器等。对于支持电子设备的更多数量的复杂功能的更小更快的ic的需求一直在增加。这个需求使得半导体制作行业缩小了衬底上ic的面积,同时还提高了ic的性能和功耗效率。

[0006]

在制作半导体ic时(尤其是在微观尺度上),执行各种制造工艺,诸如成膜沉积、刻蚀掩模创建、图案化、材料刻蚀和去除以及掺杂处理。重复执行这些工艺以在衬底上形成期望的半导体器件元件。从历史上看,已经利用微制造在一个平面上创建ic的晶体管,并在有源器件平面上方形成ic的布线/金属化,并且因此,这被表征为二维(2d)电路或2d制造。微缩(scaling)工作已经极大地增加了2d电路中每单位面积的晶体管数量,这使得异构功能电路(诸如逻辑电路和存储器电路)集成到同一半导体衬底上。然而,随着微缩进入纳米级半导体器件制造节点,2d微缩工作也将面临更大的挑战。半导体器件制造商已经表达出对晶体管堆叠在彼此顶部之上的三维(3d)半导体电路的期望,这种彼此堆叠作为进一步微缩ic的另一手段。

技术实现要素:

[0007]

本文的技术实现了晶体管上晶体管3d集成,而不会使引脚密度(即,进入逻辑单元的接入点的密度)增加到单元微缩增益被引脚接入拥塞导致的路由能力下降所掩盖的程度。根据本披露内容的一方面(1),提供了一种三维(3d)集成电路(ic)。该3d ic包括具有衬底表面的衬底以及设置在该衬底中的电力轨。半导体器件设置在该衬底中并且沿着该衬底的厚度方向位于该电力轨上方,该厚度方向基本上垂直于该衬底表面,该第一半导体器件

具有第一栅极以及设置在该第一栅极的相反两侧的第一对源极

‑

漏极区。第二半导体器件设置在该衬底中并且沿着该厚度方向堆叠在该第一半导体器件上方,该第二半导体器件具有第二栅极以及设置在该第二栅极的相反两侧的第二对源极

‑

漏极区,该第一栅极在物理上与该第二栅极分离。导电栅极到栅极带连接件从该第一栅极延伸到该第二栅极,使得该第一栅极电连接到该第二栅极。

[0008]

方面(2)包括方面(1)的3d ic,其中,该栅极到栅极带包括从该第一栅极延伸到该第二栅极的至少一个竖直接触件。

[0009]

方面(3)包括方面(2)的3d ic,其中,该第一栅极和该第二栅极共线地堆叠。

[0010]

方面(4)包括方面(3)的3d ic,其中,该栅极到栅极带包括在物理上彼此分离的多个竖直接触件。

[0011]

方面(5)包括方面(1)的3d ic,其中,该第一栅极和该第二栅极以交错布置来堆叠。

[0012]

方面(6)包括方面(5)的3d ic,其进一步包括连接到该第一栅极的第一栅极接触件、以及连接到该第二栅极的第二栅极接触件,与该第二栅极接触件相比,该第一栅极接触件具有更大的竖直高度。

[0013]

方面(7)包括方面(6)的3d ic,其进一步包括布线层,该布线层设置在该衬底中并且沿着该厚度方向位于该第二半导体器件上方,其中,该第一栅极接触件和该第二栅极接触件均竖直地延伸以与该布线层连接。

[0014]

方面(8)包括方面(1)的3d ic,其进一步包括合并外延结构,该合并外延结构将该第一半导体器件的源极

‑

漏极区与该第二半导体器件的源极

‑

漏极区相连接。

[0015]

方面(9)包括方面(8)的3d ic,其中,该合并外延结构被配置为从该3d ic提供共用输出引脚。

[0016]

方面(10)包括方面(1)的3d ic,其进一步包括从该电力轨竖直地延伸的电力壁。

[0017]

方面(11)包括一种3d ic,其包括具有衬底表面的衬底;第一半导体器件堆叠体,该第一半导体器件堆叠体沿着该衬底的厚度方向堆叠;以及第二半导体器件堆叠体,该第二半导体器件堆叠体沿着该衬底的厚度方向堆叠并且在沿着该衬底表面的方向上邻近该第一堆叠体设置。该第一堆叠体和该第二堆叠体的每个半导体器件包括栅极以及设置在各自的栅极的相反两侧的一对源极

‑

漏极区,并且该第一堆叠体和该第二堆叠体的每个栅极是分裂栅极。栅极接触件在物理上连接到这些半导体器件中的第一半导体器件的第一分裂栅极,其中,该栅极接触件形成局部互连结构的至少一部分,该局部互连结构在该3d ic中将该第一半导体器件电连接到第二半导体器件。

[0018]

方面(12)包括方面(11)的3d ic,其中,该第一半导体器件和该第二半导体器件依次堆叠在该第一半导体器件堆叠体中。

[0019]

方面(13)包括方面(12)的3d ic,其中,该栅极接触件是栅极到栅极带,该栅极到栅极带从该第一分裂栅极竖直地延伸到该第二半导体器件的第二分裂栅极,使得该第一半导体器件和该第二半导体器件电连接。

[0020]

方面(14)包括方面(13)的3d ic,其进一步包括:布线层,该布线层在该厚度方向上设置在该第一半导体器件堆叠体和该第二半导体器件堆叠体上方;以及竖直接触件,该竖直接触件从该第二分裂栅极竖直地延伸,以向该第一半导体器件和该第二半导体器件提

供共用输入。

[0021]

方面(15)包括方面(12)的3d ic,其中,该第一分裂栅极相对于该第二半导体器件的第二分裂栅极是交错的。

[0022]

方面(16)包括方面(15)的3d ic,其进一步包括:布线层,该布线层在该厚度方向上设置在该第一半导体器件堆叠体和该第二半导体器件堆叠体上方;第一竖直接触件,该第一竖直接触件从该第一分裂栅极竖直地延伸到该布线层;以及第二竖直接触件,该第二竖直接触件从该第二分裂栅极竖直地延伸到该布线层,其中,该第一竖直接触件的高度大于该第二竖直接触件的高度。

[0023]

方面(17)包括方面(11)的3d ic,其中,该第一半导体器件和该第二半导体器件分别设置在该第一堆叠体和该第二堆叠体中。

[0024]

方面(18)包括方面(17)的3d ic,其中,该局部互连结构将该第一分裂栅极电连接到该第二半导体器件堆叠体中的第二分裂栅极。

[0025]

方面(19)包括方面(18)的3d ic,其中,该栅极接触件包括水平互连结构,该水平互连结构沿着该衬底表面从该第一堆叠体延伸到该第二堆叠体。

[0026]

方面(20)包括方面(18)的3d ic,其中,该局部互连结构将该第一分裂栅极电连接到该第二堆叠体中的半导体器件的源极

‑

漏极区。

[0027]

方面(21)包括方面(20)的3d ic,其中,该栅极接触件包括水平互连结构,该水平互连结构沿着该衬底表面从该第一堆叠体延伸到该第二堆叠体。

[0028]

方面(22)包括方面(21)的3d ic,其进一步包括局部互连接线片,该局部互连接线片在沿着该衬底表面的方向上从该源极

‑

漏极区延伸,其中,该竖直接触件从该第一分裂栅极竖直地延伸到该局部互连接线片。

[0029]

应注意的是,本发明内容部分并未指明本披露内容或要求保护的发明的所有实施例和/或递增的新颖实施方面。相反,本发明内容仅提供了对不同实施例以及与常规技术相比的新颖性对应点的初步讨论。对于本发明和实施例的附加细节和/或可能的观点而言,读者应查阅如以下进一步讨论的本披露内容的具体实施方式部分和相应附图。

附图说明

[0030]

当与附图一起阅读时,从以下详细描述中最好地理解本披露内容的方面。注意,根据行业中的标准实践,各种特征未按比例绘制。事实上,为了讨论的清楚起见,各种特征的尺寸可以被任意增大或减小。

[0031]

图1示出了异构3d集成的示例;

[0032]

图2示出了同构堆叠的示例;

[0033]

图3示出了面积微缩相对较差的3d ic;

[0034]

图4是可以通过本文披露的技术来实施的两输入xor逻辑电路的逻辑图;

[0035]

图5a是栅极上栅极堆叠中使用的xor单元的俯视平面视图;

[0036]

图5b是表示图5中的单元的源极

‑

漏极平面的竖直剖面视图;

[0037]

图5c是表示图5a中的单元的栅极平面的竖直剖面视图;

[0038]

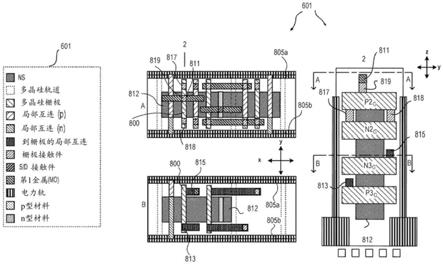

图6a和图6b展示了根据本披露内容的实施例的紧凑地呈现复杂逻辑单元(诸如xor逻辑功能)同时最小化引脚接入拥塞问题的技术架构的概览;

[0039]

图7是可以根据本披露内容的实施例实施的具有5个cfet的xor逻辑电路的详细示意图;

[0040]

图8a是根据本披露内容的实施例的xor单元的竖直剖面1的详细视图;

[0041]

图8b是根据本披露内容的实施例的xor单元的竖直剖面2的详细视图;

[0042]

图8c是根据本披露内容的实施例的xor单元的竖直剖面3的详细视图;

[0043]

图8d是根据本披露内容的实施例的xor单元的竖直剖面4的详细视图;

[0044]

图8e是根据本披露内容的实施例的xor单元的竖直剖面5的详细视图;

[0045]

图8f是根据本披露内容的实施例的xor单元的竖直剖面6的详细视图;以及

[0046]

图8g是根据本披露内容的实施例的xor单元的竖直剖面7的详细视图;

具体实施方式

[0047]

本发明的构思通过其某些实施例得到最佳描述,在本文中参考附图详细描述了这些实施例,在所有附图中,相似的附图标记指代相似的特征。应当理解,当在本文中使用时,术语“发明”旨在表示下文描述的实施例暗含的发明构思,而并非仅仅表示实施例本身。进一步应理解,总体发明构思不限于下文描述的说明性实施例,并且应当依据这样的认识来阅读以下描述。

[0048]

另外,词语“示例性”在本文用来意指“充当示例、实例或例示”。本文指定为示例性的构造、过程、设计、技术等的任何实施例不一定被解释为与其他此类实施例相比更优选或有利。本文指示为示例性的示例的特定质量或适合性既不是有意的,也不应被推断出。

[0049]

进一步地,为了便于描述,在本文中可以使用诸如“之下”、“下方”、“下部”、“上方”、“上部”等空间相关的术语来描述如附图中所展示的一个元素或特征与一个或多个其他元素或特征的关系。除了在附图中所描绘的取向之外,空间相关的术语还旨在涵盖装置在使用或操作中的不同取向。可以以其他方式定向该装置(旋转90度或处于其他取向),并且相应地可以以同样的方式解释本文使用的空间相关的描述符。

[0050]

当然,为了清楚起见,已经提出了本文所述的不同步骤的讨论顺序。通常,这些步骤可以以任何合适的顺序进行。另外,尽管可能在本披露内容的不同地方讨论了本文中的每个不同特征、技术、构型等,但是旨在每个构思可以彼此独立地或彼此组合地进行。因此,可以以许多不同的方式来实施和查看本发明。

[0051]

如背景技术中所指出的,半导体器件制造商已经表达出对晶体管堆叠在彼此顶部之上的三维(3d)半导体电路的期望,这种彼此堆叠作为除了常规的2d微缩以外的微缩ic的另一手段。3d集成(即半导体器件的竖直堆叠)旨在通过在体积而非面积方面增大晶体管密度来克服2d微缩限制。虽然随着3d nand的采用,闪速存储器行业已经成功示范并且实施了器件堆叠,但是器件堆叠应用于随机逻辑设计要困难得多。用于逻辑芯片(诸如cpu(中央处理单元)、gpu(图形处理单元)、fpga(现场可编程门阵列)和soc(片上系统))的3d集成主要通过两种方法来实行:一种方法是异构堆叠,另一种方法更像是同构堆叠。

[0052]

图1示出了使用晶圆/芯片堆叠和硅通孔(tsv)技术的异构3d集成的示例,如在以下文献中披露的:process integration aspects enabling 3d sequential stacked planar and finfet technology[实现3d顺序堆叠平面和finfet技术的工艺集成方面],anne vandooren,imec ptw[微电子研究中心伙伴技术研讨会],2018年春。在这种3d方法

中,每个芯片在设计和制作方面都针对不同的特定任务进行了优化,然后将3d集成用作一种高效的封装技术来构建堆叠soc。例如,如图1中示意性地示出的,ic 100包括可以被优化为包含化学传感器和生物传感器的芯片101,并且芯片103专用于其他传感器和成像器,而芯片105包括纳米器件和mems器件。芯片107可以针对rf、adc和/或dac功能进行优化,而芯片109可以提供存储器堆叠体。芯片111可以是为处理器而设计的,而113专用于为整个ic提供能量/电力。tsv 115被提供用于将各种功能芯片集成到紧凑封装体100中。2019年10月发布的2019年版heterogeneous integration roadmap[异构集成路线图]中提供了异构集成方法的细节,网址为eps.iee.org/hir。

[0053]

图2示出同构堆叠方法的示例,如在以下文献中披露的:monolithic 3d ic:the time is now[单片3d ic:就是现在],brian cronquist和zvi or

‑

bach,monolithic[单片],2014intl.workshop on data

‑

abundant system technology[2014国际数据丰富系统技术研讨会],2014年4月。该方法采用了晶圆键合工艺来克服与芯片堆叠中使用的微米尺寸的tsv相关联的密度损失。通过键合方法,对基础晶圆210进行处理以形成器件(诸如nmos 211和pmos 213)和若干金属化层/布线层215。然后,将减薄的soi(绝缘体上硅)层(通常称为转移施主层)220定位在基础晶圆210的顶部上方并通过氧化物

‑

氧化物键合225与基础晶圆键合以形成完整的结构200。相比于以上指出的芯片堆叠异构方法,由于所需要的通孔的尺寸显著更小(约100nm节距),所以该晶圆键合方法可以实现更好的层级间连接。然而,本发明的发明人认识到,因为独立加工的晶圆或晶圆片段是堆叠在彼此顶部上方的,所以该方法并不是真正的单片集成。因此,该晶圆键合方法并没有为半导体制造提供真正的微缩解决方案。此外,与该晶圆键合工艺相关联的工艺复杂性和成本开销未达到与真正的单片3d集成相关联的微缩目标。

[0054]

真正的单片3d集成涉及在同一硅衬底上制造多个器件级。3d nand是存储器芯片的真正单片集成的示例。3d逻辑的真正单片集成更具挑战性,部分原因是需要种类繁多的布线来连接和功能化每个器件层。

[0055]

本文的技术提供了能够将晶体管高效且紧凑地单片集成到3d逻辑功能中的器件架构和对应的局部互连结构。技术包括一套全面的竖直和侧向局部互连构造,这套构造允许在晶体管上晶体管3d集成工艺中高效且紧凑地设计复杂的逻辑单元。

[0056]

如上所述,3d集成的方法包括使用硅通孔(tsv)的晶圆堆叠、顺序3d键合以及单片(真正的单片)3d集成,在该单片3d集成中,从单个硅衬底构建器件级。3d集成方法可以使用被堆叠单元的粒度进一步分类,即宏上宏(macro

‑

on

‑

macro)3d方法、栅极上栅极3d方法以及晶体管上晶体管3d方法。

[0057]

在宏上宏3d方法中,整个功能块或逻辑宏都被堆叠。在稀疏连接的情况下,可以很好地实施堆叠整个块,因此基于tsv的方法可以很有效。在栅极上栅极3d方法中,通过将标准单元(逻辑设计上的基本构建块)堆叠在彼此顶部上方来将功能块分成两个层级,并且布线级可以放置在器件层级之间的空间中。图5c示出了在器件平面之间具有五个布线级的3d架构,如下文将进一步讨论的。虽然可以使用顺序3d来实施栅极上栅极,但这种方法显示出非常有限的微缩优势。由于需要在两个器件级之间集成大量布线级以成功完成每个单元的单元内布线以及所需的单元

‑

到单元布线,因此在单片集成方法中实施栅极上栅极3d具有挑战性。

[0058]

在晶体管上晶体管3d方法中,各个晶体管竖直地堆叠以形成每体积非常高的器件密度。虽然这种方法很有望实现具有成本效益的微缩,但一个问题是用堆叠的晶体管形成简单的逻辑单元(nand、nor、aoi等)会将单元的占用面积减少到在故障(通常称为引脚接入拥塞)时将给定单元连接到剩余设计变得低效或具有挑战性的程度。即,晶体管上晶体管3d集成的一个挑战是,竖直堆叠的晶体管本质上很难从位于器件平面上方的布线级连接起来。这可能导致单元面积微缩不佳(在交错的晶体管接触件的情况下),或者单元顶部的引脚密度过高,从而导致不可路由的布线拥塞。图3示出了面积微缩相对较差的3d ic。如所见的,ic结构300包括单元和单元边界317,该单元包括堆叠的n型晶体管301至307和堆叠的p型晶体管309至315。引脚319提供从布线级到每个晶体管的栅极的连接。如所见的,从上方的布线级接入堆叠器件可能需要昂贵的金字塔形阶梯式多晶硅栅极。

[0059]

本文的技术实现了晶体管上晶体管3d集成,而不会使引脚密度(即,进入逻辑单元的接入点的密度)增加到单元微缩增益被引脚接入拥塞导致的路由能力下降所掩盖的程度。

[0060]

本文的设计通过预先合成更复杂的逻辑单元(其在内部将多个运算串连在一起)来避免有大量输入(相对于其晶体管数量来说)的逻辑单元(例如在4个晶体管上有4个输入的aoi22)。这包括用大晶体管构建逻辑基元以输入信号计数。这种方法被称为大块合成,并已在业界进行了探索。本文的技术还使用新颖的局部互连构造,这些构造允许在这些高阶逻辑单元中高效地布线三维晶体管布置。xor(异或(exclusive or))逻辑功能是复杂或高阶逻辑单元的示例。图4是可以通过本文披露的技术来实施的两输入xor逻辑电路的逻辑图。如所见的,xor电路400的a1输入被提供给反相器401,而a2输入被提供给与反相器405串联连接的反相器403。反相器401、403和405可以各自实施为互补fet。反相器401、403和405的输出被提供给附加的互补fet电路407和409,这两个电路交叉连接以提供xor单元400的逻辑输出。

[0061]

图5a是xor单元的俯视平面视图,其展示了栅极上栅极堆叠中使用的xor单元的2d呈现。图例501提供了对与布局的不同区相关联的结构和/或材料的指示。如所见的,单元500的布局可以包括沿着衬底的东西方向与多个栅极(g)轨道交替地布置、并且南北延伸以穿过有源区503的多个源极

‑

漏极(sd)轨道。如本领域技术人员所知的,这些交替的sd区和g区在衬底的东西方向上形成一排半导体器件。单元边界由顶部和底部的电力轨505以及附图的最左侧和最右侧的多晶硅栅极轨道g形成。还示出了器件接触件507和509的示例。这种栅极上栅极方法导致相对较大的单元尺寸和布线复杂性。特别地,单元尺寸为7t(轨道)高乘以8个多晶硅轨道宽,如图5a所示。因此,需要三个金属级来完成单元内布线(m0、m1和mx)。在栅极上栅极堆叠实施例中,这三个布线级可以放置在后续器件层级之间的空间中。

[0062]

图5b是表示图5a中的单元的源极

‑

漏极平面的竖直剖面视图,并且图5c是表示图5a中的单元的栅极平面的竖直剖面视图。结构500包括有源区503以及设置在衬底中、位于有源器件平面下方的埋式电力轨505。还设置了中间电力轨506。还如所见的,半导体器件的下部层级511、布线层级513、半导体器件的中间层级515和半导体器件的顶部层级517沿厚度方向堆叠在衬底上。还示出了2x路由轨道的底部层519。如所见的,图5a至图5c的栅极上栅极堆叠架构在器件平面之间的布线层级513中包括五个布线级。该构型在名称为architecture for monolithic 3d integration of semiconductor devices[用于半导

体器件的单片3d集成的架构]的美国申请sn 16/667,442中进行了披露,该美国申请的全部内容通过援引并入本文。如上所述,图5a至图5c示出了,由于需要在两个器件级之间集成大量布线级(在此为5个级)以成功完成每个单元的单元内布线以及所需的单元

‑

到单元布线,因此在单片集成方法中实施栅极上栅极3d具有挑战性。

[0063]

图6a和图6b展示了根据本披露内容的实施例的紧凑地呈现复杂逻辑单元(诸如xor逻辑功能)同时最小化引脚接入拥塞问题的技术架构的概览。图6a示出了穿过单元的z轴截取的两个水平剖面a和b的俯视布局视图,而图6b示出了在图6a中编号的七个平面处沿y轴截取的竖直剖面视图1至7。结构600的平面视图不是沿a和b的真实剖面,而是将结构的一部分示为透明以展示平面a和b下方的结构特征。提供图例601是为了将图6a的结构和/或材料与图6b的相同结构和/或材料相关联。如在图6a的视图中所见的,单元尺寸为5t(轨道)高乘以6个多晶硅轨道宽,从而相对于图5a至图5c的栅极上栅极构型提供了xor单元的显著微缩。在图6b中示出了实现这种微缩优势的各种结构特征的概览。如所见的,这些特征包括埋式电力轨bpr、电力壁pw、局部互连接线片lit、走线(wire run)m0、局部互连li、栅极带gs、竖直接触件vc以及合并外延结构me。

[0064]

如在图6b的剖面1中所见的,结构600包括局部互连接线片lit,这些接线片将器件的sd区连接到从埋式电力轨bpr上升的“电力壁”pw中。在名称为power distribution network for 3d logic and memory[用于3d逻辑和存储器的配电网络]的申请公开号us 2020/0075489中披露了这种电力壁的细节,该申请的全部披露内容通过援引并入本文。该特征通过晶体管上晶体管堆叠实现,该堆叠在器件堆叠体中完成了整个复杂逻辑单元,并将布线(其必须穿过电力壁)留到器件堆叠体上方的空间。

[0065]

现在参考图6b的剖面2,器件被实施为“分裂栅极”,即,可以独立地接触每个晶体管(即使在n/p对中)。为了促进与一对堆叠栅极的共用连接,引入了新的栅极到栅极带gs。为了能够将3d布置中一个晶体管的输出用作另一个晶体管的信号输入,引入了到栅极构造的新“局部互连”li。如在剖面3中所见的,为了将顶部层级中的晶体管的输出布线为底部层级中的晶体管的信号输入,引入了竖直接触件vc以将顶部局部互连接线片lit连到底部栅极局部互连li。

[0066]

如在图6b的剖面4中所见的,提供了分裂栅极构型,其中,每个晶体管能够接收单独的输入信号。为了促进这一点,引入了一对可变高度的栅极接触件vc以及交错的栅极延伸部。在剖面5中,为了高效地收集几个竖直堆叠晶体管的输出并将这些输出路由到共用输出引脚,引入了合并外延me构造。me被示为半透明,以看见me内的堆叠sd区。在剖面6中,示出了竖直连接件vc能够连接到上方的布线平面m0以及晶体管源极或漏极下方的局部互连li平面的灵活性。在图6b的剖面7中,为了将来自顶部层级中的一个晶体管的信号输入连到底部层级中的另一个晶体管,引入了到栅极局部互连li的底侧竖直接触件vc。

[0067]

现在将参考图7和图8a至图8g更详细地描述本文的技术。为了便于解释实施例,描述将集中于xor逻辑功能(异或)。xor逻辑功能是复杂或高阶逻辑单元的示例,但本文也设想使用其他逻辑功能。

[0068]

图7是用编号为cfet1至cfet5的5个互补场效应晶体管(cfet)实施的xor逻辑电路的详细示意图。示出了该电路的所有10个fet。在图7中,标志符px表示编号为x的cfet的p型晶体管,而nx表示编号为x的cfet的n型晶体管。进一步地,sd1表示相关联晶体管的第一源

极/漏极区,sd2表示相关联晶体管的第二源极/漏极区,并且g表示相关联晶体管的栅极。例如,“p1

sd1”是指编号为1的cfet的p型晶体管的第一sd区,而“n1

sd2”是指编号为1的cfet的n型晶体管的第二sd区。类似地,“p1

g”是指编号为1的cfet的p型晶体管的栅极区。这些cfet被实施为堆叠的cfet结构,如下文将进一步讨论的。图7示意性地示出了由局部互连和接触件形成的必要的单元内连接(细线),也如下所讨论的。

[0069]

图8a至图8g分别是根据本披露内容的实施例的图6a的剖面1至7的详细视图。在图8a至图8g中延续了图6a和图6b的标记约定。在图8a至图8g中的每个图中复制图6a的图例601和平面视图以供参考。结构800的这些平面视图不是沿a和b的真实剖面,而是将结构800的一部分示为透明以展示平面a和b下方的结构特征。

[0070]

图8a是根据本披露内容的实施例的xor单元的竖直剖面1的详细视图。结构800表示具有基本上平坦的衬底表面的单片半导体衬底的一部分。如所见的,结构800包括埋式电力轨803a(其充当将电力输送到p型晶体管的vdd)和埋式电力轨803b(充当将电力输送到n型晶体管的vss)。sd区p3

sd1

、n3

sd1

、n2

sd1

、pn2

sd1

沿着衬底801的厚度方向依次堆叠在彼此上方。在图8a的实施例中,晶体管的sd区在结构的有源器件列812内共线地堆叠。进一步地,sd区p3

sd1

和n3

sd1

形成与xor单元的cfet3相关联的一对互补的sd区,而p2

sd1

和n2

sd1

形成与xor单元的cfet2相关联的一对互补的sd区。因此,这些堆叠的晶体管对按晶体管的掺杂类型以交替的堆叠取向来构造。堆叠取向的这种交替(即,n在p之上,然后p在n之上)提高了注入效率和功函数沉积效率。与为堆叠体中的所有器件对保持相同的堆叠顺序(n

‑

p n

‑

p)相比,交替的取向可以提高注入工艺效率和特定于器件类型的选择性沉积的工艺效率。

[0071]

提供了若干局部互连和接触件结构,以根据需要将半导体器件电连接以形成xor电路。具体地,埋式电力轨803a通过电力壁805a以及(分别地)水平互连接线片807和808连接到p3

sd1

和p2

sd1

,而埋入电力轨803b通过电力壁805b以及(分别地)水平互连接线片809和810连接到n3

sd1

和n2

sd1

。还示出了m0层的导线811。在从图6a复制的平面视图中示出了图8a的结构特征,这些结构特征是部分透明的以展示平面a和b下方的结构特征。例如,平面视图a示出了局部互连接线片808、以及在808的平面下方的平面上的局部互连接线片810。类似地,平面视图b示出了局部互连接线片809、以及在809的平面下方的平面上的局部互连接线片807。

[0072]

图8b是根据本披露内容的实施例的xor单元的竖直剖面2的详细视图。如所见的,栅极区p3

g

、n3

g

、n2

g

和p2

g

沿着衬底的厚度方向依次堆叠在彼此上方。如上面的图6中提到的,这些栅极区被实施为分裂栅极,使得可以独立地接触每个栅极区。在图8b的实施例中,晶体管的栅极区共线地堆叠。如以下所讨论的,局部互连813和815在y方向上延伸以与栅极区p5

g

、n5

g

连接。栅极到栅极带817和818提供到一对堆叠栅极p2

g

和n2

g

的共用连接。进一步地,栅极接触件819与导线811连接以向xor单元提供a2输入。因此,平面视图a的透明度示出了导线811、以及该导线下方的栅极接触件819和p2

g

下方的栅极带817。类似地,平面视图b的透明度示出了互连815以及p3

g

下方的互连813。

[0073]

图8c是根据本披露内容的实施例的xor单元的竖直剖面3的详细视图。如所见的,sd区p3

sd2

、n3

sd2

、n2

sd2

、p2

sd2

在结构的有源器件列812内共线地依次堆叠在彼此上方。即,p3

sd2

、n3

sd2

、n2

sd2

、p2

sd2

形成xor单元的cfet3和cfet2的晶体管的第二sd区。进一步地,sd区p3

sd2

、n3

sd2

、n2

sd2

和p2

sd2

分别与p5

sd1

、n5

sd1

、n4

sd1

、p4

sd1

(它们形成xor单元的cfet5和cfet4的

晶体管的第一漏极区)形成为共用源极

‑

漏极。还如所见的,形成p2

sd2

和p4

sd1

的共用sd区通过水平互连接线片821和竖直接触件823连接到cfet的下部层级中的局部互连815。类似地,形成n2

sd2

和n4

sd1

的共用sd区通过水平互连接线片825和竖直接触件827连接到局部互连813。因此,平面视图a的透明度示出了导线811、以及n3

sd2

下方的互连接线片821和sd接触件823。类似地,平面视图b的透明度示出了互连813以及p3

sd2

下方的互连815。

[0074]

图8d是根据本披露内容的实施例的xor单元的竖直剖面4的详细视图。如所见的,分裂栅极区p5

g

、n5

g

、n4

g

和p4

g

沿着衬底的厚度方向依次堆叠在彼此上方。进一步地,栅极区p4

g

和n4

g

彼此交错,使得可变高度栅极接触件839和841可以提供与顶部布线级m0的布线833和837的接触。还示出了导线835。分裂栅极区p5

g

和n5

g

分别连接到栅极接触件829和831。

[0075]

图8e是根据本披露内容的实施例的xor单元的竖直剖面5的详细视图。如所见的,sd区p5

sd2

、n5

sd2

、n4

sd2

和p4

sd2

在结构的有源器件列812内共线地依次堆叠在彼此上方。即,p5

sd2

、n5

sd2

、n4

sd2

和p4

sd2

形成xor单元的cfet5和cfet4的晶体管的第二sd区。进一步地,这些sd区被设置为合并外延生长区839,以高效地收集几个竖直堆叠晶体管的输出并将这些输出路由到xor电路的共用输出引脚。该输出由sd接触件841和m0的导线835提供。

[0076]

图8f是根据本披露内容的实施例的xor单元的竖直剖面6的详细视图。如所见的,sd区n1

sd1

、p1

sd1

在结构的有源器件列812内共线地依次堆叠在彼此上方。即,n1

sd1

、p1

sd1

形成xor单元的cfet1的晶体管的第一sd区。还如所见的,共用sd区p1

sd1

通过水平互连接线片843和竖直接触件845连接到导线833。类似地,形成n1

sd1

的sd区通过水平互连接线片847和竖直sd接触件849连接到局部互连831。还示出了局部互连829。因此,平面视图a的透明度示出了导线833、以及互连接线片843和sd接触件845。类似地,平面视图b的透明度示出了互连接线片847以及接触件849和互连831。

[0077]

图8g是根据本披露内容的实施例的xor单元的竖直剖面7的详细视图。如所见的,栅极区n1

g

和p1

g

沿着衬底的厚度方向依次堆叠在彼此上方。在图8g的实施例中,晶体管的栅极区共线地堆叠。栅极到栅极带851和852提供到一对堆叠栅极p1

g

和n1

g

的共用连接。进一步地,栅极接触件853与导线837连接以向xor单元提供a1输入的一部分。栅极接触件855将共用栅极连接到局部互连829。因此,平面视图a的透明度示出了导线837、以及该导线下方的栅极接触件853和n1

g

下方的栅极带851。类似地,平面视图b的透明度示出了互连829以及n1

g

下方的栅极接触件855。

[0078]

本文所使用的术语仅用于描述特定实施例的目的,并且不旨在对本发明做出限制。如本文所使用的,除非上下文明确指示不包括复数形式,否则单数形式“一个(a)”、“一个(an)”和“所述(the)”意图同样包括复数形式。将进一步理解的是,当在本说明书中使用术语“包括(comprises)”和/或“包括(comprising)”时,其指定陈述的特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或多个特征、整数、步骤、操作、元件、部件和/或它们的组的存在或添加。

[0079]

以下权利要求中的所有装置或步骤加功能元件的对应结构、材料、动作以及等同替换,旨在包括任何用于与具体要求保护的其他要求的保护元件相组合地执行功能的结构、材料或动作。已经出于说明和描述的目的而呈现本发明的描述,但是并不旨在穷举发明或将本发明限于所披露的形式。在不脱离本发明的范围与主旨的情况下,很多修改和变化对本领域普通技术人员都将是明显的。选择和描述了实施例,以便最佳地解释本发明的原

理以及实际应用,并且当适合于所构想的特定用途时,使得本领域的其他普通技术人员能够理解针对具有各种修改的各个实施例的本发明。

[0080]

以上描述旨在展示本发明构思的可能实施方式,而并非限制性的。在本领域的技术人员查阅本披露内容后,许多变化、修改和替代方案将变得显而易见。例如,因此,可以替换等效于所示出和描述的部件的部件,可以组合逐个描述的元件和方法,并且可以在很多部件上分布被描述为分立的元件。因此,本发明的范围不应当参考以上描述来确定,而应当参考所附权利要求以及其等同物的全部范围来确定。

[0081]

在整个本说明书中对“一个实施例”或“实施例”的提及意味着与实施例相结合描述的特定特征、结构、材料、或特性包括在至少一个实施例中,但是不表示它们存在于每个实施例中。因此,在整个本说明书中各处出现的短语“在一个实施例中”不一定指代同一个实施例。此外,在一个或多个实施例中,可以以任何合适的方式来组合特定特征、结构、材料或特性。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1