非易失性半导体存储器件的制作方法

1.本发明涉及侧壁电荷陷阱型的非易失性半导体存储器件。

背景技术:

2.现有技术中,提供一种使用通过cmos的制造工艺所制造的mos晶体管的栅极的侧壁捕获电荷的侧壁电荷陷阱型,能够进行一次写入(otp:one time programmable)或者能够多次写入(mtp:multi time programmable)的非易失性半导体存储器件(例如参照非专利文献1)。

3.图1是表示现有的侧壁电荷陷阱型中otp或者mtp的非易失性半导体存储器件的存储单元110的构造的一例的截面图。存储单元110形成在衬底的p阱111,在覆盖被漏极区域113和源极区域114夹着的沟道区域112的绝缘膜115上形成栅极116,在栅极116的侧面且沟道区域112的正上方,隔着也在栅极116的侧面延伸的绝缘膜115形成由氮化物形成的侧墙117。在栅极116的上表面、漏极区域113和源极区域114的表面分别形成有自对准硅化物(salicide)层120。以覆盖栅极116和侧墙117,且也在漏极区域113和源极区域114延伸的方式形成有氮化膜119。在该存储单元110中,在与源极区域114相对的侧墙117中,从源极区域114被注入电荷而保持该电荷。此外,该例子中关于p沟道进行了表示,但关于n沟道也是同样的。

4.现有技术文献

5.非专利文献

6.非专利文献1:m.fukuda and others,ieee electron device letter,vol.24,2003,“new nonvolatile memory with charge trapping sidewall”

技术实现要素:

7.发明要解决的问题

8.但是,在图1所示的现有的侧壁电荷陷阱型中,在otp或者mtp的非易失性半导体存储器件中,保持在存储单元110的侧墙117中的电荷的量随着时间的经过而逐渐减少,存在所存储的数据消失的情况。例如,在汽车的温度80℃的环境中使用的情况下,在10年中存在数据丢失的情况。

9.本发明是鉴于上述实情而提出的发明,其目的在于提供一种非易失性半导体存储器件,其是侧壁电荷陷阱型的otp或者mtp的非易失性半导体存储器件,其能够提高电荷保持特性,将所存储的数据长期地保存。

10.用于解决问题的技术手段

11.为了解决上述的问题,本技术的非易失性半导体存储器件,其在半导体衬底的表面形成有1个以上的存储单元,该存储单元包括:以夹着沟道区域的方式形成的源极区域和漏极区域;以覆盖沟道区域的方式形成的绝缘膜;形成在绝缘膜上的栅极;侧墙,其以位于沟道区域的正上方的方式形成于栅极的侧面;自对准硅化物阻挡膜,其以覆盖源极区域和

漏极区域的一部分,以及栅极和侧墙的方式形成;自对准硅化物层,其形成于自对准硅化物阻挡膜和从自对准硅化物阻挡膜露出的源极区域和漏极区域;和氮化膜,其以覆盖自对准硅化物阻挡膜和自对准硅化物层的方式形成。

12.自对准硅化物阻挡膜可以是膜厚形成为50nm以上的氧化膜。也可以还包括形成在自对准硅化物阻挡膜的外侧且自对准硅化物层的正上方的触点。侧墙保持从源极区域导入的电荷。

13.在半导体衬底的表面还可以形成有1个以上的mos晶体管,该mos晶体管包括:以夹着沟道区域的方式形成的源极区域和漏极区域;以覆盖沟道区域的方式形成的绝缘膜;形成在绝缘膜上的栅极;侧墙,其以位于沟道区域的正上方的方式形成于栅极的侧面;形成于源极区域、漏极区域和栅极的自对准硅化物层;和以覆盖自对准硅化物层和侧墙的方式形成的氮化膜。

14.mos晶体管所包括的绝缘膜和存储单元所包括的绝缘膜具有相同的厚度。mos晶体管所包括的栅极和存储单元所包括的栅极具有相同的高度和相同的宽度。mos晶体管所包括的侧墙和存储单元所包括的侧墙具有相同的高度和相同的宽度。

15.发明效果

16.依据本发明,被注入侧墙的电荷,通过覆盖侧墙的氧化物的自对准硅化物阻挡膜而被阻止移动。因此,在侧墙中能够稳定地保持电荷,能够提高电荷保持特性,将非易失性半导体存储器件中存储的数据长期地保存。

附图说明

17.图1是表示现有的非易失性半导体存储器件的存储单元的概略结构的截面图。

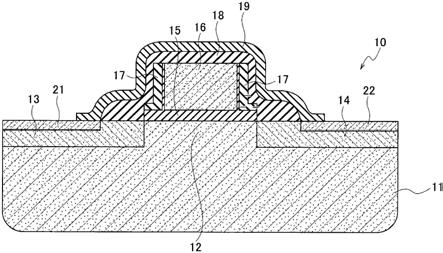

18.图2是表示本实施方式的非易失性半导体存储器件的存储单元的概略的构造的截面图。

19.图3是表示本实施方式的非易失性半导体存储器件的存储单元的构造的一例的截面图。

20.图4是本实施方式的非易失性半导体存储器件的存储单元的工艺流程图。

21.图5是本实施方式的非易失性半导体存储器件的存储单元的工艺流程图。

22.图6是本实施方式的非易失性半导体存储器件的存储单元的工艺流程图。

23.图7是表示本实施方式的非易失性半导体存储器件的变形例的截面图。

24.图8是概略地表示本实施方式的非易失性半导体存储器件的存储单元的电路的电路图。

具体实施方式

25.接着,参照附图关于非易失性半导体存储器件的实施方式进行说明。图2是概略地表示本实施方式的非易失性半导体存储器件的存储单元10的构造的截面图。本实施方式的非易失性半导体存储器件是在通过cmos制造工艺制造的mos晶体管的栅极的侧壁中捕获电荷的侧壁电荷捕获型otp或mtp。此外,在本实施方式中,关于p沟道的构造进行了例示,关于n沟道的构造也同样地能够适用。

26.存储单元10形成于在硅半导体衬底掺杂了p型杂质的掺杂阱即p阱11的表面。在p

阱11的表面,夹着沟道区域12形成有掺杂了n型杂质的漏极区域13和源极区域14。以覆盖沟道区域12的方式形成有由氧化物(sio2)构成的绝缘膜15,在绝缘膜15上形成有具有大致矩形的截面的由多晶硅构成的栅极16。绝缘膜15以也覆盖栅极16的侧面的方式延伸。在栅极16的侧面、且沟道区域12的正上方,隔着绝缘膜15形成有由氮化物(sin)构成的侧墙17。与源极区域14相对的侧墙17发挥保持从源极区域14被注入的电荷的作用。

27.以覆盖栅极16、侧墙17、漏极区域13中的与沟道区域12相邻的部分、以及源极区域14中的与沟道区域12相邻的部分的方式,形成有由氧化物(sio2)构成的自对准硅化物阻挡膜18。在从自对准硅化物阻挡膜18露出的漏极区域13的表面,形成有例如由与钛、钴或镍的自对准硅化物(tisi、cosi或者nisi)构成的漏极自对准硅化物层21,同样地在从自对准硅化物阻挡膜18露出的源极区域14的表面形成有源极自对准硅化物层22。以覆盖自对准硅化物阻挡膜18以及从自对准硅化物阻挡膜18露出的漏极自对准硅化物层21和源极自对准硅化物层22的方式形成有由氮化物(sin)构成的氮化膜19。在漏极自对准硅化物层21和源极自对准硅化物层22中的触点所要连接的部分上,氮化膜19被除去。

28.在本实施方式中,存储单元10的侧墙17由氧化物(sio2)的自对准硅化物阻挡膜18覆盖。自对准硅化物阻挡膜18的膜厚可以为50nm以上。从源极区域14被注入侧墙17中的电荷,由于由氧化物构成的自对准硅化物阻挡膜18阻止移动,被稳定地保持在侧墙17。另外,侧墙17的与沟道区域12和栅极16相对的表面也被由氧化物构成的绝缘膜15覆盖。因此,在本实施方式中,电荷被稳定地保持在侧墙17中,电荷保持特性提高,数据能够长时间地被保持。例如,在汽车中使用的情况下,在温度150

°

的环境中数据至少能够被保持20年。

29.图3是表示本实施方式的非易失性半导体存储器件的存储单元10的构造的一例的截面图。图3中更具体地表示了图2所示的存储单元10的非易失性半导体存储器件中的存储单元10的构造。

30.存储单元10形成在硅半导体衬底的p阱11的表面。p阱11从表面起在深度方向上可以由p基体11a、低电压p阱11b和高电压p阱11c构成。在p阱11的表面形成有由氧化物(sio2)构成的元件分离绝缘层27。

31.在p基体11a的表面夹着沟道区域12形成有掺杂有n型杂质的漏极区域13和源极区域14。以覆盖沟道区域12的方式形成有由氧化物(sio2)构成的绝缘膜15,在绝缘膜15上形成有具有大致矩形的截面的由多晶硅构成的栅极16。绝缘膜15以也覆盖栅极16的侧面的方式延伸。在栅极16的侧面且沟道区域12的正上方,隔着绝缘膜15形成有由氮化物(sin)构成的侧墙17。

32.以覆盖栅极16、侧墙17、漏极区域13中的与沟道区域12相邻的部分、和源极区域14中的与沟道区域12相邻的部分的方式,形成有由氧化物(sio2)构成的自对准硅化物阻挡膜18。在从自对准硅化物阻挡膜18露出的漏极区域13的表面,形成有由例如与钴的自对准硅化物(cosi)构成的漏极自对准硅化物层21,同样地在从自对准硅化物阻挡膜18露出的源极区域14的表面形成有源极自对准硅化物层22。

33.以覆盖自对准硅化物阻挡膜18、从自对准硅化物阻挡膜18露出的漏极自对准硅化物层21和源极自对准硅化物层22、以及元件分离绝缘层27的方式,形成有由氮化物(sin)构成的氮化膜19。覆盖氮化膜19且达到规定高度地形成由氧化物(sio2)构成的层间绝缘膜31,在层间绝缘膜31的上部形成有平坦的表面。在漏极自对准硅化物层21的正上方贯通氮

化膜19和层间绝缘膜31地形成漏极触点32,漏极触点32与形成在层间绝缘膜31的表面的配线35连接。另外,在源极自对准硅化物层22的正上方贯通氮化膜19和层间绝缘膜31地形成源极触点33,漏极触点32与形成在层间绝缘膜31的表面的配线35连接。

34.在本实施方式中,存储单元10的漏极触点32和源极触点33分别形成在漏极区域13的漏极自对准硅化物层21和源极区域14的源极自对准硅化物层22的正上方。漏极自对准硅化物层21和源极自对准硅化物层22,位于从包括被自对准硅化物阻挡膜18包围的栅极16和侧墙17在内的、存储单元10的有源部分向外侧的位置。因此,不会因漏极触点32或者源极触点33而损伤被自对准硅化物阻挡膜18包围的存储单元10的有源部分,能够确保存储单元10的稳定的动作。

35.图4至图6是本实施方式的非易失性半导体存储器件的存储单元10的工艺流程图。在图4的(a)所示的工序中,在硅半导体衬底中,在形成表面由第1氧化膜25覆盖且由元件分离绝缘层27分离的存储单元10的区域中,注入p型杂质而形成p阱11。

36.在图4的(b)所示的工序中,在通过图4的(a)的工序形成的p阱11中堆积多晶硅而形成栅极16。栅极16在p阱11的沟道区域12上隔着第1氧化膜25形成。在图4的(c)所示的工序中,在通过图4的(b)的工序形成的栅极16的侧面形成由氮化物(sin)构成的侧墙17。侧墙17以在栅极16的侧面覆盖预先形成的第2氧化膜28的方式形成。并且,以覆盖侧墙17的方式形成第3氧化膜29。

37.在图5的(a)所示的工序中,接着图4的(b)所示的形成侧墙17的工序,在p阱11的表面的规定范围中注入n型杂质,形成夹着沟道区域12的漏极区域13和源极区域14。在图5的(b)所示的工序中,接着图5的(a)所示的形成漏极区域13和源极区域14的工序,以覆盖栅极16、侧墙17、与侧墙17相邻的漏极区域13的一部分、和与侧墙17相邻的源极区域14的一部分的方式,形成由氧化物(sio2)构成的自对准硅化物阻挡膜18。自对准硅化物阻挡膜18的膜厚可以为50nm以上。自对准硅化物阻挡膜18与覆盖p阱11的表面的第1氧化膜25、覆盖栅极16的侧面的第2氧化膜28、和覆盖侧墙17的第3氧化膜29成为一体。在覆盖p阱11的表面的第1氧化膜25内,处于自对准硅化物阻挡膜18的外侧的部分被除去。在此,在第1氧化膜25内被称为栅极绝缘膜的处于栅极16的下部的部分、和覆盖栅极16的侧面的第2氧化膜28,形成表示本实施方式的非易失性半导体存储器件的存储单元的构造的图2或者图3的截面图中的绝缘膜15。

38.在图5的(c)所示的工序中,接着图5的(b)所示的形成自对准硅化物阻挡膜18的工序,在p阱11的漏极区域13的从自对准硅化物阻挡膜18露出的部分形成钛、钴或者镍的自对准硅化物(tisi、cosi或者nisi)的漏极自对准硅化物层21。同样地,在p阱11的源极区域14的从自对准硅化物阻挡膜18露出的部分形成源极自对准硅化物层22。在此,被自对准硅化物阻挡膜18覆盖的、漏极区域13的一部分且与沟道区域12相邻的部分、以及源极区域14的一部分且与沟道区域12相邻的部分,通过自对准硅化物阻挡膜18阻止了自对准硅化物层的形成。

39.在图6的(a)所示的工序中,接着图5的(c)所示的形成漏极自对准硅化物层21和源极自对准硅化物层22的工序,以覆盖自对准硅化物阻挡膜18、漏极自对准硅化物层21、源极自对准硅化物层22、和元件分离绝缘层27的整体的方式,形成由氮化物(sin)构成的氮化膜19。在图6的(b)所示的工序中,在通过图6所示的工序形成的氮化膜19上形成达到规定高度

的由氧化物(sio2)构成的层间绝缘膜31。并且,在漏极自对准硅化物层21的正上方贯通氮化膜19和层间绝缘膜31地形成漏极触点32,同样地,在源极自对准硅化物层22的正上方贯通氮化膜19和层间绝缘膜地形成源极触点33。在层间绝缘膜31的表面,形成与漏极触点32和源极触点33的上端连接的配线35。

40.在本实施方式中,除了图5的(b)的形成自对准硅化物阻挡膜18的工序以外,与通常的侧壁电荷陷阱型的otp或者mtp的非易失性半导体存储器件的制造工序是同样的。因此,本实施方式通过在通常的制造工序中追加形成自对准硅化物阻挡膜18的工序能够容易地实现。

41.图7是表示本实施方式的非易失性半导体存储器件的变形例的截面图。在变形例中,在硅半导体衬底的表面在图2所示的存储单元10的基础上,相邻地形成用于驱动存储单元10的mos晶体管50。在变形例中,关于与图2所示的存储单元10共同的构成要素,标注相同的附图标记而省略说明。

42.mos晶体管50在与存储单元10共同的p阱11的表面,与存储单元10以夹着元件分离绝缘层27方式相邻地形成。在p阱11的表面,夹着沟道区域52形成有掺杂了n型杂质的漏极区域53和源极区域54。从漏极区域53和源极区域54分别向沟道区域52形成有低杂质浓度漏极(ldd:lightly doped drain(轻掺杂漏极))区域65、66。以覆盖沟道区域52的方式形成有由氧化物(sio2)构成的绝缘膜55,在绝缘膜55上形成有具有大致矩形的截面的由多晶硅构成的栅极56。在栅极56的侧面且沟道区域52的正上方,隔着也沿栅极56的侧面形成的绝缘膜55,形成由氮化物(sin)构成的侧墙57。

43.在漏极区域53和源极区域54的表面分别形成有由例如与钛、钴或者镍的自对准硅化物(tisi、cosi或者nisi)构成的漏极自对准硅化物层61和源极自对准硅化物层62。在栅极56的上表面,也同样地形成有栅极自对准硅化物层63。以覆盖漏极自对准硅化物层61、源极自对准硅化物层62、栅极自对准硅化物层63和侧墙57的方式形成有由氮化物(sin)构成的氮化膜19。氮化膜19也覆盖元件分离绝缘层27和相邻的存储单元10的构造。

44.mos晶体管50与相邻的存储单元10的不同点在于,不包含自对准硅化物阻挡膜18,而形成有栅极自对准硅化物层63和低杂质浓度漏极(ldd:lightly doped drain)区域65、66这一点。因此,mos晶体管50能够利用制造存储单元10的工序来制作。例如,mos晶体管50的侧墙57,能够在图4的(c)所示的形成存储单元10的侧墙17的工序中形成。mos晶体管50的漏极区域53和源极区域54,能够在图5的(a)所示的形成存储单元10的漏极区域13和源极区域14的工序中形成。mos晶体管50的漏极自对准硅化物层61、源极自对准硅化物层62、栅极自对准硅化物层63和侧墙57,能够在图5的(c)所示的形成存储单元10的漏极自对准硅化物层21和源极自对准硅化物层22的工序中形成。

45.像这样,存储单元10和mos晶体管50能够利用共同的工序并行地制作。因此,变形例的包含存储单元10和mos晶体管50的非易失性半导体存储器件,能够抑制制造工序的工时的增加来制作,进而能够抑制制造成本。

46.图8是概略地表示本实施方式的非易失性半导体存储器件的电路的电路图。在非易失性半导体存储器件的电路中包括:控制该装置的整体的主控制器71、供给恒定电流的电源72、包含存储单元10的第1四位存储块73和第2四位存储块74。在第1四位存储块73中包括:在主控制器71的控制下控制第1四位存储块73的第1从控制器81、第2从控制器82、对栅

极供给偏置的栅极偏置部83、第1一位存储器84、第2一位存储器85、第3一位存储器86和第4一位存储器87。在此,第1一位存储器84、第2一位存储器85、第3一位存储器86和第4一位存储器87中,如图7所示,在存储单元10的结构的基础上还可以包含用于驱动存储单元10的晶体管等。第2四位存储块74也与第1四位存储块73具有同样的结构。此外,在此,关于2个四位存储块,表示了各存储块中包含4个一位存储器的例子,但一位存储器和四位存储块的数量不限于此。例如,与存储单元10对应的一位存储器的数量可以为1以上。这样的电路可以形成在1个半导体衬底上。

47.在本实施方式的非易失性半导体存储器件中,各存储器构件所包含的存储单元10,根据主控制器71和对应的从控制器的控制,实施数据的写入、读取和删除的动作。在图2所示的存储单元10中,在包含p阱11的衬底、漏极区域13、栅极16和源极区域14中,在写入、读取和删除的动作时,被施加表1所示的电压。

48.[表1]

[0049] 源极漏极栅极衬底写入5v0v5v0v读取0v0.5v~1v0v删除5v0v-5v0v

[0050]

存储单元10根据表1所示的电压进行动作,在写入的动作时,从源极区域14向与源极区域14相对的侧墙17注入电荷。读取的动作中,电荷是否被保持在与源极区域14相对的侧墙17中是根据在沟道区域12中流通的电流来判断的。在删除动作中,保持在与源极区域14相对的侧墙17中的电荷被源极区域14抽取。在表1所示的例子中,由于能够进行写入、读取和删除的动作,因此对应于mtp。仅能够进行写入和读取的动作的情况下,对应于otp。

[0051]

产业上的利用可能性

[0052]

本发明能够应用于例如ecu那样的被搭载于汽车中的控制电路。

[0053]

附图标记的说明

[0054]

10

ꢀꢀ

存储单元

[0055]

11

ꢀꢀ

p阱

[0056]

12

ꢀꢀ

沟道区域

[0057]

13

ꢀꢀ

漏极区域

[0058]

14

ꢀꢀ

源极区域

[0059]

15

ꢀꢀ

绝缘膜

[0060]

16

ꢀꢀ

栅极

[0061]

17

ꢀꢀ

侧墙

[0062]

18

ꢀꢀ

自对准硅化物阻挡膜

[0063]

19

ꢀꢀ

氮化膜

[0064]

21

ꢀꢀ

漏极自对准硅化物层

[0065]

22

ꢀꢀ

源极自对准硅化物层

[0066]

32

ꢀꢀ

漏极触点

[0067]

33

ꢀꢀ

源极触点

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1