一种封装组件、电子设备及封装方法与流程

1.本申请涉及半导体封装技术领域,特别是涉及一种封装组件、电子设备及封装方法。

背景技术:

2.半导体芯片用于各种电子应用中,诸如个人计算机、手机、数码相机和其他电子设备。随着集成电子技术的不断发展,对半导体芯片性能要求也日渐提高,如功能增强、尺寸减小、耗能与成本降低等。

3.为适应微电子封装技术的多功能、小型化、便携式、高速度、低功耗和高可靠性发展趋势,系统级封装sip(system in package)技术作为新兴异质集成技术,成为越来越多芯片的封装形式,系统级封装是将多种功能芯片和元器件集成在一个封装内,从而实现一个完整的功能。系统级封装是一种新型封装技术,具有开发周期短,功能更多,功耗更低,性能更优良、成本价格更低,体积更小,质量轻等优点。

4.然而,随着对封装组件及功能越来越高的需求,现有的系统级封装组件的封装尺寸较大,且走线较长,焊线中存在寄生电容等现象。

技术实现要素:

5.为了解决现有技术的中半导体封装组件存在的上述问题,本申请提供了一种封装组件和封装方法。

6.为解决上述问题,本申请提供了一种封装组件,该封装组件包括:

7.基板;

8.封装芯片,设置在所述基板上,所述封装芯片电连接所述基板;

9.第一半导体芯片,设置于所述封装芯片上,所述第一半导体芯片电连接所述基板;

10.扇出区域,设置于所述封装芯片上,且与所述第一半导体芯片相邻设置,所述扇出区域电连接所述第一半导体芯片和所述基板,其中所述扇出区域和所述第一半导体芯片的总面积约等于所述封装芯片的面积;

11.第一模塑料,用于封装所述第一半导体芯片、所述封装芯片和所述基板。

12.为解决上述技术问题,本申请还提供了一种电子设备,该电子设备包括上述封装组件。

13.为解决上述技术问题,本申请还提供了一种封装方法,该封装方法包括:

14.提供基板;

15.在所述基板上设置封装芯片,所述封装芯片电连接所述基板;

16.扇出第一半导体芯片得到扇出区域,所述扇出区域与所述第一半导体芯片相邻设置;

17.在所述封装芯片上设置所述第一半导体芯片和所述扇出区域,所述第一半导体芯片电连接所述基板,其中,所述扇出区域电连接所述第一半导体芯片和所述基板,所述扇出

区域和所述第一半导体芯片的总面积约等于所述封装芯片的面积;

18.通过第一模塑料封装所述第一半导体芯片、所述封装芯片和所述基板。

19.与现有技术相比,本申请的封装组件包括:基板、封装芯片、第一半导体芯片、扇出区域和第一模塑料,封装芯片设置于基板上,且电连接基板,第一半导体芯片设置在封装芯片上,且电连接基板,因此,可以减少封装组件的封装尺寸;扇出区域设置于封装芯片上,且与第一半导体芯片相邻设置,该扇出区域电连接第一半导体芯片和基板,且扇出区域和第一半导体芯片的面积约等于封装芯片的面积。因此,本申请的第一半导体芯片通过扇出区域电连接基板,能减少焊线长度,以降低信号衰减、串扰、焊线中的寄生电容等不良现象发生的几率,且第一模塑料用于封装第一半导体芯片、封装芯片和基板。

附图说明

20.为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

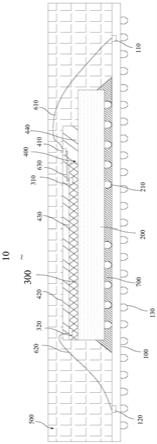

21.图1是本申请提供的封装组件的第一实施例结构示意图;

22.图2是本申请提供的封装组件中第一半导体芯片和扇出区域的第一实施例结构示意图;

23.图3是本申请提供的封装组件的第二实施例结构示意图;

24.图4是本申请提供的封装组件中第一半导体芯片和扇出区域的第二实施例结构示意图;

25.图5是本申请提供的封装方法的流程示意图。

26.附图标记为:封装组件10;基板100;封装芯片200;第一半导体芯片300;扇出区域400;第一模塑料500;第一焊盘110;第二焊盘410;第一连接线610;第一表面430;第二表面420;第三表面440;第二连接线630;第三焊盘310;第三连接线620;第四焊盘120;第五焊盘320;第一焊球210;第二焊球130;填充胶700。

具体实施方式

27.下面结合附图和实施例,对本申请作进一步的详细描述。特别指出的是,以下实施例仅用于说明本申请,但不对本申请的范围进行限定。同样的,以下实施例仅为本申请的部分实施例而非全部实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本申请保护的范围。

28.本申请的说明书和权利要求书及上述附图中的术语“第一”、“第二”、“第三”、“第四”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本申请的实施例,例如能够以除了在这里图示或描述的那些以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

29.参见图1

‑

图4,图1是本申请提供的封装组件10的第一实施例结构示意图,图2是本申请提供的封装组件10中第一半导体芯片300和扇出区域400的第一实施例结构示意图,图3是本申请提供的封装组件10的第二实施例结构示意图,图4是本申请提供的封装组件10中第一半导体芯片300和扇出区域400的第二实施例结构示意图。

30.本申请提供了一种封装组件10,该封装组件10可以包括基板100、封装芯片200、第一半导体芯片300、扇出区域400和第一模塑料500。

31.封装芯片200可以设置于基板100上,且封装芯片200可以电连接基板100。

32.第一半导体芯片300可以设置于封装芯片200上,且电连接基板100。

33.扇出区域400可以设置于封装芯片200上,且与第一半导体芯片300相邻设置,扇出区域400可以电连接第一半导体芯片300和基板100,以使第一半导体芯片300通过扇出区域400电连接基板100。

34.扇出区域400与第一半导体芯片300的总面积可以约等于封装芯片200的面积。具体地,扇出区域400与第一半导体芯片300的总面积可以小于或等于封装芯片200的面积,以使第一半导体芯片300和扇出区域400能同时设置于封装芯片200远离基板100的表面内。其中,封装芯片200的面积与扇出区域400与第一半导体芯片300的总面积的差值位于预设的阈值范围内。

35.第一模塑料500可以用来封装第一半导体芯片300、封装芯片200和基板100。

36.因此,本申请所提供的封装组件10的第一半导体芯片300通过扇出区域400电连接基板100,能减少焊线长度,以降低信号衰减、串扰、焊线中的寄生电容等不良现象发生的几率;且由于扇出区域400与第一半导体芯片300均置于封装芯片200上,可以减少封装组件10的封装尺寸。

37.参见图1

‑

图4,本申请提供了一种封装组件10。

38.该封装组件10可以包括基板100。基板100可以由与现有技术相同材料制成,例如,基板100可以由半导体材料形成,该半导体材料为硅,如双马来酰亚胺三嗪(bismaleimide triazine,bt),聚酰亚胺(polyimide)或味之素构建膜(ajinomotobuild

‑

up film,abf)的有机材料形成。

39.封装组件10进一步可以包括封装芯片200,封装芯片200可以设置于基板100上,且封装芯片200可以电连接基板100。

40.封装芯片200可以包括至少两个第二半导体芯片(图未示)。其中,第二半导体芯片可以是用于存储数据的存储器半导体芯片。存储器半导体芯片可以是高速缓存存储器芯片,其暂时存储并提供在系统级芯片(system on chip)的逻辑运算中使用的数据。

41.具体地,可以采用球珊阵列封装(ball grid array)封装方式封装至少两个第二半导体芯片以形成封装芯片200。封装芯片200采用球珊阵列封装方式并直接设置于基板100上,可以通过封装芯片200靠近基板100表面的焊球或焊凸点作为外引线,使得封装芯片200电连接基板100。

42.在本实施例中,封装芯片200采用标准的bga封装,可以将不同存储类型的第二半导体芯片封装成封装芯片200,以节约封装成本。例如,不同类型的存储芯片可以包括易失性存储芯片和/或非易失性存储芯片。易失性存储芯片可包括例如动态随机存取存储器(dynamic random

‑

access memory dram)、静态随机存取存储器(static ram,sram)、晶闸

管随机存取存储器(thyristor ram,tram)、零电容随机存取存储器(zero capacitor ram,zram)等。非易失性存储芯片可包括例如闪存、磁性随机存取存储器(magnetic ram,mramo)、自旋转移力矩随机存取存储器(spin

‑

transfer torquemram,stt

‑

mram)、铁电随机存取存储器(ferroelectric ram,fram)、相变随机存取存储器(phase change ram,pram)、电阻式随机存取存储器(resistive ram,rram)等。

43.其中,第二半导体芯片可以堆叠设置,或者第二半导体芯片可以平行设置。

44.具体地,至少两个第二半导体芯片可以包括两个第二半导体芯片,两个第二半导体芯片可以堆叠设置或者平行设置以扩大封装芯片200的存储容量。

45.在本申请一实施例中,至少两个第二半导体芯片可以包括四个第二半导体芯片,该四个第二半导体芯片可以堆叠设置,以扩大封装芯片200的存储容量的。相对于现有的多个半导体芯片平铺设置,减少封装基板100的尺寸。

46.在本申请一实施例中,至少两个第二半导体芯片可以包括六个第二半导体芯片,该六个第二半导体芯片可以堆叠设置,以扩大封装芯片200的存储容量的。相对于现有的多个半导体芯片平铺设置,减少封装基板100的尺寸。

47.在一实施例中,至少两个半导体芯片可以包括八个第二半导体芯片,该八个第二半导体芯片可以堆叠设置,以扩大封装芯片200的存储容量的。相对于现有的多个半导体芯片平铺设置,减少封装基板100的尺寸。

48.封装芯片200还可以包括第二模塑料。第二模塑料可以用于封装至少两个第二半导体芯片,以形成封装芯片200。

49.其中,第二模塑料可以由与现有技术相同材料制成。例如:第二模塑料可以由环氧树脂(epoxy),树脂(resin),可模制聚合物(moldablepolymer)等形成。其中,第二模塑料的制成材料本申请在此不作限定。

50.封装组件10还进一步包括第一半导体芯片300,第一半导体芯片300可以设置于封装芯片200上,且第一半导体芯片300电连接基板100。具体地,第一半导体芯片300可以设置于封装芯片200远离基板100一侧的表面上。

51.第一半导体芯片300可以是执行数据的逻辑运算的处理器。例如,第一半导体芯片300可包括诸如执行逻辑运算的应用处理器的系统级芯片(system on chip)。

52.在一实施例中,可以在第一半导体芯片300靠近封装芯片200的表面上设置daf胶膜,以将第一半导体芯片300固定于封装芯片200上。在其他实施例中,也可以设置其他贴膜以固定第一半导体芯片300于封装芯片200上。

53.封装组件10进一步包括扇出区域400,扇出区域400可以设置于封装芯片200上,且与第一半导体芯片300相邻设置,扇出区域400可以电连接第一半导体芯片300和基板100。并且,扇出区域400与第一半导体芯片300的总面积可以约等于封装芯片200的面积。

54.具体地,扇出区域400与第一半导体芯片300的总面积可以小于或等于封装芯片200的面积,以使第一半导体芯片300和扇出区域400能同时设置于封装芯片200远离基板100的表面内。其中,封装芯片200的面积与扇出区域400与第一半导体芯片300的总面积的差值位于预设的阈值范围内。

55.如图1和图2所示,图2是图1中第一半导体芯片300和扇出区域400的第一实施例的结构示意图。

56.扇出区域400可以围绕第一半导体芯片300的两边设置,也即可以扇出第一半导体芯片300的两条相邻边,用于扩散第一半导体芯片300的线路,以降低焊线的难度,便于加工制造,提高产品良率。

57.在一实施例中,扇出区域400还可以围绕第一半导体芯片300的一边设置或者围绕第一半导体芯片300的对边设置。

58.在一实施例中,扇出区域400还可以围绕第一半导体芯片300的某一边的部分区域设置。

59.如图3和图4所示,图4是图3中第一半导体芯片300和扇出区域400的第二实施例的结构示意图。

60.扇出区域400还可以围绕整个第一半导体芯片300设置,也即扇出整个第一半导体芯片300,用于扩散第一半导体芯片300的线路,以降低焊线的难度,便于加工制造,提高产品良率。

61.在其他实施例中,第一半导体芯片300的扇出区域400的面积可以根据实际情况。

62.参见图1封装组件10还进一步包括第一模塑料500,第一模塑料500可以用来封装第一半导体芯片300、封装芯片200和基板100。其中,第一模塑料500可以采用与第二膜塑料相同材料,在此不再赘述。

63.封装组件10还进一步包括第一连接线610,具体地,第一连接线610可以包括金线、铜线、合金线等。基板100上可以设有第一焊盘110,扇出区域400可以设有第二焊盘410。第一连接线610的一端可以连接第一焊盘110,另一端可以连接第二焊盘410。

64.封装组件10还可以包括设置在扇出区域400内的第二连接线630,具体地,第二连接线630可以包括金线、铜线、合金线等。第一半导体芯片300远离封装芯片200的表面可以设有第三焊盘310,第二连接线630的一端连接第二焊盘410,另一端连接第三焊盘310,以使得第一半导体芯片300可以通过第一连接线610和第二连接线630与基板100电连接。

65.扇出区域400还可以包括重布线层,重布线层可以具有相对设置的第一表面430和第二表面420,重布线层的第一表面430可以与第一半导体芯片300接触,第二焊盘410可以设置在重布线层的第二表面420上。

66.具体地,位于扇出区域400第二表面上420的第二焊盘410可以远离第一半导体芯片300设置。例如,第二焊盘410可以设置在重布线层的第二表面420的边缘处,以降低线路的密集度,降低焊线的难度,提高良品率。

67.在一实施例中,位于第一半导体芯片300上的第三焊盘310可以靠近扇出区域400设置。例如,第三焊盘310可以设置在第一半导体芯片300的边缘处,以缩短第二连接线630的线路。

68.封装组件10还进一步包括第三连接线620,具体地,第三连接线620可以包括金线、铜线、合金线等。基板100的可以设置有第四焊盘120。第一半导体芯片300远离封装芯片200的表面上可以设有第五焊盘320。第三连接线620的一端可以连接第四焊盘120,另一端可以连接第五焊盘320,以使第一半导体芯片300电连接基板100。

69.进一步地,重布线层可以具有第三表面440,第三表面440可以与第一表面430和第二表面420相对设置。重布线层的第三表面440可以与第一半导体芯片300靠近封装芯片200的表面位于同一平面,以使第一半导体芯片300与扇出区域400可以稳定放置于封装芯片

200上。

70.封装组件10还进一步包括第一焊球210,第一焊球210设置在封装芯片200靠近基板100的表面上。封装芯片200采用球珊阵列封装(ball grid array)封装方式封装至少两个第二半导体芯片以形成封装芯片200,以通过第一焊球210作为封装芯片200的外引线,以使封装芯片200电连接基板100。

71.封装组件10还可以包括填充胶700,填充胶700可以设置于封装芯片200与基板100之间,以通过填充胶700填充因封装芯片200与基板100焊接后,第一焊球210与基板100之间的间隙,从而能够通过填充胶700有效地防止封装芯片200与基板100之间出现空洞、气泡等缺陷。

72.封装组件10进一步包括第二焊球130,第二焊球130可以设置于基板100远离封装芯片200的表面上。

73.因此,本申请提供的封装组件10通过bga封装多个第二半导体芯片封装成一种封装芯片200,以扩大封装芯片200的存储容量的。相对于现有的多个半导体芯片平铺设置,减少封装基板100的尺寸。扇出区域400与第一半导体芯片300相邻设置,且通过扇出区域400第二表面420上的第二焊盘410与第二连接线630以扩散第一半导体芯片300的线路,从而减少线路的密集度,便于加工制造。第一半导体芯片300和扇出区域400均可以设置于封装芯片200上以减少整个基板100的尺寸,节约加工成本;且第一半导体芯片300可以通过扇出区域400电连接基板100,能减少焊线长度,以降低信号衰减、串扰、焊线中的寄生电容等不良现象发生的几率。

74.本申请还提供了一种电子设备,该电子设备包括上述任意一实施例中的封装组件10。在不同实施例中,电子设备包括但不限于蜂窝电话、智能电话、其他无线通信设备、个人数字助理、音频播放器、其他媒体播放器、音乐记录器、录像机、照相机、其他媒体记录器、收音机、医疗设备、计算器、可编程遥控器、寻呼机、上网本电脑、个人数字助理(pda)、便携式多媒体播放器(pmp)、运动图像专家组(mpeg

‑

1或mpeg

‑

2)音频层3(mp3)播放器,便携式医疗设备以及数码相机及其组合。

75.参见图5,图5是本申请提供的封装方法的流程示意图。

76.本申请还提供了一种封装方法,该方法包括:

77.步骤s101:提供基板100,其中,基板100可以由与现有技术相同材料制成,例如,基板100可以由半导体材料形成,该半导体材料为硅,如双马来酰亚胺三嗪(bismaleimide triazine,bt),聚酰亚胺(polyimide)或味之素构建膜(ajinomotobuild

‑

up film,abf)的有机材料形成。

78.步骤s102:在所述基板100上设置封装芯片200,所述封装芯片200电连接所述基板100;

79.封装芯片200可以包括至少两个第二半导体芯片(图未示)。其中,第二半导体芯片可以是用于存储数据的存储器半导体芯片。存储器半导体芯片可以是高速缓存存储器芯片,其暂时存储并提供在系统级芯片(system on chip)的逻辑运算中使用的数据。

80.具体地,可以采用球珊阵列封装(ball grid array)封装方式封装至少两个第二半导体芯片以形成封装芯片200。封装芯片200采用球珊阵列封装方式并直接设置于基板100上,可以通过封装芯片200靠近基板100表面的焊球或焊凸点作为外引线,使得封装芯片

200电连接基板100。

81.在本实施例中,封装芯片200采用标准的bga封装,可以将不同存储类型的第二半导体芯片封装成封装芯片200,以节约封装成本。

82.其中,第二半导体芯片可以堆叠设置,或者第二半导体芯片可以平行设置。

83.具体地,至少两个第二半导体芯片可以包括两个第二半导体芯片,两个半导体芯片可以堆叠设置或者平行设置以扩大封装芯片200的存储容量。

84.在本申请一实施例中,至少两个第二半导体芯片可以包括四个第二半导体芯片,该四个半导体芯片可以堆叠设置,以扩大封装芯片200的存储容量的。相对于现有的多个半导体芯片平铺设置,减少封装基板100的尺寸。

85.在本申请一实施例中,至少两个第二半导体芯片可以包括六个第二半导体芯片,该六个半导体芯片可以堆叠设置,以扩大封装芯片200的存储容量的。相对于现有的多个半导体芯片平铺设置,减少封装基板100的尺寸。

86.在一实施例中,至少两个半导体芯片可以包括八个第二半导体芯片,该八个半导体芯片可以堆叠设置,以扩大封装芯片200的存储容量的。相对于现有的多个半导体芯片平铺设置,减少封装基板100的尺寸。

87.封装芯片200还可以包括第二模塑料。第二模塑料可以用于封装至少两个第二半导体芯片,以形成封装芯片200。

88.在基板100上设置封装芯片200之前,可以植入第一焊球210于封装芯片200靠近基板100的表面。

89.其中,封装芯片200采用球珊阵列封装(ball grid array)封装方式封装至少两个第二半导体芯片以形成封装芯片200,以通过第一焊球210作为封装芯片200的外引线,以使封装芯片200电连接基板100。

90.在所述基板100上设置封装芯片200之后,还可以在封装芯片200与基板100之间植入填充胶700,以通过填充胶700填充因封装芯片200与基板100焊接后,第一焊球210与基板100之间的间隙,从而能够通过填充胶700有效地防止封装芯片200与基板100之间出现空洞、气泡等缺陷。

91.步骤s103:扇出第一半导体芯片300以得到扇出区域400,所述扇出区域400与所述第一半导体芯片300相邻设置。

92.具体地,扇出区域400可以围绕第一半导体芯片300的两边设置,也即可以扇出第一半导体芯片300的两条相邻边,用于扩散第一半导体芯片300的线路,以降低焊线的难度,便于加工制造,提高产品良率。

93.在一实施例中,扇出区域400还可以围绕第一半导体芯片300的一边设置或者围绕第一半导体芯片300的对边设置。

94.在一实施例中,扇出区域400还可以围绕第一半导体芯片300的某一边的部分区域设置。

95.在一实施例中,扇出区域400还可以围绕整个第一半导体芯片300设置,也即扇出整个第一半导体芯片300,用于扩散第一半导体芯片300的线路,以降低焊线的难度,便于加工制造,提高产品良率。

96.在其他实施例中,第一半导体芯片300的扇出区域400的面积可以根据实际情况。

97.步骤s104:在所述封装芯片200上设置所述第一半导体芯片300和所述扇出区域400,所述第一半导体芯片300电连接所述基板100,其中,所述扇出区域400电连接所述第一半导体芯片300和所述基板100,其中所述扇出区域400和所述第一半导体芯片300的总面积约等于所述封装芯片200的面积。

98.步骤s105:通过第一模塑料500封装所述第一半导体芯片300、所述封装芯片200和所述基板100。

99.具体地,第一模塑料500可以由与现有技术相同材料制成。例如:第一模塑料500可以由环氧树脂(epoxy),树脂(resin),可模制聚合物(moldablepolymer)等形成。其中,第一模塑料500的制成材料本申请在此不作限定。

100.进一步地,在用第一模塑料500封装所述第一半导体芯片300、所述封装芯片200和所述基板100之后,可以通过在基板100远离封装芯片200的表面植入第二焊球130。

101.因此,本申请提供的封装组件10通过bga封装多个第二半导体芯片封装成一种封装芯片200,以扩大封装芯片200的存储容量的。相对于现有的多个半导体芯片平铺设置,减少封装基板100的尺寸。扇出区域400与第一半导体芯片300相邻设置,且通过扇出区域400第二表面420上的第二焊盘410与第二连接线630以扩散第一半导体芯片300的线路,从而减少线路的密集度,便于加工制造。第一半导体芯片300和扇出区域400均可以设置于封装芯片200上以减少整个基板100的尺寸,节约加工成本;且第一半导体芯片300可以通过扇出区域400电连接基板100,能减少焊线长度,以降低信号衰减、串扰、焊线中的寄生电容等不良现象发生的几率。

102.本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的方法及其核心思想;同时,对于本领域的一般技术人员,依据本申请的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本申请的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1