一种驱动背板及其制作方法、探测基板及探测装置与流程

1.本发明涉及光电技术技术领域,特别是涉及一种驱动背板及其制作方法、探测基板及探测装置。

背景技术:

2.在数字医疗影像领域广泛采用了探测基板作为光探测传感部件,探测基板中的驱动背板可实现对光敏器件生成的电信号的读取,而驱动背板中的晶体管由于其本身的结构和电学性质的影响,会导致探测基板的噪声较大,尤其在低剂量下,探测基板的信噪比比较低。

3.目前,为了降低噪声,可在驱动背板中设置放大晶体管,通过放大晶体管的信号增益效果,等效降低噪声。

4.然而,目前的驱动背板中的各个放大晶体管的载流子迁移率不同,导致各个放大晶体管的信号增益不同,则驱动背板中的放大晶体管的信号增益不均匀,通过放大晶体管放大后的各个电信号的强度也不均匀,从而产生固定图像噪声甚至坏点和坏线,导致根据放大后的信号线生成的图像的成像质量差。

技术实现要素:

5.本发明提供一种驱动背板及其制作方法、探测基板及探测装置,以解决现有的在驱动背板中设置的各个放大晶体管的信号增益不同,会产生固定图像噪声甚至坏点和坏线,导致根据放大后的信号线生成的图像的成像质量差的问题。

6.为了解决上述问题,本发明公开了一种驱动背板,包括:衬底基板和设置在所述衬底基板上的多个驱动模块,每个所述驱动模块包括复位晶体管、读取晶体管、放大晶体管和存储电容;

7.所述复位晶体管,与所述存储电容连接,被配置为对所述存储电容进行复位;

8.所述存储电容,与光敏器件连接,被配置为存储所述光敏器件生成的电信号;

9.所述放大晶体管,与所述存储电容连接,被配置为对所述存储电容中存储的电信号进行放大处理;

10.所述读取晶体管,与所述放大晶体管连接,被配置为读取所述放大晶体管放大后的所述电信号;

11.其中,所述放大晶体管中的有源层的材料为非晶硅或氧化物半导体。

12.可选的,所述复位晶体管包括依次设置在所述衬底基板一侧的第一有源层、第一栅绝缘层、第一栅极、层间介质层和第一源漏电极;

13.其中,所述第一源漏电极中的第一源极通过贯穿所述层间介质层的第一过孔与所述第一有源层连接,所述第一源漏电极中的第一漏极通过贯穿所述层间介质层的第二过孔与所述第一有源层连接。

14.可选的,所述读取晶体管包括依次设置在所述衬底基板一侧的第二有源层、所述

第一栅绝缘层、第二栅极、所述层间介质层和第二源漏电极;

15.所述第二源漏电极中的第二源极通过贯穿所述层间介质层的第三过孔与所述第二有源层连接,所述第二源漏电极中的第二漏极通过贯穿所述层间介质层的第四过孔与所述第二有源层连接;

16.其中,所述第一有源层与所述第二有源层同层设置,所述第一栅极与所述第二栅极同层设置,所述第一源漏电极与所述第二源漏电极同层设置。

17.可选的,所述驱动背板还包括设置在所述衬底基板与所述第一有源层之间的缓冲层和第二栅绝缘层,所述缓冲层设置在所述第二栅绝缘层远离所述衬底基板的一侧;

18.所述放大晶体管包括依次设置在所述衬底基板上的第三栅极、所述第二栅绝缘层、第三有源层和第三源漏电极;所述第二源漏电极中的第二源极通过贯穿所述层间介质层的第五过孔与所述第三源漏电极中的第三漏极连接;

19.其中,所述第三有源层在所述衬底基板上的正投影与所述缓冲层在所述衬底基板上的正投影不存在重合区域。

20.可选的,所述第三有源层的材料为非晶硅,所述第三有源层包括设置在所述第二栅绝缘层上的第一无掺杂非晶硅层,以及设置在所述第一无掺杂非晶硅层上的第一掺杂非晶硅层;

21.或者,所述第三有源层的材料为氧化物半导体。

22.可选的,所述驱动背板还包括覆盖所述层间介质层、所述第一源漏电极和所述第二源漏电极的第二钝化层;

23.所述放大晶体管包括依次设置在所述层间介质层上的第四栅极、所述第二钝化层、第四有源层和第四源漏电极;

24.其中,所述第四栅极与所述第一源漏电极和所述第二源漏电极均同层设置,且所述第四栅极与所述第一源漏电极中的第一源极连接;所述第四源漏电极中的第四漏极通过贯穿所述第二钝化层的第六过孔与所述第二源漏电极中的第二源极连接。

25.可选的,所述第四有源层的材料为非晶硅,所述第四有源层包括设置在所述第二钝化层上的第二无掺杂非晶硅层,以及设置在所述第二无掺杂非晶硅层上的第二掺杂非晶硅层;

26.或者,所述第四有源层的材料为氧化物半导体。

27.可选的,所述存储电容包括相对设置第一极板和第二极板,所述第一极板与所述第一源漏电极同层设置,所述第二极板与所述第四源漏电极或所述第三源漏电极同层设置,且所述第一极板与所述第一源漏电极中的第一源极连接;

28.其中,所述第一极板在所述衬底基板上的正投影与所述第二极板在所述衬底基板上的正投影至少部分重合。

29.为了解决上述问题,本发明还公开了一种驱动背板的制作方法,包括:

30.提供一衬底基板;

31.在所述衬底基板上形成多个驱动模块;每个所述驱动模块包括复位晶体管、读取晶体管、放大晶体管和存储电容;

32.其中,所述复位晶体管,与所述存储电容连接,被配置为对所述存储电容进行复位;所述存储电容,与光敏器件连接,被配置为存储所述光敏器件生成的电信号;所述放大

晶体管,与所述存储电容连接,被配置为对所述存储电容中存储的电信号进行放大处理;所述读取晶体管,与所述放大晶体管连接,被配置为读取所述放大晶体管放大后的所述电信号;所述放大晶体管中的有源层的材料为非晶硅或氧化物半导体。

33.为了解决上述问题,本发明还公开了一种探测基板,包括光敏器件以及上述的驱动背板,所述光敏器件与所述驱动背板连接。

34.为了解决上述问题,本发明还公开了一种探测装置,包括上述的探测基板。

35.与现有技术相比,本发明包括以下优点:

36.通过在衬底基板上设置多个驱动模块,每个驱动模块包括复位晶体管、读取晶体管、放大晶体管和存储电容,复位晶体管与存储电容连接,被配置为对存储电容进行复位,存储电容与光敏器件连接,被配置为存储光敏器件生成的电信号,放大晶体管与存储电容连接,被配置为对存储电容中存储的电信号进行放大处理,读取晶体管与放大晶体管连接,被配置为读取放大晶体管放大后的电信号,放大晶体管中的有源层的材料为非晶硅或氧化物半导体。通过在驱动背板中设置多个放大晶体管,并采用非晶硅或氧化物半导体作为放大晶体管中有源层的材料,使得驱动背板中的各个放大晶体管中的载流子迁移率较为均匀,因此,可提高驱动背板中的各个放大晶体管的增益均匀性,避免放大晶体管放大后的电信号的强度不均匀而产生的图像噪声甚至坏点和坏线,从而可提高根据放大后的信号线生成的图像的成像质量。

附图说明

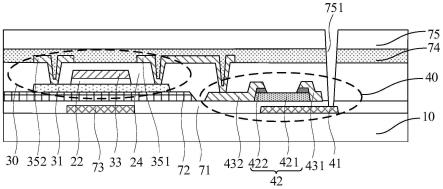

37.图1示出了本发明实施例的第一种驱动背板中读取晶体管和放大晶体管的剖面图;

38.图2示出了本发明实施例的第一种驱动背板中复位晶体管和放大晶体管的剖面图;

39.图3示出了本发明实施例的第二种驱动背板中读取晶体管和放大晶体管的剖面图;

40.图4示出了本发明实施例的第二种驱动背板中复位晶体管和放大晶体管的剖面图;

41.图5示出了本发明实施例的第三种驱动背板中读取晶体管和放大晶体管的剖面图;

42.图6示出了本发明实施例的第三种驱动背板中复位晶体管和放大晶体管的剖面图;

43.图7示出了图1至图6所示的驱动背板的等效电路图;

44.图8示出了本发明实施例的一种驱动背板的制作方法的流程图;

45.图9示出了图1所示的驱动背板对应的探测基板的剖面图;

46.图10示出了图2所示的驱动背板对应的探测基板的剖面图;

47.图11示出了图3所示的驱动背板对应的探测基板的剖面图;

48.图12示出了图4所示的驱动背板对应的探测基板的剖面图。

具体实施方式

49.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

50.在相关技术中,驱动背板中的每个放大晶体管的有源层的材料均为多晶硅,并且,放大晶体管中有源层的具体制作工序为:先沉积一层非晶硅层,再通过ela(excimer laser annealing,准分子激光退火)工艺对非晶硅层进行晶化处理,从而将非晶硅层转换为多晶硅层。

51.但是,由于晶化处理的设备和工艺等因素的影响,在采用激光退火工艺进行晶化处理时,驱动背板中的各个放大晶体管的有源层的结晶度不一致,则使得各个放大晶体管的载流子迁移率不一样,进而导致各个放大晶体管的信号增益不同,即驱动背板中的各个放大晶体管的信号增益均匀性不好,因此,通过放大晶体管对光敏器件生成的电信号进行放大处理后,放大后的各个电信号的强度也不均匀,容易产生固定图像噪声甚至坏点和坏线,根据放大后的信号线生成的图像的成像质量差。

52.因此,本发明实施例通过在驱动背板中设置多个放大晶体管,并采用非晶硅或氧化物半导体作为放大晶体管中有源层的材料,使得驱动背板中的各个放大晶体管中的载流子迁移率较为均匀,因此,可提高驱动背板中的各个放大晶体管的增益均匀性,避免放大晶体管放大后的电信号的强度不均匀而产生的图像噪声甚至坏点和坏线,从而可提高根据放大后的信号线生成的图像的成像质量。

53.实施例一

54.参照图1,示出了本发明实施例的第一种驱动背板中读取晶体管和放大晶体管的剖面图,图2示出了本发明实施例的第一种驱动背板中复位晶体管和放大晶体管的剖面图;图3示出了本发明实施例的第二种驱动背板中读取晶体管和放大晶体管的剖面图,图4示出了本发明实施例的第二种驱动背板中复位晶体管和放大晶体管的剖面图;图5示出了本发明实施例的第三种驱动背板中读取晶体管和放大晶体管的剖面图,图6示出了本发明实施例的第三种驱动背板中复位晶体管和放大晶体管的剖面图。

55.本发明实施例提供了一种驱动背板,包括:衬底基板10和设置在衬底基板10上的多个驱动模块,每个驱动模块包括复位晶体管20、读取晶体管30、放大晶体管40和存储电容50。

56.复位晶体管20与存储电容50连接,被配置为对存储电容50进行复位;存储电容50与光敏器件连接,被配置为存储光敏器件生成的电信号;放大晶体管40与存储电容50连接,被配置为对存储电容50中存储的电信号进行放大处理;读取晶体管30与放大晶体管40连接,被配置为读取放大晶体管40放大后的电信号;其中,放大晶体管40中的有源层的材料为非晶硅或氧化物半导体。

57.在实际产品中,衬底基板10可以为玻璃基板,在衬底基板10上设置有呈阵列分布的多个驱动模块,每个驱动模块均包括复位晶体管20、读取晶体管30、放大晶体管40和存储电容50。

58.在实际驱动过程中,先控制复位晶体管20打开,通过复位晶体管20对存储电容50进行复位,以释放所述存储电容50内存储的电荷;在光敏器件将光信号转换为电信号之后,存储电容50存储光敏器件生成的电信号,存储电容50基于光敏器件生成的电信号可控制放

大晶体管40的栅极电压,基于放大晶体管40的栅极电压和放大晶体管的源极提供的vdd电压,使得放大晶体管40工作在饱和区,进而通过放大晶体管40对存储电容50中存储的电信号进行放大处理;最后,控制读取晶体管30打开,读取放大晶体管40放大后的电信号。

59.其中,复位晶体管20和读取晶体管30中的有源层的材料均为多晶硅,而放大晶体管40中的有源层的材料为非晶硅或氧化物半导体。

60.通过在驱动背板中增加放大晶体管40,通过放大晶体管40的信号增益效果,等效降低噪声,因此,可在低剂量下提供较高的信噪比;并且,将放大晶体管40中的有源层的材料设置为非晶硅或氧化物半导体,则放大晶体管40中的有源层不会采用激光退火工艺进行晶化处理,可使得驱动背板中的各个放大晶体管40中的载流子迁移率较为均匀,提高驱动背板中的各个放大晶体管40的增益均匀性,避免放大晶体管40放大后的电信号的强度不均匀而产生的图像噪声甚至坏点和坏线,从而可提高根据放大后的信号线生成的图像的成像质量。

61.如图2、图4和图6所示,复位晶体管20包括依次设置在衬底基板10一侧的第一有源层21、第一栅绝缘层22、第一栅极23、层间介质层24和第一源漏电极;第一源漏电极包括同层设置的第一源极251和第一漏极252;其中,第一源漏电极中的第一源极251通过贯穿层间介质层24的第一过孔与第一有源层21连接,第一源漏电极中的第一漏极252通过贯穿层间介质层24的第二过孔与第一有源层21连接。

62.第一有源层21也就是复位晶体管20的有源层,其材料为多晶硅;并且,第一有源层21包括非掺杂区和位于非掺杂区两侧的掺杂区,与第一源极251连接位置处的第一有源层21是位于掺杂区的第一有源层21,与第一漏极252连接位置处的第一有源层21也是位于掺杂区的第一有源层21,通过对第一源极251和第一漏极252接触位置处的第一有源层21进行掺杂,以增加第一有源层21与第一源极251和第一漏极252的欧姆接触。

63.如图1、图3和图5所示,读取晶体管30包括依次设置在衬底基板10一侧的第二有源层31、第一栅绝缘层22、第二栅极33、层间介质层24和第二源漏电极;第二源漏电极包括同层设置的第二源极351和第二漏极352;第二源漏电极中的第二源极351通过贯穿层间介质层24的第三过孔与第二有源层31连接,第二源漏电极中的第二漏极352通过贯穿层间介质层24的第四过孔与第二有源层31连接;其中,第一有源层21与第二有源层31同层设置,第一栅极23与第二栅极33同层设置,第一源漏电极与第二源漏电极同层设置。

64.第二有源层31也就是读取晶体管30的有源层,其材料为多晶硅;并且,第二有源层31包括非掺杂区和位于非掺杂区两侧的掺杂区,与第二源极351连接位置处的第二有源层31是位于掺杂区的第二有源层31,与第二漏极352连接位置处的第二有源层31也是位于掺杂区的第二有源层31,通过对第二源极351和第二漏极352接触位置处的第二有源层31进行掺杂,以增加第二有源层31与第二源极351和第二漏极352的欧姆接触。

65.需要说明的是,上述复位晶体管20和读取晶体管30可以为n型晶体管也可以为p型晶体管。当复位晶体管20为p型晶体管时,第一有源层21的掺杂区掺杂的离子可以为硼离子,当复位晶体管20为n型晶体管时,第一有源层21的掺杂区掺杂的离子可以为磷离子;相应的,当读取晶体管30为p型晶体管时,第二有源层31的掺杂区掺杂的离子可以为硼离子,当读取晶体管30为n型晶体管时,第二有源层31的掺杂区掺杂的离子可以为磷离子。

66.在本发明一种可选的实施方式中,如图1和图2所示,驱动背板还包括设置在衬底

基板10与第一有源层21之间的缓冲层72和第二栅绝缘层71,缓冲层72设置在第二栅绝缘层71远离衬底基板10的一侧;放大晶体管40包括依次设置在衬底基板10上的第三栅极41、第二栅绝缘层71、第三有源层42和第三源漏电极;第三源漏电极包括同层设置的第三源极431和第三漏极432;第二源漏电极中的第二源极351通过贯穿层间介质层24的第五过孔与第三源漏电极中的第三漏极432连接;其中,第三有源层42在衬底基板10上的正投影与缓冲层72在衬底基板10上的正投影不存在重合区域。

67.具体的,放大晶体管40中的第三栅极41设置在衬底基板10上,第二栅绝缘层71覆盖第三栅极41和衬底基板10,缓冲层72设置在第二栅绝缘层71上,第一有源层21和第二有源层31均设置在缓冲层72上,即第一有源层21和第二有源层31均设置在缓冲层72远离衬底基板10的一侧;第一栅绝缘层22设置在第一有源层21和第二有源层31上,而第一栅极23和第二栅极33设置在第一栅绝缘层22上;第三有源层42设置在第二栅绝缘层71上,第三源漏电极也设置在第二栅绝缘层71上,且第三源漏电极部分覆盖第三有源层42;层间介质层24覆盖缓冲层72、第一有源层21、第二有源层31、第一栅绝缘层22、第一栅极23、第二栅极33、第三源漏电极、第三有源层42和第二栅绝缘层71;第一源漏电极和第二源漏电极设置在层间介质层24上。

68.值得注意的是,第三有源层42在衬底基板10上的正投影与缓冲层72在衬底基板10上的正投影不存在重合区域,即缓冲层72仅位于复位晶体管20和读取晶体管30所在的区域,放大晶体管40所在的区域处的缓冲层材料被刻蚀掉,因此,放大晶体管40仅包括层叠设置的第三栅极41、第二栅绝缘层71、第三有源层42和第三源漏电极。

69.缓冲层72是包括氮化硅和氧化硅的叠层结构,其具有保温作用。在实际制作过程中,复位晶体管20的第一有源层21、读取晶体管30的第二有源层31和放大晶体管40的第三有源层42对应的膜层是同时沉积的,即在通过构图工艺形成缓冲层72之后,沉积一层非晶硅薄膜,该非晶硅薄膜位于复位晶体管20、读取晶体管30和放大晶体管40所在的区域;对该非晶硅薄膜进行图案化处理,形成第一有源层21、第二有源层31和第三有源层42对应的图案;然后,将包括图案化处理后的非晶硅薄膜对应的整个驱动背板进行准分子激光退火处理,由于复位晶体管20和读取晶体管30所在的区域具有缓冲层72,缓冲层72可保持复位晶体管20和读取晶体管30所在的区域处的非晶硅处于较高的温度,从而使得复位晶体管20和读取晶体管30所在的区域处的非晶硅可以完成晶化过程,从非晶硅变为多晶硅,而放大晶体管40所在的位置处不具有缓冲层72,则放大晶体管40所在的位置处的非晶硅无法长期处于高温环境下,因此,放大晶体管40所在的位置处的非晶硅无法完成晶化过程,放大晶体管40所在的位置处的非晶硅没有晶化,依旧为非晶硅。

70.因此,通过在复位晶体管20和读取晶体管30所在的区域处设置缓冲层72,在简化工艺步骤的同时,可使得第一有源层21、第二有源层31的材料为多晶硅,而第三有源层42为非晶硅。需要说明的是,此时的第三有源层42指的是第三有源层42中的第一无掺杂非晶硅层421。

71.如图1和图2所示,第三有源层42的材料为非晶硅,第三有源层42包括设置在第二栅绝缘层71上的第一无掺杂非晶硅层421,以及设置在第一无掺杂非晶硅层421上的第一掺杂非晶硅层422。

72.具体的,第一掺杂非晶硅层422位于第一无掺杂非晶硅层421上的部分区域,在第

一无掺杂非晶硅层421的沟道区,第一掺杂非晶硅层422是被刻蚀掉的,而第三源漏电极实际覆盖的是第三有源层42中的第一掺杂非晶硅层422。

73.其中,第一无掺杂非晶硅层421的材料为非晶硅,其不掺杂有任何离子;而第一掺杂非晶硅层422的材料也为非晶硅,其掺杂有n型离子,如磷离子等。

74.第三有源层42也就是放大晶体管40的有源层,当放大晶体管40中的第三有源层42的材料为非晶硅时,在第一有源层21和第二有源层31的激光退火工艺中,第三有源层42中的第一无掺杂非晶硅层421没有被晶化,后续形成第一掺杂非晶硅层422时也不涉及激光退火工艺,因此,也就不涉及放大晶体管40中的第三有源层42的结晶度,则各个放大晶体管40的载流子迁移率较为均匀,从而提高驱动背板的各个放大晶体管40的增益均匀性。

75.第三有源层42的材料为氧化物半导体,该氧化物半导体具体可以为igzo(indium gallium zinc oxide,铟镓锌氧化物)、itgo(indium tin gallium oxide,铟镓锡氧化物)或其他材料。当放大晶体管40中的第三有源层42的材料为氧化物半导体,其也不需要采用激光退火工艺进行晶化处理,也就不涉及放大晶体管40中的第三有源层42的结晶度,则各个放大晶体管40的载流子迁移率较为均匀,从而提高驱动背板的各个放大晶体管40的增益均匀性。

76.进一步的,如图1和图2所示,驱动背板还包括设置在衬底基板10上的遮光层73,且遮光层73和第三栅极41同层设置;第二栅绝缘层71覆盖遮光层73。

77.在衬底基板10上设置遮光层73,该遮光层73位于复位晶体管20和读取晶体管30的沟道区,通过遮光层73的设置,对复位晶体管20和读取晶体管30的沟道区进行遮光,可避免外部环境光由衬底基板10照射到复位晶体管20和读取晶体管30的沟道区,而影响复位晶体管20和读取晶体管30的性能。

78.在本发明实施例中,如图1和图2所示,驱动背板还包括覆盖层间介质层24、第一源漏电极和第二源漏电极的第一钝化层74,以及设置在第一钝化层71上的第一平坦层75。其中,第一钝化层74的材料可以为氮化硅和/或氧化硅,第一平坦层75的材料为树脂。

79.并且,驱动背板还具有贯穿第一平坦层75、第一钝化层74、层间介质层24和第二栅绝缘层71的第七过孔751,以及贯穿第一平坦层75和第一钝化层74的第八过孔752,该第七过孔751用于将放大晶体管40的第三栅极41与光敏器件的第一光敏电极(即下电极)连接,该第八过孔752用于将复位晶体管20的第一源漏电极中的第一源极251与光敏器件的第一光敏电极(即下电极)连接,从而通过第一光敏电极可使得放大晶体管40的第三栅极41与复位晶体管20的第一源漏电极中的第一源极251连接。

80.在本发明另一种可选的实施方式中,如图3至图6所示,驱动背板还包括覆盖层间介质层24、第一源漏电极和第二源漏电极的第二钝化层76;放大晶体管40包括依次设置在层间介质层24上的第四栅极44、第二钝化层76、第四有源层45和第四源漏电极;第四源漏电极包括同层设置的第四源极461和第四漏极462;其中,第四栅极44与第一源漏电极和第二源漏电极均同层设置,且第四栅极44与第一源漏电极中的第一源极251连接;第四源漏电极中的第四漏极462通过贯穿第二钝化层76的第六过孔与第二源漏电极中的第二源极351连接。

81.具体的,第一有源层21和第二有源层31均直接设置在衬底基板10上,第一栅绝缘层22设置在第一有源层21和第二有源层31上,而第一栅极23和第二栅极33设置在第一栅绝

缘层22上;层间介质层24覆盖第一有源层21、第二有源层31、第一栅绝缘层22、第一栅极23、第二栅极33和衬底基板10,第一源漏电极、第二源漏电极和第四栅极44均设置在层间介质层24上;第二钝化层76覆盖层间介质层24、第一源漏电极、第二源漏电极和第四栅极44,第四有源层45设置在第二钝化层76上,第四源漏电极也设置在第二钝化层76上,且第四源漏电极部分覆盖第四有源层45。

82.如图3和图4所示,第四有源层45的材料为非晶硅,第四有源层45包括设置在第二钝化层76上的第二无掺杂非晶硅层451,以及设置在第二无掺杂非晶硅层451上的第二掺杂非晶硅层452。

83.具体的,第二掺杂非晶硅层452位于第二无掺杂非晶硅层451上的部分区域,在第二无掺杂非晶硅层451的沟道区,第二掺杂非晶硅层452是被刻蚀掉的,而第四源漏电极实际覆盖的是第四有源层45中的第二掺杂非晶硅层452。

84.其中,第二无掺杂非晶硅层451的材料为非晶硅,其不掺杂有任何离子;而第二掺杂非晶硅层452的材料也为非晶硅,其掺杂有n型离子。

85.第四有源层45也就是放大晶体管40的有源层,当放大晶体管40中的第四有源层45的材料为非晶硅时,第二无掺杂非晶硅层451和第二掺杂非晶硅层452仅需要通过薄膜沉积工艺和构图工艺即可形成,其无需采用激光退火工艺进行晶化处理,也就不涉及放大晶体管40中的第四有源层45的结晶度,则各个放大晶体管40的载流子迁移率较为均匀,从而提高驱动背板的各个放大晶体管40的增益均匀性。

86.需要说明的是,当第四有源层45的材料为非晶硅,第四有源层45也可以仅包括一层非晶硅层,在沟道区未掺杂有任何离子,而在非沟道区掺杂有n型离子。

87.如图5和图6所示,第四有源层45的材料为氧化物半导体,该氧化物半导体可以为igzo、itgo或其他材料。当放大晶体管40中的第四有源层45的材料为氧化物半导体时,第四有源层45仅包括一层氧化物半导体层,氧化物半导体层仅需要通过薄膜沉积工艺和构图工艺即可形成,其无需采用激光退火工艺进行晶化处理,也就不涉及放大晶体管40中的第四有源层45的结晶度,则各个放大晶体管40的载流子迁移率较为均匀,从而提高驱动背板的各个放大晶体管40的增益均匀性。

88.需要说明的是,当第四有源层45的材料为非晶硅时,第二钝化层76的材料可以为氮化硅或氧化硅,由于氮化硅的介电常数大于氧化硅的介电常数,因此,第二钝化层76的材料优选为氮化硅,其厚度可以为300nm至500nm;当第四有源层45的材料为氧化物半导体时,第二钝化层76的材料为氧化硅,其厚度为100nm至200nm。

89.在本发明实施例中,如图3至图6所示,驱动背板还包括覆盖第二钝化层76、第四有源层45和第四源漏电极的第二平坦层77。第二平坦层77的材料为树脂。

90.并且,驱动背板还具有贯穿第二平坦层77和第二钝化层76的第九过孔771,该第九过孔771用于将放大晶体管40的第四栅极44和复位晶体管20的第一源极251与光敏器件的第一光敏电极(即下电极)连接。

91.在本发明实施例中,存储电容50包括相对设置第一极板51和第二极板52,第一极板51与第一源漏电极同层设置,第二极板52与第四源漏电极或第三源漏电极同层设置,且第一极板51与第一源漏电极中的第一源极251连接;其中,第一极板51在衬底基板10上的正投影与第二极板52在衬底基板10上的正投影至少部分重合。

92.如图2所示,第一极板51与第一源漏电极同层设置,第二极板52与第三源漏电极同层设置,通过将第一极板51在衬底基板10上的正投影与第二极板52在衬底基板10上的正投影设置成至少部分重合,可使得第一极板51和第二极板52形成存储电容50,此时,层间介质层24作为第一极板51与第二极板52之间的绝缘介质层。

93.通过图1和图2所示的膜层关系,可以得到如图7所示的等效电路图,可以看出,读取晶体管30中的第二源极351与放大晶体管40中的第三漏极432连接,存储电容50的第一极板51与复位晶体管20中的第一源极251连接;并且,由于后续在第一平坦层75上形成的光敏器件的第一光敏电极,分别与放大晶体管40的第三栅极41和复位晶体管20的第一源极251连接,因此,光敏器件60的第一光敏电极、放大晶体管40的第三栅极41、复位晶体管20的第一源极251和存储电容50的第一极板51均相互连接。

94.如图4和图6所示,第一极板51与第一源漏电极同层设置,第二极板52与第四源漏电极同层设置,通过将第一极板51在衬底基板10上的正投影与第二极板52在衬底基板10上的正投影设置成至少部分重合,可使得第一极板51和第二极板52形成存储电容50,此时,第二钝化层76作为第一极板51与第二极板52之间的绝缘介质层。

95.通过图3和图4所示的膜层关系,或者图5和图6所示的膜层关系,均可以得到如图7所示的等效电路图,可以看出,读取晶体管30中的第二源极351与放大晶体管40中的第四漏极462连接,存储电容50的第一极板51、放大晶体管40的第四栅极44和复位晶体管20的第一源极251均相互连接;并且,由于后续在第二平坦层77上形成的光敏器件的第一光敏电极,分别与复位晶体管20的第一源极251和放大晶体管40的第四栅极44连接,因此,光敏器件60的第一光敏电极、放大晶体管40的第四栅极44、复位晶体管20的第一源极251和存储电容50的第一极板51均相互连接。

96.此外,在图7中,存储电容50的第二极板52与第一电源信号线v0连接,第一电源信号线v0用于向存储电容50的第二极板52提供恒定的电压,并且,第一电源信号线v0与第二极板52同层设置;复位晶体管20的第一栅极23与复位信号线reset连接,复位晶体管20的第一漏极252与初始化信号线vinit连接,并且,复位晶体管20的第一栅极23与复位信号线reset同层设置,复位晶体管20的第一漏极252与初始化信号线vinit也同层设置;读取晶体管30的第二栅极33与栅极gate连接,读取晶体管30的第二漏极352与读取信号线read连接,读取晶体管30的第二栅极33与栅极gate同层设置,读取晶体管30的第二漏极352与读取信号线read也同层设置;放大晶体管40的第三源极431或第四源极461与第二电源信号线vdd连接,第二电源信号线vdd用于向放大晶体管40的第三源极431或第四源极461提供固定的高电平信号,并且,第二电源信号线vdd与放大晶体管40的第三源极431或放大晶体管40的第四源极461同层设置。

97.进一步的,驱动背板包括m行n列个驱动模块,此时,驱动背板包括m条栅线gate和n条读取信号线read,且栅线gate沿驱动背板的行方向分布,读取信号线read沿驱动背板的列方向分布,位于同一行的驱动模块中的读取晶体管30的第二栅极33与同一条栅极gate连接,位于同一列的驱动模块中的读取晶体管30的第二漏极352与同一条读取信号线read连接,m和n均为大于1的正整数。

98.需要说明的是,上述仅给出了存储电容50对应的两种设置位置,当然,本发明实施例中的存储电容50的具体设置位置不局限于上述两种位置,在任意一层或多层绝缘介质层

两侧分别设置第一极板51和第二极板52均可,例如,也可以将设置在第二平坦层77上的第一光敏电极作为第一极板51,第二极板52与第四源漏电极同层设置第二钝化层76上,此时,第二平坦层77作为第一极板51与第二极板52之间的绝缘介质层。

99.在本发明实施例中,通过在驱动背板中设置多个放大晶体管,并采用非晶硅或氧化物半导体作为放大晶体管中有源层的材料,使得驱动背板中的各个放大晶体管中的载流子迁移率较为均匀,因此,可提高驱动背板中的各个放大晶体管的增益均匀性,避免放大晶体管放大后的电信号的强度不均匀而产生的图像噪声甚至坏点和坏线,从而可提高根据放大后的信号线生成的图像的成像质量。

100.实施例二

101.参照图8,示出了本发明实施例的一种驱动背板的制作方法的流程图,具体可以包括如下步骤:

102.步骤801,提供一衬底基板。

103.在本发明实施例中,在制作驱动背板时,首先提供一衬底基板10,该衬底基板10可以为玻璃基板。

104.步骤802,在所述衬底基板上形成多个驱动模块;每个所述驱动模块包括复位晶体管、读取晶体管、放大晶体管和存储电容。

105.在本发明实施例中,在衬底基板10上形成多个驱动模块,每个驱动模块均包括复位晶体管20、读取晶体管30、放大晶体管40和存储电容50,也就是说,在衬底基板10上分别形成多个复位晶体管20、多个读取晶体管30、多个放大晶体管40和多个存储电容50。

106.其中,复位晶体管20与存储电容50连接,被配置为对存储电容50进行复位;存储电容50与光敏器件连接,被配置为存储光敏器件生成的电信号;放大晶体管40与存储电容50连接,被配置为对存储电容50中存储的电信号进行放大处理;读取晶体管30与放大晶体管40连接,被配置为读取放大晶体管40放大后的电信号;其中,放大晶体管40中的有源层的材料为非晶硅或氧化物半导体。

107.在本发明一种可选的实施方式中,步骤802具体包括子步骤s8021至子步骤s8029:

108.子步骤s8021,在所述衬底基板上形成第三栅极;

109.子步骤s8022,形成覆盖所述第三栅极的第二栅绝缘层;

110.子步骤s8023,在所述第二栅绝缘层上形成缓冲层;

111.子步骤s8024,在所述缓冲层上形成第一有源层和第二有源层,并在所述第二栅绝缘层上形成第三有源层;

112.子步骤s8025,在所述第一有源层和所述第二有源层上形成第一栅绝缘层;

113.子步骤s8026,在所述第一栅绝缘层上形成第一栅极和第二栅极;

114.子步骤s8027,在所述第二栅绝缘层上形成第二极板以及部分覆盖所述第三有源层的第三源漏电极;

115.子步骤s8028,形成层间介质层;所述层间介质层覆盖所述缓冲层、所述第一有源层、所述第二有源层、所述第一栅绝缘层、所述第一栅极、所述第二栅极、所述第三有源层、所述第三源漏电极、所述第二极板和第二栅绝缘层;

116.子步骤s8029,在所述层间介质层上形成第一源漏电极、第二源漏电极和第一极板;其中,所述第一极板与所述第一源漏电极中的第一源极连接;所述第二源漏电极中的第

二源极通过贯穿所述层间介质层的第五过孔与所述第三源漏电极中的第三漏极连接。

117.首先,在衬底基板10上通过构图工艺形成第三栅极41,然后,形成覆盖第三栅极41和衬底基板10的第二栅绝缘层71,在第二栅绝缘层71上再通过构图工艺形成缓冲层72,使得缓冲层72仅位于复位晶体管20和读取晶体管30所在的区域,放大晶体管40所在的区域处的缓冲层材料被刻蚀掉;接着,沉积一层非晶硅薄膜,该非晶硅薄膜位于复位晶体管20、读取晶体管30和放大晶体管40所在的区域,对该非晶硅薄膜进行图案化处理,以在缓冲层72上形成第一有源层21和第二有源层31,并在第二栅绝缘层71上形成第三有源层42,将形成第一有源层21、第二有源层31和第三有源层42的整个驱动背板进行准分子激光退火处理,使得复位晶体管20的第一有源层21和读取晶体管30的第二有源层31从非晶硅变为多晶硅,而放大晶体管40的第三有源层42依旧为非晶硅。需要说明的是,此时形成的第三有源层42指的是第三有源层42中的第一无掺杂非晶硅层421。

118.在形成第一有源层21、第二有源层31和第三有源层42之后,在第一有源层21和第二有源层31上通过构图工艺形成第一栅绝缘层22,接着,在第一栅绝缘层22上通过构图工艺形成第一栅极23和第二栅极33,并采用自对准工艺对第一有源层21和第二有源层31中的掺杂区进行离子注入。

119.接着,在第三有源层42中的第一无掺杂非晶硅层421上采用构图工艺形成第一掺杂非晶硅层422;然后采用构图工艺在第二栅绝缘层71上形成第二极板52以及部分覆盖第三有源层42的第三源漏电极。

120.然后,形成层间介质层24,该层间介质层24覆盖缓冲层72、第一有源层21、第二有源层31、第一栅绝缘层22、第一栅极23、第二栅极33、第三源漏电极、第三有源层42、第二极板52和第二栅绝缘层71,并形成贯穿层间介质层24的第一过孔、第二过孔、第三过孔、第四过孔和第五过孔。

121.最后,在层间介质层24上通过构图工艺形成第一源漏电极、第二源漏电极和第一极板51。第一源漏电极中的第一源极251通过贯穿层间介质层24的第一过孔与第一有源层21连接,第一源漏电极中的第一漏极252通过贯穿层间介质层24的第二过孔与第一有源层21连接;第二源漏电极中的第二源极351通过贯穿层间介质层24的第三过孔与第二有源层31连接,第二源漏电极中的第二漏极352通过贯穿层间介质层24的第四过孔与第二有源层31连接;第二源漏电极中的第二源极351通过贯穿层间介质层24的第五过孔与第三源漏电极中的第三漏极432连接;并且,第一极板51与第一源漏电极中的第一源极251连接。

122.进一步的,在层间介质层24上形成第一源漏电极、第二源漏电极和第一极板51之后,还需要形成覆盖层间介质层24、第一源漏电极、第二源漏电极和第一极板51的第一钝化层74,然后,在第一钝化层74上形成第一平坦层75。此外,还需要对第一平坦层75进行曝光、显影,使得部分区域的第一平坦层75被去除,从而露出第一钝化层74,对露出的第一钝化层74进行刻蚀,从而形成贯穿第一平坦层75和第一钝化层74的第八过孔752,并对露出的第一钝化层74以及第一钝化层74下面的层间介质层24和第二栅绝缘层71进行刻蚀,从而形成贯穿第一平坦层75、第一钝化层74、层间介质层24和第二栅绝缘层71的第七过孔751。

123.当然,在衬底基板10上通过构图工艺形成第三栅极41时,还可以同时在衬底基板10上形成遮光层73,该遮光层73和第三栅极41采用同一构图工艺同时形成。

124.需要说明的是,上述仅给出了第三有源层42的材料为非晶硅时的具体制作工艺,

当第三有源层42的材料为氧化物半导体时,其采用单独的一道构图工艺形成,可以是第一栅极23和第二栅极33形成之后去制作第三有源层42,也可以是在第一栅极23和第二栅极33形成之前去制作第三有源层42,本发明实施例对此不做限制。

125.在本发明另一种可选的实施方式中,步骤802具体包括子步骤s8031至子步骤s8038:

126.子步骤s8031,在所述衬底基板上形成第一有源层和第二有源层;

127.子步骤s8032,在所述第一有源层和所述第二有源层上形成第一栅绝缘层;

128.子步骤s8033,在所述第一栅绝缘层上形成第一栅极和第二栅极;

129.子步骤s8034,形成层间介质层;所述层间介质层覆盖所述第一有源层、所述第二有源层、所述第一栅绝缘层、所述第一栅极、所述第二栅极和所述衬底基板;

130.子步骤s8035,在所述层间介质层上形成第一源漏电极、第二源漏电极、第四栅极和第一极板;

131.子步骤s8036,形成第二钝化层;所述第二钝化层覆盖所述层间介质层、所述第一源漏电极、所述第二源漏电极、所述第四栅极和所述第一极板;

132.子步骤s8037,在所述第二钝化层上形成第四有源层;

133.子步骤s8038,在所述第二钝化层上形成第二极板以及部分覆盖所述第四有源层的第四源漏电极;其中,所述第四栅极与所述第一源漏电极中的第一源极连接;所述第四源漏电极中的第四漏极通过贯穿所述第二钝化层的第六过孔与所述第二源漏电极中的第二源极连接;所述第一极板与所述第一源漏电极中的第一源极连接。

134.首先,衬底基板10上通过构图工艺形成第一有源层21和第二有源层31,并对第一有源层21和第二有源层31进行准分子激光退火处理,使得第一有源层21和第二有源层31从非晶硅变为多晶硅;然后,在第一有源层21和第二有源层31上通过构图工艺形成第一栅绝缘层22,在第一栅绝缘层22上通过构图工艺形成第一栅极23和第二栅极33,并采用自对准工艺对第一有源层21和第二有源层31中的掺杂区进行离子注入;接着,形成层间介质层24,该层间介质层24覆盖第一有源层21、第二有源层31、第一栅绝缘层22、第一栅极23、第二栅极33和衬底基板10,并形成贯穿层间介质层24的第一过孔、第二过孔、第三过孔和第四过孔。

135.然后,在层间介质层24上通过构图工艺形成第一源漏电极、第二源漏电极、第四栅极44和第一极板51;第一源漏电极中的第一源极251通过贯穿层间介质层24的第一过孔与第一有源层21连接,第一源漏电极中的第一漏极252通过贯穿层间介质层24的第二过孔与第一有源层21连接;第二源漏电极中的第二源极351通过贯穿层间介质层24的第三过孔与第二有源层31连接,第二源漏电极中的第二漏极352通过贯穿层间介质层24的第四过孔与第二有源层31连接。并且,第四栅极44、第一极板51与第一源漏电极中的第一源极251均相互连接。

136.接着,形成第二钝化层76,该第二钝化层76覆盖层间介质层24、第一源漏电极、第二源漏电极、第四栅极44和第一极板51。

137.在形成第二钝化层76之后,在第二钝化层76上通过构图工艺形成第四有源层45,第四有源层45的材料为非晶硅或氧化物半导体,当第四有源层45的材料为非晶硅时,其可以采用一次构图工艺形成一层非晶硅层,然后对非晶硅层进行离子注入,也可以采用两次

构图工艺分别形成第二无掺杂非晶硅层451和第二掺杂非晶硅层452。

138.然后,形成贯穿第二钝化层76的第六过孔,接着在第二钝化层76上通过构图工艺形成第二极板52以及部分覆盖第四有源层45的第四源漏电极,使得第四源漏电极通过贯穿第二钝化层76的第六过孔与第二源漏电极中的第二源极351连接。

139.进一步的,在第二钝化层76上形成第二极板52以及部分覆盖第四有源层45的第四源漏电极之后,还需要形成覆盖第二钝化层76、第四有源层45和第四源漏电极的第二平坦层77,并形成贯穿第二平坦层77和第二钝化层76的第九过孔771。

140.在本发明实施例中,通过在驱动背板中设置多个放大晶体管,并采用非晶硅或氧化物半导体作为放大晶体管中有源层的材料,使得驱动背板中的各个放大晶体管中的载流子迁移率较为均匀,因此,可提高驱动背板中的各个放大晶体管的增益均匀性,避免放大晶体管放大后的电信号的强度不均匀而产生的图像噪声甚至坏点和坏线,从而可提高根据放大后的信号线生成的图像的成像质量。

141.实施例三

142.参照图9,示出了图1所示的驱动背板对应的探测基板的剖面图,图10示出了图2所示的驱动背板对应的探测基板的剖面图,图11示出了图3所示的驱动背板对应的探测基板的剖面图,图12示出了图4所示的驱动背板对应的探测基板的剖面图。

143.本发明实施例提供了一种探测基板,包括光敏器件60以及上述的驱动背板,光敏器件60与驱动背板连接。具体的,光敏器件60是与驱动背板中的复位晶体管20、放大晶体管40和存储电容50连接。

144.在本发明实施例中,光敏器件60包括第一光敏电极61、第二光敏电极63和设置在第一光敏电极61和第二光敏电极63之间的光敏层62。

145.如图9和图10所示,第一光敏电极61通过贯穿第一平坦层75、第一钝化层74、层间介质层24和第二栅绝缘层71的第七过孔751与第三栅极41连接,第一光敏电极61还通过贯穿第一平坦层75和第一钝化层74的第八过孔752与第一源漏电极中的第一源极251连接。此时,第一光敏电极61设置在第一平坦层75远离衬底基板10的一侧。

146.如图11和图12所示,第一光敏电极61通过贯穿第二平坦层77和第二钝化层76的第九过孔771与第四栅极44连接。此时,第一光敏电极61设置在第二平坦层77远离衬底基板10的一侧。

147.其中,第一光敏电极61作为光敏器件60的下电极,第二光敏电极63作为光敏器件60的上电极,为了保证射线可以正常通过第二光敏电极63入射至光敏层62上,需要采用透明导电材料制作第二光敏电极63,即第二光敏电极63的材料为透明导电材料,如ito(indium tin oxides,氧化铟锡)等。

148.在本发明一种可选的实施方式中,光敏层62的材料为直接转化材料,如有机材料、钙钛矿、碘化汞、碘化铅、氧化铅、碘化铋或cd

1-x

zn

x

te(碲锌镉)等,其可以直接将x射线、γ射线或其他射线转换为电信号。此时,在第二光敏电极63远离光敏层62的一侧还设置有第三钝化层81。

149.在本发明另一种可选的实施例方式中,探测基板还包括依次设置在第二光敏电极63远离光敏层62一侧的第三钝化层81和闪烁体层82;光敏层62包括依次设置在第一光敏电极61远离驱动背板一侧的第一掺杂层621、本征层622和第二掺杂层623。

150.此时,光敏层62实际上为光电二极管,其无法直接将x射线、γ射线或其他射线转换为电信号,只能将可见光转换为电信号,因此,需要增加一层闪烁体层82,x射线、γ射线或其他射线经过闪烁体层82转换为可见光,可见光再经过第三钝化层81和第二光敏电极63照射到光敏层62上,从而通过光敏层62将可见光转换为电信号。

151.其中,第一掺杂层621可以为p型层,本征层622可以为i型层,第二掺杂层623可以为n型层;或者,第一掺杂层621可以为n型层,本征层622可以为i型层,第二掺杂层623可以为i型层。并且,i型层的材料为钙钛矿,p型层和n型层的材料为有机或无机材料;或者,p型层、i型层和n型层的材料均为有机材料。

152.需要说明的是,图9和图10示出了的是光敏层62为直接转换材料的结构,即直接转换型的光敏层62,图11和图12示出的是光敏层62是光电二极管的结构,即间接转换型的光敏层62,这两种光敏层62均可设置在图1至图6中的任意一种驱动背板上,不局限于是在图1和图2所示的驱动背板上设置直接转换型的光敏层62,而在图3和图4所示的驱动背板上设置间接转换型的光敏层62。

153.如图9至图12所示,光敏器件60在衬底基板10上的正投影,覆盖复位晶体管20、读取晶体管30、放大晶体管40和存储电容50在衬底基板10上的正投影。即在整个驱动背板上均设置光敏器件60,光敏器件60占整个探测基板的面积基本上可达到100%,从而提高探测基板的填充因子,避免驱动背板中的复位晶体管20、读取晶体管30、放大晶体管40和存储电容50过多的占用光敏面积,提高光电转换效率。

154.或者,光敏器件60在衬底基板10上的正投影,与复位晶体管20、读取晶体管30、放大晶体管40和存储电容50在衬底基板10上的正投影不存在重合区域。

155.此时,探测基板的面积为复位晶体管20、读取晶体管30、放大晶体管40和存储电容50的面积,与光敏器件60的面积之和,并且,光敏器件60的面积占探测基板的面积为60%至70%。

156.本发明实施例还提供了一种探测装置,包括上述的探测基板,该探测装置可以是fpd(flat panel detector,平板探测器)。

157.在本发明实施例中,通过在驱动背板中设置多个放大晶体管,并采用非晶硅或氧化物半导体作为放大晶体管中有源层的材料,使得驱动背板中的各个放大晶体管中的载流子迁移率较为均匀,因此,可提高驱动背板中的各个放大晶体管的增益均匀性,避免放大晶体管放大后的电信号的强度不均匀而产生的图像噪声甚至坏点和坏线,从而可提高根据放大后的信号线生成的图像的成像质量。

158.本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

159.最后,还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、商品或者设备中还存在另外的相同要素。

160.以上对本发明所提供的一种驱动背板及其制作方法、探测基板及探测装置,进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1