存储器装置的制作方法

1.本发明属于存储技术领域,涉及一种存储器装置。

背景技术:

2.近年来,半导体装置的尺寸已逐渐缩小。在半导体技术中,特征尺寸的缩小、速度、性能、密度与每单位集成电路的成本的改进皆为相当重要的目标。

技术实现要素:

3.本发明有关于一种存储器装置,可具有优良的操作效能。

4.根据本发明的一方面,提出一种存储器装置,其包括一源极元件、一漏极元件、多个通道层、多个控制电极层与一存储层。通道层独立电性连接在源极元件与漏极元件之间。多个存储单元定义在控制电极层与通道层之间的存储层中。

5.根据本发明的另一方面,提出一种存储器装置,其包括一通道元件、多个控制电极层与一存储层。通道元件包括电性连接的多个较厚通道部与多个较薄通道部。多个存储单元定义在较厚通道部与控制电极层之间的存储层中。

6.根据本发明的又一方面,提出一种存储器装置,其包括多个控制电极层、多个通道层与一存储层。通道层在一第一方向上与控制电极层交错配置并重叠。多个存储单元定义在控制电极层与通道层之间的存储层中。

7.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附附图详细说明如下:

附图说明

8.图1a绘示一实施例的存储器装置的剖面图。

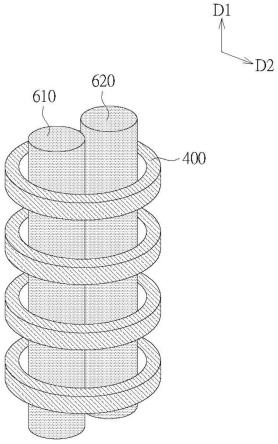

9.图1b绘示一实施例的存储器装置的立体图。

10.图1c绘示一实施例的存储器装置的剖面图。

11.图1d绘示实施例的存储器装置的源极元件、漏极元件与通道层。

12.图2a绘示一实施例的存储器装置的剖面图。

13.图2b绘示一实施例的存储器装置的立体图。

14.图2c绘示一实施例的存储器装置的剖面图。

15.图2d绘示实施例的存储器装置的源极元件、漏极元件与通道元件。

16.图3a至图9c绘示一实施例中的存储器装置的制造方法。

17.图10a至图13绘示另一实施例中的存储器装置的制造方法。

18.图14绘示比较例的存储器装置。

19.【符号说明】

20.100:控制电极层

21.110:干部电极

22.111:第一电极表面

23.120:第一支部电极

24.122:第二电极表面

25.124:第四电极表面

26.130:第二支部电极

27.133:第三电极表面

28.135:第五电极表面

29.200:绝缘层

30.300:基底

31.400:通道层

32.401:第一通道表面

33.402:第二通道表面

34.403:第三通道表面

35.404:通道表面

36.460:通道元件

37.461:较厚通道部

38.462:较薄通道部

39.470,470c:通道膜

40.471:第一通道膜部

41.4711:第一通道表面

42.472:第二通道膜部

43.4722:第二通道表面

44.500:存储层

45.510:第一存储层部

46.520:第二存储层部

47.530:第三存储层部

48.540:第四存储层部

49.571,573:氧化物层

50.572:氮化物层

51.610:源极元件

52.620:漏极元件

53.700:绝缘元件

54.810:第一材料层

55.820:开孔

56.830:凹洞

57.840:第二材料层

58.850:狭缝

59.cs,cs1,cs2,es1,es2:尺寸

60.d1:第一方向

61.d2:第二方向

具体实施方式

62.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

63.本公开的一概念中,存储器装置的通道层可在不同方向上与控制电极层重叠,因此对应于存储单元的有源通道部分可具有较大的有效通道宽度,从而提升存储器装置的操作性能。本公开的另一概念中,通道层可独立电性连接在源极元件与漏极元件之间,因此能避免操作过程中邻近存储单元之间的干扰。本公开的又一概念中,存储器装置的通道元件包括较厚通道部与较薄通道部,其中较厚通道部为对应于存储单元的有源通道部分,因此存储器装置可具有较高的存储单元电流。以下实施例以3d and存储器装置为例作说明,但本公开不限于此。

64.以下以一些实施例做说明。须注意的是,本公开并非显示出所有可能的实施例,未于本公开提出的其他实施例也可能可以应用。再者,附图上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和图示内容仅作叙述实施例之用,而非作为限缩本公开保护范围之用。另外,实施例中的叙述,例如细节结构、工艺步骤和材料应用等等,仅为举例说明之用,并非对本公开欲保护的范围做限缩。实施例的步骤和结构各自细节可在不脱离本公开的精神和范围内根据实际应用工艺的需要而加以变化与修饰。以下是以相同/类似的符号表示相同/类似的元件做说明。

65.图1a至图1d用以说明一实施例中的存储器装置。

66.请参照图1a至图1c。图1a与图1c分别为沿图1b的立体图中的aa线与cc线绘制出的剖面图。

67.控制电极层100与绝缘层200在第一方向d1(例如,垂直方向,或z方向,或基底300的上表面的法线方向)上交错配置在基底300上。控制电极层100通过绝缘层200互相分开。通道层400与绝缘层200交错配置在第一方向d1上。

68.控制电极层100包括干部电极110、第一支部电极120与第二支部电极130。干部电极110可电性连接在第一支部电极120与第二支部电极130之间。控制电极层100包括干部电极110的第一电极表面111、第一支部电极120的第二电极表面122与第二支部电极130的第三电极表面133。第一电极表面111在第二电极表面122与第三电极表面133之间。第一电极表面111为纵向电极表面或侧壁电极表面。第二电极表面122与第三电极表面133为面朝向彼此的横向电极表面。第二电极表面122为面朝向基底300的电极表面。第三电极表面133为背向基底300的电极表面。控制电极层100还包括第一支部电极120的第四电极表面124与第二支部电极130的第五电极表面135。第一支部电极120的第二电极表面122在干部电极110的第一电极表面111与第一支部电极120的第四电极表面124之间。第二支部电极130的第三电极表面133在干部电极110的第一电极表面111与第二支部电极130的第五电极表面135之间。实施例中,控制电极层100可用作字线。

69.控制电极层100的支部电极(包括第一支部电极120与第二支部电极130)与通道层400是在第一方向d1上交错配置。通道层400重叠在控制电极层100的第一支部电极120与第二支部电极130之间。控制电极层100的干部电极110可与通道层400在第二方向d2上重叠。

通道层400在干部电极110的第一电极表面111、第一支部电极120的第二电极表面122与第二支部电极130的第三电极表面133之间。第二方向d2可为实质上垂直于第一方向d1的横方向,例如水平方向、x方向、y方向、或在x-y平面上的任意横方向。

70.通道层400包括第一通道表面401、第二通道表面402与第三通道表面403。第一通道表面401在第二通道表面402与第三通道表面403之间。第一通道表面401为纵向通道表面或侧壁通道表面。第二通道表面402与第三通道表面403为背朝向彼此的横向通道表面。第二通道表面402为背向基底300的通道表面。第三通道表面403为面朝向基底300的通道表面。

71.第一通道表面401与第一电极表面111面朝向彼此,并在第二方向d2上重叠。第二通道表面402与第二电极表面122面朝向彼此,并在第一方向d1上重叠。第三通道表面403与第三电极表面133面朝向彼此,并在第一方向d1上重叠。

72.此实施例中,通道层400在第一方向d1上的尺寸cs是小于控制电极层100的干部电极110在第一方向d1上的尺寸es1,也小于干部电极110的第一电极表面111在第一方向d1上的尺寸es2。

73.存储层500可包括第一存储层部510、第二存储层部520与第三存储层部530。第一存储层部510在第二存储层部520与第三存储层部530之间。第一存储层部510可在通道层400的第一通道表面401与控制电极层100的第一电极表面111之间。第二存储层部520可在通道层400的第二通道表面402与控制电极层100的第二电极表面122之间。第三存储层部530可在通道层400的第三通道表面403与控制电极层100的第三电极表面133之间。存储层500可还包括第四存储层部540。第四存储层部540连接在第二存储层部520与第三存储层部530之间。第四存储层部540在第一支部电极120的第四电极表面124上,并在第二支部电极130的第五电极表面135上。通道层400在第一方向上d1通过存储层500的第二存储层部520、第三存储层部530与第四存储层部540彼此分开。

74.通道层400与存储层500之间具有第一界面。此实施例中,第一界面包括第一通道表面401、第二通道表面402与第三通道表面403。第一界面为含有第一通道表面401、第二通道表面402与第三通道表面403的具有夹角(例如90度、锐角或钝角)的弯折面。控制电极层100与存储层500之间具有第二界面。此实施例中,第二界面包括第一电极表面111、第二电极表面122、第三电极表面133、第四电极表面124与第五电极表面135。第二界面可为含有第一电极表面111、第二电极表面122、第三电极表面133、第四电极表面124与第五电极表面135的具有夹角(例如90度、锐角度或钝角度)的弯折面。此实施例中,第一界面与第二界面包括相似或相同弯折轮廓的弯折面。存储单元可定义在存储层500在第一界面与第二界面之间的第一存储层部510、第二存储层部520与第三存储层部530中。

75.请参照图1b至图1d。图1d仅绘示源极元件610、漏极元件620与通道层400。源极元件610与漏极元件620可通过绝缘元件700(图1a至图1c)彼此分开。源极元件610与漏极元件620可为延伸在第一方向d1上的电极柱。通道层400可配置在源极元件610、漏极元件620与绝缘元件700的外侧。通道层400电性连接在源极元件610与漏极元件620之间。详细来说,此实施例中,互相分开的通道层400是独立电性连接在源极元件610与漏极元件620之间。

76.图14绘示一比较例的存储器装置,其具有通道膜470c延伸在第一方向d1上,并只在第二方向d2上与控制电极层100重叠。相较于比较例的存储器装置,参照图1a至第1d所述

的实施例的存储器装置可具有至少以下优势。实施例中,通道层400与控制电极层100重叠在实质上互相垂直的第一方向d1与第二方向d2上,因此对应于存储单元的通道层400可具较大的有效通道宽度,从而存储器装置能具有较佳的操作效能,例如具有较快的编程速率。实施例的存储器装置可具有更大的增量型脉冲编程(ispp)斜率与编程窗口(pgm window)。实施例中,通道层400是独立电性连接在源极元件610与漏极元件620之间,因此能避免操作过程中邻近存储单元之间的干扰。而图14的比较例的存储器装置中,通道膜470c在控制电极层100之间的部分可能在存储单元操作过程中造成漏电流路径而造成干扰。

77.图2a至图2d用以说明另一实施例中的存储器装置。

78.请参照图2a与图2c,其分别为沿图2b的立体图中的aa线与cc线绘制出的剖面图。控制电极层100包括第一电极表面111、第二电极表面122与第三电极表面133。第一电极表面111在相对的第二电极表面122与第三电极表面133之间。第一电极表面111可为纵向电极表面或侧壁电极表面。第一电极表面111可为弯曲面。第二电极表面122与第三电极表面133为彼此背对的横向电极表面。第二电极表面122为背向基底300的电极表面。第三电极表面133为面朝向基底300的电极表面。

79.控制电极层100包括干部电极110、第一支部电极120与第二支部电极130。干部电极110可电性连接在第一支部电极120与第二支部电极130之间。控制电极层100的第一电极表面111包括干部电极110、第一支部电极120与第二支部电极130的电极表面。

80.通道元件460包括通道膜470以及通道层400。

81.通道膜470可包括第一通道膜部471与第二通道膜部472。第一通道膜部471具有第一通道表面4711。第二通道膜部472具有第二通道表面4722。通道层400可在第一通道膜部471的第一通道表面4711上。绝缘层200可在第二通道膜部472的第二通道表面4722上。通道层400在第一方向d1上互相分开,并可经由邻接的第一通道膜部471与连接在第一通道膜部471之间的第二通道膜部472彼此电性连接。

82.通道层400可利用沉积方式形成。一实施例中,通道层400是以外延的方式从第一通道膜部471的第一通道表面4711生长形成。一实施例中,通道层400可具有类似透镜形状的结构。通道层400在第一方向d1上的尺寸是往朝向控制电极层100的第二方向d2逐渐变小。举例来说,通道层400在靠近第一通道膜部471处的部分具有最大的第一方向d1的尺寸。通道层400在远离第一通道膜部471处的部分具有最小的第一方向d1的尺寸。通道层400的通道表面404(侧壁通道表面)可为弯曲面,并朝控制电极层100的方向凸出。实施例中,通道层400并不限于如图2c所示的轮廓,而可包含由沉积方式形成在第一通道膜部471上,或以外延生长的方式从第一通道膜部471的第一通道表面4711形成的任何可能轮廓。

83.控制电极层100的支部电极(包括第一支部电极120与第二支部电极130)与通道层400可在第一方向d1上交错配置。通道层400可在第一方向d1上重叠于控制电极层100的第一支部电极120与第二支部电极130之间。控制电极层100的干部电极110可与通道层400在第二方向d2上重叠。但本公开不限于此。

84.通道元件460包括较厚通道部461与较薄通道部462。较厚通道部461包括通道层400与通道膜470的第一通道膜部471。较薄通道部462包括通道膜470的第二通道膜部472,或者,由第二通道膜部472构成。较厚通道部461在第二方向d2上的尺寸cs1是大于较薄通道部462在第二方向d2上的尺寸cs2。

85.存储层500可包括第一存储层部510、第二存储层部520与第三存储层部530。第一存储层部510在第二存储层部520与第三存储层部530之间。第一存储层部510可在通道层400的通道表面404与控制电极层100的第一电极表面111之间。第二存储层部520可在控制电极层100的第二电极表面122与绝缘层200的下绝缘表面之间。第三存储层部530可在控制电极层100的第三电极表面133与绝缘层200的上绝缘表面之间。控制电极层100在较厚通道部461的侧壁通道表面(或通道层400的通道表面404)上。绝缘层200在较薄通道部462(或第二通道膜部472)的侧壁通道表面上。

86.通道层400的通道表面404可邻接存储层500,因此通道层400与存储层500之间的第一界面可为弯曲面。控制电极层100的第一电极表面111可为轮廓与通道表面404互补的弯曲面。控制电极层100的第一电极表面111可邻接存储层500的第一存储层部510,因此控制电极层100与第一存储层部510之间的第二界面可为弯曲面。第一界面与第二界面可具有相似或相同的弯曲方向。存储单元可定义在存储层500的第一存储层部510中。

87.请参照图2a至图2d。图2d仅绘示源极元件610、漏极元件620与通道元件460。通道元件460在源极元件610与漏极元件620的外侧,并且电性连接在源极元件610与漏极元件620之间。

88.图14绘示比较例的存储器装置,其只具有通道膜470c延伸在第一方向d1上,且通道膜470c在第二方向d2上的尺寸均一(即一致厚度)。相较于比较例的存储器装置,参照图2a至第2d所描述的实施例的存储器装置可具有至少以下优势。实施例中,较厚通道部461与控制电极层100重叠在实质上互相垂直的第一方向d1与第二方向d2上,因此对应于存储单元的较厚通道部461可具较大的有效通道宽度,从而存储器装置能具有较佳的操作效能,例如具有较快的编程速率。实施例中,对应于存储单元的有源通道部分为较厚通道部461,其厚度(或在第二方向d2上的尺寸)比在控制电极层100之间的较薄通道部462(或通道膜470/470c)大,因此存储器装置可具有较高的存储单元电流。

89.图3a至图9c绘示一实施例中的存储器装置的制造方法。

90.请参照图3a与图3b,可利用沉积方式,在基底300上交错堆叠绝缘层200与第一材料层810以形成叠层结构。基底300可例如包括硅或其它半导体材料。绝缘层200的材料可不同于第一材料层810。一实施例中,绝缘层200可包括氧化物例如氧化硅,第一材料层810可包括氮化物例如氮化硅。但本公开不限于此。形成开孔820于叠层结构中。

91.请参照图4,可利用回蚀的方式,移除开孔820露出的部分第一材料层810以形成凹洞830在绝缘层200之间。

92.请参照图5,可利用沉积方式,形成第二材料层840在基底300与叠层结构上。第二材料层840可形成在凹洞830露出的第一材料层810的侧壁表面与绝缘层200的下绝缘表面及上绝缘表面上。第二材料层840可形成在开孔820露出的绝缘层200的侧壁绝缘表面与基底300的上表面上。此外,第二材料层840可形成在最顶层的绝缘层200的上表面上。第二材料层840的材料可相同于第一材料层810。一实施例中,第二材料层840可包括氮化物例如氮化硅。但本公开不限于此。

93.请参照图6,可利用刻蚀方式移除第二材料层840在开孔820中与在最顶层的绝缘层200的上表面上的部分,并留下在凹洞830中的部分。

94.请参照图7a至图7c。图7a与图7c分别为沿图7b的立体图中的aa线与cc线绘制出的

剖面图。可利用沉积方法形成存储层500在开孔820露出的基底300上与绝缘层200的侧壁绝缘表面上,并在凹洞830露出的第二材料层840上。一实施例中,存储层500可包括氧化物-氮化物-氧化物(ono)结构,例如包括氧化物层571、氮化物层572与氧化物层573。但本公开不限于此,存储层500可包括任意的电荷俘获结构,例如onono结构、ononono结构、或be-sonos结构等。举例来说,电荷俘获层可使用氮化物例如氮化硅,或是其他类似的高介电常数物质包括金属氧化物,例如三氧化二铝(al2o3)、氧化铪(hfo2)等。可利用沉积方法形成通道层400在凹洞830露出的存储层500上。通道层400可包括硅,例如多晶硅或单晶硅,或其它的半导体材料。可利用沉积方法形成绝缘元件700在开孔820中。绝缘元件700可包括氧化物例如氧化硅。但本公开不限于此。可利用沉积方法形成源极元件610与漏极元件620在绝缘元件700中。源极元件610与漏极元件620可包括硅,例如多晶硅或单晶硅,或其它的半导体材料。

95.请参照图8a至图8c。图8a与图8c分别为沿图8b的立体图中的aa线与cc线绘制出的剖面图。可利用刻蚀方法移除第一材料层810与第二材料层840以形成狭缝850在绝缘层200之间。

96.请参照图9a至图9c。图9a与图9c分别为沿图9b的立体图中的aa线与cc线绘制出的剖面图。可利用沉积方法形成控制电极层100填充狭缝850。控制电极层100可包括金属例如钨,或其它的导电材料。

97.图10a至图13绘示另一实施例中的存储器装置的制造方法。一实施例中,可在进行参照图3a与图3b所述的制造步骤之后,进行参照图10a至图10b所述的制造步骤。

98.请参照图10a至图10c。图10a与图10c分别为沿图10b的立体图中的aa线与cc线绘制出的剖面图。可形成通道膜470在开孔820露出的第一材料层810的侧壁表面与绝缘层200的侧壁绝缘表面上。通道膜470的第一通道膜部471可在第一材料层810上。通道膜470的第二通道膜部472可在绝缘层200上。通道膜470可包括硅,例如多晶硅或单晶硅等。可形成绝缘元件700在开孔820中。可形成源极元件610与漏极元件620在绝缘元件700中,并在通道膜470的侧壁通道表面上。

99.请参照图11a与图11b。图11a为沿图11b的立体图中的aa线绘制出的剖面图。可移除第一材料层810以形成狭缝850在绝缘层200之间,并露出第一通道膜部471的第一通道表面4711。

100.请参照图12a与图12b。图12a为沿图12b的立体图中的aa线绘制出的剖面图。可形成通道层400在第一通道膜部471上。通道层400可包括硅,例如多晶硅或单晶硅等。通道层400可利用沉积方式形成。一实施例中,可利用选择性外延方法,从狭缝850露出的第一通道膜部471的第一通道表面4711生长出邻接在第一通道表面4711上的通道层400。一实施例中,外延形成的通道层400具有相对端部较薄,而往中间部逐渐变厚的轮廓。实施例中,通道层400并不限于如图12a和图12b所示的轮廓,而可包含由沉积方式形成在第一通道膜部471上,或以外延生长的方式从第一通道膜部471的第一通道表面4711形成的任何可能轮廓。举例来说,通道层400的通道表面404可能为弯曲表面、平整的表面或非平整的表面。

101.请参照图13,可形成存储层500在狭缝850露出的通道层400的通道表面404与绝缘层200的上、下绝缘表面上。一实施例中,存储层500可包括氧化物-氮化物-氧化物(ono)结构,例如包括氧化物层571、氮化物层572与氧化物层573。但本公开不限于此。可形成控制电极层100在狭缝850露出的存储层500上。

102.综上所述,虽然本发明已以实施例公开如上,然其并非用以限定本发明。本发明所属技术领域中具有公知常识的技术人员,在不脱离本发明的精神和范围内,当可作各种的改动与润饰。因此,本发明的保护范围当以权利要求所界定的范围为准。

103.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1