半导体装置的制作方法

半导体装置

1.关联申请

2.本技术享受以日本专利申请2020-157832号(申请日:2020年9月18日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

3.本发明的实施方式涉及半导体装置。

背景技术:

4.mosfet(metal oxide semiconductor field effect transistor)等半导体装置被用于电力转换等用途。关于这样的半导体装置,期望的是良品率高的半导体装置。

技术实现要素:

5.本发明的实施方式提供良品率高的半导体装置。

6.实施方式的半导体装置具有第1电极和基板,上述基板具有第1电极所接触的第1面和与第1面对置的第2面,上述基板的第1面具有第2方向的长度小于第1方向的长度的第1槽,上述第1方向平行于上述第1面,上述第2方向与上述第1方向交叉且平行于上述第1面,基板具有:第1导电型的第1半导体层、设于第1半导体层与第2面之间且第1导电型的杂质浓度比第1半导体层高的第2半导体层、设于第2半导体层与第2面之间的第2导电型的第1半导体区域、设于第1半导体区域与第2面之间的第1导电型的第2半导体区域、和在从第2面到达第2半导体层且在第2方向上延伸的第1沟槽内隔着第1绝缘膜而与第1半导体区域对置地设置的第2电极。

附图说明

7.图1是第1实施方式的半导体装置的示意性的电路图。

8.图2是第1实施方式的半导体装置的示意俯视图。

9.图3是第1实施方式的半导体装置的示意剖面图。

10.图4是第1实施方式的半导体装置的主要部分的示意剖面图。

11.图5是第1实施方式的半导体装置的主要部分的示意剖面图的其他的一例。

12.图6是第1实施方式的半导体装置的主要部分的示意剖面图。

13.图7是第1实施方式的半导体装置的主要部分的示意剖面图的其他的一例。

14.图8是第1实施方式的半导体装置的主要部分的示意剖面图。

15.图9是第1实施方式的半导体装置的主要部分的示意剖面图。

16.图10是成为第1实施方式的比较方式的半导体装置的示意剖面图。

17.图11是第2实施方式的半导体装置的主要部分的示意图。

18.图12是表示第2实施方式的半导体装置的制造工序的主要部分的示意剖面图。

19.图13是第3实施方式的半导体装置的主要部分的示意图。

20.图14是第4实施方式的半导体装置的主要部分的示意图。

21.图15是第5实施方式的半导体装置的主要部分的示意图。

22.图16是第6实施方式的半导体装置的主要部分的示意图。

具体实施方式

23.以下,一边参照附图一边说明本发明的实施方式。另外,以下的说明中,对相同的部件等赋予相同的附图标记,对说明过一次的部件等适当省略其说明。

24.本说明书中,为了表示构件等的位置关系,将附图的上方向记载为“上”,将附图的下方向记载为“下”。本说明书中,“上”、“下”的概念不一定是表示与重力的朝向的关系的用语。

25.以下,以第1导电型为n型、第2导电型为p型的情况为例进行说明。

26.在以下的说明中,n

+

、n、n

-

以及p

+

、p、p

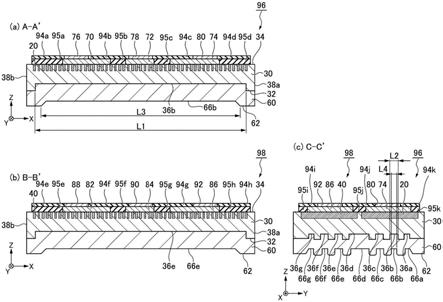

-

的标记表示各导电型中的杂质浓度的相对高低。即n

+

表示与n相比n型的杂质浓度相对较高,n

-

表示与n相比n型的杂质浓度相对较低。并且,p

+

表示与p相比p型的杂质浓度相对较高,p

-

表示与p相比p型的杂质浓度相对较低。另外,也有将n

+

型、n

-

型仅记载为n型、将p

+

型、p

-

型仅记载为p型的情况。

27.(第1实施方式)

28.本实施方式的半导体装置具有第1电极和基板,上述基板具有第1电极所接触的第1面和与第1面对置的第2面,上述基板的第1面具有第2方向的长度小于第1方向的长度的第1槽,上述第1方向平行于上述第1面,上述第2方向与上述第1方向交叉且平行于上述第1面,基板具有:第1导电型的第1半导体层、设于第1半导体层与第2面之间且第1导电型的杂质浓度比第1半导体层高的第2半导体层、设于第2半导体层与第2面之间的第2导电型的第1半导体区域、设于第1半导体区域与第2面之间的第1导电型的第2半导体区域、和在从第2面到达第2半导体层且在第2方向上延伸的第1沟槽内隔着第1绝缘膜而与第1半导体区域对置地设置的第2电极。

29.进而,本实施方式的半导体装置的基板还具备设于第2半导体层与第2面之间的第2导电型的第3半导体区域、设于第3半导体区域与第2面之间的第1导电型的第4半导体区域、在从第2面到达第2半导体层且在第2方向上延伸的第2沟槽内隔着第2绝缘膜而与第3半导体区域对置地设置的第3电极,基板具有第1区域和第2区域,上述第1区域具有第1半导体区域、第2半导体区域、和第2电极,上述第2区域在第1方向上与第1区域邻接,并具有第3半导体区域、第4半导体区域和第3电极,第1槽跨过第1区域和第2区域。

30.图1是本实施方式的半导体装置100的示意性的电路图。本实施方式的半导体装置100的电路是第1晶体管tr1的漏极与第2晶体管tr2的漏极被电连接而成的电路。例如,半导体装置100的电路是能够充放电的二次电池的用于充电以及放电的电路。例如,图1中从右向左流过的第1电流是来自二次电池的放电电流。并且,例如,图1中从左向右流过的第2电流是向二次电池的充电电流。如此,半导体装置100的电路能够流过彼此相反的朝向的第1电流和第2电流。

31.这里,考虑仅设有第1晶体管tr1而没有设置第2晶体管tr2的情况。该情况下,即使想要将第1晶体管tr1截止而停止第2电流的流动,也经由第1晶体管tr1的体二极管bd1而导致流过第2电流。

32.并且,考虑仅设有第2晶体管tr2而没有设置第1晶体管tr1的情况。该情况下,即使想要将第2晶体管tr2截止而停止第1电流的流动,也经由第2晶体管tr2的体二极管bd2而导致流过第1电流。

33.因此,在半导体装置100中将第1晶体管tr1的漏极与第2晶体管tr2的漏极电连接。通过这样的连接,体二极管bd1的阴极与体二极管bd2的阴极被电连接。这里考虑将第1晶体管tr1与第2晶体管tr2截止而停止第2电流的情况。该情况下,即使第2电流想要经由第1晶体管tr1的体二极管bd1流动,也由于体二极管bd2的阴极与体二极管bd1的阴极电连接因此不流过第2电流。并且,考虑将第1晶体管tr1与第2晶体管tr2截止而停止第1电流的情况。该情况下,即使第1电流想要经由第2晶体管tr2的体二极管bd2流动,也由于体二极管bd1的阴极与体二极管bd2的阴极电连接因此不流过第1电流。由此,在半导体装置100中能够进行第1电流以及第2电流的控制。

34.图2是本实施方式的半导体装置100的示意俯视图。图3是本实施方式的半导体装置100的示意剖面图。图4是本实施方式的半导体装置100的主要部分的示意剖面图。图5是本实施方式的半导体装置100的主要部分的示意剖面图的其他的一例。图6是本实施方式的半导体装置100的主要部分的示意剖面图。图7是本实施方式的半导体装置100的主要部分的示意剖面图的其他的一例。

35.使用图2、图3、图4、图5、图6以及图7来说明本实施方式的半导体装置100。

36.半导体装置100具备基板30。基板30具有第1面32、第2面34和侧面38。例如图3的(a)以及图3的(b)中,设有作为侧面38的、侧面38a以及侧面38b。

37.这里,定义x方向(第1方向的一例)、与x方向垂直地交叉的y方向(第2方向的一例)、与x方向以及y方向垂直地交叉的z方向(第3方向的一例)。第1面32以及第2面34是相对于与x方向以及y方向平行的xy平面而言平行地设置的面。

38.并且,半导体装置100中设有第1区域96以及第2区域98(图2)。第1区域96以及第2区域98分别是如图2所示那样的例如在y方向上并排的矩形状的区域。此外,例如,在第1区域96设有第1晶体管tr1(图1),在第2区域98设有第2晶体管tr2(图1)。第1晶体管tr1以及第2晶体管tr2例如分别是mosfet,但不限定于此。

39.图3的(a)是第1区域96的、沿a-a’线的与xz平面平行的面的示意剖面图。图3的(b)是第2区域98的、沿b-b’线的与xz平面平行的面的示意剖面图。图3的(c)是沿跨过第1区域96以及第2区域98的c-c’线的与yz面平行的面的示意剖面图。

40.漏极电极(第1电极的一例)60设置于基板30之下,与第1面32接触。换言之,基板30设置于漏极电极60之上。漏极电极60作为第1晶体管tr1以及第2晶体管tr2中的共同的漏极电极发挥功能。

41.基板30的第1面32具有y方向的长度l2比x方向的长度l1短的槽(第1槽的一例)36。图3中作为槽36而图示了槽36a、槽36b、槽36c、槽36d、槽36e、槽36f以及槽36g。并且,如图3的(a)以及图3的(b)所示,槽36b以及槽36e没有贯通基板30的侧面38(侧面38a以及侧面38b)。其他的槽36a、槽36c、槽36d、槽36f以及槽36g也同样没有贯通基板30的侧面38。在设有多个槽36的情况下,优选的是,所有的槽36都不贯通基板30的侧面38。并且,槽36d跨过第1区域96和第2区域98。

42.槽36的部分相对于基板30所占的体积比例优选的是,5%以上20%以下。

43.漏极电极60具有通过覆盖第1面32的槽36而与槽36对应的槽66(第2槽的一例)。换言之,漏极电极60的底面62在槽36之下具有y方向的长度l4比x方向的长度l3短的槽(第2槽的一例)66。图3中作为槽66而图示了槽66a、槽66b、槽66c、槽66d、槽66e、槽66f以及槽66g。这里,l3<l1,l4<l2。

44.图4是第1区域96中的、半导体装置100的主要部分的示意剖面图。

45.漏极层(第1半导体层的一例)10设置在漏极电极60之上。漏极层10例如是n

+

型的半导体材料。

46.漂移层(第2半导体层的一例)12设置于漏极层10之上。漂移层12是作为mosfet的漂移层而发挥功能的层。漂移层12例如是n

-

型的半导体材料。

47.基底区域(第1半导体区域的一例)14设置于漂移层12之上。基底区域14作为mosfet的基底发挥功能。基底区域14是能够在对后述的第1栅极电极28施加了电压的情况下形成沟道、并在漏极层10与后述的源极区域16之间流过载流子的区域。基底区域14例如是p型的半导体材料。

48.源极区域(第2半导体区域的一例)16设置于基底区域14之上。源极区域16是作为mosfet的源极发挥功能的区域。在对后述的第1栅极电极28施加了适当的电压的情况下,在源极区域16与漏极层10之间流过载流子。源极区域16例如是n

+

型的半导体材料。

49.接触区域18设置于基底区域14之上,与基底区域14以及源极区域16电连接。接触区域18为了使基底区域14以及源极区域16与后述的源极金属70的电接触提高而设置。接触区域18例如是p

+

型的半导体材料。

50.第1沟槽20以从基底区域14以及源极区域16之上到达漂移层12的方式设置。第1沟槽20沿着纸面进深方向(y方向)延伸。

51.第3绝缘膜22设置于第1沟槽20内。例如,第3绝缘膜22以覆盖后述的第1场板电极24的方式设置。并且,例如,第3绝缘膜22设置在第1场板电极24与第1栅极电极28之间。但是,第3绝缘膜22的方式不限定于此。第3绝缘膜22包含sio

x

(氧化硅),但不限定于此。

52.第1绝缘膜21在第1沟槽20内设置在第3绝缘膜22之上的、基底区域14与第1栅极电极28之间以及后述的层间绝缘膜95与源极区域16之间。第1绝缘膜21包含sio

x

(氧化硅)但不限定于此。

53.第1场板电极24在第1沟槽20内隔着第3绝缘膜22而与漂移层12对置地设置于漂移层12。例如,第1场板电极24与漂移层12并排地设置。第1场板电极24例如为了促进耗尽层从基底区域14向漂移层12延伸并使耐压增加而被设置。另外,也可以不设置第1场板电极24。

54.第1栅极电极(第2电极的一例)28位于第1场板电极24之上,隔着第1绝缘膜21而设置于多个基底区域14之间。第1栅极电极28是作为mosfet的栅极发挥功能的电极。

55.层间绝缘膜95设置于源极区域16、第1栅极电极28以及第1绝缘膜21之上。层间绝缘膜95例如包含sio

x

,但不限定于此。

56.源极金属70、以及源极金属74(图3的(a))设置于源极区域16以及接触区域18之上,并与源极区域16以及接触区域18电连接。

57.图5是第1区域96中的半导体装置100的主要部分的示意剖面图的其他的一例。也可以不设置接触区域18。

58.图6是第2区域98中的半导体装置100的主要部分的示意剖面图。例如,与第1区域

96共用地设置漏极电极60、漏极层10以及漂移层12。

59.另一方面,在第2区域98中在漂移层12之上设有基底区域(第3半导体区域的一例)54。在基底区域54之上设有源极区域(第4半导体区域的一例)56。在基底区域54之上设有接触区域58。换言之,关于基底区域、源极区域以及接触区域,在第1区域96和第2区域98中独立地设置。

60.并且,代替第1沟槽20而设置沿纸面进深方向(y方向)延伸的第2沟槽40。代替第3绝缘膜22而设置第4绝缘膜42。代替第1绝缘膜21而设置第2绝缘膜41。代替第1场板电极24而设置第2场板电极44。另外,也可以不设置第2场板电极44。代替第1栅极电极28而设置第2栅极电极(第3电极的一例)48。代替源极金属70以及源极金属74而设置源极金属82以及源极金属86(图3的(a))。

61.图7是第2区域98中的、半导体装置100的主要部分的示意剖面图的其他的一例。也可以不设置接触区域58。

62.另外,第1区域96中的构成与第2区域98中的构成不限定于上述的关系。

63.栅极金属72在第1区域96中设置于源极金属70与源极金属74之间。

64.栅极金属84在第2区域98中设置于源极金属82与源极金属86之间。

65.栅极金属72与源极金属70通过作为层间绝缘膜95的层间绝缘膜95b而被分离。栅极金属72与源极金属74通过作为层间绝缘膜95的层间绝缘膜95c而被分离。栅极金属84与源极金属82通过作为层间绝缘膜95的层间绝缘膜95f而被分离。栅极金属84与源极金属86通过作为层间绝缘膜95的层间绝缘膜95g而被分离。

66.源极金属74与源极金属86通过作为层间绝缘膜95的层间绝缘膜95j而被分离。另外,源极金属70与源极金属82、以及栅极金属72与栅极金属84也同样通过层间绝缘膜95而被分离。

67.图8是第1实施方式的半导体装置100的主要部分的示意剖面图。图8是用于表示第1场板电极24与源极金属70的连接方法的一例以及第1栅极电极28与栅极金属72的连接方法的一例的示意剖面图。例如,图4~图7的示意剖面图相当于图8的d-d’剖面中的示意剖面图。

68.第1场板电极24具有沿z方向延伸的部分。此外,使用沿该z方向延伸的部分,第1场板电极24经由设置于层间绝缘膜95以及第3绝缘膜22的接触孔而与源极金属70电连接。

69.第1栅极电极28经由设置于层间绝缘膜95的接触孔而与栅极金属72电连接。源极金属70以及第1场板电极24通过层间绝缘膜95以及第3绝缘膜22而与第1栅极电极28绝缘。

70.另外,关于源极金属74与第1场板电极24的电连接、源极金属82与第2场板电极44的电连接、栅极金属84与第2栅极电极48的电连接、及源极金属86与第2场板电极44的电连接,也能够同样进行。

71.镀层88、镀层78、镀层80、镀层76、镀层90以及镀层92分别被设置于源极金属70、栅极金属72、源极金属74、源极金属82、栅极金属84以及源极金属86之上。此外,镀层88、镀层78、镀层80、镀层76、镀层90以及镀层92分别各自与源极金属70、栅极金属72、源极金属74、源极金属82、栅极金属84以及源极金属86电连接。镀层88、镀层78、镀层80、镀层76、镀层90以及镀层92为了提高与未图示的外部电路之间的基于焊料等的连接的强度而设置。

72.镀层88与镀层78通过作为绝缘膜94的绝缘膜94b而被分离。镀层78与镀层80通过

作为绝缘膜94的绝缘膜94c而被分离。镀层76与镀层90通过作为绝缘膜94的绝缘膜94f而被分离。镀层90与镀层92通过作为绝缘膜94的绝缘膜94g而被分离。镀层80与镀层92通过作为绝缘膜94的绝缘膜94j而被分离。另外,镀层88与镀层76、以及镀层78与镀层90也同样通过绝缘膜94而被分离。

73.图9是第1实施方式的半导体装置的主要部分的示意剖面图。图9是示出了槽36的剖面的一例的图。槽36优选的是通过等离子体蚀刻而被形成。这里,通过重复执行使用了f(氟)系自由基的各向同性蚀刻、包含cf4(四氟化碳)系自由基的保护膜的形成、以及使用了f系离子的各向异性蚀刻,来进行该等离子体蚀刻。通过这样的等离子体蚀刻,在槽36的侧面35形成具有贝壳状的形状的扇贝形部(scallop)37。具体来说,形成有扇贝形部37a、扇贝形部37b、扇贝形部37c以及扇贝形部37d。另外,关于其他的附图的槽36,省略了扇贝形部37的图示。

74.基板30例如是硅基板。但是,基板30也可以是例如碳化硅(sic)基板、氮化镓(gan)基板或砷化镓(gaas)基板等。

75.在作为半导体材料而使用si的情况下,能够使用例如砷(as)、磷(p)或锑(sb)作为n型杂质,并且使用例如b(硼)作为p型杂质。

76.第1场板电极24、第2场板电极44、第1栅极电极28以及第2栅极电极48包含例如含有导电型杂质的多晶硅等导电材料。

77.漏极电极60、源极金属70、栅极金属72、源极金属74、源极金属82、栅极金属84、源极金属86包含例如al(铝)、ag(银)、cu(铜)等金属材料,例如通过电镀法形成。

78.接着,记载本实施方式的半导体装置的作用效果。

79.图10是成为第1实施方式的比较方式的半导体装置的示意剖面图。

80.在本实施方式的半导体装置那样的、包含第1晶体管tr1以及第2晶体管tr2的半导体装置中,特别要求由基板30的薄膜化带来的漂移层12的电阻降低。这里,若将基板30薄膜化,则导致基板30翘曲,在半导体装置的制造工序中有变得不能进行搬运等的问题。

81.特别是在半导体装置的微细化等方面具有长处的沟槽栅构造的半导体装置中,存在基板30的翘曲变大的问题。这里,作为基板30的翘曲的形态,有例如如图10的(a)所示在xz平面内中央部分朝着上方的方向翘曲的情况、和如图10的(b)所示在xz平面内中央部分朝着下方的方向翘曲的情况。这能够理解为,在与第1沟槽20以及第2沟槽40延伸的y方向垂直的面内(xz面内),发生了较大的翘曲。但是,第1沟槽20以及第2沟槽40的形状和材料、第1栅极电极28以及第2栅极电极48的形状和材料、第1场板电极24以及第2场板电极44的形状和材料、基底区域14以及源极区域16的形状和材料、基底区域54以及源极区域56的形状和材料直接关系到mosfet的特性。因此,为了抑制该翘曲而改变上述的形状和材料是困难的。

82.因此,本实施方式的半导体装置100在基板30的第1面32具有如下的槽36,该槽36中,与平行于第1面32的x方向的长度相比,交叉于x方向且平行于第1面32的y方向上的长度更短。并且,在基板30内,第1沟槽20以及第2沟槽40沿y方向延伸。

83.由此,通过设置槽36,能够抑制可能在xz面内发生的基板30的翘曲。并且,通过槽36的形成,能够将基板30的一部分薄膜化而进行漂移层12的电阻降低。因此,能够提供良品率高的半导体装置。

84.并且,槽36通过等离子体蚀刻而形成的话,由于能够按照基板30的翘曲的形状而

容易地改变所形成的槽36的深度和图案,因此是优选的。该情况下,槽36的侧面35成为具有扇贝形部37。

85.并且,槽36优选的是不贯通基板30的侧面38。这是因为,若槽36将基板30的侧面38贯通,则导致该贯通了的部分的基板30的强度变弱。由于相同的理由,在设有多个槽36的情况下,优选的是所有的槽36都不贯通基板30的侧面38。

86.在形成了槽36的基板30的第1面32形成漏极电极60时,在漏极电极60的底面,在槽36之下形成y方向的长度l4比x方向的长度l3短的槽66。这里,例如l3<l1,l4<l2。这是在形成漏极电极60时通过使漏极电极60的形状追随于槽36的形状而形成的。

87.根据本实施方式的半导体装置100,能够提供良品率高的半导体装置100。

88.(第2实施方式)

89.本实施方式的半导体装置与第1实施方式的半导体装置的不同点在于,在第1槽之中设有第3槽,第3槽的长度比第1槽的长度短,第3槽的深度比第1槽的深度深。这里,省略与第1实施方式重复的内容的记载。

90.图11是本实施方式的半导体装置110的示意图。图11的(a)是示出了基板30的第1面32以及第1面32所形成的槽36的示意图。图11的(b)是图11的(a)的沿e-e’剖面的基板30以及槽36的示意剖面图。图11的(a)中图示了作为槽36的槽36h1(第1槽的一例)、槽36h2、槽36h3、槽36h4(第3槽的一例)、槽36h5、槽36h6、槽36h7、槽36h8、槽36h9以及槽36h10。槽36h1之中设有槽36h4。如图11的(b)所示,槽36h4的长度l12比槽36h1的长度l11短。并且,如图11的(b)所示,槽36h4的深度d2比槽36h1的深度d1深(长)。

91.例如,能够在图3所示的槽36d(第1槽的一例)之中还设有与槽36d相比长度更短且深度更深的槽(第3槽的一例)。

92.图12是表示本实施方式的半导体装置110的制造工序的主要部分的示意剖面图。图12是表示相对于基板30的第1面32的、槽36的制造工序的主要部分的示意剖面图。

93.首先,在基板30的第1面32形成设置了长度l12的间隔的光致抗蚀剂pa(图12的(a))。

94.接着,通过等离子体蚀刻,对没有设置光致抗蚀剂pa的部分的基板30的一部分进行削去,形成槽36h4以及槽36h6(图12的(b))。接着,将光致抗蚀剂pa除去(图12的(c))。

95.接着,在基板30的、没有形成槽36h4以及槽36h6的第1面32之上,形成设置了沿x方向具有长度l11的开口的光致抗蚀剂pb(图12的(d))。

96.接着,通过等离子体蚀刻,对没有设置光致抗蚀剂pa的部分的基板30的一部分进行削去,形成槽36h1以及槽36h7。接着,将光致抗蚀剂pa除去(图12的(e))。通过以上,能够形成本实施方式的槽36h1以及槽36h4。

97.为了进一步抑制基板30的翘曲,通过组合本实施方式的制造方法,能够形成各种各样的形状的槽36。例如,通过将图3所示的槽36d设为图11所示的槽36h1以及槽36h4那样的形状的槽,有可能能够进一步抑制基板30的翘曲。因此,根据本实施方式的半导体装置110,能够提供良品率更高的半导体装置。

98.(第3实施方式)

99.本实施方式的半导体装置与第1以及第2实施方式的半导体装置的不同点在于,第1面在第1槽与基板的端部之间具有第2方向的长度比第1槽短的第4槽。这里,省略与第1以

及第2实施方式重复的内容的记载。

100.图13是本实施方式的半导体装置120的示意图。图13是示出了基板30的第1面32以及第1面32所形成的槽36的示意图。图13中图示了作为槽36的槽36i1(第4槽的一例)、槽36i2(第4槽的一例)、槽36i3(第4槽的一例)、槽36i4(第1槽的一例)、槽36i5(第4槽的一例)、槽36i6(第4槽的一例)以及槽36i7(第4槽的一例)。y方向的槽36i1、槽36i2、槽36i3、槽36i5、槽36i6以及槽36i7的长度是d2,比y方向的槽36i4的长度d1短。

101.例如,能够使图3所示的槽36a(第4槽的一例)、槽36b(第4槽的一例)、槽36c(第4槽的一例)、槽36e(第4槽的一例)、槽36f(第4槽的一例)以及槽36g(第4槽的一例)的y方向的长度比槽36d(第1槽的一例)的y方向的长度短。

102.通过使第1面32的中央部分的槽36i4的y方向的长度比其他的槽长,从而能够在基板30的中央部分的翘曲更强的情况下抑制该翘曲。

103.根据本实施方式的半导体装置120,能够提供良品率高的半导体装置120。

104.(第4实施方式)

105.本实施方式的半导体装置与第1~第3实施方式的半导体装置的不同点在于,第1面在第1槽与基板的端部之间具有第2方向的长度比第1槽长的第5槽。这里,省略与第1~第3实施方式重复的内容的记载。

106.图14是本实施方式的半导体装置130的示意图。图14是示出了基板30的第1面32以及第1面32所形成的槽36的示意图。图14中图示了作为槽36的槽36j1(第5槽的一例)、槽36j2(第1槽的一例)、槽36j3(第1槽的一例)、槽36j4(第1槽的一例)以及槽36j5(第5槽的一例)。y方向的槽36j1以及槽36j5的长度是d3,比y方向的槽36j2、槽36j3以及槽36j4的长度d4长。

107.例如,能够使图3所示的槽36a(第5槽的一例)、槽36b(第5槽的一例)、槽36c(第5槽的一例)、槽36e(第5槽的一例)、槽36f(第5槽的一例)以及槽36g(第5槽的一例)的y方向的长度比槽36d(第1槽的一例)的y方向的长度长。

108.通过使第1面32的端部分的槽36j1以及槽36j5的y方向的长度比槽36j2、槽36j3以及槽36j4的y方向的长度长,能够在基板30的端部的翘曲更强的情况下抑制该翘曲。

109.根据本实施方式的半导体装置130,能够提供良品率高的半导体装置130。

110.(第5实施方式)

111.本实施方式的半导体装置与第1~第4实施方式的半导体装置的不同点在于,第1面具有:在第1方向上与第1槽并排的多个第6槽、和在第2方向上与第1槽以及多个第6槽分别并排的多个第7槽。这里省略与第1~第4实施方式重复的内容的记载。

112.图15是本实施方式的半导体装置140的示意图。图15是示出了基板30的第1面32以及第1面32所形成的槽36的示意图。图15中图示了作为槽36的、槽36o1、槽36o2、槽36o3、槽36o4、槽36o5、槽36o6、槽36o7、槽36n1、槽36n2、槽36n3、槽36n4、槽36n5、槽36n6、槽36n7、槽36m1、槽36m2、槽36m3、槽36m4、槽36m5、槽36m6、槽36m7、槽36l1、槽36l2、槽36l3、槽36l4、槽36l5、槽36l6、槽36l7、槽36k1、槽36k2、槽36k3、槽36k4、槽36k5、槽36k6、槽36k7。

113.槽36o1、槽36n1、槽36l1以及槽36k1(多个第6槽的一例)与槽36m1(第1槽的一例)在x方向上并排。槽36o3、槽36o4、槽36o5、槽36o6以及槽36o7(多个第7槽的一例)与槽36o1在y方向上并排。槽36n2、槽36n3、槽36n4、槽36n5、槽36n6以及槽36n7(多个第7槽的一例)与

槽36n1在y方向上并排。槽36l2、槽36l3、槽36l4、槽36l5、槽36l6以及槽36l7(多个第7槽的一例)与槽36l1在y方向上并排。槽36k2、槽36k3、槽36k4、槽36k5、槽36k6以及槽36k7(多个第7槽的一例)与槽36k1在y方向上并排。

114.槽36m4的y方向的宽度是d7。槽36m3以及槽36m5的y方向的宽度是d6,d6<d7。槽36m1、槽36m2、槽36m6以及槽36m7的y方向的宽度是d5,d5<d6。另一方面,槽36m1、槽36m2、槽36m3、槽36m4、槽36m5、槽36m6以及槽36m7的x方向的宽度是d8,都相等。本实施方式的槽36在x方向上排列有这样的槽36m1、槽36m2、槽36m3、槽36m4、槽36m5、槽36m6以及槽36m7。

115.例如,通过将图3所示的槽36a、槽36b、槽36c、槽36d、槽36e、槽36f以及槽36g在x方向上分割为5部分,并变更y方向的宽度,从而能够得到图15所示的槽36。

116.本实施方式的半导体装置140中的槽36的这种配置在基板30整体扭曲的情况下,能够抑制这种扭曲。

117.根据本实施方式的半导体装置140,能够提供良品率高的半导体装置140。

118.(第6实施方式)

119.本实施方式的半导体装置与第1~第5实施方式的半导体装置的不同点在于,形状不同的槽被配置在镀层76之下、镀层80之下、镀层88之下以及镀层92之下。这里,省略与第1~第5实施方式重复的内容的记载。

120.图16是本实施方式的半导体装置150的示意图。图16是示出了基板30的第1面32以及第1面32所形成的槽36的示意图。本实施方式的半导体装置150还具备:在第1区域96之上的第2面34设置且与源极区域16(第2半导体区域的一例)电连接的镀层76(第4电极的一例)、在第1区域96之上的第2面34设置且与源极区域16(第2半导体区域的一例)电连接的镀层80(第5电极的一例)、在镀层76(第4电极的一例)与镀层80(第5电极的一例)之间的第2面34设置且与第1栅极电极28(第2电极的一例)电连接的镀层78(第6电极的一例)、在第2区域98之上的第2面34设置且与源极区域56(第4半导体区域的一例)电连接的镀层88(第7电极的一例)、在第2区域98之上的第2面34设置且与源极区域56(第4半导体区域的一例)电连接的镀层92(第8电极的一例)、在镀层88(第7电极的一例)与镀层92(第8电极的一例)之间的第2面34设置且与第2栅极电极48(第3电极的一例)电连接的镀层90(第9电极的一例),第1面32还具备:设于镀层76(第4电极的一例)之下的槽36p1(第8槽的一例)、设于镀层80(第5电极的一例)之下的槽36p2(第9槽的一例)、设于镀层88(第7电极的一例)之下的槽36p3(第10槽的一例)、设于镀层92(第8电极的一例)之下的槽36p4(第11槽的一例)。

121.槽36p1、槽36p2、槽36p3以及槽36p4的形状各不相同。具体来说,槽36p1、槽36p2、槽36p3以及槽36p4的x方向的长度d11、d12、d13以及d14各不相同。并且,槽36p1、槽36p2、槽36p3以及槽36p4的y方向的长度d21、d22、d23、d24各不相同。另外,槽36p1、槽36p2、槽36p3以及槽36p4的形状不同的方式当然不限定于上述的方式。

122.在基板30具有复杂的翘曲的情况下,通过如上述那样使槽36的形状变化,能够抑制翘曲。

123.根据本实施方式的半导体装置150,能够提供良品率高的半导体装置150。

124.说明了本发明的若干实施方式以及实施例,但这些实施方式以及实施例是作为例子而提示的,不意图限定发明的范围。这些新的实施方式能够以其他各种各样的方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、替换、变更。这些实施方式及其变形包

含在发明的范围及主旨中,并且包含在权利要求书所记载的发明及其等价的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1