外延结构、发光器件和外延结构的制作方法与流程

1.本技术涉及半导体发光技术领域,尤其涉及一种外延结构、发光器件和外延结构的制作方法。

背景技术:

2.为促进micro-led(micro-light emitting diode,微发光二极管)商业化进程,大尺寸外延衬底导入降低成本势在必行,然而优选的大尺寸衬底(硅衬底或者蓝宝石衬底)均与外延层主材料gan之间存在着显著的晶格失配和热失配问题。衬底尺寸增加之后晶格热失配导致的翘曲问题会更加显著,翘曲变化直接影响外延结构的均匀性。要解决此难题需要在底层引入更加合理的应力释放层来抵消因晶格热失配导致的翘曲问题,因此先进应力释放层搭配大尺寸衬底来实现高效率micro-led产品开发势在必行。

3.相比于大尺寸器件,micro-led分光分色比较困难,且micro-led的波长均匀性直接影响显示的色彩精准度,因此需要对micro-led的波长均匀性提出更高的要求。基于技术进步以及工艺成本的考虑,micro-led外延的衬底在不断往大尺寸方向发展。衬底尺寸越大,外延结构生长过程中应力控制更加困难,从而对波长均匀性越难以控制。

4.因此,如何在衬底尺寸较大的情况下控制外延结构的应力水平,进而控制波长均匀性是亟需解决的问题。

技术实现要素:

5.鉴于上述现有技术的不足,本技术的目的在于提供一种外延结构、发光器件和外延结构的制作方法,旨在解决在衬底尺寸较大的情况下控制外延结构的应力水平,进而控制波长均匀性的问题。

6.一种外延结构,包括:

7.衬底;

8.缓冲层,形成在所述衬底上;以及

9.应力释放层,所述应力释放层包括第一应力释放层,所述第一应力释放层形成在所述缓冲层上,所述第一应力释放层的材质为algan,其中,al组分含量占比为50%-90%。

10.第一应力释放层的材质为al组分含量较高的algan,可预先引入压应力,实现高质量无裂纹的gan薄膜外延生长。基于tem表征和hall测试方法,高al组分的第一应力释放层不仅过滤大量位错,而且引入的压应力使得部分位错转弯煙灭,最终实现镜面光滑无裂纹且低位错密度的gan薄膜,与未采用此应力释放层的结构相比本技术的外延结构使得薄膜的表面粗糙度改善20-50%,位错密度降低30-50%,在衬底尺寸较大的情况下控制外延结构的应力水平,进而控制波长均匀性。

11.一种实施方式中,所述应力释放层还包括第二应力释放层和第四应力释放层,所述第二应力释放层形成在所述第一应力释放层上,所述第四应力释放层形成在所述第二应力释放层上;

12.其中,所述第二应力释放层的材质为aln,

ⅴ

/ⅲ比为400-1000,所述第四应力释放层的材质为aln,

ⅴ

/ⅲ比为30-100。

13.较高的

ⅴ

/ⅲ比可改变第二应力释放层的生长方式,使之更加趋向于三维生长(3d)模式,而高

ⅴ

/ⅲ下表征晶体质量更进一步的得到改善,缺陷密度也更进一步的减小,最终内量子效率得到显著提升。较低

ⅴ

/ⅲ比的第四应力释放层更加趋向于二维生长(2d)模式,具有光滑的表面为后续层高质量的生长提供基础。

14.一种实施方式中,所述应力释放层还包括第三应力释放层,所述第三应力释放层形成在所述第一应力释放层上;

15.其中,所述第三应力释放层为第一子应力释放层和第二子应力释放层交替生长形成的超晶格结构,且起始生长所述第一子应力释放层,交替生长周期不大于100,所述第一子应力释放层的材质为aln,所述第二子应力释放层的材质为gan。

16.通过设置本实施方式的第三应力释放层,处于较大压应变的第一子应力释放层和第二子应力释放层进一步的降低了因晶格失配和热失配导致的张应力,减小多量子阱发光层的压电极化电场,量子限制斯塔克得到削弱,从而提升了电子和空穴辐射复合效率。

17.一种实施方式中,所述应力释放层还包括第二应力释放层、第三应力释放层和第四应力释放层,所述第二应力释放层形成在所述第一应力释放层上,所述第三应力释放层形成在所述第二应力释放层上,所述第四应力释放层形成在所述第三应力释放层上;

18.其中,所述第二应力释放层的材质为aln,

ⅴ

/ⅲ比为400-1000;所述第三应力释放层为第一子应力释放层和第二子应力释放层交替生长形成的超晶格结构,且起始生长所述第一子应力释放层,交替生长周期不大于100,所述第一子应力释放层的材质为aln,所述第二子应力释放层的材质为gan;所述第四应力释放层的材质为aln,

ⅴ

/ⅲ比为30-100。

19.结合以上第一应力释放层到第四应力释放层,本实施方式的外延结构,一方面改善了因大尺寸衬底和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底尤其是硅衬底上生长外延结构存在的裂纹(crack)问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子发光层存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。

20.一种实施方式中,所述第一应力释放层的厚度为50-150nm。设置本实施方式的厚度的第一应力释放层,合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

21.一种实施方式中,所述第二应力释放层的厚度为50-100nm。设置本实施方式的厚度的第二应力释放层,合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

22.一种实施方式中,所述第三应力释放层中,所述第一子应力释放层的厚度小于10nm,所述第二子应力释放层的厚度为15-30nm。设置本实施方式的厚度的第三应力释放层,合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

23.一种实施方式中,所述第四应力释放层的厚度为20-50nm。设置本实施方式的厚度的第四应力释放层,合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的

晶体质量,从而提升发光效率。

24.一种实施方式中,所述外延结构还包括依次形成在所述应力释放层上的n型gan层、多量子阱发光层和p型gan层。

25.基于相同的构思,本技术还提供一种发光器件,包括前述实施方式中任一项所述的外延结构。

26.基于相同的构思,本技术还提供一种外延结构的制作方法,包括:

27.在衬底上形成缓冲层;

28.在所述缓冲层上形成应力释放层;

29.其中,所述应力释放层包括第一应力释放层,所述第一应力释放层形成在所述缓冲层上,所述第一应力释放层的材质为algan,al组分含量占比为50%-90%。

30.第一应力释放层的材质为al组分含量较高的algan,可预先引入压应力,实现高质量无裂纹的gan薄膜外延生长。基于tem表征和hall测试方法,高al组分的第一应力释放层不仅过滤大量位错,而且引入的压应力使得部分位错转弯煙灭,最终实现镜面光滑无裂纹且低位错密度的gan薄膜,与未采用此应力释放层的结构相比本技术的外延结构使得薄膜的表面粗糙度改善20-50%,位错密度降低30-50%,在衬底尺寸较大的情况下控制外延结构的应力水平,进而控制波长均匀性。

31.一种实施方式中,所述应力释放层还包括第二应力释放层和第四应力释放层,所述方法还包括:

32.在所述第一应力释放层上形成所述第二应力释放层,在所述第二应力释放层上形成所述第四应力释放层;

33.其中,所述第二应力释放层的材质为aln,

ⅴ

/ⅲ比为400-1000,所述第四应力释放层的材质为aln,

ⅴ

/ⅲ比为30-100。

34.较高的

ⅴ

/ⅲ比可改变第二应力释放层的生长方式,使之更加趋向于三维生长(3d)模式,而高

ⅴ

/ⅲ下表征晶体质量更进一步的得到改善,缺陷密度也更进一步的减小,最终内量子效率得到显著提升。较低

ⅴ

/ⅲ比的第四应力释放层更加趋向于二维生长(2d)模式,具有光滑的表面为后续层高质量的生长提供基础。

35.一种实施方式中,所述应力释放层还包括第三应力释放层,所述方法还包括:

36.在所述第一应力释放层上形成所述第三应力释放层;

37.其中,所述第三应力释放层为第一子应力释放层和第二子应力释放层交替生长形成的超晶格结构,且起始生长所述第一子应力释放层,交替生长周期不大于100,所述第一子应力释放层的材质为aln,所述第二子应力释放层的材质为gan。

38.通过设置本实施方式的第三应力释放层,处于较大压应变的第一子应力释放层和第二子应力释放层进一步的降低了因晶格失配和热失配导致的张应力,减小多量子阱发光层的压电极化电场,量子限制斯塔克得到削弱,从而提升了电子和空穴辐射复合效率。

39.一种实施方式中,所述应力释放层还包括第二应力释放层、第三应力释放层和第四应力释放层,所述方法还包括:

40.在所述第一应力释放层上形成所述第二应力释放层,在所述第二应力释放层上形成所述第三应力释放层,在所述第三应力释放层上形成所述第四应力释放层;

41.其中,所述第二应力释放层的材质为aln,

ⅴ

/ⅲ比为400-1000;所述第三应力释放

层为第一子应力释放层和第二子应力释放层交替生长形成的超晶格结构,且起始生长所述第一子应力释放层,交替生长周期不大于100,所述第一子应力释放层的材质为aln,所述第二子应力释放层的材质为gan;所述第四应力释放层的材质为aln,

ⅴ

/ⅲ比为30-100。

42.结合以上第一应力释放层到第四应力释放层,本实施方式的外延结构,一方面改善了因大尺寸衬底和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底尤其是硅衬底上生长外延结构存在的裂纹(crack)问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子发光层存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。

43.一种实施方式中,在温度大于1000℃,压力小于75mbar的条件下形成所述第一应力释放层,所述第一应力释放层的厚度为50-150nm。设置本实施方式的温度和压力条件,并生成本实施方式的厚度的第一应力释放层,一方面合理的改善了因大尺寸衬底和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底尤其是硅衬底上生长外延结构存在的crack问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子阱发光层存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

44.一种实施方式中,在温度大于1050℃,压力小于75mbar的条件下形成所述第二应力释放层,所述第二应力释放层的厚度为50-100nm。设置本实施方式的温度和压力条件,并生成本实施方式的厚度的第二应力释放层,一方面合理的改善了因大尺寸衬底和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底尤其是硅衬底上生长外延结构存在的crack问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子阱发光层存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

45.一种实施方式中,在温度大于1000℃,压力小于200mbar的条件下形成所述第三应力释放层,所述第三应力释放层中,所述第一子应力释放层的厚度小于10nm,所述第二子应力释放层的厚度为15-30nm。设置本实施方式的温度和压力条件,并生成本实施方式的厚度的第三应力释放层,一方面合理的改善了因大尺寸衬底和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底尤其是硅衬底上生长外延结构存在的crack问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子阱发光层存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

46.一种实施方式中,在温度大于1050℃,压力小于75mbar的条件下形成所述第四应力释放层,所述第四应力释放层的厚度为20-50nm。设置本实施方式的温度和压力条件,并

生成本实施方式的厚度的第四应力释放层,一方面合理的改善了因大尺寸衬底和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底尤其是硅衬底上生长外延结构存在的crack问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子阱发光层存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

47.一种实施方式中,所述方法还包括:

48.在所述应力释放层上依次形成n型gan层、多量子阱发光层和p型gan层。

附图说明

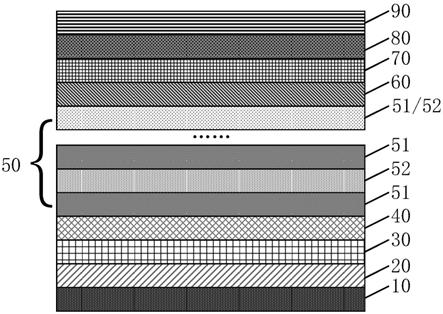

49.图1为一种实施例的外延结构的结构示意图。

50.附图标记说明:

51.10-衬底,20-缓冲层,30-第一应力释放层,40-第二应力释放层,50-第三应力释放层,51-第一子应力释放层,52-第二子应力释放层,60-第四应力释放层,70-n型gan层,80-多量子阱发光层,90-p型gan层。

具体实施方式

52.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的较佳实施方式。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施方式。相反地,提供这些实施方式的目的是使对本技术的公开内容理解的更加透彻全面。

53.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施方式的目的,不是旨在于限制本技术。

54.micro-led(micro-light emitting diode,微发光二极管)外延结构的晶体质量会直接影响显示效果。与大尺寸的led芯片相比,micro-led外延结构缺陷、极化电场影响和波长均匀性等问题更为突出。由于micro-led芯片尺寸在50um以下,应用于显示时处于低电流密度,此时由表面缺陷导致的非辐射复合变得尤为重要。并且由于尺寸减小使得同一外延结构上芯片之间的穿透位错密度统计涨落更加显著,因此对于micro-led需要更低缺陷密度的外延结构,或者钝化这些缺陷结构。micro-led有源区的极化电场会导致电子和空穴波函数分离,降低内量子效率,且极化电场会使得电流密度变化时发光峰值波长发生偏移,不利于显示应用,因此需要有效地控制有源区的极化电场。

55.相比于大尺寸器件,micro-led分光分色比较困难,且micro-led的波长均匀性直接影响显示的色彩精准度,因此需要对micro-led的波长均匀性提出更高的要求。基于技术进步以及工艺成本的考虑,micro-led外延的衬底在不断往大尺寸方向发展。衬底尺寸越大,外延结构生长过程中应力控制更加困难,从而对波长均匀性越难以控制。

56.因此,如何在衬底尺寸较大的情况下控制外延结构的应力水平,进而控制波长均匀性是亟需解决的问题。

57.基于此,本技术希望提供一种能够解决上述技术问题的方案,其详细内容将在后续实施例中得以阐述。

58.请参考图1,本技术实施例提供一种外延结构,包括衬底10、缓冲层20和应力释放层。

59.衬底10可为大尺寸(不小于6寸)的基板,材质可为硅。

60.缓冲层20形成在衬底10上,应力释放层形成在缓冲层20上。

61.外延结构还包括依次形成在应力释放层上的n型gan(氮化镓)层70、多量子阱发光层80和p型gan层90。

62.实施例一:

63.应力释放层包括第一应力释放层30、第二应力释放层40、第三应力释放层50和第四应力释放层60。第一应力释放层30形成在缓冲层20上,第二应力释放层40形成在第一应力释放层30上,第三应力释放层50形成在第二应力释放层40上,第四应力释放层60形成在第三应力释放层50上,n型gan层70形成在第四应力释放层60上。

64.其中,第一应力释放层30的材质为algan(氮化镓铝),其中,al(铝)组分含量占比为50%-90%。可选的,al组分含量占比可为50%、60%、70%、80%、90%等,优选的,al组分含量占比为75%。

65.第一应力释放层30的材质为al组分含量较高的algan,可预先引入压应力,实现高质量无裂纹的gan薄膜外延生长。基于tem(transmission electron microscope,透射电子显微镜)表征和hall(霍尔)测试方法,高al组分的第一应力释放层30不仅过滤大量位错,而且引入的压应力使得部分位错转弯煙灭,最终实现镜面光滑无裂纹且低位错密度的gan薄膜,与未采用此应力释放层的结构相比本技术的外延结构使得薄膜的表面粗糙度改善20-50%,位错密度降低30-50%,在衬底10尺寸较大的情况下控制外延结构的应力水平,进而控制波长均匀性。

66.制作第一应力释放层30时,在温度大于1000℃,压力小于75mbar的条件下在缓冲层20上生长第一应力释放层30,并使第一应力释放层30的厚度为50-150nm。可选的,温度可为1020℃、1040℃、1050℃、1060℃、1080℃、1100℃等,优选的,温度为1050℃。可选的,压力为40mbar、45mbar、50mbar、55mbar、60mbar、65mbar、70mbar等,优选的,压力为50mbar。可选的,厚度为50nm、80nm、100nm、120nm、130nm、140nm、150nm等,优选的,厚度为120nm。

67.设置本实施例的温度和压力条件,并生成本实施例的厚度的第一应力释放层30,一方面合理的改善了因大尺寸衬底10和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底10尤其是硅衬底上生长外延结构存在的裂纹(crack)问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子阱发光层80存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

68.其中,第二应力释放层40的材质为aln(氮化铝),

ⅴ

/ⅲ比为400-1000。可选的,

ⅴ

/ⅲ比可为400、500、600、700、800、900、1000等,优选的,

ⅴ

/ⅲ比为600。其中,

ⅴ

/ⅲ比是指化合物中元素周期表中

ⅴ

族元素和ⅲ族元素的质量占比。

69.较高的

ⅴ

/ⅲ比可改变第二应力释放层40的生长方式,使之更加趋向于三维生长(3d)模式,而高

ⅴ

/ⅲ下表征晶体质量更进一步的得到改善,缺陷密度也更进一步的减小,最终内量子效率得到显著提升。

70.制作第二应力释放层40时,在温度大于1050℃,压力小于75mbar的条件下形成第二应力释放层40,第二应力释放层40的厚度为50-100nm。可选的,温度可为1060℃、1080℃、1100℃、1120℃、1140℃、1150℃等,优选的,温度为1100℃。可选的,压力为40mbar、45mbar、50mbar、55mbar、60mbar、65mbar、70mbar等,优选的,压力为50mbar。可选的,厚度为50nm、60nm、70nm、80nm、90nm、100nm等,优选的,厚度为80nm。

71.设置本实施例的温度和压力条件,并生成本实施例的厚度的第二应力释放层40,一方面合理的改善了因大尺寸衬底10和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底10尤其是硅衬底上生长外延结构存在的crack问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子阱发光层80存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

72.其中,第三应力释放层50为第一子应力释放层51和第二子应力释放层52交替生长形成的超晶格结构,且起始生长第一子应力释放层51,交替生长周期不大于100,第一子应力释放层51的材质为aln,第二子应力释放层52的材质为gan。如图1所示的,一第一子应力释放层51生长在第二应力释放层40上,一第二子应力释放层52生长在第一子应力释放层51上,下一第一子应力释放层51生长在第二子应力释放层52上,依此交替生长,直至生长到第n个第一子应力释放层51或第二子应力释放层52为止,n不大于200,也就是以每生长一个第一子应力释放层51和第二子应力释放层52为一个周期。

73.通过设置本实施例的第三应力释放层50,处于较大压应变的第一子应力释放层51和第二子应力释放层52进一步的降低了因晶格失配和热失配导致的张应力,减小多量子阱发光层80的压电极化电场,量子限制斯塔克得到削弱,从而提升了电子和空穴辐射复合效率。

74.制作第三应力释放层50时,在温度大于1000℃,压力小于200mbar的条件下形成第三应力释放层50,第三应力释放层50中,第一子应力释放层51的厚度小于10nm,第二子应力释放层52的厚度为15-30nm。

75.可选的,温度可为1020℃、1040℃、1050℃、1060℃、1080℃、1100℃等,优选的,温度为1050℃。可选的,压力为50mbar、80mbar、100mbar、120mbar、150mbar、180mbar、200mbar等,优选的,压力为100mbar。可选的,第一子应力释放层51的厚度为2nm、4nm、5nm、6nm、8nm、9nm等,优选的,第一子应力释放层51的厚度为5nm。可选的,第二子应力释放层52的厚度为15nm、18nm、20nm、22nm、25nm、28nm、30nm等,优选的,第二子应力释放层52的厚度为22nm。

76.设置本实施例的温度和压力条件,并生成本实施例的厚度的第三应力释放层50,一方面合理的改善了因大尺寸衬底10和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底10尤其是硅衬底上生长外延结构存在的crack问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底10下应力导致的micro-led均匀性也得到改善,对应

的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子阱发光层80存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

77.其中,第四应力释放层60的材质为aln,

ⅴ

/ⅲ比为30-100。可选的,

ⅴ

/ⅲ比可为30、40、50、60、70、80、90、100等,优选的,

ⅴ

/ⅲ比为50。

78.较低

ⅴ

/ⅲ比的第四应力释放层60更加趋向于二维生长(2d)模式,具有光滑的表面为后续层高质量的生长提供基础。

79.制作第四应力释放层60时,在温度大于1050℃,压力小于75mbar的条件下形成第四应力释放层60,第四应力释放层60的厚度为20-50nm。可选的,温度可为1060℃、1080℃、1100℃、1120℃、1140℃、1150℃等,优选的,温度为1100℃。可选的,压力为40mbar、45mbar、50mbar、55mbar、60mbar、65mbar、70mbar等,优选的,压力为50mbar。可选的,厚度为20nm、30nm、35nm、40nm、50nm等,优选的,厚度为35nm。

80.设置本实施例的温度和压力条件,并生成本实施例的厚度的第四应力释放层60,一方面合理的改善了因大尺寸衬底10和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底10尤其是硅衬底上生长外延结构存在的crack问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底10下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子阱发光层80存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。合理的厚度可以减小因晶格失配导致的缺陷密度,提高了外延结构的晶体质量,从而提升发光效率。

81.结合以上第一应力释放层30到第四应力释放层60,本实施例的外延结构,一方面改善了因大尺寸衬底10和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底10尤其是硅衬底10上生长外延结构存在的裂纹(crack)问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底10下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子发光层存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。

82.实施例二:

83.本实施例与实施例一基本相同,区别在于,应力释放层只包括第一应力释放层30,而无第二应力释放层40、第三应力释放层50和第四应力释放层60,n型gan层70形成在第一应力释放层30上。

84.本实施例中,第一应力释放层30的结构、制作条件、生长厚度以及有益效果等可参考实施例一,不再赘述。

85.实施例三:

86.本实施例与实施例一基本相同,区别在于,应力释放层只包括第一应力释放层30和第三应力释放层50,而无第二应力释放层40和第四应力释放层60。其中,第三应力释放层50直接形成在第一应力释放层30上,n型gan层70形成在第三应力释放层50上。

87.本实施例中,第一应力释放层30和第三应力释放层50的结构、制作条件、生长厚度

以及有益效果等可参考实施例一,不再赘述。

88.实施例四:

89.本实施例与实施例一基本相同,区别在于,应力释放层只包括第一应力释放层30,第二应力释放层40和第四应力释放层60,而无第三应力释放层50,n型gan层70形成在第四应力释放层60上。

90.本实施例中,第一应力释放层30、第二应力释放层40和第四应力释放层60的结构、制作条件、生长厚度以及有益效果等可参考实施例一,不再赘述。

91.本技术实施例还提供一种发光器件,包括前述实施例中的外延结构。本实施例的发光器件具体可为micro-led芯片,一方面改善了因大尺寸衬底10和外延结构晶格失配和热失配导致的张应力过大问题,解决了大尺寸衬底10尤其是硅衬底10上生长外延结构存在的裂纹(crack)问题,晶体质量得到提高,且应力得到有效控制后大尺寸衬底10下应力导致的micro-led均匀性也得到改善,对应的micro-led芯片发射波长不一致导致的色差问题。另一方面能够减小多量子发光层存在的压电极化导致的量子限制斯塔克效应,从而可以实现量子阱中电子和空穴的高效复合,发光效率显著提升。

92.应当理解的是,本技术的应用不限于上述的举例,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,所有这些改进和变换都应属于本技术所附权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1