半导体存储装置的制作方法

半导体存储装置

1.[相关申请案]

[0002]

本技术案享有以日本专利申请案2020

‑

43028号(申请日:2020年3月12日)为基础申请案的优先权。本技术案通过参照该基础申请案而包含基础申请案的全部内容。

技术领域

[0003]

本实施方式关于一种半导体存储装置。

背景技术:

[0004]

已知有一种半导体存储装置,具备:半导体衬底,具备第1面及第2面;第1电极及第2电极,设置在半导体衬底的第1面侧;第3电极及第4电极,设置在半导体衬底的第2面侧;第1贯通电极,沿与第1面及第2面交叉的第1方向延伸且在第1方向的一端连接于第1电极,在第1方向的另一端连接于第3电极;以及第2贯通电极,沿第1方向延伸且在第1方向的一端连接于第2电极,在第1方向的另一端连接于第4电极。

技术实现要素:

[0005]

实施方式提供一种可靠性较高的半导体存储装置。

[0006]

一实施方式的半导体存储装置具备:半导体衬底,具备第1面及第2面;第1电极及第2电极,设置在半导体衬底的第1面侧;第3电极及第4电极,设置在半导体衬底的第2面侧;第1贯通电极,沿与第1面及第2面交叉的第1方向延伸,且在第1方向的一端连接于第1电极,在第1方向的另一端连接于第3电极;第2贯通电极,沿第1方向延伸,且在第1方向的一端连接于第2电极,在第1方向的另一端连接于第4电极;以及第1绝缘层,设置在半导体衬底与第1贯通电极之间及半导体衬底与第2贯通电极之间。另外,第1绝缘层具备:第1部分,设置在半导体衬底与第1贯通电极之间;以及第2部分,设置在半导体衬底与第2贯通电极之间。进而,半导体衬底在第2面侧设置着:n型的第1杂质区域,隔着第1部分而与第1贯通电极的外周面对向;以及n型的第2杂质区域,隔着第2部分而与第2贯通电极的外周面对向,且与第1杂质区域相分离。另外,在第1杂质区域与第2杂质区域之间,与第1杂质区域接触而设置着p型的第3杂质区域。

附图说明

[0007]

图1是表示第1实施方式的存储器系统10的构成的示意性的框图。

[0008]

图2是表示第1实施方式的存储器裸片md1的构成的示意性的框图。

[0009]

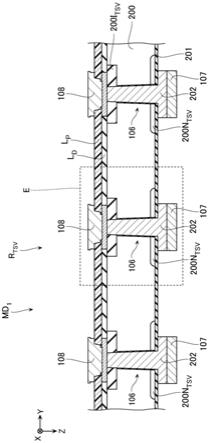

图3是表示第1实施方式的存储器系统10的构成例的示意性的剖视图。

[0010]

图4a是表示存储器裸片md1的构成例的示意性的仰视图。

[0011]

图4b是表示存储器裸片md1的构成例的示意性的剖视图。

[0012]

图4c是表示存储器裸片md1的构成例的示意性的俯视图。

[0013]

图5是表示存储器裸片md1的构成例的示意性的剖视图。

[0014]

图6是表示存储器裸片md1的构成例的示意性的剖视图。

[0015]

图7是表示存储器裸片md1的构成例的示意性的剖视图。

[0016]

图8~17是用来对存储器裸片md1的制造方法进行说明的示意性的剖视图。

[0017]

图18是表示第2实施方式的存储器裸片md2的构成例的示意性的剖视图。

[0018]

图19是表示存储器裸片md2的构成例的示意性的剖视图。

[0019]

图20~26是用来对存储器裸片md2的制造方法进行说明的示意性的剖视图。

[0020]

图27是表示第3实施方式的存储器裸片md3的构成例的示意性的剖视图。

[0021]

图28是表示其它实施方式的存储器裸片md4的构成例的示意性的俯视图。

[0022]

图29是表示存储器裸片md4的构成例的示意性的剖视图。

[0023]

图30是表示其它实施方式的存储器裸片md5的构成例的示意性的俯视图。

[0024]

图31是表示存储器裸片md5的构成例的示意性的剖视图。

[0025]

图32是表示存储器裸片md

n

的构成例的示意性的剖视图。

具体实施方式

[0026]

接下来,参照附图对实施方式的半导体存储装置详细地进行说明。此外,以下的实施方式只不过为一例,并不表示意图限定本发明。另外,以下的附图是示意性的图,为了方便说明,有时省略一部分构成等。另外,有时对在多个实施方式中共通的部分标注相同的符号并省略说明。

[0027]

另外,在本说明书中言及“半导体存储装置”的情况下,有时是指存储器裸片,也有时是指存储器芯片、存储卡、ssd(solid state drive,固态驱动器)等包含控制裸片的存储器系统。进而,也有时是指智能手机、平板终端、个人计算机等包含主机的构成。

[0028]

另外,在本说明书中,在言及第1构成“电连接”于第2构成的情况下,可为第1构成直接连接于第2构成,也可为第1构成经由配线、半导体构件或晶体管等而连接于第2构成。例如,在将3个晶体管串联连接的情况下,即便第2个晶体管为断开(off)状态,第1个晶体管也“电连接”于第3个晶体管。

[0029]

另外,在本说明书中,在言及第1构成在第2构成与第3构成“之间连接”的情况下,有时是指第1构成、第2构成及第3构成串联连接,且第1构成设置在第2构成及第3构成的电流路径上。

[0030]

另外,在本说明书中,有时将沿着特定面的方向称为第1方向,将沿着该特定面与第1方向交叉的方向称为第2方向,将与该特定面交叉的方向称为第3方向。这些第1方向、第2方向及第3方向可与说明书中所例示的x方向、y方向及z方向的任一个方向对应,也可不对应。

[0031]

[第1实施方式]

[0032]

图1是表示第1实施方式的存储器系统10的构成的示意性的框图。

[0033]

存储器系统10根据从主机20发送的信号,进行用户数据的读出、写入、抹除等。存储器系统10例如是存储器芯片、存储卡、ssd或其它的能够存储用户数据的系统。存储器系统10具备:多个存储器裸片md1,存储用户数据;以及控制裸片cd,连接于这些多个存储器裸片md1及主机20。控制裸片cd例如具备处理器、ram(random access memory,随机存取存储器)等,且进行逻辑地址与物理地址的转换、比特错误检测/纠正、垃圾回收(压缩)、损耗均

衡等处理。

[0034]

图2是表示第1实施方式的存储器裸片md1的构成的示意性的框图。此外,图2图示了多个控制端子等。这些多个控制端子存在表示为与高态有效信号(正逻辑信号)对应的控制端子的情况、表示为与低态有效信号(负逻辑信号)对应的控制端子的情况、以及表示为与高态有效信号及低态有效信号这两者对应的控制端子的情况。在图2中,与低态有效信号对应的控制端子的符号包含上线(overline)。在本说明书中,与低态有效信号对应的控制端子的符号包含斜杠(“/”)。

[0035]

如图2所示,存储器裸片md1具备存储数据的存储单元阵列mca、及连接于存储单元阵列mca的周边电路pc。周边电路pc具备电压产生电路vg、行解码器rd、感测放大器模块sam、及序列发生器sqc。另外,周边电路pc具备高速缓冲存储器cm、地址寄存器adr、指令寄存器cmr、及状态寄存器str。另外,周边电路pc具备输入输出控制电路i/o、及逻辑电路ctr。

[0036]

存储单元阵列mca包含多条位线、多条字线、以及连接于这些多条位线及字线的多个存储单元。这些多个存储单元存储1比特或多比特的数据。作为存储单元阵列mca,能够应用各种构成。例如,存储单元阵列mca也可在栅极绝缘膜包含电荷蓄积膜、强介电膜或其它存储器膜的存储器晶体管。另外,存储单元阵列mca也可为包含gesbte等硫属化物膜且硫属化物膜的结晶状态根据写入动作而变化的相变存储器。另外,存储单元阵列mca也可为包含对向配置的一对强磁性膜、及设置在这些强磁性膜之间的隧道绝缘膜,且所述强磁性膜的磁化方向根据写入动作而变化的mram(magnetoresistive random access memory,磁阻式随机存取存储器)。另外,存储单元阵列mca也可为包含一对电极、及设置在这些电极之间的金属氧化物等,且根据写入动作而所述电极彼此经由氧缺陷等丝状路径等导通的reram(resistance random access memory,阻变随机存取存储器)。另外,存储单元阵列mca也可为具备电容器及晶体管,且在写入动作及读出动作时进行对电容器的充放电的dram(dynamic random access memory,动态随机存取存储器)。另外,存储单元阵列mca也可具有其它构成。

[0037]

电压产生电路vg例如包含稳压器等降压电路、电荷泵电路等升压电路等。这些降压电路、升压电路等分别连接于供给电源电压v

cc

及接地电压v

ss

的端子。电压产生电路vg例如根据来自序列发生器sqc的控制信号,产生在对存储单元阵列mca的读出动作、写入动作及抹除动作时施加至位线、字线等的多种动作电压,并同时输出至多条电压供给线。从电压供给线输出的动作电压根据来自序列发生器sqc的控制信号而适当调整。

[0038]

行解码器rd例如具备:地址解码器,将地址数据add中的行地址ra解码;及开关电路,根据地址解码器的输出信号使存储单元阵列mca中的字线适当与电压供给线导通。

[0039]

感测放大器模块sam具备连接于存储单元阵列mca中的多条位线的多个感测放大器单元。感测放大器单元分别具备连接于位线的感测电路及开关电路、以及连接于这些感测电路及开关电路的锁存电路。锁存电路锁存从存储单元读出的读出数据及写入至存储单元的写入数据。感测电路在读出动作等时,将与位线的电压或电流的大小对应的数据作为读出数据锁存在锁存电路。开关电路在写入动作等时,与锁存在锁存电路的写入数据对应地,使与写入数据的各比特对应的电压供给线与位线导通。

[0040]

高速缓冲存储器cm经由数据总线dbus连接于感测放大器模块sam内的锁存电路。高速缓冲存储器cm具备与感测放大器模块sam内的多个锁存电路对应的多个锁存电路。在

高速缓冲存储器cm中锁存与读出数据及写入数据对应的数据dat。

[0041]

此外,感测放大器模块sam或高速缓冲存储器cm具备未图示的解码电路及开关电路。解码电路将保存在地址寄存器adr的列地址ca解码。开关电路也可为根据解码电路的输出信号,而使与列地址ca对应的锁存电路与总线db导通者。另外,开关电路也可为根据解码电路的输出信号,而使与列地址ca对应的位线与感测放大器单元导通者。

[0042]

序列发生器sqc将保存在指令寄存器cmr的指令数据cmd依次解码,并对行解码器rd、感测放大器模块sam、及电压产生电路vg输出内部控制信号。另外,序列发生器sqc适当将表示自身状态的状态数据st输出至状态寄存器str。另外,序列发生器sqc产生就绪/忙碌信号,并输出至端子ry/(/by)。

[0043]

输入输出控制电路i/o具备数据信号输入输出端子dq0~dq7、时钟信号输入输出端子dqs、/dqs、以及连接于数据信号输入输出端子dq0~dq7的比较器等输入电路及ocd(off chip driver,芯片外驱动器)电路等输出电路。另外,输入输出电路i/o具备连接于这些输入电路及输出电路的移位寄存器、以及缓冲电路。输入电路、输出电路、移位寄存器及缓冲电路分别连接于供给电源电压v

ccq

及接地电压v

ss

的端子。经由数据信号输入输出端子dq0~dq7输入的数据根据来自逻辑电路ctr的内部控制信号,从缓冲电路输出至高速缓冲存储器cm、地址寄存器adr或指令寄存器cmr。另外,经由数据信号输入输出端子dq0~dq7输出的数据根据来自逻辑电路ctr的内部控制信号,而从高速缓冲存储器cm或状态寄存器str输入至缓冲电路。

[0044]

逻辑电路ctr经由外部控制端子/ce、cle、ale、/we、re、/re从控制裸片cd接收外部控制信号,并根据外部控制信号对输入输出控制电路i/o输出内部控制信号。

[0045]

图3是表示第1实施方式的存储器系统10的构成例的示意性的剖视图。

[0046]

此外,在以下的说明中,表示存储器系统10具备8个存储器裸片md

1a

~md

1h

作为所述存储器裸片md1的例。但是,这样的构成只不过为例示,所安装的存储器裸片md1的数量能够适当调整。

[0047]

另外,在以下的说明中,将相对于图3所例示的安装衬底103的正面平行的特定方向称为x方向,将相对于该正面平行且与x方向垂直的方向称为y方向,将相对于该正面垂直的方向称为z方向。

[0048]

本实施方式的存储器系统10具备支持衬底101、积层在支持衬底101的多个存储器裸片md

1a

~md

1h

、及将这些多个存储器裸片md

1a

~md

1h

密封的树脂构件102。另外,本实施方式的存储器系统10具备连接于存储器裸片md

1h

的控制裸片cd、及安装这些构成的安装衬底103。

[0049]

支持衬底101例如也可为引线框架等金属板。支持衬底101的材料例如可为铜(cu)等,也可为42合金(fe

‑

ni系合金)等。另外,也可在支持衬底101设置着将支持衬底101与存储器裸片md

1a

连接的绝缘性的接着剂104。

[0050]

多个存储器裸片md

1a

~md

1h

分别以正面成为安装衬底103侧、背面成为与安装衬底103相反侧的方式配置。另外,多个存储器裸片md

1a

~md

1h

排列在z方向。另外,多个存储器裸片md

1a

~md

1h

分别具备:多个贯通导电部106,从存储器裸片md

1b

~md

1h

的背面(图3中的上表面)以至正面(图3中的下表面)设置;背面电极107,连接于这些多个贯通电极的背面侧的端部(图3中的上端部);及正面电极108,其连接于这些多个贯通电极的正面侧的端部(图3中

的下端部)。此外,存储器裸片md

1a

可具有贯通导电部106及背面电极107,也可不具有贯通导电部106及背面电极107。这些多个存储器裸片md

1a

~md

1h

经由贯通导电部106、背面电极107及正面电极108而相互电连接。

[0051]

此外,像参照图2所说明的一样,存储器裸片md

1a

~md

1h

具备多个端子。图3的贯通导电部106作为这些多个端子的任一个端子发挥功能。例如,这些多个贯通导电部106中的一部分作为供给电源电压v

cc

、电源电压v

ccq

或接地电压v

ss

的端子发挥功能。另外,这些多个贯通导电部106中的一部分作为数据信号输入输出端子dq0~dq7发挥功能。另外,这些多个贯通导电部106中的一部分作为时钟信号输入输出端子dqs、/dqs发挥功能。另外,这些多个贯通导电部106中的一部分作为外部控制端子/ce、cle、ale、/we、re、/re发挥功能。另外,这些多个贯通导电部106中的一部分作为端子ry/(/by)发挥功能。

[0052]

另外,存储器裸片md

1h

的正面(图3中的下表面)具备设置在存储器裸片md

1h

的正面的连接配线109、与正面电极108及连接配线109对应地设置的连接电极110、设置在连接配线109的焊垫电极111。

[0053]

控制裸片cd以正面成为与安装衬底103相反侧、背面成为安装衬底103侧的方式配置。控制裸片cd具备设置在正面(图3中的上表面)的多个连接电极112a、112b。这些多个连接电极分别连接于设置在存储器裸片md

1h

的连接电极110。控制裸片cd经由多个连接电极112a而与多个存储器裸片md

1a

~md

1h

电连接。另外,控制裸片cd经由多个连接电极112b而与主机20(图1)电连接。

[0054]

在安装衬底103的正面(图3中的上表面)设置着印刷配线113、以及覆盖安装衬底103的正面及印刷配线113的侧面的阻焊剂114。印刷配线113经由凸块电极115连接于设置在存储器裸片md

1h

的正面的焊垫电极111。

[0055]

在安装衬底103的背面(图3中的下表面)设置着印刷配线116、以及覆盖安装衬底103的背面及印刷配线116的侧面的阻焊剂117。印刷配线116与设置在正面的印刷配线113电连接。另外,在印刷配线116的一部分设置着凸块电极118。

[0056]

此外,设置在安装衬底103的正面侧的支持衬底101、存储器裸片md

1a

~md

1h

及控制裸片cd利用树脂构件119而密封。

[0057]

此外,图3所示的构成只不过为例示,具体的构成能够适当调整。例如,在图3所示的例中,存储器裸片md

1a

~md

1h

及控制裸片cd设置在安装衬底103。在这样的构成中,多个存储器裸片md1及控制裸片cd包含在一个封装内。然而,控制裸片cd也可包含在与存储器裸片md1不同的封装。

[0058]

图4a是表示存储器裸片md1的构成例的示意性的仰视图。

[0059]

如图4a所示,存储器裸片md1具备半导体衬底200。在图示的例中,在半导体衬底200设置着排列在x方向的2个存储单元阵列区域r

mca

。另外,在这些存储单元阵列区域r

mca

之间设置着贯通电极区域r

tsv

。另外,在半导体衬底200的y方向的端部设置着沿x方向延伸的周边电路区域r

pc

。

[0060]

图4b是表示存储器裸片md1的构成例的示意性的剖视图。图4b中表示了将图4a所示的构成沿着a

‑

a'线、b

‑

b'线、c

‑

c'线切断且从箭头方向观察的截面。

[0061]

如图4b所示,存储器裸片md1具备设置在半导体衬底200的正面的元件层l

d

、及设置在元件层l

d

的正面侧保护层l

p

。

[0062]

半导体衬底200例如是包括包含硼(b)或其它p型杂质的p型硅(si)的半导体衬底。在半导体衬底200的正面(图4b中的上表面)例如设置着包含磷(p)、砷(as)或其它n型杂质的n型阱区域200n、包含硼(b)或其它p型杂质的p型阱区域200p、及绝缘区域200i。

[0063]

例如,在半导体衬底200的正面(图4b中的上表面)中与存储单元阵列区域r

mca

对应的部分,形成有包含n型阱区域200n及p型阱区域200p的双重阱构造。p型阱区域200p作为存储单元阵列mca(图2)的一部分发挥功能。

[0064]

另外,例如,在半导体衬底200的正面(图4b中的上表面)中与周边电路区域r

pc

对应的部分,存在由晶体管tr、电容器等构成的周边电路pc。

[0065]

另外,例如,在半导体衬底200的正面(图4b中的上表面)中与贯通电极区域r

tsv

对应的部分,也可设置着绝缘区域200i

tsv

。另外,在半导体衬底200的背面(图4b中的下表面)中与贯通电极区域r

tsv

对应的部分,设置着n型的杂质区域200n

tsv

。杂质区域200n

tsv

沿着半导体衬底200的背面设置。n型的杂质区域200n

tsv

例如包含磷(p)、砷(as)或其它n型的杂质。另外,在半导体衬底200中与贯通电极区域r

tsv

对应的部分,设置着从所述绝缘区域200i

tsv

以至所述杂质区域200n

tsv

贯通半导体衬底200的贯通孔h

tsv1

。另外,在该贯通孔h

tsv1

的内周面设置着氧化硅(sio2)等绝缘层201。另外,在该贯通孔h

tsv1

的内部,介隔绝缘层201设置着衬底贯通电极202。衬底贯通电极202作为所述贯通导电部106(图3、图4a)的一部分发挥功能。

[0066]

在元件层l

d

的存储单元阵列区域r

mca

,设置着排列在y方向的多个存储器区块blk。存储器区块blk具备排列在z方向的多个导电层210、沿z方向延伸的多个半导体层220、以及分别设置在多个导电层210与多个半导体层220之间的多个栅极绝缘膜230。导电层210是沿x方向延伸的大致板状的导电层。导电层210也可包含氮化钛(tin)等障壁导电膜及钨(w)等金属膜的积层膜等。半导体层220沿x方向及y方向以特定的图案排列。半导体层220例如是多晶硅(si)等半导体层。栅极绝缘膜230例如具备氧化硅(sio2)等隧道绝缘膜、氮化硅(sin)等电荷蓄积膜、及氧化硅(sio2)等阻挡绝缘膜。此外,栅极绝缘膜230也可具备多晶硅等浮动栅极来代替氮化硅(sin)等电荷蓄积膜。

[0067]

另外,在元件层l

d

的存储单元阵列区域r

mca

,设置着沿z方向延伸且连接于半导体衬底200的正面的导电层240。另外,在该导电层240与半导体衬底200的连接部分,设置着n型的杂质区域241。导电层240例如设置在存储器区块blk之间。导电层240例如也可包含氮化钛(tin)等障壁导电膜及钨(w)等金属膜的积层膜等。对n型的杂质区域241例如注入着磷(p)、砷(as)或其它n型的杂质。

[0068]

在元件层l

d

的周边电路区域r

pc

及贯通电极区域r

tsv

,设置着设置在半导体衬底200的正面的多个绝缘层251、设置在多个绝缘层251的正面的多个半导体层252、设置在多个半导体层252的正面的多个绝缘层253、设置在多个绝缘层253的正面的多个导电层254、及设置在多个导电层254的正面的多个绝缘层255。绝缘层251例如包含氧化硅(sio2)等。半导体层252例如包含多晶硅(si)等。绝缘层253例如包含氧化硅(sio2)等。导电层254例如包含多晶硅(si)与钨(w)等金属膜的积层膜等。绝缘层255例如包含氮化硅(sin)等。

[0069]

在这些构成(绝缘层251、半导体层252、绝缘层253、导电层254、绝缘层255)中设置在周边电路区域r

pc

者的至少一部分作为晶体管tr的一部分发挥功能。这样的半导体层252与半导体衬底200的除绝缘区域200i以外的区域对向。另外,这样的导电层254连接于半导

体层252。

[0070]

另外,在这些构成(绝缘层251、半导体层252、绝缘层253、导电层254、绝缘层255)中设置在贯通电极区域r

tsv

者的至少一部分作为所述贯通导电部106(图3、图4a)的一部分发挥功能。这样的半导体层252例如与半导体衬底200的绝缘区域200i

tsv

对向。另外,这样的导电层254连接于半导体层252。

[0071]

另外,在元件层l

d

的周边电路区域r

pc

及贯通电极区域r

tsv

,设置着沿z方向延伸且连接于导电层254的接点cs1、及沿z方向延伸且连接于半导体衬底200的正面的接点cs2。另外,在接点cs2与半导体衬底200的连接部分设置着杂质区域256。接点cs1、cs2例如也可包含氮化钛(tin)等障壁导电膜及钨(w)等金属膜的积层膜等。可对杂质区域256例如注入磷(p)、砷(as)或其它n型的杂质,也可注入硼(b)或其它p型的杂质。

[0072]

这些构成(接点cs1、接点cs2)中设置在周边电路区域r

pc

者的至少一部分与所述晶体管tr一起作为所述周边电路pc(图2)的一部分发挥功能。

[0073]

另外,这些构成(接点cs2)中设置在贯通电极区域r

tsv

者的至少一部分作为所述贯通导电部106(图3、图4a)的一部分发挥功能。

[0074]

另外,在元件层l

d

的存储单元阵列区域r

mca

、周边电路区域r

pc

及贯通电极区域r

tsv

,设置着设置在比存储器区块blk、导电层240等靠存储器裸片md1的正面侧(图4b的上方)的金属配线层m0、m1、m2。金属配线层m0具备多条配线m0。这些多条配线m0也可包含氮化钛(tin)等障壁导电膜及钨(w)等金属膜的积层膜等。金属配线层m1具备多条配线m1。这些多条配线m1也可包含氮化钛(tin)等障壁导电膜及铜(cu)等金属膜的积层膜等。金属配线层m2具备多条配线m2。这些多条配线m2也可包含氮化钛(tin)等障壁导电膜及铝(al)等金属膜的积层膜等。

[0075]

金属配线层m0中的多条配线m0中设置在存储单元阵列区域r

mca

的配线m0

mca

连接于导电层240。金属配线层m1中的多条配线m1中设置在存储单元阵列区域r

mca

的配线m1

mca

连接于半导体层220。

[0076]

另外,金属配线层m0、m1、m2中的多条配线m0、m1、m2中设置在周边电路区域r

pc

的配线m0

pc

、m1

pc

、m2

pc

连接于接点cs1、cs2。这些配线m0

pc

、m1

pc

、m2

pc

与所述晶体管tr一起作为所述周边电路pc(图2)的一部分发挥功能。

[0077]

另外,金属配线层m0、m1、m2中的多条配线m0、m1、m2中设置在贯通电极区域r

tsv

的配线m0

tsv

、m1

tsv

、m2

tsv

连接于接点cs1。这些配线m0

tsv

、m1

tsv

、m2

tsv

作为所述贯通导电部106(图3、图4a)的一部分发挥功能。另外,虽然省略图示,但是这些构成中的一部分连接于配线m0

pc

、m1

pc

、m2

pc

。

[0078]

正面侧保护层l

p

具备设置在元件层l

d

的正面(图4b中的上表面)的无机系保护膜261、及设置在该无机系保护膜261的正面的有机系保护膜262。无机系保护膜261例如包含氧化硅(sio2)、氮化硅(sin)或包含这些的积层膜。有机系保护膜262例如包含聚酰亚胺系的树脂、或酚系的树脂。

[0079]

例如,在正面侧保护层l

p

中与贯通电极区域r

tsv

对应的部分,设置着贯通无机系保护膜261及有机系保护膜262的贯通孔h

tsv2

。另外,在该贯通孔h

tsv2

的内部设置着参照图3所说明的正面电极108。

[0080]

图4c是表示存储器裸片md1的构成例的示意性的俯视图。图4c表示了将图4a所示

的构成颠倒后观察的截面。图5是表示存储器裸片md1的构成例的示意性的剖视图。图5表示了将图4a所示的构成沿着d

‑

d'线切断且从箭头方向观察的截面。

[0081]

如图5所示,在本实施方式的存储器裸片md1的贯通电极区域r

tsv

,设置着相分离配置的多个贯通导电部106。另外,在半导体衬底200的背面(图5中的下表面),与这些多个贯通导电部106对应地设置着多个杂质区域200n

tsv

。这些多个杂质区域200n

tsv

相互分离而配置。另外,这些多个杂质区域200n

tsv

分别介隔绝缘层201而与衬底贯通电极202的外周面对向。另外,如图4c所示,这些多个杂质区域200n

tsv

分别以在半导体衬底200的背面中遍及全周包围衬底贯通电极202的外周面的方式设置。

[0082]

图6及图7是表示存储器裸片md1的构成例的示意性的剖视图。图6表示了由图5的e所示的部分的放大图。图7表示由图6的f所示的部分的放大图。

[0083]

例如,如图6所示,本实施方式的绝缘层201具备氧化硅(sio2)等绝缘层311、氮化硅(sin)等绝缘层312、氧化硅(sio2)等绝缘层313。绝缘层311、绝缘层312及绝缘层313设置在半导体衬底200的背面。另外,绝缘层313具备设置在贯通孔h

tsv1

的内周面的部分,该贯通孔h

tsv1

设置在半导体衬底200。

[0084]

另外,例如,如图6所示,本实施方式的衬底贯通电极202具备氮化钛(tin)等障壁导电层321、铜(cu)等晶种层322、及镍(ni)等金属层323。这些构成沿着设置在半导体衬底200的贯通孔h

tsv1

的内周面沿z方向延伸。另外,例如,如图7所示,这些构成连接于元件层l

d

中的配线m0

tsv

、m1

tsv

、m2

tsv

等构成。

[0085]

另外,例如,如图6所示,本实施方式的背面电极107具备铜(cu)等基底金属层371、及包含锡(sn)等的凸块电极372。这些构成设置在衬底贯通电极202的存储器裸片md1的背面侧的面(图6中的下表面)。

[0086]

另外,例如,如图6所示,本实施方式的正面电极108具备氮化钛(tin)等障壁导电层381、包含镍(ni)等的凸块电极382、及金(au)等金属层383。障壁导电层381沿着贯通孔h

tsv2

的内周面及底面设置。凸块电极382填埋在贯通孔h

tsv2

的内部。金属层383覆盖凸块电极382的图6中的上表面。

[0087]

接下来,参照图8~图17,对本实施方式的存储器裸片md1的制造方法进行说明。图8~图17是用来对该制造方法进行说明的示意性的剖视图。图8~图12表示了与图5对应的部分。图13~图17表示了与图6对应的部分。

[0088]

图8所示的构造具备半导体衬底200a、设置在半导体衬底200a的正面的元件层l

d

、设置在元件层l

d

的正面的正面侧保护层l

p

、设置在正面侧保护层l

p

的正面电极108、覆盖正面侧保护层l

p

及正面电极108的接着剂层s1、以及经由接着剂层s1连接于正面侧保护层l

p

及正面电极108的支持衬底s2。半导体衬底200a基本上与参照图4a等所说明的半导体衬底200相同地构成。然而,半导体衬底200a具有大于半导体衬底200的厚度。另外,在半导体衬底200a的背面未设置杂质区域200n

tsv

。另外,在半导体衬底200a未设置贯通孔h

tsv1

。

[0089]

在本实施方式的制造方法中,如图9所示,削掉半导体衬底200a的背面的一部分,使半导体衬底200a的z方向的厚度变小。

[0090]

接下来,如图10所示,在半导体衬底200a的背面涂布抗蚀剂r1。另外,通过光刻法等方法进行图案化,在抗蚀剂r1形成开口op1。

[0091]

接下来,如图11所示,经由开口op1对半导体衬底200a的背面注入磷(p)、砷(as)或

其它n型的杂质。由此,在半导体衬底200a的背面形成杂质区域200n

tsv

。

[0092]

接下来,如图12所示,剥离抗蚀剂r1。

[0093]

接下来,如图13所示,在半导体衬底200a的背面形成绝缘层311及绝缘层312。该工序例如通过cvd(chemical vapor deposition,化学气相沉积)等方法而进行。

[0094]

接下来,如图14所示,在半导体衬底200a的背面涂布抗蚀剂r2。另外,通过光刻法等方法而进行图案化,在抗蚀剂r2形成开口op2。

[0095]

接下来,如图15所示,经由开口op2,在半导体衬底200a形成贯通孔h

tsv1

。该工序例如通过rie(reactive ion etching,反应性离子蚀刻)等方法而进行。通过该工序而形成半导体衬底200。

[0096]

接下来,如图16所示,剥离抗蚀剂r2。

[0097]

接下来,如图17所示,在绝缘层312的正面(图17中的下表面)以及贯通孔h

tsv1

的内周面及底面形成绝缘层313。该工序例如通过cvd等方法而进行。通过该工序,形成绝缘层201。

[0098]

然后,在贯通孔h

tsv1

的内部形成衬底贯通电极202(图6),在衬底贯通电极202的一端(图6中的下表面)形成背面电极107,由此形成如参照图4a至图7所说明的存储器裸片md1。另外,将已形成的存储器裸片md1在支持衬底101(图3)积层多个,将这些构成搭载在安装衬底103(图3),通过树脂构件119(图3)而密封,由此形成如参照图3所说明的存储器系统10。

[0099]

此处,在这样的存储器系统10的制造工序中,存在绝缘层313(图6)中设置在半导体衬底200的背面与贯通孔h

tsv1

的交界附近的部分(由图6的g所示的部分)产生裂痕的情况。此处,例如在对半导体衬底200供给接地电压v

ss

,对衬底贯通电极202供给大于接地电压v

ss

的电压的情况下,有在半导体衬底200与衬底贯通电极202之间产生泄漏电流的可能性。

[0100]

因此,在本实施方式中,在半导体衬底200的背面与贯通孔h

tsv1

的交界附近,设置着n型的杂质区域200n

tsv

。根据这样的构成,即使绝缘层313的所述部分产生裂痕,也通过耗尽层而将杂质区域200n

tsv

与半导体衬底200的其它部分电切断,从而能够抑制所述泄漏电流。

[0101]

另外,在本实施方式中,例如,如参照图4c及图5所说明,在半导体衬底200的背面,设置着与多个衬底贯通电极202对应的多个杂质区域200n

tsv

。根据这样的构成,例如,即便在供给接地电压v

ss

的衬底贯通电极202的附近产生绝缘层313的裂痕,且供给电源电压v

cc

或电源电压v

ccq

的衬底贯通电极202的附近产生绝缘层313的裂痕的情况下,也可使各杂质区域200n

tsv

为电独立的状态。由此,能够抑制衬底贯通电极202之间的泄漏电流。

[0102]

[第2实施方式]

[0103]

图18及图19是表示第2实施方式的存储器系统的构成例的示意性的剖视图。图19表示了由图18的h所示的部分的放大图。

[0104]

本实施方式的存储器系统基本上与第1实施方式的存储器系统10相同地构成。但是,本实施方式的存储器系统具备存储器裸片md2来代替存储器裸片md1。存储器裸片md2基本上与存储器裸片md1相同地构成。但是,本实施方式的存储器裸片md2具备半导体衬底200'来代替半导体衬底200。本实施方式的半导体衬底200'基本上与半导体衬底200相同地构成。但是,未在本实施方式的半导体衬底200'的背面设置杂质区域200n

tsv

。另外,在形成在

本实施方式的半导体衬底200'的贯通孔h

tsv1

的内周面设置着杂质区域200n

tsv

'。杂质区域200n

tsv

'沿着贯通孔h

tsv1

的内周面沿z方向延伸。此外,该杂质区域200n

tsv

'沿着衬底贯通电极202的外周面沿z方向延伸。

[0105]

接下来,参照图20~图26,对本实施方式的存储器裸片md2的制造方法进行说明。图20~图26是用来对该制造方法进行说明的示意性的剖视图。图20~图26表示了与图19对应的部分。

[0106]

本实施方式的制造方法至参照图9所说明的工序为止,与第1实施方式的制造方法相同。

[0107]

在本实施方式的制造方法中,如图20所示,在半导体衬底200a的背面形成绝缘层311及绝缘层312。该工序例如通过cvd等方法而进行。

[0108]

接下来,如图21所示,在半导体衬底200a的背面涂布抗蚀剂r2。另外,通过光刻法等方法而进行图案化,在抗蚀剂r2形成开口op2。

[0109]

接下来,如图22所示,经由开口op2而在半导体衬底200a形成贯通孔h

tsv1

。该工序例如通过rie等方法而进行。

[0110]

接下来,如图23及图24所示,经由开口op2对贯通孔h

tsv1

的内周面注入磷(p)、砷(as)或其它n型的杂质。在该工序中,对半导体衬底200a的背面从倾斜方向(与z方向交叉的方向)注入杂质。在该工序中,例如也可将注入杂质的工序、与以z轴为中心使半导体衬底200a旋转的工序交替地进行复数次。另外,在该工序中,例如,也可一边以z轴为中心使半导体衬底200a旋转一边注入杂质。通过该工序,形成半导体衬底200'。

[0111]

接下来,如图25所示,剥离抗蚀剂r2。

[0112]

接下来,如图26所示,在绝缘层312的正面(图26中的下表面)、以及贯通孔h

tsv1

的内周面及底面形成绝缘层313。该工序例如通过cvd等方法而进行。通过该工序而形成绝缘层201。

[0113]

然后,在贯通孔h

tsv1

的内部形成衬底贯通电极202(图18、图19),在衬底贯通电极202的一端(图18、图19中的下表面)形成背面电极107,由此,形成如参照图18、图19所说明的存储器裸片md2。另外,将已形成的存储器裸片md2在支持衬底101(图3)积层多个,将这些构成搭载在安装衬底103(图3),通过树脂构件119(图3)而密封,由此形成第2实施方式的存储器系统。

[0114]

在第2实施方式中,也与第1实施方式相同地,能够抑制衬底贯通电极202、与半导体衬底200'的除杂质区域200n

tsv

'以外的区域之间的泄漏电流。

[0115]

另外,在第2实施方式中,也与第1实施方式相同地,能够抑制衬底贯通电极202之间的泄漏电流。

[0116]

另外,在第1实施方式中,例如,在参照图10所说明的工序中在半导体衬底200a的背面形成使用在杂质的注入的抗蚀剂r1,在参照图14所说明的工序中在半导体衬底200a的背面形成使用在贯通孔h

tsv1

的形成的抗蚀剂r2。另一方面,在第2实施方式中,例如,如参照图21~图24所说明,杂质的注入及贯通孔h

tsv1

的形成均使用抗蚀剂r2。根据第2实施方式的方法,存在通过省略抗蚀剂r1的涂布工序及图案化工序,而能够比第1实施方式的方法廉价地制造半导体存储装置的情况。

[0117]

[第3实施方式]

[0118]

图27是表示第3实施方式的存储器系统的构成例的示意性的剖视图。

[0119]

本实施方式的存储器系统基本上与第1实施方式的存储器系统10相同地构成。但是,本实施方式的存储器系统具备存储器裸片md3来代替存储器裸片md1。存储器裸片md3基本上与存储器裸片md1相同地构成。但是,本实施方式的存储器裸片md3具备半导体衬底200”来代替半导体衬底200。本实施方式的半导体衬底200”基本上与半导体衬底200相同地构成。但是,未在本实施方式的半导体衬底200”的背面设置杂质区域200n

tsv

。另外,在本实施方式的半导体衬底200”的背面及贯通孔h

tsv1

的内周面设置着杂质区域200n

tsv”。杂质区域200n

tsv”具备与杂质区域200n

tsv

相同地形成的背面部200n1、及与杂质区域200n

tsv

'相同地形成的贯通孔部200n2。

[0120]

本实施方式的制造方法至参照图15所说明的工序为止,与第1实施方式的制造方法相同。在本实施方式的制造方法中,对图15所示的构造,与第2实施方式的制造方法相同地进行参照图23等所说明的工序以后的工序。

[0121]

在第3实施方式中,也与第1实施方式相同地,能够抑制衬底贯通电极202、与半导体衬底200”的除杂质区域200n

tsv”以外的区域之间的泄漏电流。

[0122]

另外,在第3实施方式中,与第1实施方式相同地,能够抑制衬底贯通电极202之间的泄漏电流。

[0123]

另外,第3实施方式的杂质区域200n

tsv”具备与杂质区域200n

tsv

相同地形成的背面部200n1、及与杂质区域200n

tsv

'相同地形成的贯通孔部200n2。因此,在如上所述的裂痕朝向半导体衬底200”的正面侧延伸的情况下,朝向半导体衬底200”的背面侧延伸的情况下,均能够较佳地抑制泄漏电流。

[0124]

[其它实施方式]

[0125]

以上,对第1实施方式~第3实施方式的半导体存储装置进行了说明。然而,这些实施方式的半导体存储装置只不过为例示,具体的构成、动作等能够适当调整。

[0126]

例如,如参照图4c及图5所说明,在第1实施方式中,设置在半导体衬底200的背面的多个杂质区域200n

tsv

相互分离而配置。然而,例如,如图28所示,当在x方向或y方向上相邻的2个以上的衬底贯通电极202均作为供给电源电压v

cc

的端子发挥功能的情况下,与这些衬底贯通电极202对应的杂质区域200n

tsv”'也可设为共通的区域。此外,例如,如图29所示,与这样的衬底贯通电极202对应的配线m0

tsv

、m1

tsv

、m2

tsv

的至少一者也可相互连接。关于供给电源电压v

ccq

的端子、及供给接地电压v

ss

的端子也相同。

[0127]

另外,如参照图4c等所说明,在第1实施方式中,关于设置在存储器裸片md1的所有衬底贯通电极202,表示了设置与这些对应的杂质区域200n

tsv

的示例。然而,例如,如图30及图31所示,关于多个衬底贯通电极202中作为供给接地电压v

ss

的端子发挥功能的衬底贯通电极202,也可省略与这些对应的杂质区域200n

tsv

。

[0128]

另外,在第1实施方式~第3实施方式中,对半导体衬底200、200'、200”是p型的半导体衬底,杂质区域200n

tsv

、200n

tsv

'、200n

tsv”是n型的杂质区域的示例进行了说明。然而,例如,也可设置n型的半导体衬底来代替p型的半导体衬底,设置p型的杂质区域来代替n型的杂质区域。

[0129]

例如,图32所例示的存储器裸片md

n

基本上与第1实施方式的存储器裸片md1相同地构成。但是,存储器裸片md

n

具备半导体衬底400来代替半导体衬底200。半导体衬底400基本

上与半导体衬底200相同地构成。但是,半导体衬底400是n型的半导体衬底而并非p型的半导体衬底。另外,未在半导体衬底400的背面设置杂质区域200n

tsv

。另外,在半导体衬底400的背面设置着杂质区域400p

tsv

。杂质区域400p

tsv

基本上与第1实施方式的杂质区域200n

tsv

相同地构成。但是,杂质区域400p

tsv

是p型的杂质区域而并非n型的杂质区域。此外,在图示的例中,杂质区域400p

tsv

设置在与第1实施方式的杂质区域200n

tsv

相同的范围。然而,例如,也可将杂质区域400p

tsv

设置在与第2实施方式的杂质区域200n

tsv

'或第3实施方式的杂质区域200n

tsv”相同的范围。

[0130]

对本发明的几个实施方式进行了说明,但这些实施方式是作为示例而提出的,并不旨在限定发明的范围。这些新颖的实施方式能够以其它各种方式实施,可在不脱离发明的主旨的范围内进行各种省略、置换、变更。这些实施方式或其变化包含在发明的范围或主旨中,并且包含在权利要求书中所记载的发明及其均等范围中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1