一种内嵌硅控整流器的PMOS型ESD器件及其实现方法与流程

本发明涉及半导体集成电路技术领域,特别是涉及一种用于防静电保护设计的内嵌硅控整流器的pmos型esd器件及其实现方法。

背景技术:

在集成电路防静电保护设计领域,防静电保护设计窗口一般取决于工作电压和内部受保护电路的栅氧化层厚度,以某公司55lp先进工艺平台为例,核心器件(1.2vmosfet)的工作电压为1.2v,栅氧化层厚度为25a,所以某公司55lp先进工艺平台核心器件(1.2vmosfet)的防静电保护设计窗口通常为1.32v~5v之间。然而,该公司55lp先进工艺平台核心器件(1.2vnmos)的回滞效应特性曲线如图1所示,表明核心器件的触发电压(vt1,右侧曲线较低位置拐点对应电压)为6.7v,超出核心器件的防静电保护设计窗口,如果将该核心器件(1.2vnmos)直接用于防静电保护设计,极易导致核心器件(1.2vmosfet)的栅氧化层发生可靠性问题。

业界某文献于2015年首先提出了一种如图2所示的内嵌硅控整流器的pmos型esd器件试图解决先进工艺平台核心器件的防静电保护设计问题,根据图2的器件结构,可以得出其对应的如图3所示的等效电路图。

根据已存在的内嵌硅控整流器的pmos型esd器件的等效电路图,可以得出该pmos(22/40/20/60)器件本身漏极22/28构成其内嵌硅控整流器内部寄生npn三极管(60/28/30)的基极,其触发机制是利用pmos器件漏极的击穿(breakdown)产生的漏电流来触发其内嵌的硅控整流器的回滞效应,所以已存在的内嵌硅控整流器的pmos型esd器件的回滞效应的触发电压(vt1)是由该pmos型esd器件的漏极击穿电压决定的。该文献所报道的该内嵌硅控整流器的pmos器件在某工艺平台中实际测到回滞效应曲线如下图4a中proposedscr1(正三角)对应的曲线,为了看到清晰数据,将图4a左下角虚框内予以放大观察得到图4b,该曲线表明已存在的内嵌硅控整流器的pmos器件的触发电压(vt1),左下侧曲线较低位置中间拐点对应电压)为5.5v左右,可见该已存在的内嵌硅控整流器的pmos器件相较于传统的硅控整流器确实可以大幅降低其回滞效应的触发电压(vt1),但仍然超过了一般先进cmos工艺平台的核心器件的防静电保护设计窗口,因此需要进一步降低其回滞效应的触发电压。

技术实现要素:

为克服上述现有技术存在的不足,本发明之目的在于提供一种内嵌硅控整流器的pmos型esd器件及实现方法,以实现一种更容易降低内嵌硅控整流器的触发电压的pmos型esd器件。

为达上述及其它目的,本发明提出一种内嵌硅控整流器的pmos型esd器件,其特征在于,所述内嵌硅控整流器的pmos型esd器件包括:

半导体衬底(80);

生成于所述半导体衬底(80)中的n阱(60);

高浓度n型掺杂(32)、高浓度p型掺杂(20)、高浓度p型掺杂(22)、高浓度n型掺杂(30)、高浓度p型掺杂(24)依次置于所述n阱(60)上部,并且高浓度p型掺杂(22)、高浓度n型掺杂(30)、高浓度p型掺杂(24)及其中间的间隔部分的正下方设置一层p型esd掺杂(28);

所述高浓度p型掺杂(20)与所述高浓度p型掺杂(22)间为所述n阱(60)的一部分,在该部分n阱上方放置p型栅(40);

在所述高浓度n型掺杂(32)的上方、高浓度p型掺杂(20)上方分别生成金属硅化物(50)并引出电极相连并组成所述pmos型esd器件的阳极;在所述高浓度n型掺杂(30)和高浓度p型掺杂(24)的上方分别生成金属硅化物(50)并引出电极相连作为所述pmos型esd器件的阴极,并于该阳极与阴极之间设置rc延时电路调节所述p型栅(40)的栅极电压。

优选地,所述阳极和p型栅(40)间连接一电阻,所述p型栅(40)和阴极间连接一电容。

优选地,所述电阻的取值范围为100ω~1mω。

优选地,所述电容的取值范围为100ff~10pf。

优选地,所述rc延时电路的时间常数设定为1ns~100ns。

优选地,所述高浓度n型掺杂(32)、高浓度p型掺杂(20)置于所述n阱(60)的左上部,高浓度p型掺杂(22)、高浓度n型掺杂(30)、高浓度p型掺杂(24)置于n阱(60)的右上部。

优选地,所述高浓度n型掺杂(32)、高浓度p型掺杂(20)间用浅沟道隔离层(10)隔离,所述高浓度n型掺杂(32)的左侧为浅沟道隔离层(10),所述高浓度n型掺杂(24)和p型esd掺杂(28)的右侧为浅沟道隔离层(10)。

为达到上述目的,本发明还提供一种内嵌硅控整流器的pmos型esd器件的实现方法,所述方法将现有内嵌硅控整流器的pmos型esd器件中直接与阳极相连的p型栅(40)断开,于阳极与阴极之间设置rc延时电路调节所述p型栅(40)的栅极电压。

优选地,所述方法包括如下步骤:

步骤s1,提供一半导体衬底;

步骤s2,在该p型衬底(80)中生成一个n阱(60),高浓度n型掺杂(32)、高浓度p型掺杂(20)、高浓度p型掺杂(22)、高浓度n型掺杂(30)、高浓度p型掺杂(24)依次生成于所述n阱(60)上部,并且高浓度p型掺杂(22)、高浓度n型掺杂(30)、高浓度p型掺杂(24)及其中间的间隔部分的正下方生成一层p型esd掺杂(28);

步骤s3,所述高浓度p型掺杂(20)与所述高浓度p型掺杂(22)间为所述n阱(60)的一部分,在该部分n阱上方生成p型栅(40);

步骤s4,在所述高浓度n型掺杂(32)与高浓度p型掺杂(20)上方分别生成金属硅化物(50)并引出电极相连并组成所述pmos型esd器件的阳极;在所述高浓度n型掺杂(30)和高浓度p型掺杂(24)的上方分别生成金属硅化物(50)并引出电极相连作为所述pmos型esd器件的阴极,并于该阳极与阴极之间设置rc延时电路调节所述p型栅(40)的栅极电压。

优选地,所述阳极和p型栅(40)间连接一电阻,所述p型栅(40)和阴极间连接一电容。

与现有技术相比,本发明一种内嵌硅控整流器的pmos型esd器件及其实现方法通过将现有内嵌硅控整流器的pmos型esd器件中p型栅极40与阳极的连接断开,而用rc延时电路调节控制该pmos型esd器件的栅极电压,当esd脉冲施加在该pmos型esd器件的阳极时,该pmos型esd器件因为rc延时电路对栅极电压的调节而处于导通状态,导通之后的pmos协助触发该pmos型esd器件内嵌的硅控整流器,相较于现有的内嵌硅控整流器的pmos器件利用pmos器件的击穿来协助触发该pmos器件内嵌的硅控整流器,本发明更容易降低内嵌硅控整流器的触发电压。

附图说明

图1为某公司55lp工艺平台1.2vggnmos回滞效应特性曲线;

图2为现有一种内嵌硅控整流器的pmos型esd器件的结构图;

图3为现有内嵌硅控整流器的pmos型esd器件的等效电路图;

图4a为现有内嵌硅控整流器的pmos器件的回滞效应特性曲线图;

图4b为现有内嵌硅控整流器的pmos器件的回滞效应特性曲线细节放大图;

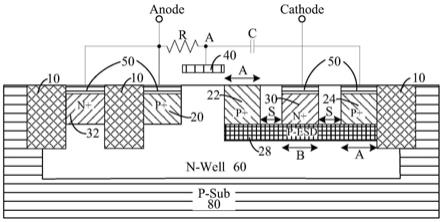

图5为本发明一种内嵌硅控整流器的pmos型esd器件之较佳实施例的器件结构图;

图6为本发明之内嵌硅控整流器的pmos型esd器件的等效电路图;

图7为本发明一种内嵌硅控整流器的pmos型esd器件的实现方法的步骤流程图;

图8为本发明的应用场景示意图。

具体实施方式

以下通过特定的具体实例并结合附图说明本发明的实施方式,本领域技术人员可由本说明书所揭示的内容轻易地了解本发明的其它优点与功效。本发明亦可通过其它不同的具体实例加以施行或应用,本说明书中的各项细节亦可基于不同观点与应用,在不背离本发明的精神下进行各种修饰与变更。

图5为本发明一种内嵌硅控整流器的pmos型esd器件之较佳实施例的器件结构图。如图5所示,本发明一种内嵌硅控整流器的pmos型esd器件,包括:多个浅沟道隔离层(sti,shallowtrenchisolation)10、高浓度n型掺杂(n+)32、高浓度p型掺杂(p+)20、高浓度p型掺杂(p+)22、高浓度n型掺杂(n+)30、高浓度p型掺杂(p+)24、p型esd掺杂(p-esdimp)28、n阱(n-well)60、p型栅(p-gate)40以及多个连接掺杂区与电极的金属硅化物(silicide)50。

整个esd器件置于p型衬底(p-sub)80上,在p型衬底(p-sub)80中生成一个n阱(n-well)60,高浓度n型掺杂(n+)32、高浓度p型掺杂(p+)20置于n阱(n-well)60的左上部,高浓度p型掺杂(p+)22、高浓度n型掺杂(n+)30、高浓度p型掺杂(p+)24置于n阱(n-well)60的右上部,并且高浓度p型掺杂(p+)22、高浓度n型掺杂(n+)30、高浓度p型掺杂(p+)24及其中间的间隔部分的正下方设置一层p型esd掺杂(p-esdimp)28,其中高浓度p型掺杂(p+)20、n阱(n-well)60以及p型esd掺杂(p-esdimp)28构成等效pnp三极管结构,n阱(n-well)60、p型esd掺杂(p-esdimp)28与高浓度n型掺杂(n+)30构成等效npn三极管结构;

高浓度n型掺杂(n+)32、高浓度p型掺杂(p+)20间用浅沟道隔离层(sti,shallowtrenchisolation)10隔离,高浓度p型掺杂(p+)20的右侧和高浓度p型掺杂(p+)22间为n阱(n-well)60的一部分,在该部分n阱上方放置p型栅(p-gate)40,高浓度n型掺杂(n+)32的左侧为浅沟道隔离层(sti,shallowtrenchisolation)10;高浓度p型掺杂(p+)22、高浓度n型掺杂(n+)30、高浓度p型掺杂(p+)24间为n阱(n-well)60的一部分,即高浓度p型掺杂(p+)22底部、高浓度n型掺杂(n+)30底部、高浓度p型掺杂(p+)24底部及其中间的间隔部分的正下方为一层p型esd掺杂(p-esdimp)28,高浓度n型掺杂(n+)24和p型esd掺杂(p-esdimp)28的右侧为浅沟道隔离层(sti,shallowtrenchisolation)10;高浓度p型掺杂(p+)22、高浓度n型掺杂(n+)30间间隔为s,高浓度n型掺杂(n+)30、高浓度p型掺杂(p+)24间间隔为s,高浓度p型掺杂(p+)22和高浓度p型掺杂(p+)24的宽度为a,高浓度n型掺杂(n+)30的宽度为b。

在高浓度n型掺杂(n+)32的上方、高浓度p型掺杂(p+)20的上方生成2个金属硅化物50引出电极相连并组成本发明之pmos器件的阳极anode;在高浓度n型掺杂(n+)30和高浓度p型掺杂(p+)24的上方生成金属硅化物50引出电极相连作为本发明之pmos器件的阴极cathode;在阳极anode和p型栅(p-gate)40间连接一电阻r,电阻r的取值范围为100ω~1mω,在p型栅(p-gate)40和阴极cathode间连接一电容c,电容c的取值范围为100ff~10pf,rc延时电路的时间常数可以设定为1ns~100ns;

本发明等效电路图如图6所示,本发明通过将现有pmos型esd器件(22/40/20/60)中将p型栅极40与阳极的连接断开,高浓度n型掺杂(n+)32与高浓度p型掺杂(p+)20相连组成本发明之pmos型esd器件的阳极anode,节点a为电阻r、电容c连接到p型栅极40的网络,利用rc延时电路调节控制该pmos型esd器件的栅极电压,当esd脉冲施加在该内嵌硅控整流器的pmos型esd器件的阳极时,该pmos型esd器件因为rc延时电路对栅极电压的调节而处于导通状态,导通之后的pmos协助触发该pmos型esd器件内嵌的硅控整流器,相较于已有的内嵌硅控整流器的pmos型esd器件利用pmos器件的击穿来协助触发该pmos型esd器件内嵌的硅控整流器,本发明所提出的新型内嵌硅控整流器的pmos型esd器件更容易降低内嵌硅控整流器的触发电压(vt1),所以本发明所提出的内嵌硅控整流器的pmos型esd器件更适用于先进cmos工艺平台核心器件的防静电保护设计。

图7为本发明一种内嵌硅控整流器的pmos型esd器件的实现方法的步骤流程图。如图7所示,本发明一种内嵌硅控整流器的pmos型esd器件的实现方法,包括如下步骤:

步骤s1,提供一半导体衬底,在本发明具体实施例中,提供一p型衬底(p-sub)80,并于该p型衬底(p-sub)80中生成一个n阱(n-well)60。

步骤s2,在该p型衬底(p-sub)80中生成一个n阱(n-well)60,高浓度n型掺杂(n+)32、高浓度p型掺杂(p+)20依次生成于n阱(n-well)60的左上部,高浓度p型掺杂(p+)22、高浓度n型掺杂(n+)30、高浓度p型掺杂(p+)24生成于n阱(n-well)60的右上部,于高浓度p型掺杂(p+)22、高浓度n型掺杂(n+)30、高浓度p型掺杂(p+)24及其中间的间隔部分的正下方生成一层p型esd掺杂(p-esdimp)28,其中高浓度p型掺杂(p+)20、n阱(n-well)60以及p型esd掺杂(p-esdimp)28构成等效pnp三极管结构,n阱(n-well)60、p型esd掺杂(p-esdimp)28与高浓度n型掺杂(n+)30构成等效npn三极管结构。

步骤s3,将高浓度n型掺杂(n+)32、高浓度p型掺杂(p+)20间用浅沟道隔离层(sti,shallowtrenchisolation)10隔离,高浓度p型掺杂(p+)20的右侧和高浓度p型掺杂(p+)22间为n阱(n-well)60的一部分,在该部分n阱上方设置p型栅(p-gate)40,高浓度n型掺杂(n+)32的左侧为浅沟道隔离层(sti,shallowtrenchisolation)10;高浓度p型掺杂(p+)22、高浓度n型掺杂(n+)30、高浓度p型掺杂(p+)24间为n阱(n-well)60的一部分,高浓度n型掺杂(n+)24和p型esd掺杂(p-esdimp)28的右侧为浅沟道隔离层(sti,shallowtrenchisolation)10。高浓度p型掺杂(p+)22、高浓度n型掺杂(n+)30间间隔为s,高浓度n型掺杂(n+)30、高浓度p型掺杂(p+)24间间隔为s,高浓度p型掺杂(p+)22和高浓度p型掺杂(p+)24的宽度为a,高浓度n型掺杂(n+)30的宽度为b。

步骤s4,在高浓度n型掺杂(n+)32的上方、高浓度p型掺杂(p+)20的上方生成2个金属硅化物50并引出电极相连组成本发明之pmos型esd器件的阳极anode;在高浓度n型掺杂(n+)30和高浓度p型掺杂(p+)24的上方生成金属硅化物50并引出电极相连作为本发明之pmos型esd器件的阴极cathode;在阳极anode和p型栅(p-gate)40间连接一电阻r,电阻r的取值范围为100ω~1mω,在p型栅(p-gate)40和阴极cathode间连接一电容c,电容c的取值范围为100ff~10pf,rc延时电路的时间常数可以设定为1ns~100ns;

应用时,为保护io端口,将本发明之内嵌硅控整流器的pmos型esd器件的阴极cathode对外接io(输入输出端),对内接内部电路,并通过某种esd保护器件接地vss,其阳极接电源电压vdd;为保护电源,在该内嵌硅控整流器的pmos型esd器件之后还可以连接其他的某种esd保护器件以获得需要的特性,如图8所示。

综上所述,本发明一种内嵌硅控整流器的pmos型esd器件及其实现方法通过将现有内嵌硅控整流器的pmos型esd器件中p型栅极40与阳极的连接断开,而用rc延时电路调节控制该pmos型esd器件的栅极电压,当esd脉冲施加在该pmos型esd器件的阳极时,该pmos型esd器件因为rc延时电路对栅极电压的调节而处于导通状态,导通之后的pmos协助触发该pmos型esd器件内嵌的硅控整流器,相较于现有的内嵌硅控整流器的pmos器件利用pmos器件的击穿来协助触发该pmos器件内嵌的硅控整流器,本发明更容易降低内嵌硅控整流器的触发电压(vt1),因此本发明更适用于先进cmos工艺平台核心器件的防静电保护设计。

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何本领域技术人员均可在不违背本发明的精神及范畴下,对上述实施例进行修饰与改变。因此,本发明的权利保护范围,应如权利要求书所列。

- 还没有人留言评论。精彩留言会获得点赞!