套刻标记的形成方法及半导体结构与流程

本发明涉及半导体制造技术领域,尤其涉及一种套刻标记的形成方法及半导体结构。

背景技术:

套刻标记(overlaymark)是半导体制程中用于衡量不同层之间对准精度的图形,用以判断上下层之间的对准精度是否满足工艺制程的要求。在半导体结构的制程线宽较宽时,套刻标记的制程较为简单。

随着半导体行业的发展,为了提高企业利润以及芯片集成度,制程的线宽越来越窄,进而实现于一片晶圆上形成的芯片数据量越来越多。但随着线宽的不断缩小,衍生出来的问题也相应越来越多。其中,用于不同层之间对准精度量测的套刻标记在制程中的问题越来越凸显。因此,如何减小结构密度效应对套刻标记图案的影响,使得能够准确的形成所需的套刻标记图案,从而有助于提高不同层间的对准精度,是当前亟待解决的技术问题。

技术实现要素:

本发明提供一种套刻标记的形成方法及半导体结构,用于解决现有技术由于受到结构密度效应影响不能准确的形成所需套刻标记的问题,以确保半导体制程的顺利进行。

为了解决上述问题,本发明提供了一种套刻标记的形成方法,包括如下步骤:

提供一衬底,所述衬底表面具有标记层、以及覆盖于所述标记层表面的第一掩膜层,所述标记层包括第一标记区域和位于所述第一标记区域端部的第二标记区域;

图形化所述第一掩膜层,于所述第一掩膜层中形成第一图形区域和位于所述第一图形区域端部的第二图形区域,所述第一图形区域中具有多个第一沟槽,所述第二图形区域中具有多个第二沟槽,所述第一标记区域与所述第一图形区域对应,所述第二标记区域与所述第二图形区域对应;

形成至少覆盖所述第一沟槽侧壁和所述第二沟槽侧壁的间隔层;

回填所述第一沟槽和所述第二沟槽,形成第二掩膜层;

去除所述间隔层,于所述第一掩膜层和所述第二掩膜层之间形成刻蚀窗口;

沿所述刻蚀窗口刻蚀所述标记层,于所述第一标记区域形成主套刻标记,并于所述第二标记区域形成伪套刻标记。

可选的,形成至少覆盖所述第一沟槽侧壁和所述第二沟槽侧壁的间隔层的具体步骤包括:

沉积间隔材料,形成覆盖所述第一沟槽侧壁和底壁、所述第二沟槽侧壁和底壁、以及所述第一掩膜层顶面的所述间隔层。

可选的,形成第二掩膜层的具体步骤包括:

回填所述第一沟槽和所述第二沟槽,形成填充满所述第一沟槽和所述第二沟槽、并覆盖位于所述第一掩膜层顶面的所述间隔层的第二掩膜层,位于所述第一图形区域的所述第二掩膜层厚度小于位于所述第二图形区域的所述第二掩膜层厚度。

可选的,所述第二标记区域环绕所述第一标记区域的外围分布;

所述第二图形区域环绕所述第一图形区域的外围分布。

可选的,所述主套刻标记为沿第一方向延伸的条状图形,多条所述主套刻标记沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记为环绕所述第一标记区域的围框状图形,多条所述伪套刻标记沿所述第一标记区域指向所述第二标记区域的方向依次嵌套。

可选的,所述主套刻标记为沿第一方向延伸的条状图形,多条所述主套刻标记沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记包括第一伪图形和第二伪图形,多条所述第一伪图形位于所述主套刻标记沿所述第二方向的相对两端、且均沿所述第一方向延伸,多条所述第二伪图形位于所述主套刻标记沿所述第一方向的相对两端、且均沿所述第二方向延伸。

可选的,所述主套刻标记为沿第一方向延伸的条状图形,多条所述主套刻标记沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记包括多个第三伪图形,多个所述第三伪图形环绕所述第一标记区域的外周呈围框状排布。

可选的,所述伪套刻标记的特征尺寸小于或者等于所述主套刻标记的特征尺寸。

为了解决上述问题,本发明还提供了一种半导体结构,包括:

衬底;

标记层,位于所述衬底上,包括第一标记区域和位于所述第一标记区域端部的第二标记区域,所述第一标记区域具有主套刻标记,所述第二标记区域具有伪套刻标记。

可选的,所述第二标记区域环绕所述第一标记区域的外围分布。

可选的,所述主套刻标记为沿第一方向延伸的条状图形,多条所述主套刻标记沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记为环绕所述第一标记区域的围框状图形,多条所述伪套刻标记沿所述第一标记区域指向所述第二标记区域的方向依次嵌套。

可选的,所述主套刻标记为沿第一方向延伸的条状图形,多条所述主套刻标记沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记包括第一伪图形和第二伪图形,多条所述第一伪图形位于所述主套刻标记沿所述第二方向的相对两端、且均沿所述第一方向延伸,多条所述第二伪图形位于所述主套刻标记沿所述第一方向的相对两端、且均沿所述第二方向延伸。

可选的,所述主套刻标记为沿第一方向延伸的条状图形,多条所述主套刻标记沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记包括多个第三伪图形,多个所述第三伪图形环绕所述第一标记区域的外周呈围框状排布。

可选的,所述主套刻标记贯穿所述标记层;

所述伪套刻标记贯穿或者未贯穿所述标记层。

可选的,在沿所述第一标记区域指向所述第二标记区域的方向上,所述第二标记区域的宽度小于所述第一标记区域。

本发明提供的套刻标记的形成方法及半导体结构,通过将用于形成套刻标记的标记层划分为第一标记区域和位于所述第一标记区域端部的第二标记区域,并于所述第一标记区域形成主套刻标记、于所述第二标记区域形成伪套刻标记,使得在套刻标记形成过程中由于结构密度效应导致的第二掩膜层的高低差向外拉,提高了所述第一标记区域填充的所述第二掩膜层厚度的均匀性,从而确保于所述标记层中形成完整的、并完全贯穿所述标记层的主套刻标记,确保了半导体制程工序的顺利进行。

附图说明

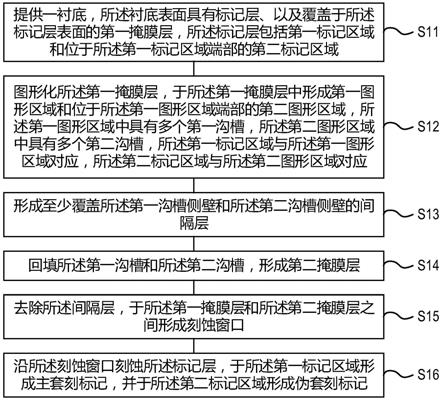

附图1是本发明具体实施方式中套刻标记的形成方法流程图;

附图2a-2j是本发明具体实施方式在形成套刻标记的过程中主要的工艺截面示意图;

附图3是本发明具体实施方式中半导体结构的截面示意图。

具体实施方式

目前在制程工艺中采用旋涂有机碳(spinoncarbon,soc)来作为形成套刻标记的硬掩模层,这是因为soc具有很好的流动性,因而具有很好的填充能力。但在实际的半导体制程中,soc的流动性并没有那么完美,并且受图案结构密度的影响,即结构密度效应或者图案负载效应(patternloading),soc在图案结构密度越高的位置其填充高度越低,相应的,soc在图案结构密度越低的位置其填充高度越高,因此,在图形结构中心处填充的soc与图形结构边缘处填充的soc之间存在高度差,例如图形结构中心处填充的soc的高度低于图形结构边缘处填充的soc。soc填充高度的不均匀性会影响后续制程的顺利进行,例如会使得后续光刻过程中,图形结构边缘处刻蚀不充分,影响最终形成的产品结构的性能,严重时甚至导致晶圆的报废,引起半导体制造成本的增加。

为了解决上述问题,本发明提供一种套刻标记的形成方法及半导体结构,用于解决现有技术由于受到结构密度效应影响不能准确的形成所需套刻标记的问题,以确保半导体制程的顺利进行,提高产品良率。下面结合附图对本发明提供的套刻标记的形成方法及半导体结构的具体实施方式做详细说明。

本具体实施方式提供了一种套刻标记的形成方法,附图1是本发明具体实施方式中套刻标记的形成方法流程图,附图2a-2j是本发明具体实施方式在形成套刻标记的过程中主要的工艺截面示意图。如图1、图2a-图2j所示,本具体实施方式提供的套刻标记的形成方法,包括如下步骤:

步骤s11,提供一衬底20,所述衬底20表面具有标记层21、以及覆盖于所述标记层21表面的第一掩膜层22,所述标记层21包括第一标记区域ⅰ和位于所述第一标记区域ⅰ端部的第二标记区域ⅱ,如图2a所示。

具体来说,所述衬底20可以是单一硅衬底,也可以是由多个膜层叠置形成的衬底。所述标记层21后续用于形成套刻标记。所述第一掩膜层22的材料可以为硬掩膜材料,例如有机碳材料。所述第一标记区域ⅰ用于形成主套刻标记,所述第二标记区域ⅱ用于形成伪套刻标记。在半导体制程工序中,使用所述主套刻标记进行套刻对准。所述第二标记区域ⅱ的宽度本领域技术人员可以根据实际需要进行设置,例如可以是0.5μm~10μm。

步骤s12,图形化所述第一掩膜层22,于所述第一掩膜层22中形成第一图形区域和位于所述第一图形区域端部的第二图形区域,所述第一图形区域中具有多个第一沟槽241,所述第二图形区域中具有多个第二沟槽242,所述第一标记区域ⅰ与所述第一图形区域对应,所述第二标记区域ⅱ与所述第二图形区域对应,如图2b所示。

具体来说,在图形化所述第一掩膜层22之前,还可以先于所述第一掩膜层22表面形成辅助掩膜层23,用于确保于所述第一掩膜层22中形成的图形的形貌。所述辅助掩膜层23的材料与所述第一掩膜层22的材料不同,以便于后续进行选择性刻蚀。所述辅助掩膜层23的材料可以是但不限于氮化物材料。之后,刻蚀所述辅助掩膜层23和所述第一掩膜层22,于与所述第一标记区域ⅰ对应的所述第一图形区域中形成多个所述第一沟槽241、并同时于与所述第二标记区域ⅱ对应的所述第二图形区域中形成多个所述第二沟槽242。所述第一沟槽241和所述第二沟槽242均沿垂直于所述衬底20的方向(例如图2b中的z轴方向)贯穿所述辅助掩膜层23和所述第一掩膜层22。本具体实施方式中所述的多个是指两个及两个以上。

步骤s13,形成至少覆盖所述第一沟槽241侧壁和所述第二沟槽侧壁242的间隔层25,如图2c所示。

可选的,形成至少覆盖所述第一沟槽241侧壁和所述第二沟槽242侧壁的间隔层25的具体步骤包括:

沉积间隔材料,形成覆盖所述第一沟槽241侧壁和底壁、所述第二沟槽242侧壁和底壁、以及所述第一掩膜层22顶面的所述间隔层25。

具体来说,在形成所述第一沟槽241和所述第二沟槽242之后,采用原子层沉积工艺或者其他沉积工艺沉积间隔材料,形成覆盖所述第一沟槽241侧壁和底壁、所述第二沟槽242侧壁和底壁、以及所述辅助掩膜层23顶面(即所述辅助掩膜层23背离所述衬底20的表面)的所述间隔层25。所述间隔层25覆盖所述第一沟槽241的侧壁和底壁,未填充满所述第一沟槽241;所述间隔层25覆盖所述第二沟槽242的侧壁和底壁,未填充满所述第二沟槽242。通过调整所述间隔层25的厚度,可以控制后续形成的所述主套刻标记和所述伪套刻标记的宽度。

步骤s14,回填所述第一沟槽241和所述第二沟槽242,形成第二掩膜层26,如图2d所示。

可选的,形成第二掩膜层26的具体步骤包括:

回填所述第一沟槽241和所述第二沟槽242,形成填充满所述第一沟槽241和所述第二沟槽242、并覆盖位于所述第一掩膜层22顶面的所述间隔层25的第二掩膜层26,位于所述第一图形区域的所述第二掩膜层26厚度小于位于所述第二图形区域的所述第二掩膜层26厚度。

具体来说,通过回填所述第一沟槽241和所述第二沟槽242,形成所述第二掩膜层26。所述第二掩膜层26填充满所述第一沟槽241和所述第二沟槽242,并覆盖位于所述辅助掩膜层23顶面的所述间隔层25。通过设置具有所述第二沟槽242的所述第二图形区域,即便是在填充所述第二掩膜层26的过程中,受结构密度效应的影响,也能够将所述第二掩膜层26的厚度高低差向外拉,减小所述第一图形区域内的所述第二掩膜层26的厚度差,使得位于所述第一图形区域的所述第二掩膜层26的厚度小于位于所述第二图形区域的所述第二掩膜层26的厚度,确保后续能够形成完整的主套刻标记。所述第二掩膜层26的材料可以与所述第一掩膜层22的材料相同,例如都为硬掩膜材料有机碳。在其他具体实施方式中,本领域技术人员也可以根据实际需要将所述第二掩膜层26的材料设置为与所述第一掩膜层22的材料不同。

步骤s15,去除所述间隔层25,于所述第一掩膜层22和所述第二掩膜层26之间形成刻蚀窗口27,如图2f所示。

具体来说,在形成所述第二掩膜层26之后,采用化学机械研磨工艺平坦化所述第二掩膜层26,以所述间隔层25作为研磨截止层。由于受结构密度效应的影响,研磨之后,位于所述第一图形区域的所述间隔层25能够完整暴露,而由于所述第二图形区域的所述第二掩膜层26的厚度较大,位于所述第二图形区域的所述间隔层25则不能完整暴露,如图2e所示。之后,通过干法或者湿法刻蚀工艺区域所述间隔层25,位于所述第一沟槽241侧壁的所述间隔层25能够被完整的、充分的去除,位于所述第二沟槽242侧壁的所述间隔层25则不能被充分去除,使得于所述第二沟槽242侧壁残留有部分所述间隔层25,如图2f所示。

步骤s16,沿所述刻蚀窗口27刻蚀所述标记层21,于所述第一标记区域ⅰ形成主套刻标记,并于所述第二标记区域ⅱ形成伪套刻标记。

具体来说,沿所述刻蚀窗口27刻蚀所述标记层21,于所述第一标记区域ⅰ形成主套刻标记槽281、并同时于所述第二标记区域ⅱ形成伪套刻标记槽282。所述第一标记区域ⅰ中的所有主套刻标记槽281均沿垂直于所述衬底20的方向贯穿所述标记层21,所述第二标记区域ⅱ中存在未贯穿所述标记层21的伪套刻标记槽282,如图2g所示。之后,采用标记材料填充所述主套刻标记槽281,形成主套刻标记;同时采用标记材料填充所述伪套刻标记槽282,形成伪套刻标记。所述标记材料可以是但不限于金属材料。所述标记层21的材料可以为绝缘介质材料。

可选的,所述伪套刻标记的特征尺寸小于或者等于所述主套刻标记的特征尺寸。

具体来说,通过限定所述伪套刻标记的特征尺寸小于或者等于所述主套刻标记的特征尺寸,使得在进行套刻对准的过程中,所述伪套刻标记不影响所述主套刻标记的对准。

可选的,所述第二标记区域ⅱ环绕所述第一标记区域ⅰ的外围分布;

所述第二图形区域环绕所述第一图形区域的外围分布。

本具体实施方式是以所述第二标记区域ⅱ环绕所述第一标记区域ⅰ的外围分布为例进行说明,以充分减少结构密度效应对主套刻标记各个角度的影响。在其他具体实施方式中,本领域技术人员也可以根据实际需要在所述第一标记区域ⅰ的一侧或者多侧设置所述第二标记区域ⅱ。多侧是指两侧及两侧以上。

可选的,所述主套刻标记为沿第一方向延伸的条状图形,多条所述主套刻标记沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记为环绕所述第一标记区域的围框状图形,多条所述伪套刻标记沿所述第一标记区域指向所述第二标记区域的方向依次嵌套。

图2h为本具体实施方式形成的第一种套刻标记的俯视结构示意图。举例来说,如图2h所示,当层的主套刻标记30的外围环绕有当层的伪套刻标记32。所述当层的主套刻标记30为沿y轴方向延伸的条状图形,多条所述当层的主套刻标记30沿x轴方向平行排布。所述当层的伪套刻标记32为围框状图形结构,且在沿所述当层的主套刻标记30指向当层的伪套刻标记32的方向上,多条所述当层的伪套刻标记32依次嵌套。在套刻对准的过程中,使用当层的主套刻标记30与前层的主套刻标记31对准。

可选的,所述主套刻标记为沿第一方向延伸的条状图形,多条所述主套刻标记沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记包括第一伪图形和第二伪图形,多条所述第一伪图形位于所述主套刻标记沿所述第二方向的相对两端、且均沿所述第一方向延伸,多条所述第二伪图形位于所述主套刻标记沿所述第一方向的相对两端、且均沿所述第二方向延伸。

图2i为本具体实施方式形成的第二种套刻标记的俯视结构示意图。举例来说,如图2i所示,当层的主套刻标记30的外围环绕有当层的伪套刻标记。所述当层的主套刻标记30为沿y轴方向延伸的条状图形,多条所述当层的主套刻标记30沿x轴方向平行排布。所述当层的伪套刻标记包括第一伪图形321和第二伪图形322。所述第一伪图形321分布于所述主套刻标记30沿y轴方向的相对两端、且均沿x轴方向延伸;所述第二伪图形322分布于所述主套刻标记30沿x轴方向的相对两端、且均沿y轴方向延伸。在套刻对准的过程中,使用当层的主套刻标记30与前层的主套刻标记31对准。

可选的,所述主套刻标记为沿第一方向延伸的条状图形,多条所述主套刻标记沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记包括多个第三伪图形,多个所述第三伪图形环绕所述第一标记区域的外周呈围框状排布。

图2j为本具体实施方式形成的第三种套刻标记的俯视结构示意图。举例来说,如图2j所示,当层的主套刻标记30的外围环绕有当层的伪套刻标记。所述当层的主套刻标记30为沿y轴方向延伸的条状图形,多条所述当层的主套刻标记30沿x轴方向平行排布。所述当层的伪套刻标记包括多个第三伪图形32,多个所述第三伪图形环绕所述当层的主套刻标记30的外围分布,并形成围框状结构。在套刻对准的过程中,使用当层的主套刻标记30与前层的主套刻标记31对准。

本具体实施方式是以所述伪套刻标记中的多个所述第三伪图形的结构和尺寸均相同为例进行说明。在其他具体实施方式中,本领域技术人员可以根据实际需要将多个所述第三伪图形的结构和/或尺寸设置的不相同。

不仅如此,本具体实施方式还提供了一种半导体结构。附图3是本发明具体实施方式中半导体结构的截面示意图,本具体实施方式提供的半导体结构可以采用如图1、图2a-图2j所示的方法形成。如图3所示,本具体实施方式提供的半导体结构,包括:

衬底20;

标记层21,位于所述衬底20上,包括第一标记区域ⅰ和位于所述第一标记区域ⅰ端部的第二标记区域ⅱ,所述第一标记区域ⅰ具有主套刻标记40,所述第二标记区域ⅱ具有伪套刻标记41。

可选的,所述第二标记区域ⅱ环绕所述第一标记区域ⅰ的外围分布。

可选的,所述主套刻标记40为沿第一方向延伸的条状图形,多条所述主套刻标记40沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记41为环绕所述第一标记区域的围框状图形,多条所述伪套刻标记41沿所述第一标记区域指向所述第二标记区域的方向依次嵌套。

可选的,所述主套刻标记40为沿第一方向延伸的条状图形,多条所述主套刻标记40沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记41包括第一伪图形和第二伪图形,多条所述第一伪图形位于所述主套刻标记40沿所述第二方向的相对两端、且均沿所述第一方向延伸,多条所述第二伪图形位于所述主套刻标记40沿所述第一方向的相对两端、且均沿所述第二方向延伸。

可选的,所述主套刻标记40为沿第一方向延伸的条状图形,多条所述主套刻标记40沿与所述第一方向垂直的第二方向平行排布,所述第一方向和所述第二方向均为平行于所述衬底的方向;

所述伪套刻标记41包括多个第三伪图形,多个所述第三伪图形环绕所述第一标记区域ⅰ的外周呈围框状排布。

可选的,所述主套刻标记40贯穿所述标记层21;

所述伪套刻标记41贯穿或者未贯穿所述标记层21。

可选的,在沿所述第一标记区域ⅰ指向所述第二标记区域ⅱ的方向上,所述第二标记区域ⅱ的宽度小于所述第一标记区域ⅰ。

本具体实施方式提供的套刻标记的形成方法及半导体结构,通过将用于形成套刻标记的标记层划分为第一标记区域和位于所述第一标记区域端部的第二标记区域,并于所述第一标记区域形成主套刻标记、于所述第二标记区域形成伪套刻标记,使得在套刻标记形成过程中由于结构密度效应导致的第二掩膜层的高低差向外拉,提高了所述第一标记区域填充的所述第二掩膜层厚度的均匀性,从而确保于所述标记层中形成完整的、并完全贯穿所述标记层的主套刻标记,确保了半导体制程工序的顺利进行。

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

- 还没有人留言评论。精彩留言会获得点赞!