封装结构和测试方法与流程

1.本公开涉及一种封装结构和一种测试方法,且涉及一种包含具有至少一个测试电路结构的布线结构的封装结构,和一种用于测试所述封装结构的方法。

背景技术:

2.随着电子行业的快速发展及半导体处理技术的进步,半导体封装结构与不断增加的数目的电子组件或电子装置集成以实现改进的电气性能和额外的功能。相应地,在热工艺期间可能发生半导体封装结构的翘曲。因为半导体封装结构的刚性或硬度相对低,所以在半导体封装结构的顶部表面处或在保护材料中可能会形成裂缝,并且此裂缝延伸或生长到半导体封装结构的内部中。如果裂缝到达半导体封装结构,则半导体封装结构中的导电电路层可能会断裂或破损,这可能会导致断路,并且致使半导体封装结构不能正常操作。因此,半导体封装结构的良率可能降低。

技术实现要素:

3.在一些实施例中,一种封装结构包含布线结构、第一电子装置和第二电子装置。所述布线结构包含至少一个介电层、与介电层接触的至少一个导电电路层,以及与介电层接触的至少一个测试电路结构。测试电路结构安置成邻近于导电电路层的互连部分。第一电子装置电连接到布线结构。第二电子装置电连接到布线结构。第二电子装置经由导电电路层的互连部分电连接到第一电子装置。

4.在一些实施例中,一种测试方法包含:(a)提供封装结构,其中所述封装结构包含第一电子装置、经由至少一个导电电路层电连接到第一电子装置的第二电子装置,和安置成邻近于所述至少一个导电电路层的至少一个测试电路结构;以及(b)测试所述至少一个测试电路结构。

附图说明

5.当结合附图阅读时,从以下具体实施方式容易理解本公开的一些实施例的各方面。应注意,各种结构可能未按比例绘制,且出于论述的清楚起见,可任意增大或减小各种结构的尺寸。

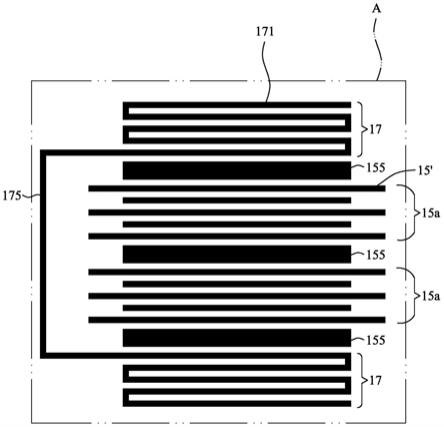

6.图1示出根据本公开的一些实施例的封装结构的俯视图。

7.图2示出图1中的区“a”的放大视图,其中为了图示清楚起见省略了第一电子装置、第二电子装置、第一保护材料和第一介电层。

8.图2a示出根据本公开的一些实施例的互连部分和测试电路结构的俯视图。

9.图3示出图2的立体图。

10.图4示出图1的封装结构的沿着线4

‑

4截取的截面视图。

11.图5示出图1的封装结构的沿着线5

‑

5截取的截面视图。

12.图6示出图1的封装结构的沿着线6

‑

6截取的截面视图。

13.图7示出根据本公开的一些实施例的封装结构的截面图。

14.图8示出根据本公开的一些实施例的封装结构的截面图。

15.图9示出根据本公开的一些实施例的封装结构的截面图。

16.图10示出根据本公开的一些实施例的封装结构的截面图。

17.图11示出根据本公开的一些实施例的测试电路结构和互连部分的立体图。

18.图12示出根据本公开的一些实施例的测试电路结构和互连部分的立体图。

19.图13示出根据本公开的一些实施例的组合件结构的截面图。

20.图14示出根据本公开的一些实施例的测试方法的实例的一或多个阶段。

21.图15示出根据本公开的一些实施例的测试方法的实例的一或多个阶段。

22.图16示出根据本公开的一些实施例的测试方法的实例的一或多个阶段。

23.图17示出根据本公开的一些实施例的测试方法的实例的一或多个阶段。

24.图18示出根据本公开的一些实施例的测试方法的实例的一或多个阶段。

25.图19示出根据本公开的一些实施例的测试方法的实例的一或多个阶段。

26.图20示出根据本公开的一些实施例的测试方法的实例的一或多个阶段。

27.图21示出根据本公开的一些实施例的测试方法的实例的一或多个阶段。

具体实施方式

28.贯穿图式及详细描述使用共同参考标号来指示相同或相似组件。根据以下结合附图作出的详细描述将容易理解本公开的实施例。

29.以下公开内容提供用于实施所提供主题的不同特征的许多不同实施例或实例。下文描述组件及布置的特定实例以解释本公开的某些方面。当然,这些只是实例且并不希望为限制性的。举例来说,在以下描述中,第一特征形成在第二特征上方或上可包含第一特征和第二特征直接接触地形成或安置的实施例,且还可包含额外特征可在第一特征与第二特征之间形成或安置使得第一特征和第二特征可不直接接触的实施例。此外,本公开可在各种实例中重复参考标号和/或字母。这种重复是出于简化和清楚的目的且本身并不规定所论述的各种实施例和/或配置之间的关系。

30.本公开的至少一些实施例提供包含至少一个测试电路结构的布线结构。在一些实施例中,一种封装结构包含此布线结构使得可对测试电路结构进行测试,且此测试的结果可模拟布线结构的导电电路层的状况。本公开的至少一些实施例进一步提供用于测试封装结构的技术。

31.图1示出根据本公开的一些实施例的封装结构3的俯视图。图2示出图1中的区“a”的放大视图,其中为了图示清楚起见省略了第一电子装置24、第二电子装置26、第一保护材料32和第一介电层141。图2a示出根据本公开的一些实施例的互连部分15a和测试电路结构17的俯视图。图3示出图2的立体图。图4示出图1的封装结构3的沿着线4

‑

4截取的截面视图。图5示出图1的封装结构3的沿着线5

‑

5截取的截面视图。如图4和图5所示,封装结构3包含布线结构(wiring structure)1、第一电子装置24、第二电子装置26、第一保护材料32、封装体(encapsulant)34和多个接合材料(solder material)36。如图1中所示,封装结构3可包含一个第一电子装置24和两个第二电子装置26。然而,第一电子装置24和第二电子装置26的数量在本公开中不受限制。

32.如图4和图5所示,布线结构1具有第一表面11(例如,顶部表面)、与第一表面11相对的第二表面12(例如,底部表面)、在第一表面11和第二表面12之间延伸的侧面13。布线结构1可包含至少一个介电层14、与介电层14接触的至少一个导电电路层(conductive circuit layer)15、与介电层14接触的至少一个测试电路结构(test circuit structure)17,以及多个突出衬垫20。布线结构1可进一步包含第一芯片接合区域18、第二芯片接合区域19,以及安置于第一芯片接合区域18和第二芯片接合区域19之间的高线密度区(high line density region)16(或精细线区(fine line region))。第一电子装置24可附接到第一芯片接合区域18,且第二电子装置26可附接到第二芯片接合区域19。因此,高线密度区16(或精细线区)可安置于第一电子装置24和第二电子装置26之间。

33.举例来说,如图4和5中所示,布线结构1包含第一介电层141、第一导电电路层151、第二介电层142、第二导电电路层152、第三介电层143、第三导电电路层153、第四介电层144、第四导电电路层154和第五介电层145。也就是说,所述至少一个介电层14包含第一介电层141、第二介电层142、第三介电层143、第四介电层144和第五介电层145。所述至少一个导电电路层15包含第一导电电路层151、第二导电电路层152、第三导电电路层153和第四导电电路层154。

34.第一介电层141可以是布线结构1的最顶部介电层或最外介电层。第一导电电路层151可以是布线结构1的最顶部导电电路层或最外导电电路层。第一导电电路层151的材料可包含(例如)铜、另一导电金属,或其合金。第一介电层141的材料可包含绝缘材料、钝化材料、介电材料或阻焊剂材料,例如基于苯并环丁烯的聚合物(benzocyclobutene(bcb)based polymer)或聚酰亚胺(pi)。在一些实施例中,第一介电层141可由光可成像材料(photoimageable material)制成。另外,布线结构1的第一表面11可以是第一介电层141的顶部表面。第一导电电路层151安置成邻近于第一介电层141的顶部表面。在一些实施例中,第一导电电路层151嵌入于第一介电层141中,且从第一介电层141的顶部表面暴露。也就是说,第一介电层141覆盖第一导电电路层151,且界定多个开口以暴露第一导电电路层151的部分。

35.此外,第一导电电路层151可包含互连部分15a和外围部分15b。第一导电电路层151可以是布线结构1的最顶部导电电路层或最外导电电路层。互连部分15a位于高线密度区16中,并且外围部分15b位于高线密度区16外部的区(例如,低线密度区)中。举例来说,第二电子装置26可经由第一导电电路层151的互连部分15a电连接到第一电子装置24。第二电子装置26和第一电子装置24可经由第一导电电路层151的外围部分15b电连接到布线结构1的第二表面12上的接合材料36。在一些实施例中,第一导电电路层151的互连部分15a可包含彼此平行的多个导电迹线15',且第一导电电路层151的外围部分15b可包含多个导电迹线15"。互连部分15a的导电迹线15'的线宽/线距(line width/line space,l/s)可小于外围部分15b的导电迹线15"的l/s。举例来说,互连部分15a的导电迹线15'的l/s可小于或等于约5μm/约5μm,或者小于或等于约2μm/约2μm,或者小于或等于约0.8μm/约0.8μm。外围部分15b的导电迹线15"的l/s可小于或等于约10μm/约10μm,或者小于或等于约7μm/约7μm,或者小于或等于约5μm/约5μm。

36.第一介电层141和第一导电电路层151可安置在第二介电层142上。此外,第二介电层142可覆盖第二导电电路层152。第一导电电路层151的一部分(即,导通孔部分15c)延伸

穿过第二介电层142以电连接第二导电电路层152。第二介电层142的材料可与第一介电层141的材料相同或类似。第二导电电路层152还可包含位于高线密度区16中的互连部分15a,和位于高线密度区16外部的外围部分15b。在一些实施例中,第一导电电路层151的导通孔部分15c可从外围部分15b延伸,且它们可同时且一体地形成。

37.类似地,第二介电层142和第二导电电路层152可安置在第三介电层143上。此外,第三介电层143可覆盖第三导电电路层153。第二导电电路层152的一部分(即,导通孔部分15c)延伸穿过第三介电层143以电连接第三导电电路层153。第三介电层143的材料可与第二介电层142的材料相同或类似。第三导电电路层153还可包含位于高线密度区16中的互连部分15a,和位于高线密度区16外部的外围部分15b。在一些实施例中,第二导电电路层152的导通孔部分15c可从外围部分15b延伸,且它们可同时且一体地形成。

38.类似地,第三介电层143和第三导电电路层153可安置在第四介电层144上。此外,第四介电层144可覆盖第四导电电路层154。第三导电电路层153的一部分(即,导通孔部分15c)延伸穿过第四介电层144以电连接第四导电电路层154。第四介电层144的材料可与第三介电层143的材料相同或类似。第四导电电路层154还可包含位于高线密度区16中的互连部分15a,和位于高线密度区16外部的外围部分15b。

39.第四介电层144和第四导电电路层154可安置在第五介电层145上。第四导电电路层154的一部分(即,导通孔部分15c)延伸穿过第五介电层145以从第五介电层145的底部表面(例如,布线结构1的第二表面12)暴露。第五介电层145的材料可与第四介电层144的材料相同或类似。如图4和图5所示,第二电子装置26可经由导电电路层15的互连部分15a(包含例如第一导电电路层151、第二导电电路层152、第三导电电路层153和第四导电电路层154的互连部分15a)电连接到第一电子装置24。第二电子装置26和第一电子装置24可经由导电电路层15的外围部分15b(包含例如第一导电电路层151、第二导电电路层152、第三导电电路层153和第四导电电路层154的外围部分15b)的导通孔部分15c电连接到接合材料36。

40.突出衬垫20可安置在布线结构1的第一介电层141(即,最顶部介电层或最外介电层)上并且从所述第一介电层141突出。突出衬垫20可安置在布线结构1的第一表面11上且从所述第一表面11突出,并延伸穿过第一介电层141(即,最顶部介电层或最外介电层)以电连接第一导电电路层151。突出衬垫20可包含对应于第一电子装置24的多个第一突出衬垫21和对应于第二电子装置26的多个第二突出衬垫22。

41.第一电子装置24和第二电子装置26安置成并排地邻近于布线结构1的第一表面11,且电连接到布线结构1的导电电路层15。第一电子装置24可以是半导体装置,例如专用集成电路(pplication specific integrated circuit,asic)裸片。如图4和图5所示,第一电子装置24可具有第一有源表面241、与第一有源表面241相对的第一背面242,以及在第一有源表面241和第一背面242之间延伸的侧面243。第一电子装置24可具有第一有源表面241上的第一有源区域264。多个电路和多个电组件安置于第一有源区域264内。此外,第一电子装置24可包含安置成邻近于第一有源表面241的多个第一电接触件(electrical contact)244。第一电接触件244可从第一有源表面241暴露或突出以用于电连接。第一电接触件244可以是衬垫(pad)、凸块(bump)、立柱(stud)、柱(pillar)或支柱(post)。在一些实施例中,第一电子装置24的第一电接触件244可经由多个接合材料245电连接和物理连接到第一突出衬垫21。换句话说,第一电子装置24可通过倒装芯片接合电连接到布线结构1。举例来说,

第一电接触件244可包含铜、金、铂和/或其它合适的材料。

42.第二电子装置26可以是半导体装置,例如高带宽存储器(high bandwidth memory,hbm)裸片。如图4和图5所示,第二电子装置26可具有第二有源表面261、与第二有源表面261相对的第二背面262,以及在第二有源表面261和第二背面262之间延伸的侧面263。第二电子装置26可具有第二有源表面261上的第二有源区域266。多个电路和多个电组件安置于第二有源区域266内。此外,第二电子装置26可包含安置成邻近于第二有源表面261的多个第二电接触件264。第二电接触件264可从第二有源表面261暴露或突出以用于电连接。第二电接触件264可以是衬垫、凸块、立柱、柱或支柱。在一些实施例中,第二电子装置26的第二电接触件264可经由多个接合材料265电连接和物理连接到第二突出衬垫22。换句话说,第二电子装置26可通过倒装芯片接合电连接到布线结构1。举例来说,第二电接触件264可包含铜、金、铂和/或其它合适的材料。

43.如图1到图3中所展示,测试电路结构17可安置成邻近于导电电路层15的互连部分15a。在一些实施例中,布线结构1可包含多个互连部分15a、多个测试电路结构17和多个屏蔽壁155。互连部分15a、测试电路结构17和屏蔽壁155可安置于同一层处且可同时形成。因此,测试电路结构17的材料和屏蔽壁155的材料可与互连部分15a的材料相同,且测试电路结构17的厚度和屏蔽壁155的厚度可与互连部分15a的厚度相同。最外介电层(即,第一介电层141)可覆盖最外导电电路层(即,第一导电电路层151)和测试电路结构17。在一些实施例中,第一导电电路层151、测试电路结构17和屏蔽壁155可构成布线结构1的第一金属层(即,最顶部金属层)。此外,布线结构1可进一步包含含有第二导电电路层152的第二金属层、含有第三导电电路层153的第三金属层,以及含有第四导电电路层154的第四金属层。在一些实施例中,第一金属层和第三金属层可为信号发射传输层,且第二金属层和第四金属层可为电源/接地层。

44.此外,互连部分15a紧挨着彼此安置。测试电路结构17安置在互连部分15a的两侧上。一些屏蔽壁155可安置于互连部分15a之间以便防止互连部分15a之间的串扰(crosstalk)。一些屏蔽壁155可安置于互连部分15a和测试电路结构17之间以便防止互连部分15a和测试电路结构17之间的串扰。应注意,屏蔽壁155可以或可以不电连接到接地层。测试电路结构17和屏蔽壁155可位于高线密度区16中。因此,互连部分15a、测试电路结构17和屏蔽壁155安置于第一电子装置24的侧面243和第二电子装置26的侧面263之间的间隙30下方。也就是说,互连部分15a的两端分别延伸到第一芯片接合区域18和第二芯片接合区域19。互连部分15a的第一部分安置于第一电子装置24的第一有源区域246的竖直投影内,且互连部分15a的第二部分安置于第二电子装置26的第二有源区域266的竖直投影内。此外,测试电路结构17的两端分别延伸到第一芯片接合区域18和第二芯片接合区域19。屏蔽壁155的两端分别延伸到第一芯片接合区域18和第二芯片接合区域19。测试电路结构17的第一部分安置于第一电子装置24的第一有源区域246的竖直投影内,且测试电路结构17的第二部分安置于第二电子装置26的第二有源区域266的竖直投影内。也就是说,测试电路结构17的第一部分延伸到第一电子装置24下方的空间,且测试电路结构17的第二部分延伸到第二电子装置26下方的空间。

45.在一些实施例中,测试电路结构17可以是虚设(dummy)的,且可以不电连接到导电电路层15的互连部分15a。也就是说,测试电路结构17可与导电电路层15的互连部分15a电

隔离。此外,测试电路结构17可与第一电子装置24和第二电子装置26电隔离。举例来说,导电电路层15的互连部分15a可用于在第一电子装置24和第二电子装置26之间传输信号(例如,数字信号),而测试电路结构17不具有传输信号(例如,数字信号)的功能。因此,测试电路结构17可与封装结构3的数字信号传输路径电隔离。

46.如图2所示,测试电路结构17的型式(或图案或布局)可与导电电路层15的互连部分15a的型式(或图案或布局)类似或相同。举例来说,测试电路结构17可包含彼此平行的多个片段(segment)171。测试电路结构17的片段171的线宽/线距(l/s)可大体上等于互连部分15a的导电迹线15'的线宽/线距(l/s)。此外,互连部分15a的导电迹线15'和屏蔽壁155可与测试电路结构17的片段171大体上平行。此外,屏蔽壁155的宽度可比互连部分15a的导电迹线15'的宽度大例如两倍、三倍、四倍或五倍或更大。

47.在一些实施例中,导电电路层15的互连部分15a和屏蔽壁155之间的间隙可大体上等于互连部分15a的导电迹线15'之间的线间隔(line space)。测试电路结构17和屏蔽壁155之间的间隙可大体上等于互连部分15a的导电迹线15'之间的线间隔。如果省略屏蔽壁155,则测试电路结构17和互连部分15a之间的间隙可大体上等于互连部分15a的导电迹线15'之间的线间隔。

48.如图2a所示,互连部分15a的导电迹线15'和测试电路结构17的片段171之间可形成夹角。此夹角可小于90度、60度、45度、30度或15度。因此,互连部分15a的导电迹线15'不垂直于测试电路结构17的片段171。

49.如图2和图3所示,测试电路结构17中的每一个的片段171彼此串联连接。在一些实施例中,测试电路结构17中的每一个可呈蛇形(serpentine)形状。此外,测试电路结构17可经由连接部分175彼此电连接。连接部分175可位于高线密度区16中或高线密度区16外部。此外,连接部分175和测试电路结构17可安置于相同层或不同层处。在一些实施例中,连接部分175可安置于互连部分15a的正上方或正下方。

50.如图3和图5所示,测试电路结构17的一端可电连接到布线结构1的第二表面12。举例来说,测试电路结构17中的一个的最外片段171可具有电连接端(electrical connection end)172,所述电连接端172经由向下电路径174向下电连接到布线结构1的第二表面12。向下电路径174可包含第一导电电路层151的导通孔部分15c、第二导电电路层152的导通孔部分15c、第三导电电路层153的导通孔部分15c和第四导电电路层154的导通孔部分15c。应注意,第四导电电路层154的暴露的导通孔部分15c可以是供探针91(图18)接触的电接触件。测试电路结构17电连接到电接触件。举例来说,测试电路结构17中的另一个的最外片段171可具有电连接端173,所述电连接端173经由向下电路径176(图6)向下电连接到布线结构1的第二表面12。向下电路径176可包含第一导电电路层151、第二导电电路层152、第三导电电路层153和第四导电电路层154的导通孔部分15c。应注意,第四导电电路层154的暴露的导通孔部分15c可以是供探针接触的电接触件。测试电路结构17电连接到电接触件。因此,测试电路结构17不向上电连接到第一电子装置24和第二电子装置26。测试电路结构17上不存在突出衬垫20。测试电路结构17可不含向上电连接。在一些实施例中,向下电路径174、176是布线结构1中的独立电路径。

51.如图4和图5所示,第一保护材料32(即,底部填充物(underfill))安置于第一电子装置24和布线结构1之间的第一空间25中,及第二电子装置26和布线结构1之间的第二空间

27中,以便覆盖和保护由第一电接触件244、第一突出衬垫21和接合材料245形成的接合结构,及由第二电接触件264、第二突出衬垫22和接合材料265形成的接合结构。此外,第一保护材料32可进一步延伸到第一电子装置24的侧面243和第二电子装置26的侧面263之间的间隙30中。

52.封装体34(即,第二保护材料)覆盖布线结构1的第一表面11的至少一部分、第一电子装置24的至少一部分、第二电子装置26的至少一部分和第一保护材料32。封装体34的材料可以是含或不含填料的模制化合物(molding compound)。封装体34具有第一表面341(例如,顶部表面)和侧面343。在一些实施例中,封装体34的第一表面341、第一电子装置24的第一背面242、第二电子装置26的第二背面262和间隙30中的第一保护材料32的顶部表面可彼此大体上共面。然而,在其它实施例中,间隙30中的第一保护材料32的顶部表面可从第一电子装置24的第一背面242和/或第二电子装置26的第二背面262凹入。因此,封装体34的一部分可延伸到第一电子装置24和第二电子装置26之间的间隙30中。此外,封装体34的侧面343可与布线结构1的侧面13大体上共面。

53.接合材料36(例如,焊料球)可安置为邻近于布线结构1的第二表面12以用于外部连接。如图4和图5所示,接合材料36安置在第四导电电路层154的暴露部分(即,导通孔部分15c的底部部分)上。在一些实施例中,接合材料36可包含测试接合材料361。测试接合材料361电连接到向下电路径174。因此,测试接合材料361经由第一导电电路层151的导通孔部分15c、第二导电电路层152的导通孔部分15c、第三导电电路层153的导通孔部分15c和第四导电电路层154的导通孔部分15c电连接到测试电路结构17的最外片段171的电连接端172。

54.图6示出图1的封装结构3的沿着线6

‑

6截取的截面视图。测试电路结构17中的一个的最外片段171可具有电连接端173,所述电连接端173经由向下电路径176(图3)向下电连接到布线结构1的第二表面12。向下电路径176可包含第一导电电路层151的导通孔部分15c、第二导电电路层152的导通孔部分15c、第三导电电路层153的导通孔部分15c和第四导电电路层154的导通孔部分15c。在一些实施例中,接合材料36可包含测试接合材料362。测试接合材料362电连接到向下电路径176。因此,测试接合材料362经由第一导电电路层151的导通孔部分15c、第二导电电路层152的导通孔部分15c、第三导电电路层153的导通孔部分15c和第四导电电路层154的导通孔部分15c电连接到测试电路结构17的最外片段171的电连接端173。

55.在图1到图6所示的实施例中,测试电路结构17的型式(或图案或布局)可与导电电路层15的互连部分15a的型式(或图案或布局)类似或相同。因此,测试电路结构17可模拟导电电路层15的互连部分15a的状况。也就是说,如果测试电路结构17的片段171断裂或破损,且测试电路结构17中发生断路,则可认为导电电路层15的互连部分15a断裂或破损。在封装结构3中,如果在间隙30中的第一保护材料32的顶部表面处形成裂缝且所述裂缝向下延伸或生长以使导电电路层15的互连部分15a断裂或破损,则此裂缝可能同时使测试电路结构17断裂或破损。因此,在测试阶段中,可从布线结构1的第二表面12(例如,底部表面)经由向下电路径174、176对测试电路结构17进行测试,以推测导电电路层15的互连部分15a是否断裂或破损。此测试环路仅安置于布线结构1中,且不经过第一电子装置24和第二电子装置26。因此,第一电子装置24和第二电子装置26不必添加任何电路来测试导电电路层15的互连部分15a。

56.图7示出根据本公开的一些实施例的封装结构3a的截面图。图7的封装结构3a类似于图1到图6的封装结构3,不同处在于布线结构1a的测试电路结构17a的结构。测试电路结构17中的一个的最外片段171的电连接端173电连接到布线结构1a的电源/接地路径。因此,可省略图6的测试接合材料362。在一些实施例中,测试电路结构17中的一个的最外片段171的电连接端173可电连接到导电电路层15。因此,测试电路结构17可接收来自导电电路层15的测试信号。

57.图8示出根据本公开的一些实施例的封装结构3b的截面图。图8的封装结构3b类似于图1到图6的封装结构3,不同处在于布线结构1b的测试电路结构17的位置。测试电路结构17可安置于导电电路层15的互连部分15a上方。如图8所示,测试电路结构17可安置在第一介电层141的顶部表面(例如,布线结构1a的第一表面11)上和第一导电电路层151的互连部分15a的正上方。因此,最外介电层(即,第一介电层141)可覆盖最外导电电路层(即,第一导电电路层151),且测试电路结构17可安置在最外介电层(即,第一介电层141)上。在一些实施例中,从俯视图来看,测试电路结构17的总面积可大于第一导电电路层151的互连部分15a的总面积,因此,向下电路径174、176可不接触第一导电电路层151的互连部分15a。在一些实施例中,测试电路结构17可安置于导电电路层15的互连部分15a下方。

58.图9示出根据本公开的一些实施例的封装结构3c的截面图。图9的封装结构3c类似于图1到图6的封装结构3,不同处在于布线结构1c的测试电路结构17的位置。第三导电电路层153的互连部分15a、测试电路结构17和屏蔽壁155可安置于同一层处且可同时形成。因此,测试电路结构17可安置于第一导电电路层151下方。布线结构1c的第一金属层中可不存在测试电路结构17。布线结构1c的第一金属层可仅包含第一导电电路层151。

59.图10示出根据本公开的一些实施例的封装结构3d的截面图。图10的封装结构3d类似于图1到图6的封装结构3,不同处在于布线结构1d的测试电路结构17的数量和位置。布线结构1d的金属层中的每一个可包含测试电路结构17。也就是说,第二金属层可进一步包含安置成邻近于第二导电电路层152的互连部分15a的测试电路结构17,第三金属层可进一步包含安置成邻近于第三导电电路层153的互连部分15a的测试电路结构17,且第四金属层可进一步包含安置成邻近于第四导电电路层154的互连部分15a的测试电路结构17。在一些实施例中,安置于不同金属层处的测试电路结构17彼此串联电连接。

60.图11示出根据本公开的一些实施例的测试电路结构17和互连部分15a的立体图。图11的测试电路结构17类似于图3的测试电路结构17,不同处在于测试电路结构17彼此不电连接。也就是说,省略了连接部分175。此外,测试电路结构17中的每一个可包含电连接到向下电路径174的电连接端172,以及电连接到向下电路径176的电连接端173。

61.图12示出根据本公开的一些实施例的测试电路结构17和互连部分15a的立体图。图12的测试电路结构17类似于图11的测试电路结构17,不同处在于测试电路结构17的数量。如图12中所展示,仅存在一个安置在互连部分15a的一侧上的测试电路结构17。

62.图13示出根据本公开的一些实施例的组合件结构4的截面图。组合件结构(assembly structure)4还可为封装结构,且可包含基底衬底40、封装结构3、第三保护材料44、散热器46和多个外部连接器49。

63.基底衬底40可包含玻璃强化型环氧树脂材料(例如,fr4)、双马来酰亚胺三嗪(bt)、环氧树脂、硅、印刷电路板(pcb)材料、玻璃、陶瓷或光可成像介电(pid)材料。基底衬

底40可具有第一表面401和与第一表面401相对的第二表面402。如图13中所展示,基底衬底40可包含第一图案化电路41、第二图案化电路42和多个导电通孔43。第一图案化电路41可安置成邻近于基底衬底40的第一表面401,且第二图案化电路42可安置成邻近于基底衬底40的第二表面402。导电通孔43可延伸穿过基底衬底40,且电连接第一图案化电路41和第二图案化电路42。

64.图13的封装结构3可与图1到图6的封装结构3相同或类似。封装结构3可经由接合材料36电连接到基底衬底40的第一图案化电路41。第三保护材料44(即,底部填充物)安置于封装结构3和基底衬底40之间的空间中以便覆盖和保护接合材料36和第一图案化电路41。

65.散热器46可以是盖或帽结构,并且可界定腔461以用于容纳封装结构3。散热器46的材料可包含金属,例如,铜、铝,和/或其它合适的材料。散热器46的一部分可经由热材料48(例如,热界面材料(thermal interface material,tim))附接到封装结构3的顶部表面以便耗散由第一电子装置24和第二电子装置26生成的热量。散热器46的另一部分(例如,底部部分)可经由粘合剂材料附接到基底衬底40。此外,外部连接器49(例如,焊料球)形成或安置于第二图案化电路42上以用于外部连接。应注意,封装结构3可被图7、8、9、10的封装结构3a、3b、3c、3d代替。

66.在测试过程期间,可从基底衬底40的第二表面402测试测试电路结构17。

67.图14到图21示出根据本公开的一些实施例的测试方法。在一些实施例中,所述方法还可用于制造图1到图6中展示的封装结构3,以及图13的组合件结构4。

68.参看图14,提供载体50。载体50可以是晶片型或条带型。载体50可包含安置在其上的离型层52。接着,布线结构1'形成或安置于载体50上的离型层52上。图14的布线结构1'可类似于图5的布线结构1,且可具有第一表面11、与第一表面11相对的第二表面12、高线密度区16(或精细线区)、第一芯片接合区域18和第二芯片接合区域19。布线结构1'可包含至少一个介电层14、与介电层14接触的至少一个导电电路层15、与介电层14接触的至少一个测试电路层17,以及多个突出衬垫20。举例来说,如图14所示,布线结构1'包含第一介电层141、第一导电电路层151、第二介电层142、第二导电电路层152、第三介电层143、第三导电电路层153、第四介电层144、第四导电电路层154和第五介电层145。

69.第一导电电路层151可包含互连部分15a和外围部分15b。互连部分15a位于高线密度区16中,并且外围部分15b位于高线密度区16外部(例如,低密度区)。互连部分15a的导电迹线15'的线宽/线距(l/s)可小于外围部分15b的导电迹线15"的l/s。

70.测试电路结构17可安置成邻近于导电电路层15的互连部分15a。在一些实施例中,布线结构1'可包含多个互连部分15a、多个测试电路结构17和多个屏蔽壁155。互连部分15a、测试电路结构17和屏蔽壁155可安置于同一层处且可同时形成。测试电路结构17和屏蔽壁155可位于高线密度区16中。

71.在一些实施例中,测试电路结构17可以是虚设的,且可以不电连接到导电电路层15的互连部分15a。也就是说,测试电路结构17可与导电电路层15的互连部分15a电隔离。举例来说,导电电路层15的互连部分15a可用于传输信号(例如,数字信号),而测试电路结构17不具有传输信号(例如,数字信号)的功能。

72.如图2所示,测试电路结构17的型式(或图案或布局)可与导电电路层15的互连部

分15a的型式(或图案或布局)类似或相同。举例来说,测试电路结构17可包含彼此平行的多个片段171。测试电路结构17的片段171的线宽/线距(l/s)可大体上等于互连部分15a的导电迹线15'的线宽/线距(l/s)。此外,互连部分15a的导电迹线15'和屏蔽壁155可与测试电路结构17的片段171大体上平行。如图2和图3所示,测试电路结构17中的每一个的片段171彼此串联连接。此外,测试电路结构17可经由连接部分175彼此电连接。如图3和图5所示,测试电路结构17的一端可电连接到布线结构1'的第二表面12。测试电路结构17上不存在突出衬垫20。测试电路结构17可不含向上电连接。

73.突出衬垫20可安置在布线结构1'的第一介电层141(即,最顶部介电层或最外介电层)上并且从所述第一介电层141突出。突出衬垫20可安置在布线结构1'的第一表面11上且从所述第一表面11突出,并延伸穿过第一介电层141(即,最顶部介电层或最外介电层)以电连接第一导电电路层151。突出衬垫20可包含多个第一突出衬垫21和多个第二突出衬垫22。

74.参看图15,第一电子装置24和第二电子装置26通过倒装芯片接合电连接到布线结构1'的导电电路层15。因此,第二电子装置26可经由导电电路层15的互连部分15a电连接到第一电子装置24。在一些实施例中,第一电子装置24的第一电接触件244可经由多个接合材料245电连接和物理连接到第一突出衬垫21。在一些实施例中,第二电子装置26的第二电接触件264可经由多个接合材料265电连接和物理连接到第二突出衬垫22。

75.参看图16,第一保护材料32(即,底部填充物)形成或安置在第一电子装置24和布线结构1'之间的第一空间25以及第二电子装置26和布线结构1'之间的第二空间27中,以便覆盖布线结构1'、第一电子装置24和第二电子装置26,且保护由第一电接触件244、第一突出衬垫21和接合材料245形成的接合结构,以及由第二电接触件264、第二突出衬垫22和接合材料265形成的接合结构。此外,第一保护材料32可进一步延伸到第一电子装置24的侧面243和第二电子装置26的侧面263之间的间隙30中。

76.参看图17,形成或安置封装体34(即,第二保护材料)以覆盖布线结构1'的第一表面11的至少一部分、第一电子装置24的至少一部分、第二电子装置26的至少一部分和第一保护材料32。封装体34具有第一表面341(例如,顶部表面)。

77.参看图18,移除载体50和离型层52。因此,暴露布线结构1'的第二表面12,且从布线结构1'的第二表面12暴露第四导电电路层154的部分(即,导通孔部分15c的底部部分)。

78.接着,可从布线结构1'的第二表面12(例如,底部表面)经由向下电路径174、176对测试电路结构17进行测试。此测试可以是如下文描述的例如断路/短路测试(open/short test)等电测试。分别实施或提供测试设备的第一探针91和第二探针来接触向下电路径174和向下电路径176(图6)。在一些实施例中,测试信号施加到电路径中的一个(例如,测试信号可经由第一探针91施加到向下电路径174),且电路径中的另一个接地(例如,向下电路径176可经由第二探针电连接到接地层)。.举例来说,测试信号可以是测试电流。因此,测试电流可经由第一探针91施加到向下电路径174。接着,测量两个电路径174、176之间的电压。使用测得的电压来判断向下电路径174、176之间是否发生断路。如果测试电路结构17中发生断路,则可推测在导电电路层15的互连部分15a中发生断路。也就是说,可认为导电电路层15的互连部分15a断裂或破损。因此,导电电路层15的互连部分15a的质量可被判定为不合格或异常。

79.在本公开中,因为测试电路结构17的型式(或图案或布局)与导电电路层15的互连

部分15a的型式(或图案或布局)类似或相同,所以测试电路结构17可模拟导电电路层15的互连部分15a的状况。也就是说,如果测试电路结构17的片段171断裂或破损,且测试电路结构17中发生断路,则可认为导电电路层15的互连部分15a的导电迹线15'断裂或破损。

80.应注意,如图7所示,如果测试电路结构17中的一个的最外片段171的电连接端173电连接到布线结构1a的电源/接地路径,则可省略第二探针。

81.参看图19,多个接合材料36(例如,焊料球)形成或安置在布线结构1'的第二表面12上。如图19中所展示,接合材料36安置在第四导电电路层154的暴露部分(即,导通孔部分15c的底部部分)上。在一些实施例中,接合材料36可包含两个测试接合材料361、362(图6)。测试接合材料361电连接到向下电路径174,且测试接合材料362电连接到向下电路径176。在一些实施例中,可对测试接合材料361、362进行上文提及的测试(电测试)以测试测试电路结构17。举例来说,第一探针91可接触测试接合材料361,且第二探针可接触接合材料362。

82.参看图20,封装体34从其第一表面341薄化。因此,封装体34的第一表面341、第一电子装置24的第一背面242、第二电子装置26的第二背面262和间隙30中的第一保护材料32的顶部表面可彼此大体上共面。

83.在一些实施例中,可对布线结构1'进行分离工艺(singulation process),以便获得多个图1到图6所示的封装结构3。

84.参看图21,封装结构3可经由接合材料36电连接到基底衬底40的第一图案化电路41。基底衬底40可具有第一表面401和与第一表面401相对的第二表面402。基底衬底40可包含第一图案化电路41、第二图案化电路42和多个导电通孔43。第一图案化电路41可安置成邻近于基底衬底40的第一表面401,且第二图案化电路42可安置成邻近于基底衬底40的第二表面402。导电通孔43可延伸穿过基底衬底40且电连接第一图案化电路41和第二图案化电路42。接着,第三保护材料44(即,底部填充物)形成或安置在封装结构3和基底衬底40之间的空间中以便覆盖和保护接合材料36和第一图案化电路41。

85.接着,散热器46可附接到第一电子装置24、第二电子装置26和基底衬底40。在一些实施例中,散热器46可以是盖或帽结构,并且可界定腔461以用于容纳封装结构3。散热器46的一部分可经由热材料48(例如,热界面材料(tim))附接到封装结构3的顶部表面。散热器46的另一部分(例如,底部部分)可经由粘合剂材料附接到基底衬底40。接着,多个外部连接器49(例如,焊料球)可形成或安置于第二导电电路层42上以用于外部连接。

86.在一些实施例中,可对外部连接器49(对基底衬底40的第二表面402)进行上文提及的测试(电测试)以测试测试电路结构17。接着,可对布线结构1'进行分离工艺,以便获得多个图13中所示的组合件结构4。

87.除非另外说明,否则例如“上方”、“下方”、“上”、“左”、“右”、“下”、“顶部”、“底部”、“竖直”、“水平”、“侧面”、“高于”、“低于”、“上部”、“在

……

上”、“在

……

下”等空间描述是相对于图中所示的定向来指示的。应理解,本文中所使用的空间描述仅出于说明的目的,且本文中所描述的结构的实际实施方案可以任何定向或方式在空间上布置,其限制条件为本公开的实施例的优点不会因此布置而有偏差。

88.如本文中所使用,术语“大致”、“大体上”、“实质”和“约”用于描述和解释小的变化。当与事件或情形结合使用时,所述术语可以指其中事件或情形明确发生的情况以及其

中事件或情形极接近于发生的情况。举例来说,当与数值结合使用时,术语可指小于或等于所述数值的

±

10%的变化范围,例如小于或等于

±

5%、小于或等于

±

4%、小于或等于

±

3%、小于或等于

±

2%、小于或等于

±

1%、小于或等于

±

0.5%、小于或等于

±

0.1%,或者小于或等于

±

0.05%。举例来说,如果两个数值之间的差小于或等于所述值的平均值的

±

10%(例如小于或等于

±

5%、小于或等于

±

4%、小于或等于

±

3%、小于或等于

±

2%、小于或等于

±

1%、小于或等于

±

0.5%、小于或等于

±

0.1%、或者小于或等于

±

0.05%),则可认为所述两个数值“大体上”相同或相等。

89.如果两个表面之间的位移不超过5μm、不超过2μm、不超过1μm或不超过0.5μm,则可认为这两个表面是共面的或大体上共面的。

90.如本文中所使用,除非上下文另外明确规定,否则单数术语“一(a/an)”和“所述”可包含复数个提及物。

91.如本文中所使用,术语“导电”和“电导率”指代运送电流的能力。导电材料通常指示展现对于电流流动的极少或零对抗的那些材料。电导率的一个量度是西门子/米(s/m)。通常,导电材料是电导率大于约104s/m(例如至少105s/m或至少106s/m)的一种材料。材料的电导率有时可随温度而改变。除非另外规定,否则在室温下测量材料的电导率。

92.另外,有时在本文中按范围格式呈现量、比率和其它数值。应理解,此类范围格式是为了便利和简洁起见,且应灵活地理解,不仅包含明确地指定为范围限制的数值,而且包含涵盖于所述范围内的所有个别数值或子范围,如同明确地指定每一数值和子范围一般。

93.虽然已参考本公开的具体实施例描述并说明本公开,但这些描述和说明并非限制性的。所属领域的技术人员应理解,可在不脱离如由所附权利要求书定义的本公开的真实精神和范围的情况下,作出各种改变且取代等效物。图示可能未必按比例绘制。由于制造工艺和公差,本公开中的工艺再现与实际设备之间可能存在区别。可存在未特定说明的本公开的其它实施例。应将说明书和图式视为说明性的,而非限制性的。可做出修改,以使特定情形、材料、物质组成、方法或工艺适应于本公开的目标、精神及范围。所有此类修改都希望在所附权利要求书的范围内。虽然本文中公开的方法已参考按特定次序执行的特定操作加以描述,但应理解,可在不脱离本公开的教示的情况下组合、细分或重新排序这些操作以形成等效方法。相应地,除非本文中特别指示,否则操作的次序和分组并非对本公开的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1