半导体元件结构及其制备方法与流程

1.本公开主张2020年3月6日申请的美国正式申请案第16/811,824号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

背景技术:

2.当半导体元件结构变得更小且更高度整合(highly integrated)时,已经发展出许多制造具有微图案的半导体元件结构的技术。特别地是,一光刻工艺(photolithography process)是典型地被用来在一基底上制造电子或光电元件(electronic and optoelectronic devices),且由光刻工艺所制备的光刻胶图案(photoresist patterns)是在蚀刻(etching)或离子植入(ion implantation)工艺中当作是遮罩。当所需之间距尺寸(pitch size)与临界尺寸(critical dimension,cd)持续变小时,光刻胶图案的精细度(fineness)在整合程度上变成是一个非常重要的参数(important factor)。然而,用于制造半导体部件(semiconductor features)的光刻工艺在曝光设备(exposure apparatus)的持续提升的分辨率中存在有一限制。

3.虽然存在具有微图案的半导体元件结构及其制备方法是已满足其预期目的,但其并非所有方面已完全地满足。因此,针对经由光刻工艺所制备的具有微图案的半导体元件结构的技术,目前仍有许多问题必须克服。

4.上文的“现有技术”说明仅是提供背景技术,并未承认上文的“现有技术”说明公开本公开的标的,不构成本公开的现有技术,且上文的“现有技术”的任何说明均不应作为本公开的任一部分。

技术实现要素:

5.本公开的一实施例提供一种半导体元件结构。该半导体元件结构包括一基底;一第一目标结构,设置在该基底上,其中该第一目标结构包括一第一部分、一第二部分以及一第三部分,该第三部分连接到该第一部分与该第二部分,该第一部分的一高度与该第二部分的一高度大于该第三部分的一高度;一第二目标结构,设置在该第一目标结构上,其中该第二目标结构包括一第四部分、一第五部分以及一第六部分,该第六部分连接到该第四部分与该第五部分;一低位面导电图案,位于该第一目标结构与该第二目标结构之间;以及一高位面导电图案,位于该第一目标结构中。

6.在本公开的一些实施例中,该低位面导电图案具有一第一上端以及一第一下端,该高位面导电图案具有一第二上端以及一第二下端,该第一下端低于该第二下端,且该第一上端与该第二上端大致在相同位面。

7.在本公开的一些实施例中,该半导体元件结构还包括一第一高气隙以及一第二高气隙,该第一高气隙位于该第一目标结构与该低位面导电图案之间,该第二高气隙位于该第二目标结构与该低位面导电图案之间。

8.在本公开的一些实施例中,在剖视图中,该第一高气隙与该第二高气隙具有间隙

子轮廓。

9.在本公开的一些实施例中,该第一高气隙与该第二高气隙大致以在该第一目标结构与该第二目标结构之间的一中间线而对称设置。

10.在本公开的一些实施例中,该半导体元件结构还包括一第三高气隙,其中该第一高气隙位于该第二部分的一侧壁上,且该第三高气隙位于该第一部分的一侧壁上。

11.在本公开的一些实施例中,该第一高气隙与该第三高气隙大致以在该第一部分与该第二部分之间的一中间线而对称设置。

12.在本公开的一些实施例中,该半导体元件结构还包括一第一高介电间隙子以及一第二高介电间隙子,该第一高介电间隙子位于该第一高气隙与该低位面导电图案之间,该第二高介电间隙子位于该第二高气隙与该低位面导电图案之间。

13.在本公开的一些实施例中,该半导体元件结构还包括一第一矮气隙以及一第一矮介电间隙子,其是位于该第一高气隙与该高位面导电图案之间。

14.在本公开的一些实施例中,该半导体元件结构还包括一第一矮气隙以及一第二矮气隙,其是设置在该高位面导电图案的两侧。

15.在本公开的一些实施例中,该第一矮气隙与该第二矮气隙大致以在该第一部分与该第二部分之间的一中间线而对称设置。

16.在本公开的一些实施例中,该高位面导电图案位于该第一部分与该第二部分之间。

17.在本公开的一些实施例中,该半导体元件结构还包括一高气隙以及一矮气隙,该高气隙位于该低位面导电图案与该第二部分之间,该矮气隙位于该高位面导电图案与该第二部分之间。

18.在本公开的一些实施例中,在剖视图中,该高气隙与该矮气隙具有间隙子轮廓。

19.在本公开的一些实施例中,该第一部分与该第二部分大致以在该第一部分与该第二部分之间的一中间线而对称设置。

20.本公开的一实施例提供一种半导体元件结构的制备方法。该方法包括形成一硬遮罩材料在一基底上;蚀刻该硬遮罩材料以形成多个硬遮罩柱;形成多个间隙子在所述多个硬遮罩柱的侧壁表面上;蚀刻所述多个硬遮罩柱与该目标材料,其是通过所述多个间隙子当作一遮罩进行蚀刻,以一体成形多个目标结构、一高位面凹陷在其中一个目标结构中,以及一低位面凹陷在二目标结构之间;以及一体成形一高位面导电图案在该高位面凹陷中以及一低位面导电图案在该低位面凹陷中。

21.在本公开的一些实施例中,至少一目标结构包括一第一部分、一第二部分以及一第三部分,该第三部分连接到该第一部分与该第二部分,且该方法还包括:形成一高气隙以及一矮气隙,该高气隙位于该低位面导电图案与该第二部分之间,该矮气隙位于该高位面导电图案与该第二部分之间。

22.在本公开的一些实施例中,在剖视图中,该高气隙与该矮气隙具有间隙子轮廓。

23.在本公开的一些实施例中,该方法还包括:形成一第一高介电间隙子以及一第二高介电间隙子,该第一高介电间隙子位于该高气隙与该低位面导电图案之间,该第二高介电间隙子位于该矮气隙与该高层次导电图案之间。

24.在本公开的一些实施例中,至少一目标结构包括一第一部分、一第二部分以及一

第三部分,该第三部分连接到该第一部分与该第二部分,且该方法还包括:形成一高介电间隙子以及一矮介电间隙子,该高介电间隙子位于该低位面导电图案与该第二部分之间,该矮介电间隙子位于该高位面导电图案与该第二部分之间。

25.提供有一半导体元件结构及其制备方法的一些实施例。该半导体元件的制备方法可包括底切一光刻胶图案在一半导体基底上,以及形成一内间隙子元件在该光刻胶图案的一侧壁表面上。该内间隙子元件具有延伸进入该光刻胶图案的一凹陷(例如该底切区)的一部分,以形成一基脚(footing),且该内间隙子元件的该部分的一宽度是随着该部分向该半导体基板的延伸而连续增加。因此,该内间隙子元件可避免在该光刻胶图案移除之后的塌陷。

26.此外,该高位面导电图案与该低位面导电图案之下端是位于不同位面(level),且在该高位面导电图案与该低位面导电图案之间有多个气隙。因此,可有效地降低在该高位面导电图案与该低位面导电图案之间的寄生电容。也就是说,可通过在该高位面导电图案与该低位面导电图案之间延伸的距离,来显着减轻在该高位面导电图案与该低位面导电图案上感应或施加的电子信号之间的干扰效应(interference effect)。

27.上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得优选了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文公开的概念与特定实施例可作为修改或设计其它结构或工艺而实现与本公开相同的目的。本公开所属技术领域中技术人员亦应了解,这类等效建构无法脱离权利要求所界定的本公开的构思和范围。

附图说明

28.参阅实施方式与权利要求合并考量附图时,可得以更全面了解本公开的公开内容,附图中相同的元件符号是指相同的元件。

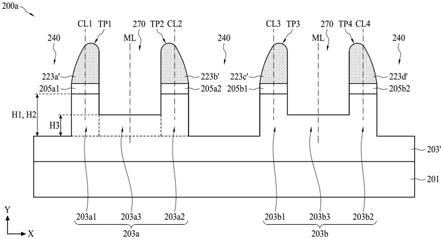

29.图1为依据本公开一些实施例一种半导体元件结构的剖视示意图。

30.图2为依据本公开一些实施例一种半导体元件结构的剖视示意图。

31.图3为依据本公开一些实施例一种半导体元件结构的剖视示意图。

32.图4为依据本公开一些实施例一种半导体元件结构的制备方法的流程示意图。

33.图5为依据本公开一些实施例一种半导体元件结构的制备方法的流程示意图。

34.图6为依据本公开一些实施例中多个硬遮罩柱以及多个光刻胶图案形成在一基底上的一中间阶段的剖视示意图。

35.图7为依据本公开一些实施例中一共形间隙子材料形成在该基底上的一中间阶段的剖视示意图。

36.图8为依据本公开一些实施例中一间隙子元件形成在该基底上的一中间阶段的剖视示意图。

37.图9为依据本公开一些实施例中多个凹陷形成在该基底上的一中间阶段的剖视示意图。

38.图10为依据本公开一些实施例中一第一间隙子层形成在该基底上的一中间阶段的剖视示意图。

39.图11为依据本公开一些实施例中多个第一间隙子形成在该基底上的一中间阶段

的剖视示意图。

40.图12为依据本公开一些实施例中一第二间隙子层形成在该基底上的一中间阶段的剖视示意图。

41.图13为依据本公开一些实施例中多个第二间隙子形成在该基底上的一中间阶段的剖视示意图。

42.图14为依据本公开一些实施例中一衬垫层形成在该基底上的一中间阶段的剖视示意图。

43.图15为依据本公开一些实施例中一高位面导电图案以及一低位面导电图案形成在该基底上的一中间阶段的剖视示意图。

44.图16为依据本公开一些实施例中执行一平坦化工艺在该基底上的一中间阶段的剖视示意图。

45.图17为依据本公开一些实施例中多个气隙形成在该基底上的一中间阶段的剖视示意图。

46.图18为依据本公开一些实施例中多个硬遮罩柱以及多个光刻胶图案形成在一基底上的一中间阶段的剖视示意图。

47.图19为依据本公开一些实施例中一共形间隙子材料形成在该基底上的一中间阶段的剖视示意图。

48.图20为依据本公开一些实施例中一间隙子元件形成在该基底上的一中间阶段的剖视示意图。

49.图21为依据本公开一些实施例中一能量可移除图案形成在一基底上的一中间阶段的剖视示意图。

50.图22为依据本公开一些实施例中一共形间隙子材料形成在所述多个能量可移除图案上的一中间阶段的剖视示意图。

51.图23为依据本公开一些实施例中一间隙子元件形成在该基底上的一中间阶段的剖视示意图。

52.图24为依据本公开一些实施例中围绕所述多个能量可移除图案的一介电层以及多个间隙子形成在该半导体元件结构上的一中间阶段的剖视示意图。

53.图25为依据本公开一些实施例中使用所述多个间隙子当作一蚀刻遮罩以蚀刻所述多个能量可移除图案、该介电层以及该目标材料之后,形成一半导体元件结构的剖视示意图。

54.附图标记说明:

55.101:半导体基底

56.103:光刻胶图案

57.200a:半导体元件结构

58.200b:半导体元件结构

59.201:半导体基底

60.203:目标材料

61.203’:目标层

62.203a:目标结构

63.203a1:第一部分

64.203a2:第二部分

65.203a3:第三部分

66.203b:目标结构

67.203b1:第四部分

68.203b2:第五部分

69.203b3:第六部分

70.205:硬遮罩层

71.205a:硬遮罩部

72.205a1:硬遮罩结构

73.205a2:硬遮罩结构

74.205b:硬遮罩部

75.205b1:硬遮罩结构

76.205b2:硬遮罩结构

77.207a:硬遮罩柱

78.207b:硬遮罩柱

79.209a:光刻胶图案

80.209b:光刻胶图案

81.210:开孔

82.213:间隙子材料

83.220:开孔

84.223a:间隙子

85.223a’:间隙子元件

86.223b:间隙子

87.223b’:间隙子元件

88.223c:间隙子

89.223c’:间隙子元件

90.223d:间隙子

91.223d’:间隙子元件

92.230:开孔

93.240:凹陷

94.270:凹陷

95.300:半导体元件结构

96.301:半导体基底

97.301t:上表面

98.303:目标材料

99.303a:目标结构

100.303b:目标结构

101.303c:目标结构

102.303d:目标结构

103.304a:上表面

104.304b:上表面

105.305:能量可移除图案

106.307:间隙子材料

107.307a’:间隙子元件

108.307b’:间隙子元件

109.307c’:间隙子元件

110.307d’:间隙子元件

111.308b1:下表面

112.308b2:下表面

113.308i:内表面

114.308o:外表面

115.309:介电层

116.310:开孔

117.403a:高位面导电图案

118.403a

‑

1:第二上端

119.403a

‑

2:第二下端

120.403b:低位面导电图案

121.403b

‑

1:第一上端

122.403b

‑

2:第一下端

123.501:第一间隙子层

124.503:第一间隙子

125.505:第二间隙子层

126.507:第二间隙子

127.507a

‑

1:第一矮介电间隙子

128.507b

‑

1:第一高介电间隙子

129.507b

‑

2:第二高介电间隙子

130.509:衬垫层

131.511:气隙

132.511a

‑

1:第一矮气隙

133.511a

‑

2:第二矮气隙

134.511b

‑

1:第一高气隙

135.511b

‑

2:第二高气隙

136.511b

‑

3:第三高气隙

137.513:钝化层

138.cl1:中心线

139.cl2:中心线

140.cl3:中心线

141.cl4:中心线

142.h1:高度

143.h2:高度

144.h3:高度

145.ml:中间线

146.ml

‑

1:中间线

147.ml

‑

2:中间线

148.tp1:最高点

149.tp2:最高点

150.tp3:最高点

151.tp4:最高点

152.w1:宽度

153.w2:宽度

154.20:制备方法

155.s21:步骤

156.s23:步骤

157.s25:步骤

158.s27:步骤

159.s28:步骤

160.s29:步骤

161.30:制备方法

162.s31:步骤

163.s33:步骤

164.s35:步骤

165.s37:步骤

166.s39:步骤

具体实施方式

167.本公开的以下说明伴随并入且组成说明书的一部分的附图,说明本公开的实施例,然而本公开并不受限于该实施例。此外,以下的实施例可适当整合以下实施例以完成另一实施例。

[0168]“一实施例”、“实施例”、“例示实施例”、“其他实施例”、“另一实施例”等是指本公开所描述的实施例可包含特定特征、结构或是特性,然而并非每一实施例必须包含该特定特征、结构或是特性。再者,重复使用“在实施例中”一语并非必须指相同实施例,然而可为相同实施例。

[0169]

为了使得本公开可被完全理解,以下说明提供详细的步骤与结构。显然,本公开的实施不会限制该技艺中的技术人士已知的特定细节。此外,已知的结构与步骤不再详述,以免不必要地限制本公开。本公开的优选实施例详述如下。然而,除了详细说明之外,本公开亦可广泛实施于其他实施例中。本公开的范围不限于详细说明的内容,而是由权利要求定

义。

[0170]

应当理解,以下公开内容提供用于实作本发明的不同特征的诸多不同的实施例或实例。以下阐述组件及排列形式的具体实施例或实例以简化本公开内容。当然,所述多个仅为实例且不旨在进行限制。举例而言,元件的尺寸并非仅限于所公开范围或值,而是可相依于工艺条件及/或装置的所期望性质。此外,以下说明中将第一特征形成于第二特征“之上”或第二特征“上”可包括其中第一特征及第二特征被形成为直接接触的实施例,且亦可包括其中第一特征与第二特征之间可形成有附加特征、进而使得所述第一特征与所述第二特征可能不直接接触的实施例。为简洁及清晰起见,可按不同比例任意绘制各种特征。在附图中,为简化起见,可省略一些层/特征。

[0171]

此外,为易于说明,本文中可能使用例如“之下(beneath)”、“下面(below)”、“下部的(lower)”、“上方(above)”、“上部的(upper)”等空间相对关系用语来阐述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对关系用语旨在除图中所示出的取向外亦囊括元件在使用或操作中的不同取向。所述装置可具有其他取向(旋转90度或处于其他取向)且本文中所用的空间相对关系描述语可同样相应地进行解释。

[0172]

图1为依据本公开一些实施例一种半导体元件结构200a的剖视示意图。如图1所示,依据一些实施例,半导体元件结构200a具有一目标层203’以及目标结构203a、203b,目标层203’设置在一半导体基底201上,目标结构203a与203b设置在目标层203’上。

[0173]

在目标结构203a与目标层203’之间以及目标结构203b与目标层203’之间并未存在明显的界面。如图1所示的虚线是用以阐明本公开。应当理解,依据一些实施例,目标结构203a与203b以及目标层203’由相同材料所制,并同时从相同材料层所形成。

[0174]

更特别地,目标结构203a具有一第一部分203a1、一第二部分203a2以及一第三部分203a3,第三部分203a3位于第一部分203a1与第二部分203a2之间。类似地,目标结构203b具有一第四部分203b1、一第五部分203b2以及一第六部分203b3,第六部分203b3位于第四部分203b1与第五部分203b2之间。

[0175]

在第一部分203a1与第三部分203a3之间以及在第三部分203a3与第二部分203a2之间并未存在明显的界面。类似地,在第四部分203b1与第六部分203b3间以及在第六部分203b3与第五部分203b2之间并未存在明显的界面。如图1所示的虚线用于阐明本公开。

[0176]

在目标结构203a中,第一部分203a1沿y方向具有一高度h1,第二部分203a2沿y方向具有一高度h2,且第三部分203a3沿y’向具有一高度h3。在一些实施例中,第一高度h1大致相同于高度h2,且高度h3大于高度h1与h2。在本公开的内容中,字词“大致(substantially)”意指优选者为至少90%,优选者为95%,再优选者为98%,且最佳者为99%。在一些实施例中,第一部分203a1、第二部分203a2以及第三部分203a3形成一u形结构。

[0177]

目标结构203b的特征是类似于上述目标结构203a的特征,且在文中不再重复其描述。举例来说,依据一些实施例,第四部分203b1、第五部分203b2以及第六部分203b3形成另一个u形结构。

[0178]

在一些实施例中,半导体元件结构200a亦具有硬遮罩结构205a1、205a2、205b1、205b2,硬遮罩结构205a1设置在目标结构203a的第一部分203a1上,硬遮罩结构205a2设置在目标结构203a的第二部分203a2上,硬遮罩结构205b1设置在目标结构203b的第四部分

203b1上,硬遮罩结构205b2设置在目标结构203b的第五部分203b2上。依据一些实施例,硬遮罩结构205a1、205a2、205b1、205b2由相同材料所制,且同时从相同材料层所形成。

[0179]

在一些实施例中,半导体元件结构200a还具有间隙子元件223a’、223b’、223c’、223d’,间隙子元件223a’设置在硬遮罩结构205a1上,间隙子元件223b’设置在硬遮罩结构205a2上,间隙子元件223c’设置在硬遮罩结构205b1上,间隙子元件223d’设置在硬遮罩结构205b2上。依据一些实施例,间隙子元件223a’、223b’、223c’、223d’由相同材料所制,并同时从相同材料层所形成。

[0180]

如图2的剖视图所示,目标结构203a的第一部分203a1具有一中心线cl1,目标结构203a的第二部分203a2具有一中心线cl2,目标结构203b的第四部分203b1具有一中心线cl3,且目标结构203b的第五部分203b2具有一中心线cl4。再者,间隙子元件223a’具有一最高点tp1,间隙子元件223b’具有一最高点tp2,间隙子元件223c’具有一最高点tp3,以及间隙子元件223d’具有一最高点tp4。

[0181]

尤其是,在图2的剖视图中,依据一些实施例,间隙子元件223a’的最高点tp1与间隙子元件223b’的最高点tp2位于中心线cl1与中心线cl2之间,且间隙子元件223c’的最高点tp3与间隙子元件223d’的最高点tp4位于中心线cl3与中心线cl4之间。

[0182]

在一些实施例中,多个凹陷270设置在目标结构203a与203b上,而多个凹陷240形成在相邻的目标结构之间(例如目标结构203a与203b之间)。在一些实施例中,间隙子元件223a’与223b’通过其中一个凹陷270而分开设置,间隙子元件223c’与223d’通过另一个凹陷270而分开设置,且间隙子元件223b’与223’通过其中一个凹陷240而分开设置。应当理解,依据一些实施例,所述多个凹陷240较深于所述多个凹陷270(例如延伸到在y方向的一较低位面)。

[0183]

图2为依据本公开一些实施例一种半导体元件结构200b的剖视示意图,而半导体元件结构200b为半导体元件结构200a的另一实施例。为了保持一致与清晰,在图1与图2中均有出现的类似元件是具有相同元件编号。在如图1所示的实施例以及如图2所示的实施例之间的一差异,在于硬遮罩结构205a1、205a2、205b1、205b2并未形成在如图2所示的实施例中。

[0184]

图3为依据本公开一些实施例一种半导体元件结构300的剖视示意图。如图3所示,依据一些实施例,半导体元件结构300具有目标结构303a、303b、303c、303d以及间隙子元件307a’、307b’、307c’、307d’,目标结构303a、303b、303c、303d设置在一半导体基底301上,间隙子元件307a’、307b’、307c’、307d’设置在目标结构303a、303b、303c、303d上。

[0185]

在一些实施例中,间隙子元件307a’设置在目标结构303a上,间隙子元件307b’设置在目标结构303b上,间隙子元件307c’设置在目标结构303c上,间隙子元件307d’设置在目标结构303d上。再者,在一些实施例中,每一相邻对之间隙子元件307a’、307b’、307c’、307d’通过一开孔310而分开设置。在一些实施例中,每一相邻对的目标结构303a、303b、303c、303d通过其中一开孔310而分开设置,以使半导体基底301的一上表面301t暴露在开孔310中。

[0186]

如图3所示,目标结构303a具有一中心线cl1,目标结构303b具有一中心线cl2,目标结构303c具有一中心线cl3,目标结构303d具有一中心线cl4。再者,间隙子元件307a’具有一最高点tp1,间隙子元件307b’具有一最高点tp2,间隙子元件307c’具有一最高点tp3,

间隙子元件307d’具有一最高点tp4。

[0187]

在一些实施例中,如图3所示,依据一些实施例,间隙子元件307a’的最高点tp1与间隙子元件307b’的最高点tp2位于中心线cl1与中心线cl2之间,间隙子元件307c’的最高点tp3与间隙子元件307d’的最高点tp4位于中心线cl3与中心线cl4之间。

[0188]

图4为依据本公开一些实施例一种半导体元件结构(例如半导体元件结构200a或200b)的制备方法20的流程示意图,其中,依据一些实施例,制备方法20具有步骤s21、s23、s25、s27、s28、s29。

[0189]

依据一些实施例,结合图6至图17以详细阐述图4的步骤s21到s29,其是示出在形成半导体元件结构200a中按序各中间阶段的剖视示意图。依据一些其他实施例,结合图6至图17以详细阐述图4的步骤s21到s29,其是示出在形成半导体元件结构200b中按序各中间阶段的剖视示意图。

[0190]

如图6所示,提供半导体基底201,且一目标材料203设置在半导体基底201上。个别的步骤是示出在如图4所示的制备方法20中的步骤s21。半导体基底201的详细内容可类似于或相同于半导体基底101的详细内容,且在文中不再重复详细描述。

[0191]

在一些实施例中,目标材料203为一介电层。举例来说,目标材料203由下列材料所制:氧化硅、碳化硅、氮化硅、氮氧化硅、其他适合的介电材料或其组合。在一些实施例中,目标材料203具有一内连接结构,其是具有形成在目标材料203上的一或多个金属化层(例如铜层),且内连接结构用于连接各式不同的电子元件以形成功能电路。在一些实施例中,目标材料203通过任何适合的工艺所形成,例如沉积、镶嵌(damascene)及/或双镶嵌。

[0192]

仍请参考图6,依据一些实施例,一硬遮罩层205设置在目标材料203上,且硬遮罩柱207a与207b通过一蚀刻工艺而设置在硬遮罩层205上,而其是使用光刻胶图案209a与209b当作一遮罩以进行该蚀刻工艺。在一些实施例中,硬遮罩层205与硬遮罩柱207a、207b由介电材料所制,例如氧化硅、碳化硅、氮化硅、氮氧化硅、一或多个适合的材料或其组合。

[0193]

在一些实施例中,依据一些实施例,硬遮罩层205与硬遮罩柱207a、207b通过一沉积工艺以及一蚀刻工艺所形成。举例来说,一遮罩材料(图未示)可共形地沉积在目标层205的上表面上,且光刻胶图案209a与209b设置在硬遮罩材料上。用于形成光刻胶图案209a与209b的一些工艺硅类似于或相同于用于形成所述多个光刻胶图案103的工艺,且在文中不再重复详细描述。如图6所示,在光刻胶图案209a与209b形成之后,硬遮罩材料通过光刻胶图案209a与209b暴露的一些部分是通过一干蚀刻工艺而移除,以形成多个开孔210在相邻的硬遮罩柱之间(例如硬遮罩柱207a与207b)。个别的步骤是示出在如图4所示的制备方法20中的步骤s23及步骤s25。

[0194]

应当理解,依据一些实施例,目标材料203并未通过开孔210而暴露。再者,依据一些实施例,硬遮罩层205以及硬遮罩柱207a、207b由相同材料所制且同时形成。在获得开孔210之后,可移除光刻胶图案209a与209b。

[0195]

请参考图7,在一些实施例中,依据一些实施例,在移除光刻胶图案209a与209b之后,一间隙子材料213共形地沉积在硬遮罩柱207a、207b的上表面与侧壁表面上,以及沉积在硬遮罩层205的上表面上,以便获得缩减的开孔220。

[0196]

在一些实施例中,间隙子材料213由下列材料所制:氧化硅、碳化硅、氮化硅、氮氧化硅、其他适合的材料或其组合,而用于形成间隙子材料213的沉积工艺,包括一化学气相

沉积(cvd)工艺、一物理气相沉积(pvd)工艺、一原子层沉积(ald)工艺、一旋转涂布工艺或其他适合的工艺。在一些实施例中,间隙子材料213的材料不同于硬遮罩柱207a与207b的材料。应当理解,硬遮罩柱207a与207b的材料相对于间隙子材料213的材料是具有一高蚀刻选择性。

[0197]

请参考图8,依据一些实施例,蚀刻间隙子材料213以形成间隙子223a、223b、223c、223d在硬遮罩柱207a、207b的侧壁表面上。个别的步骤是示出在如图4所示的制备方法20中的步骤s27。在一些实例中,蚀刻工艺为一非等向性蚀刻工艺,其是垂直地移除间隙子材料213在所有位置的相同数量,并余留间隙子223a、223b、223c、223d在硬遮罩柱207a与207b的侧壁表面上。在一些实施例中,蚀刻工艺为一干蚀刻工艺。

[0198]

再者,如图8所示,依据一些实施例,移除硬遮罩层205位于硬遮罩柱207a与207b之间的一些部分,以形成硬遮罩部205a与205b,在相邻的硬遮罩部之间(例如硬遮罩部205a与205b)获得多个开孔230。在一些实施例中,目标材料203通过所述多个开孔230而暴露。在一些实施例中,间隙子223a、223b、223c、223d通过硬遮罩部205a、205b而与目标材料203分开设置。

[0199]

请参考图9,在一些实施例中,依据一些实施例,硬遮罩柱207a与207b、硬遮罩部205a与205b以及目标材料203使用间隙子223a、223b、223c、223d当作一遮罩进行蚀刻,且一体成形一高位面凹陷(浅开孔)270以及一低位面凹陷(深开孔)240。个别的步骤是示出在如图4所示的制备方法20中的步骤s29。在一些实施例中,蚀刻工艺为一干蚀刻工艺。

[0200]

在一些实施例中,依据一些实施例,完全移除硬遮罩柱207a、207b,通过蚀刻硬遮罩部205a、205b以及目标层203’以形成硬遮罩结构205a1、205a2、205b1、205b2,且目标结构203a、203b通过蚀刻目标材料203而设置在目标层203’上。此外,稍微蚀刻间隙子223a、223b、223c、223d,以形成间隙子元件223a’、223b’、223c’、223d’。应当理解,在蚀刻工艺期间,硬遮罩柱207a、207b的材料相对于间隙子223a、223b、223c、223d(例如间隙子元件223a’、223b’、223c’、223d’的材料)具有一高蚀刻选择性。

[0201]

硬遮罩柱207a、207b的材料相对于间隙子223a、223b、223c、223d具有一第一蚀刻选择性;硬遮罩部205a、205b的材料相对于间隙子223a、223b、223c、223d具有一第二蚀刻选择性;且目标材料203的材料相对于间隙子223a、223b、223c、223d具有一第三蚀刻选择性。在一些实施例中,第一蚀刻选择性、第二蚀刻选择性以及第三蚀刻选择性是相互类似。

[0202]

依据一些实施例,由于在蚀刻工艺之前,硬遮罩柱207a、207b的上表面高于目标材料203的上表面,所以在蚀刻工艺之后,低位面凹陷240较深于高位面凹陷270。因此,由于通过下层目标结构203a与203b所提供的支撑,所以间隙子元件223a’、223b’、223c’、223d’可避免塌陷,而目标结构203a与203b为从目标层203’突出的u形结构。

[0203]

再者,因为在用于形成间隙子元件223a’、223b’、223c’、223d’的蚀刻工艺中,硬遮罩柱207a与207b、硬遮罩部205a与205b以及目标材料203相较于间隙子223a、223b、223c、223d具有一较高蚀刻选择性,所以间隙子元件223a’、223b’、223c’、223d’可避免崩塌。

[0204]

请参考图10,在一些实施例中,可移除间隙子元件223a’、223b’、223c’、223d’以及硬遮罩结构205a1、205a2、205b1、205b2,并余留具有目标结构203a、203b的目标层203’在基底201上。在一些实施例中,高位面凹陷270形成在目标结构203a与203b上,且低位面凹陷240形成在相邻目标结构203a与203b之间。

[0205]

接下来,可形成一第一间隙子层501以覆盖目标结构203a与203b。在一些实施例中,第一间隙子层501可由掺杂氧化物所制,例如硼硅玻璃(borosilica glass)、磷硅玻璃(phosphosilica glass)、硼磷硅玻璃(borophosphosilica glass)、硅氟玻璃(fluoride silicate glass)、掺碳氧化硅或其类似物。或者是,在其他实施例中,第一间隙子层501可由一热可分解聚合物(thermal decomposable polymer)或一热可降解聚合物(thermal degradable polymer)所制。

[0206]

请参考图11,在一些实施例中,可执行一蚀刻工艺,例如一非等向性干蚀刻工艺,以形成多个第一间隙子503,而多个第一间隙子503是贴合到目标结构203a的第一部分203a1的各侧壁、目标结构203a的第二部分203a2的各侧壁、目标结构203b的第四部分203b1的各侧壁以及目标结构203b的第五部分203b2的各侧壁。

[0207]

请参考图12,在一些实施例中,可形成一第二间隙子层505以覆盖目标结构203a、203b以及多个第一间隙子503。在一些实施例中,举例来说,第二间隙子层505可由氮化硅所制。

[0208]

请参考图13,在一些实施例中,可执行一蚀刻工艺,例如一非等向性干蚀刻工艺,以形成多个第二间隙子507,而多个第二间隙子507是贴合到多个第一间隙子503的各表面。

[0209]

请参考图14,在一些实施例中,可形成一衬垫层509以覆盖目标结构203a与203b以及多个第二间隙子507。在一些实施例中,举例来说,衬垫层507可由下列材料所制:钛、氮化钛、氮化钛硅(titanium silicon nitride)、钽、氮化钽、氮化钽硅(tantalum silicon nitride)或其组合。

[0210]

请参考图15,在一些实施例中,一导电材料可通过一金属化工艺而沉积进入低位面凹陷240与高位面凹陷270,举例来说,导电材料为掺杂多晶硅、金属、金属氮化物或金属硅化物。在所述的实施例中,导电材料可为钨。在金属化工艺之后,可执行一平坦化工艺,例如化学机械研磨,以移除在衬垫层509上多余的填充材料,以提供一大致平坦表面给接下来的处理步骤,并一体成形一高位面导电图案403a在高位面凹陷270中以及一低位面导电图案403b在低位面凹陷240中。在一些实施例中,高位面导电图案403a以及低位面导电图案403b为当作导电接触点的导电图案,而导电接触点是在不同位面具有下端,用以接触在不同位面的端子(terminals)。

[0211]

在一些实施例中,高位面导电图案403a的下端电性接触一平面晶体管(planar transistor)的一栅极端子(gate terminal),且低位面导电图案403b的下端电性接触该平面晶体管的一源极/漏极端子,其中栅极端子设置在一相对高的位面,而源极/漏极端子设置在一相对低的位面。

[0212]

请参考图16及图17,在一些实施例中,多个气隙511可形成在基底201上。请参考图16,可执行一平坦化工艺,例如化学机械研磨,以移除衬垫层209位于目标结构203a(第一部分203a1与第二部分203a2)以及目标结构203b(第四部分203b1与第五部分203b2)上的部分。在平坦化工艺之后,可暴露多个第一间隙子503设置在邻近目标结构203a的第一部分203a1与第二部分203a2以及目标结构203b的第四部分203b1与第五部分203b2的上表面。

[0213]

请参考图17,可移除设置在邻近目标结构203a的第一部分203a1与第二部分203a2以及目标结构203b的第四部分203b1与第五部分203b2的多个第一间隙子503,以形成多个气隙511。接下来,可形成一钝化层513,以密封多个气隙511。在一些实施例中,可引入一氢

氟酸蒸气(vapor hydrogen fluoride),并蚀刻设置在邻近目标结构203a的第一部分203a1与第二部分203a2以及目标结构203b的第四部分203b1与第五部分203b2的多个第一间隙子503。

[0214]

在一些实施例中,在由掺杂氧化物所制的多个第一间隙子503上,氢氟酸蒸气具有一较高蚀刻率;因此,可选择地移除设置在邻近目标结构203a的第一部分203a1与第二部分203a2以及目标结构203b的第四部分203b1与第五部分203b2的多个第一间隙子503,且由氮化硅所制的多个第二间隙子507可选择地留下。多个第二间隙子507可在接下来例如热处理的处理步骤期间,避免位于高位面凹陷270中的高位面导电图案403a以及位于低位面凹陷240中的低位面导电图案403b流进多个气隙511中。

[0215]

请参考图17,或者是,在另一实施例中,施加一加热工艺以移除由热可分解聚合物或热可降解聚合物所制的多个第一间隙子503。加热工艺的一温度可介于300℃到450℃之间。在一些实施例中,加热工艺的温度可介于350℃到420℃之间。

[0216]

请参考图17,在一些实施例中,高位面导电图案403a位于第一部分203a1与第二部分203a2之间。在一些实施例中,低位面导电图案403b具有一第一上端403b

‑

1以及一第一下端403b

‑

2,高位面导电图案403a具有一第二上端403a

‑

1以及一第二下端403a

‑

2,第一下端403b

‑

2低于第二下端403a

‑

2,且第一上端403b

‑

1与第二上端403a

‑

1大致位于相同位面。在一些实施例中,高位面导电图案403a与低位面导电图案403b的各下端是位于不同位面,且在高位面导电图案403a与低位面导电图案403b之间具有多个气隙。因此,可有效地降低在高位面导电图案403a与低位面导电图案403b之间的寄生电容。也就是说,可通过在高位面导电图案403a与低位面导电图案403b之间延伸的距离,来显着减轻在高位面导电图案403a与低位面导电图案403b上感应或施加的电子信号之间的干扰效应(interference effect)。

[0217]

请参考图17,在一些实施例中,半导体元件结构还包括一第一高气隙511b

‑

1以及一第二高气隙511b

‑

2,第一高气隙511b

‑

1位于第一目标结构203a与低位面导电图案403b之间,第二高气隙511b

‑

2位于第二目标结构203b与低位面导电图案403b之间。在一些实施例中,在剖视图中,第一高气隙511b

‑

1与第二高气隙511b

‑

2具有间隙子轮廓(spacer profiles)。在一些实施例中,第一高气隙511b

‑

1与第二高气隙511b

‑

2大致以位于第一目标结构203a与第二目标结构203b之间的一中间线ml

‑

1而对称设置。

[0218]

请参考图17,在一些实施例中,半导体元件结构还包括一第三高气隙511b

‑

3,其中第一高气隙511b

‑

1位于第二部分203a2的一侧壁上,且第三高气隙511b

‑

3位于第一部分203a1的一侧壁上。在一些实施例中,第一高气隙511b

‑

1与第三高气隙511b

‑

3大致以位于第一部分203a1与第二部分203a2之间的一中间线ml

‑

2而对称设置。

[0219]

请参考图17,在一些实施例中,半导体元件结构还包括一第一高介电间隙子507b

‑

1以及一第二高介电间隙子507b

‑

2,第一高介电间隙子507b

‑

1位于第一高气隙511b

‑

1与低位面导电图案403b之间,第二高介电间隙子507b

‑

2位于第二高气隙511b

‑

2与低位面导电图案403b之间。在一些实施例中,第一高介电间隙子507b

‑

1与第二高介电间隙子507b

‑

2大致以位于第一目标结构203a与第二目标结构203b之间的中间线ml

‑

1而对称设置。

[0220]

请参考图17,在一些实施例中,半导体元件结构还包括一第一矮气隙511a

‑

1以及一第一矮介电间隙子507a

‑

1,是位于第一高气隙511b

‑

1与高位面导电图案403a之间。在一

些实施例中,半导体元件结构包括第一矮气隙511a

‑

1与一第二矮气隙511a

‑

2,是位于高位面导电图案403a的两侧处。在一些实施例中,第一矮气隙511a

‑

1与第二矮气隙511a

‑

2大致以位于第一部分203a与第二部分203a2之间的中间线ml

‑

2而对称设置。在一些实施例中,半导体元件结构还包括一第二矮介电间隙子507a

‑

2,位于第二矮气隙511a

‑

2与高位面导电图案403a之间。

[0221]

请参考图17,在一些实施例中,第一高气隙511b

‑

1位于低位面导电图案403b与第二部分203a2之间,且第一矮气隙511a

‑

1位于高位面导电图案403a与第二部分203a2之间。在一些实施例中,在剖视图中,高气隙与低气隙具有间隙子轮廓。在一些实施例中,第一部分203a1与第二部分203a2大致以位于第一部分203a1与第二部分203a2之间的中间线ml

‑

2而对称设置。

[0222]

图18至图20以及图2为形成半导体元件结构200b的按序各中间阶段的剖视示意图。半导体元件结构200b类似于或相同于半导体元件结构200a,除了硬遮罩结构205a1、205a2、205b1、205b2并未形成在间隙子元件223a’、223b’、223c’、223d’与目标结构203a、203b之间之外。

[0223]

如图18所示,依据一些实施例,目标材料203设置在半导体基底201上,且硬遮罩柱207a与207b通过使用光刻胶图案209a与209b当作一遮罩的一蚀刻工艺而设置在目标材料203上。个别的步骤是示出在如图4所示的制备方法20中的步骤s21、s23、s25。在一些实施例中,相较于如图6所示的结构,图18的目标材料203并未被硬遮罩层205所覆盖。更特别地,依据一些实施例,硬遮罩层205并未形成在图18的结构中,且目标材料203并未通过开孔210而暴露。

[0224]

接着,如图19所示,依据一些实施例,移除光刻胶图案209a与209b,且间隙子材料213共形地沉积在硬遮罩柱207a、207b的上表面与侧壁表面上以及在目标材料213的上表面上,以便获得缩减的开孔220。

[0225]

如图20所示,依据一些实施例,蚀刻间隙子材料213以形成间隙子223a、223b、223c、223d在硬遮罩柱207a、207b的侧壁表面上。个别的步骤是示出在如图4所示的制备方法20中的步骤s27。在一些实施例中,相较于如图5所示的结构,图20之间隙子223a、223b、223c、223d直接接触目标材料203。

[0226]

接着,如图3所示,依据一些实施例,使用间隙子223a、223b、223c、223d当作一遮罩以蚀刻硬遮罩柱207a、207b与目标材料203,并稍微蚀刻间隙子223a、223b、223c、223d以形成间隙子元件223a’、223b’、223c’、223d’。个别的步骤是示出在如图4所示的制备方法20中的步骤s28。

[0227]

在一些实施例中,依据一些实施例,完全移除硬遮罩柱207a、207b,且通过蚀刻目标材料203以形成目标结构203a、203b在目标层203’上。如上所述,依据一些实施例,相较于半导体元件结构200a,半导体元件结构200b之间隙子元件223a’、223b’、223c’、223d’直接接触目标结构203a与203b。在一些实施例中,如图10到图17所示的制造流程可在图20之后执行,以形成如图17所示的高位面导电图案403a与低位面导电图案403b。

[0228]

图5为依据本公开一些实施例一种半导体元件结构300的制备方法30的流程示意图,其中,依据一些实施例,制备方法30具有步骤s31、s33、s35、s37、s39。结合图21至图25以详细阐述图5的步骤s31到s39,其是示出在形成半导体元件结构300中按序各中间阶段的剖

视示意图。

[0229]

如图21所示,提供半导体基底301,且一目标材料303设置在半导体基底301上。半导体基底301与目标材料303的详细内容可类似于或相同于半导体基底201与目标材料203的详细内容,且在文中不再重复描述。个别的步骤是示出在如图5所示的制备方法30中的步骤s31。

[0230]

仍请参考图21,依据一些实施例,多个能量可移除图案305设置在目标材料303上。个别的步骤是示出在如图5所示的制备方法30中的步骤s33。在一些实施例中,所述多个能量可移除图案305具有一热可分解材料。在一些其他实施例中,所述多个能量可移除图案305具有一光可分解材料、一电子束可分解材料或其他可应用的能量可分解材料。尤其是,在一些实施例中,所述多个能量可移除图案305具有一基础材料以及一可分解成孔剂材料,,而该可分解成孔剂材料是在暴露在一能量源(意即热源)时而被大致地移除。

[0231]

在一些实施例中,基础材料包含氢倍半硅氧烷(hydrogen silsesquioxane,hsq)、甲基硅酸盐(methylsilsesquioxane,msq)、多孔聚芳醚(porous polyarylether,pae)、多孔silk(porous silk)或多孔氧化硅(porous sio2),而可分解成孔剂材料包含一成孔剂有机化合物(porogen organic compound),其是可提供孔隙率给原本被在接下来的工艺的所述多个能量可移除图案305所占用的空间。

[0232]

在一些实施例中,所述多个能量可移除图案305通过一沉积工艺与一图案化工艺所形成。沉积工艺包括cvd、pvd、ald、旋转涂布或其他适合的工艺,而用于形成所述多个能量可移除图案305的图案化工艺可包括一光刻(photolithography)工艺以及一蚀刻工艺。光刻工艺可包括光刻胶涂布(例如旋转涂布)、软烘烤(soft baking)、遮罩对准(mask aligning)、曝光、曝光后烘烤(post

‑

exposure baking)、光刻胶显影、冲洗(rinsing)及干燥(drying)(例如:硬烘烤(hard baking))。蚀刻工艺可包括一干蚀刻工艺或一湿蚀刻工艺。

[0233]

在一些实施例中,目标材料203包含一热可分解材料、一光可分解材料、一电子束可分解材料或其他可应用的能量可分解材料。应当理解,依据一些实施例,目标材料203与所述多个能量可移除图案305包含相同材料或类似材料。

[0234]

如图22所示,依据一些实施例,在所述多个能量可移除图案305形成之后,一间隙子材料307共形地沉积在所述多个能量可移除图案305的上表面与侧壁表面上以及在目标材料303的上表面上。

[0235]

在一些实施例中,间隙子材料307由下列材料所制:氧化硅、碳化硅、氮化硅、氮氧化硅、其他适合的材料或其组合,而用于形成间隙子材料307的沉积工艺包括cvd、pvd、ald、旋转涂布或其他适合的工艺。在一些实施例中,间隙子材料307的材料不同于所述多个能量可移除图案305的材料。应当理解,所述多个能量可移除图案305的材料相对间隙子材料307的材料具有一高蚀刻选择性。

[0236]

接着,如图23所示,依据一些实施例,蚀刻间隙子材料307以形成间隙子307a、307b、307c、307d在所述多个能量可移除图案305的侧壁表面上。个别的步骤阐明在如图5所示的制备方法30的步骤s35中。在一些实施例中,蚀刻工艺为一非等向性蚀刻工艺,其是垂直地移除间隙子材料307在所有位置的相同数量,并余留下间隙子307a、307b、307c、307d在所述多个能量可移除图案305的侧壁表面上。在一些实施例中,蚀刻工艺为一干蚀刻工艺。

[0237]

如图24所示,依据一些实施例,间隙子307a、307b、307c、307d形成之后,形成一介电层309以围绕所述多个能量可移除图案305以及间隙子307a、307b、307c、307d。个别的步骤阐明在如图5所示的制备方法30的步骤s37中。

[0238]

在一些实施例中,介电层309包括下列材料:氧化硅、碳化硅、氮化硅、氮氧化硅、一或多个适合的介电材料或其组合。在一些实施例中,介电层309的材料不同于间隙子307a、307b、307c、307d的材料。应当理解,介电层309的材料相对于间隙子307a、307b、307c、307d的材料具有一高蚀刻选择性。

[0239]

在一些实施例中,介电层309包含一热可分解材料、一光可分解材料、一电子束可分解材料或其他可应用的能量可分解材料。应当理解,依据一些实施例,介电层309与所述多个能量可移除图案305包含相同材料或类似材料。

[0240]

在一些实施例中,介电层309通过一沉积工艺与一继续的平坦化工艺所形成。沉积工艺可为cvd、pvd、ald、旋转涂布或其他可应用的工艺,而平坦化工艺可为一化学机械研磨(cmp)工艺。

[0241]

接着,如图25所示,依据一些实施例,所述多个能量可移除图案305、介电层309与目标材料303使用间隙子307a、307b、307c、307d当作一遮罩进行蚀刻。个别的步骤阐明在如图5所示的制备方法30的步骤s39中。在一些实施例中,蚀刻工艺为一干蚀刻工艺。在一些实施例中,请参考图25,间隙子元件307a’与间隙子元件307b’大致以位于间隙子元件307a’与间隙子元件307b’之间的中间线ml而对称设置。

[0242]

在一些实施例中,请参考图25,在剖视图中,间隙子元件307a’与间隙子元件307b’分别在最高点tp1与最高点tp2具有一圆凸(rounding)上表面。在一些实施例中,请参考图25,间隙子元件307a’具有一内表面308i以及一外表面308o,在剖视图中,内表面308i面向中心线ml,外表面308o面向相对侧,内表面308i大致为一非弯曲(non

‑

curved)表面,外表面308o大致为一弯曲表面,内表面308i的曲率(curvature)小于外表面308o的曲率。

[0243]

在一些实施例中,请参考图25,目标结构303a具有一上表面304a,其是具有一第一上宽度,间隙子元件307a’具有下表面308b1,其是具有一第一下宽度,上表面304a接触下表面308b1,且第一上宽度大致相同于第一下宽度。在一些实施例中,请参考图25,目标结构203b具有一上表面304b,其是具有一第二上宽度,间隙子元件307b’具有下表面308b2,其是具有一第二下宽度,上表面304b接触下表面308b2,且第二上宽度大致相同于第二下宽度。

[0244]

在一些实施例中,请参考图25,所述多个开孔310具有相同的宽度w1,且目标结构303a、303b、303c、303d具有相同宽度w2。在一些实施例中,宽度w1被设计相同于宽度w2,例如相同空间与图案。在一些实施例中,半导体元件结构300具有一膜结构(图未示),位于半导体基底301上。在一些实施例中,目标结构303a、303b、303c、303d形成在膜结构上,当成是微图案,其是可被用来当作在接下来的制造流程中的一硬遮罩,而接下来的制造流程是用以图案化在膜结构中的对应微图案。在一些实施例中,在图20之后可执行如图10到图17所示的制造流程,以形成如图17所示的高位面导电图案403a以及低位面导电图案403b。

[0245]

在一些实施例中,依据一些实施例,可完全移除所述多个能量可移除图案305,且目标结构303a、303b、303c、303d可通过蚀刻穿过目标材料303而形成。此外,可稍微蚀刻间隙子307a、307b、307c、307d,以形成间隙子元件307a’、307b’、307c’、307d’。应当理解,在蚀刻期间,所述多个能量可移除图案305的材料相对于间隙子307a、307b、307c、307d的材料

(例如间隙子元件307a’、307b’、307c’、307d’的材料),具有一高蚀刻选择性。

[0246]

所述多个能量可移除图案305的材料相对于间隙子307a、307b、307c、307d的材料具有一第一蚀刻选择性,介电层309的材料相对于间隙子307a、307b、307c、307d的材料具有一第二蚀刻选择性,且目标材料303的材料间隙子307a、307b、307c、307d的材料具有一第三蚀刻选择性。在一些实施例中,第一蚀刻选择性、第二蚀刻选择性以及第三蚀刻选择性是相互类似。

[0247]

由于所述多个能量可移除图案305、介电层309以及目标材料303相对于间隙子307a、307b、307c、307d在用于形成间隙子元件307a’、307b’、307c’、307d’的蚀刻工艺中具有一高蚀刻选择性,所以蚀刻工艺可以一直进行到半导体基底301的上表面301t,同时避免间隙子元件307a’、307b’、307c’、307d’的塌陷。

[0248]

本公开的一实施例提供一种半导体元件结构。该半导体元件结构包括一基底;一第一目标结构,设置在该基底上,其中该第一目标结构包括一第一部分、一第二部分以及一第三部分,该第三部分连接到该第一部分与该第二部分,该第一部分的一高度与该第二部分的一高度大于该第三部分的一高度;一第二目标结构,设置在该第一目标结构上,其中该第二目标结构包括一第四部分、一第五部分以及一第六部分,该第六部分连接到该第四部分与该第五部分;一低位面导电图案,位于该第一目标结构与该第二目标结构之间;以及一高位面导电图案,位于该第一目标结构中。

[0249]

本公开的一实施例提供一种半导体元件结构的制备方法。该方法包括形成一硬遮罩材料在一基底上;蚀刻该硬遮罩材料以形成多个硬遮罩柱;形成多个间隙子在所述多个硬遮罩柱的侧壁表面上;蚀刻所述多个硬遮罩柱与该目标材料,其是通过所述多个间隙子当作一遮罩进行蚀刻,以一体成形多个目标结构、一高位面凹陷在其中一个目标结构中,以及一低位面凹陷在二目标结构之间;以及一体成形一高位面导电图案在该高位面凹陷中以及一低位面导电图案在该低位面凹陷中。

[0250]

提供有一半导体元件结构及其制备方法的一些实施例。该半导体元件的制备方法可包括底切一光刻胶图案在一半导体基底上,以及形成一内间隙子元件在该光刻胶图案的一侧壁表面上。该内间隙子元件具有延伸进入该光刻胶图案的一凹陷(例如该底切区)的一部分,以形成一基脚(footing),且该内间隙子元件的该部分的一宽度是随着该部分向该半导体基板的延伸而连续增加。因此,该内间隙子元件可避免在该光刻胶图案移除之后的塌陷。

[0251]

此外,该高位面导电图案与该低位面导电图案的下端是位于不同位面(level),且在该高位面导电图案与该低位面导电图案之间有多个气隙。因此,可有效地降低在该高位面导电图案与该低位面导电图案之间的寄生电容。也就是说,可通过在该高位面导电图案与该低位面导电图案之间延伸的距离,来显着减轻在该高位面导电图案与该低位面导电图案上感应或施加的电子信号之间的干扰效应(interference effect)。

[0252]

虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的构思与范围。例如,可用不同的方法实施上述的许多工艺,并且以其他工艺或其组合替代上述的许多工艺。

[0253]

再者,本公开的范围并不受限于说明书中所述的工艺、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的公开内容理解可根据本公

开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的工艺、机械、制造、物质组成物、手段、方法、或步骤。据此,这些工艺、机械、制造、物质组成物、手段、方法、或步骤是包含于本公开的权利要求内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1