集成电容元件与对应的生产方法与流程

集成电容元件与对应的生产方法

1.优先权要求

2.本技术要求于2020年3月16日提交的法国专利申请no.2002552的优先权,其内容在法律允许的最大程度上通过整体引用并入于此。

技术领域

3.实施例和实现方式涉及集成电路(特别是集成电容元件)和用于生产集成电路的方法。

背景技术:

4.在集成电路中,通常提供了电容元件,例如,以解耦电源电压。

5.常规地,关于这点由于低生产成本而提供了金属氧化物半导体(mos)型电容元件(除了为晶体管设想的步骤之外,没有专门用于生产的步骤)。实际上,常规mos电容元件具有常规cmos(“互补金属氧化物半导体”)晶体管平面栅极结构,其中导电栅极区域形成电容元件的一个电极,而半导体区域(衬底或阱)形成电容元件的另一个电极。

6.也就是说,常规mos电容元件的性能不是最佳的,特别是在高漏电流和相对较低的每单位表面积电容值方面。

7.此外,出于使用的灵活性以及由于反转模式可以在电容值的电压中具有优越的稳定性的原因,在累积模式和反转模式中设计兼容的mos电容元件是被期望的。

8.根据形成电容元件的半导体衬底或半导体阱的n或p型导电性,相对于电容元件的使用,极化半导体区域可以是有问题的。

9.例如,为了使p型阱具有非零正电势,设计规则在距其他p型阱安全距离处(通常在质量电势(mass potential)处)施加该阱的定位约束。实际上,根据通常使用术语“闩锁”所指的现象,这种类型的极化可以经由在电路阱的接口处形成的寄生双极元件引入传导路径。这个安全距离可以在6μm或12μm的量级上,该安全距离在集成电路的规模上非常庞大。

10.被期望的是,提供更紧凑的电容元件(即,具有更高的每单位表面积的电容值),具有很少的泄漏、与反转模式兼容并且受到很少或没有设计规则定位约束,并且进一步需要很少或没有专用于其产生的步骤。

技术实现要素:

11.就此而言,根据一方面,一种集成电路包括第一导电类型的第一掺杂半导体阱,被包含在半导体衬底中。第一阱包含第二掺杂半导体阱,第二掺杂半导体阱具有与第一导电类型相对的第二导电类型,第二掺杂半导体阱具有限定第一阱的内部区域的环形形状。集成电路还包括电容元件,电容元件包括第一电极和第二电极。第一电极包括至少一个竖直导电结构,竖直导电结构填充竖直延伸到第一阱中的沟槽,竖直导电结构由覆盖沟槽的基部和侧面的介电包封层与第一阱电隔离。竖直导电结构在沟槽的至少一个纵向端部穿透到第二阱中。第二电极包括所述第一阱和所述第二阱。

12.第二阱被用作在第一阱中少数载流子的源,以使能反转模式。

13.实际上,假设沟槽纵向穿透到第二阱中,则竖直导电结构形成适于在第一阱中引入导电沟道区域的pmos型器件,该pmos型器件衬套竖直导电结构的介电包封层的基部和侧部。

14.此外,给定第二阱被包含在第一阱中(即,第一阱包围第二阱),则第二阱通过pnp双结特别地与半导体衬底以及其他p型阱隔离,并且因此较少或不受“闩锁”现象的影响。

15.因此,根据该方面的集成电容元件能够实现不受到定位约束的反转模式,并且由于使用阱的深度形成在第一电极与第二电极之间的电容接口,因此每单位表面积具有高电容值。

16.根据实施例,第二阱具有环形形状,限定第一阱的内部区域和外部区域,并且所述至少一个竖直导电结构直接穿过第一阱的内部区域,在沟槽的两个纵向端部处穿透第二阱。

17.这特别地有利于以下方面:在反转模式中形成导电沟道区域,以及在反转中电容元件的电容值的电压稳定性。

18.根据实施例,第二阱被定位于包含接触件的区域内侧,其中第一电极的元件以及第二电极的元件分别电耦合。

19.因此,设想第二阱以特别地使能在反转模式下的操作并不实质上增加由电容元件的结构占据的表面积,进一步设想包含接触件的区域,用于电耦合第一电极的元件(特别是竖直导电区域),以及用于将第二电极的元件,特别是第一阱和第二阱的元件彼此耦合。

20.根据实施例,第二阱的基部通过第一导电类型的掺杂半导体厚度与半导体衬底竖直分隔。

21.实际上,可以设想在小于第一阱的深度处形成第二阱,但是例如,由于生产步骤的汇集的原因,以及可选的掺杂剂扩散控制,可以优选地在衬底中附加地植入深埋半导体层,形成竖直分隔第二阱的基部与衬底的半导体厚度。

22.根据实施例,第二种导电性是“p”正型。

23.根据实施例,第一种导电性是“p”正型。

24.根据实施例,半导体衬底是“p”正型掺杂的。

25.根据实施例,竖直导电结构、介电包封层、第一阱和第二阱被相互布置以分别形成金属氧化物半导体“mos”型晶体管的栅极区域、mos晶体管的介电栅极区域,mos晶体管的半导体本体和mos晶体管的至少一个导电端子。

26.根据实施例,第一电极还包括第一水平导电结构,其位于第一介电层上,第一介电层覆盖第一阱并且覆盖所述至少一个竖直导电结构,以便将第一水平导电结构与第一阱和所述至少一个竖直导电结构电隔离。

27.该实施例使得针对在衬底上相同的占用表面积,能够在第一电极与第二电极之间添加额外的电容接口。这使得能够增加电容元件的每单位表面积的电容值。

28.并且,例如,第二电极还可以包括位于覆盖第一水平导电结构的第二介电层上的第二水平导电结构,以便将第二水平导电结构与第一水平导电结构电隔离。

29.这里再次,针对在衬底上未改变的占用表面积,在第一电极与第二电极之间添加额外的电容接口,以便进一步增加电容元件每单位表面积的电容值。

30.根据实施例,集成电路还包括逻辑部分,被配置成以非零正逻辑电平电源电压供电,并且电容元件被配置成以反转模式极化,具有在第一电极上的第一电压,例如地接地参考电压,以及在第二电极上的第二电压(例如,在第二电极上的逻辑电平电源电压),第二电压大于或等于第一电压、并且小于或等于逻辑电平电源电压。

31.换句话说,在第二电极上引入反转模式的高电平电压由逻辑电平限制,以便严格防止“闩锁”寄生双极效应。因此,高度宽容性的定位约束被获得(即,小的、甚至最小的安全距离),并且这在集成电路的设计的尺寸和灵活性方面是有利的。

32.根据另一方面,一种用于生产集成电路的方法,包括生产具有第一电极和第二电极的电容元件,包括:形成被包含在半导体衬底中的第一导电类型的第一掺杂半导体阱;形成与第一导电类型相对的第二导电类型的第二掺杂半导体阱,第二掺杂半导体阱被包含在第一阱中,并且具有限定第一阱的内部区域的环形形状;形成至少一个竖直导电结构,包括:分别形成至少一个沟槽、介电包封层以及竖直导电结构,至少一个沟槽竖直延伸至第一阱中并且在至少一个纵向端部处穿透至所述第二阱中,介电包封层覆盖所述至少一个沟槽的基部和侧面,竖直导电结构填充至少一个沟槽,并且通过介电包封层与第一阱电隔离;电耦合第一电极,包括在竖直导电结构上形成接触件;以及电耦合第二电极,包括在第一阱和第二阱上形成接触件。

33.根据实现方式,方法还包括:形成具有环形形状的第二阱,环形形状限定了第一阱的内部区域和外部区域,以及形成至少一个竖直导电结构,竖直导电结构直接穿过所述第一阱的内部区域,并且在沟槽的两个纵向端部处穿透到第二阱中。

34.根据实现方式,第二阱被定位于包含接触件的区域内,在该区域上分别形成电耦合的第一电极以及第二电极的元件。

35.根据实现方式,形成被包含在第一阱中的第二阱包括形成将第二阱与半导体衬底竖直分隔的第一导电类型的掺杂半导体厚度。

36.根据实现方式,第二导电性是“p”正型。

37.根据备选的实现方式,第一导电性是“p”正型。

38.根据实现方式,半导体衬底是“p”正型掺杂的。

39.根据实现方式,竖直导电结构、介电包封层、第一阱和第二阱的形成被相互布置以分别形成金属氧化物半导体“mos”型晶体管的栅极区域、mos晶体管的介电栅极区域,mos晶体管的半导体本体和mos晶体管的至少一个导电端子。

40.根据实现方式,方法还包括:形成第一介电层,覆盖第一阱并且覆盖至少一个竖直导电结构;形成第一水平导电结构,位于第一介电层上并且通过第一介电层与第一阱和至少一个竖直导电结构电隔离;其中,电耦合第一电极还包括在第一水平导电结构上形成接触件。

41.根据实现方式,方法还包括:形成覆盖第一水平导电结构的第二介电层;形成位于第二介电层上并且通过第二介电层与第一水平导电结构电隔离的第二水平导电结构;其中,电耦合第二电极还包括在第二水平导电结构上形成接触件。

42.根据实现方式,方法还包括:在半导体衬底中产生逻辑部分,逻辑部分具有的电源处于非零正逻辑电平电源电压,其中电容元件以反转模式极化,在第一电极的接触件上具有第一电压,并且在第二电极的接触件上具有大于第一电压并且小于或等于逻辑电平电源

电压的第二电压。

43.根据实现方式,方法还包括在半导体衬底中产生高电压部分和非易失性存储器,其中:形成第一阱与在高电压部分中形成第一导电类型的掺杂半导体阱同时进行;形成第二半导体阱与在高电压部分中形成第二导电类型的掺杂半导体阱同时进行;以及形成至少一个竖直导电结构与在非易失性存储器中形成竖直栅极掩埋晶体管同时进行。

44.根据实现方式,在非易失性存储器中形成所述竖直栅极掩埋晶体管的源极区域的同时,形成将第二阱与半导体衬底竖直分隔的第一导电类型的掺杂半导体厚度,包括在衬底深处形成第一导电类型的掺杂掩埋半导体区域。

45.根据实现方式:形成第一介电层与形成覆盖半导体衬底的表面的非易失性存储器中的浮动栅极状态晶体管的隧道介电层同时进行;形成第一水平导电结构与形成位于非易失性存储器中的隧道介电层上的状态晶体管的浮动栅极同时进行。

46.根据实现方式:形成第二介电层与形成覆盖半导体衬底的表面的非易失性存储器中的浮动栅极状态晶体管的栅极介电层同时进行;形成第二水平导电结构与形成位于非易失性存储器中的栅极介电层上的状态晶体管的控制栅极同时进行。

附图说明

47.本发明的其他优点和特征将在研究决不是限制性的实施例和实现方式的详细描述及附图的详细描述时显现,其中:

48.图1表示了集成电路电容元件的俯视图;

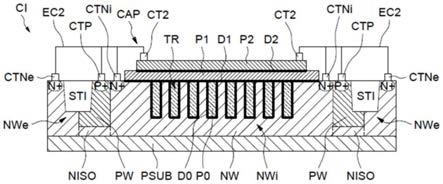

49.图2和图3是图1电容元件的截面图;

50.图4表示了集成电路应用的架构的示意性示例;

51.图5是存储器单元的截面图;

52.图6示意性地在左侧图示了用于产生参考图1至4的上述电容元件cap以及在右侧图示了产生参考图5的上述存储器单元cel的方法的步骤。

具体实施方式

53.图1表示了集成电路ci的电容元件cap的俯视图,图2表示了在图1中平面ii

‑

ii中电容元件cap的截面图,图3表示了图1中平面iii

‑

iii中电容元件cap的截面图。

54.在图1、图2和图3中的视图中表示的相同元件具有相同的附图标记,现在将对图1、图2和图3进行联合而笼统的描述。

55.集成电路ci由掺杂半导体衬底psub(例如硅)制成,该衬底具有导电类型(例如p型)。

56.例如通过常规掺杂剂植入,在衬底psub中产生第一导电类型(例如n型)的第一掺杂半导体阱nw。

57.在第一阱nw中形成与第一导电类型相对的第二导电类型(例如p型)的第二掺杂阱pw,从而被包含在第一阱nw中。这意味着第二阱pw由第一阱nw包围,从而通过pnp双结与第二导电类型的其他半导体区域(例如衬底psub)电隔离。

58.为了简洁起见,第一种导电性在下文中被称为n型,第二种导电性被称为p型。

59.也就是说,通过非限制性示例的方式,下文所述的电容元件cap可以完美地由具有

与本文所述电导性相对的电导性的半导体阱产生。

60.因此,第一导电类型可以是“p”正型,而第二导电类型可以是“n”负型。

61.尽管通常几乎总是p型,但衬底psub的导电性类型可以可选地是n型。

62.在该示例中,如图1俯视图所示,根据方形环形形状生产第二阱pw。因此,环形形状定义了第一阱nw的内部区域nwi和第一阱nw的外部区域nwe。显然,第一阱nwi、nwe区域的内部和外部定向由环形形状的向内径向和向外径向分别确定。

63.第二阱pw的半导体区域不接合衬底psub。实际上,第二阱pw的侧面面对第一阱的外部区域nwe,而第二阱pw的基部通过n型掺杂半导体厚度niso与半导体衬底psub竖直分隔。

64.半导体厚度niso使得能够将第二阱pw与衬底psub电隔离。实际上,如下文所示,第二阱pw将以与衬底psub不同的电压极化。

65.在第二阱为n型并且衬底为p型的情况下,与第二阱的导电类型相对的导电类型的半导体层niso是可选的。

66.例如,形成第二阱pw的p型掺杂剂的植入被配置成使得掺杂剂不在深度上扩散到衬底psub中。

67.也就是说,出于掺杂剂扩散控制和生产方法步骤的汇集的原因,优选的是进行掩埋半导体层niso的额外植入(即,位于衬底的深度),以形成竖直分隔第二阱pw的基部与衬底psub的所述半导体厚度niso。

68.电容元件cap是mos“金属氧化物半导体”类型,给定它包括第一电极ec1和第二电极ec2,第一电极ec1包括导电结构p0,并且第二电极ec2特别地包括第一半导体阱nw。

69.第一电极ec1和第二电极ec2由形成电容接口的介电材料d0电分隔。

70.第一电极ec1实际上包括至少一个竖直导电结构p0,至少一个导电结构填充竖直延伸到第一阱nw中的沟槽tr。“填充沟槽”通常表示沟槽的内部体积不包括竖直导电结构以外的材料。

71.尽管如此,沟槽tr的基部和侧面仍覆盖有介电包封层d0,从而电隔离填充沟槽tr内部体积的竖直导电结构p0与第一阱nw。

72.根据掩模的图案通过干蚀刻形成沟槽tr,并且该蚀刻的图案被配置成使得沟槽tr的至少一个纵向端部ex1、ex2从第一阱的内部区域nwi穿透到第二阱pw中。

73.在该示例中,沟槽tr和因此所述至少一个竖直导电结构p0直接穿过第一阱的内部区域nwi,并且在沟槽tr的两个纵向端部ex1、ex2处穿透第二阱pw。

74.显然,竖直导电结构p0、d0的数目越多,在第一电极ec1与第二电极ec2之间的电容性接口的表面积越大(即,特别是第一阱nw),并且每单位表面积的电容值越大。实际上,竖直导电结构p0的电容性接口的大部分表面积竖直延伸到nw阱的深度中,而很少地延伸到nw阱的表面。

75.在所有沟槽的竖直导电结构p0上产生第一电极ec1的接触件ct0,以使它们特别地彼此电耦合(未示出)。由此形成的第一电极ec1包括所有竖直导电结构p0。

76.例如,在竖直导电结构p0的两个纵向端部ex1、ex2、第二阱pw的环的层级和第一阱nw的内部区域nwi的边缘的层级上产生接触件ct0。

77.第二电极ec2的接触件ctni在第一阱nw的内部区域nwi上产生,并且接触件ctne在

第一阱的外部区域nwe上产生。此外,在第二阱pw上产生第二电极ec2的接触件ctp。

78.由此形成的第二电极ec2包括第一阱nw(内部区域nwi和外部区域nwe)和第二阱pw。

79.第二阱pw将用作在第一阱nw中的少数载流子的源,以实现电容元件cap的反转模式。

80.实际上,给定沟槽tr纵向穿透到第二阱pw中,竖直导电结构p0和介电包封层d0形成与pmos型晶体管类似的结构tpm。

81.因此,相对于第一电极ec1正极化第二电极ec2在第一n型阱nw中引入p型导电隧道区域,该p型导电沟道区域衬套沟槽tr的介电包封层d0的基部和侧面。

82.在n型阱nw中的反转模式特别地有利于相对于在电容元件cap的端子ec1、ec2处的电压的电容值的稳定性,尤其是相对于在p型阱中类似结构的mos型电容元件的累积模式。

83.此外,给定p型第二阱pw特别地通过利用第一阱nw形成的pnp双结与p型半导体衬底psub以及任何其他p型阱隔离,电容元件cap被保护以防止寄生双极元件泄漏(“闩锁”)现象。

84.将第一阱nw带到正电势通常不会引入特定的定位约束。

85.因此,在反转模式中,电容元件cap受到很少或没有定位约束,并且更由于使用阱nw的深度来形成在第一电极ec1与第二电极ec2之间的电容接口,因此每单位表面积具有高电容值。

86.此外,电容元件cap有利地包括两个额外的水平电容接口,水平电容接口通过水平导电结构p1、p2获得,类似于平面晶体管双栅极结构,堆叠在第一阱nw和填充有竖直导电结构p0的沟槽tr的顶部。

87.因此,第一电极ec1有利地进一步包括位于第一介电层d1上的第一水平导电结构p1。水平导电结构p1和第一介电层d1覆盖第一阱nw,并且覆盖所述至少一个竖直导电结构p0。因此,水平导电结构p1与第一阱nw电隔离,形成与属于第二电极ec2的第一阱nw的附加电容接口。第一介电层d1将第一水平导电结构p1与沟槽tr的竖直导电结构p0电隔离,也就是说,第一水平导电结构p1和竖直导电结构p0属于第一电极ec1,在这点上,第一水平导电结构p1和竖直导电结构p0属于第一电极ec1通过在第一水平导电结构p1上的接触件ct1以及与竖直导电结构p0耦合的接触件ct0彼此电耦合。

88.此外,第二电极ec2有利地包括位于第二介电层d2上的第二水平导电结构p2,第二介电层d2覆盖大部分第一水平导电结构p1。因此,第二水平导电结构p2与第一水平导电结构p1电隔离并且在第一电极ec1与二电极ec2之间形成附加电容接口。第二电极ec2在接触件ct2上与第二水平导电结构p2电耦合,接触件ct2与在第一阱nw上的接触件ctni、ctne以及在第二pw上的接触件ctp耦合。

89.因此,针对在衬底psub(即在阱nw的表面)上的相同占用表面积,在第一电极ec1与第二电极ec2之间添加了两个额外电容接口。这使得电容元件cap的每单位表面积的电容值能够增加。

90.实际上,如下文参考图6所示,产生第一导电结构p1和第二导电结构p2的步骤可以有利地汇集在产生非易失性存储器的步骤中,并且因此是无需额外付出(free)的。

91.而且,设想电容元件cap的外围区域产生接触件ctne、ctni、ctp、ct2以电耦合第二

电极ec2的元件nwe、nwi、pw、p2,并且产生第一电极ec1的元件p0、p1的接触件ct0、ct1。

92.并且,第二阱pw的环形形状是有利的实施例示例,使得特别地能够将由第二阱pw占据的表面区域定位在针对包含所述接触件的实施例的外围区域所设想的表面区域内。可选地,第二阱可以被定位成与设想用于包含接触件的外围区域的表面区域的至少一部分相交。

93.而且,即使在没有设想水平导电结构p1、d1、p2、d2的情况下,也应设想外围区域包含接触件ct0、ctni、ctne、ctp,使得尤其能够将电容元件cap的第一电极ec1和第二电极ec2与例如外部端子电耦合。

94.第二阱pw的进一步的形状显然可以设想为将第二阱pw至少部分定位在针对包含接触件的区域设想的表面区域内,特别地根据为所述接触件选择的位置。

95.因此,第二阱pw在衬底psub上引入很少或不引入专用于其产生的额外表面积。

96.现在参考图4。

97.图4表示集成电路ci的应用的架构的示意性示例,其中集成电路进一步包括电容元件cap、在同一衬底psub中和其上的逻辑部件lg,电源级alm和高电压部分hv,包括非易失性存储器mem和高电压信号发生器hvgen。例如,高电压信号为10至15伏量级。

98.受益于在衬底psub上的非限制性定位规则,电容元件cap被布置成填充在集成电路ci的其他元件lg、hvgen、mem、alm之间可用的剩余表面积。因此,尽管由电容元件cap占据了表面积,但是集成电路ci相对紧凑。

99.逻辑部分lg被配置为以非零正逻辑电平电源电压vdd供电,并且电容元件cap被用作在逻辑电平电压vdd与接地参考电压gnd之间的解耦电容器。

100.电容元件cap有利地以反转模式极化(即,利用在第一电极ec1上的接地参考电压gnd和在第二电极ec2上的逻辑电平电源电压vdd)。

101.图5表示属于上述参考图4的集成电路ci的非易失性存储器mem的存储器单元cel的有利示例。

102.存储器单元cel形成在包含在衬底psub中的p型掺杂阱hvpw中以及其上。在阱hvpw下,n型掺杂掩埋半导体区sl位于衬底psub的深度处。掩埋半导体区sl形成用作源极线的源极平面。n型掺杂半导体区hvnw从阱hvpw的顶面延伸到掩埋半导体区sl,形成适于经由所述顶面极化源极线sl的接触阱。

103.存储器单元cel包括与状态晶体管te串联的存取晶体管ta。存取晶体管ta是竖直栅极掩埋晶体管,并且具有填充沟槽trta的导电栅极gv,沟槽trta的基部和侧部由包围竖直导电栅极gv的竖直栅极介电层dgv覆盖。存取晶体管ta的源极区域由源极平面sl具体化,并且可选地,n型半导体区域被植入或扩散在沟槽trta的基部中。

104.状态晶体管te就其本身而言是浮动栅级晶体管,包括浮动栅级fg,通过所谓的“隧道”介电层dtn与阱hvpw电隔离,以及控制栅极cg通过所谓的控制栅极介电层dcg与浮动栅级电隔离。

105.现在参考图6。

106.一方面,图6在左侧示意性地示出了用于产生上述图1至图4所示的电容元件cap的方法的步骤;另一方面,图6在右侧示意性地示出了产生上述图5所示的存储器单元cel的步骤。

107.电容元件cap的第一阱nw的形成步骤601可以有利地与高电压部分hv中的n型掺杂半导体阱hvnw的形成步骤1601(例如存储器mem的接触阱)同时进行。

108.步骤601、1601包括,例如通过在衬底psub顶面上形成的掩模的图案、并且以能够在10到15伏量级的电压操作的浓度共同植入n型掺杂剂。

109.电容元件cap的第二阱pw的形成步骤602可以有利地与在高电压部分hv中,特别是在存储器mem中的p型掺杂半导体阱hvpw的形成步骤1602同时进行。

110.步骤602、1602包括,例如通过在衬底psub顶面上形成的掩模的图案、并且以能够在10到15伏量级的电压操作的浓度共同植入p型掺杂剂。

111.针对电容元件cap,将第二阱pw与半导体衬底psub竖直分隔的n型掺杂半导体厚度niso的形成步骤603可以有利地与存储器mem的源极平面sl的形成步骤1603同时进行。

112.步骤603、1603包括,例如在包括电容元件cap的衬底psub的整个区域以及包括存储器mem的衬底psub的整个区域中共同植入n型掺杂剂。植入603、1603被配置在导致在衬底psub中的扩散受限的能量处,以便将掩埋半导体区域定位在衬底psub的深度。

113.例如,在植入601

‑

1601、602

‑

1602和可选的603

‑

1603之后,针对电容元件cap和高压部分hv可以同时设想的是,形成常规的横向浅沟槽隔离区sti(参见图2至图3和图5)。

114.电容元件cap的沟槽tr的形成步骤604可有利地与存储器mem的存取晶体管ta的沟槽trta的形成步骤1604同时进行。

115.步骤604、1604包括例如共同干蚀刻,例如通过共同光刻掩模使用反应性离子蚀刻(rie)技术。

116.竖直导电结构p0的形成步骤605,将竖直导电结构p0封装在电容元件cap的所述沟槽tr中的介电包封层d0中,可以有利地与存储器mem的存取晶体管ta的竖直栅极区域gv和竖直栅极介电层dgv的形成步骤1605同时进行。

117.步骤605、1605首先包括在公共步骤604、1604中蚀刻的沟槽tr、trta的侧面和基部上的氧化硅层的热生长;其次,用相同的导电材料p0、gv例如通过化学气相沉积(cvd)形成的原位掺杂多晶硅来过量填充,然后进行化学机械平坦化(cmp),例如,到可选的先前沉积的停止层为止,或至阱nw、hvpw的顶表面为止。

118.位于电容元件cap的第一介电层d1上的第一水平导电结构p1的形成步骤606可以有利地与位于存储器mem的状态晶体管te的隧道介电层dtn上的浮动栅极fg的形成步骤1606同时进行。

119.步骤606、1606包括,例如首先在阱nw、hvpw的顶表面上共同生长氧化硅层,在由此生长的隧道介电层dtn中选择性地部分蚀刻隧道窗口;其次,共同cvd沉积导电多晶硅,接着是可选地共同cmp抛光;并且第三,通过光刻掩模的干蚀刻来限定相应的导电区域。

120.位于电容元件cap的第一介电层d2上的第二水平导电结构p2的形成步骤607可以有利地与位于存储器mem的状态晶体管te的控制栅极介电层dcg上的控制栅极cg的形成步骤1607同时进行。

121.步骤607、1607包括,例如首先在第一水平导电结构p1以及浮动栅极fg上共同形成硅“ono”氧化物、氮化物和氧化物层的重叠层;其次,共同cvd沉积导电多晶硅,然后进行可选的共同cmp抛光;以及第三,通过光刻掩模的干蚀刻来限定相应的导电区域。

122.所有接触件ct的形成步骤608(即,第二电极ec2的接触件ctni、ctne、ctp、ct2,以

及电容元件cap的第一电极ec1的接触件ct0、ct1)可以有利地与接触件区域形成步骤1608同时进行,特别是在存储器mem中,但也可以设想通常用于集成电路ci的其他元件。

123.步骤608、1608包括例如,在将高浓度p型掺杂剂(p+)植入p型阱的表面并且将高浓度n型掺杂剂(n+)植入n型阱的表面之后,用于减少对高掺杂区域p+、n+的接入电阻的硅化步骤sal,最后,在硅化表面形成接触件,通常由钨制成。

124.硅化步骤通常包括暴露的硅表面的硅化反应sal,特别是高掺杂硅和多晶硅表面与金属材料的硅化反应。

125.因此,用于产生集成电容元件cap的方法的所有步骤601

‑

608可与步骤1601

‑

1608同时执行,进一步设想产生集成电路的高压部分hv,具体包括如参考图5所述的非易失性存储器mem。

126.因此,生产电容元件cap的方法可以完全无需额外付出。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1