半导体装置的制造方法与流程

1.本发明实施例涉及一种半导体装置的制造方法,特别涉及一种具有测试垫的半导体装置。

背景技术:

2.半导体装置用于各式各样的电子应用中,例如个人电脑、手机、数码相机与其他电子装置。半导体装置的制造一般是通过于半导体基板上依序沉积绝缘或介电层、导电层以及半导体层的材料,并使用微影图案化各种材料层以于其上形成电路组件与元件。

3.半导体工业通过不断减小最小部件尺寸来持续提高各种电子元件(例如,晶体管、二极管、电阻器、电容器等)的整合密度,允许了将更多的元件整合至给定区域中。再者,随着更多元件被整合至给定区域中,可采用复杂的三维(three

‑

dimensional,3d)整合电路(three

‑

dimensional integrated circuit,3dic)封装技术,以进一步提高整合密度,使得更复杂的系统也可被整合至3dic装置中。然而,随着最小部件尺寸减小、以及随着更复杂的系统被整合至3dic装置中,出现了额外的问题需要被解决。

技术实现要素:

4.本发明实施例提供一种半导体装置的制造方法,包括:沉积介电层于基板上;蚀刻多个开口于介电层中;及沉积导电材料于所述开口中,以形成测试垫的第一栅格部件(grid feature)及面板区,第一栅格部件从面板区纵向延伸至测试垫的周边,第一栅格部件于面板区具有第一宽度,第一宽度小于面板区在第一栅格部件的宽度。

5.本发明实施例提供一种半导体装置的制造方法,包括:蚀刻多个开口于基板上方的介电层中;沉积导电材料于所述开口中;及用介电层平坦化导电材料,以形成测试垫,测试垫包括框、位于框内的栅格区、以及位于栅格区的内部的探针区,栅格区包括被介电层的多个部分隔开的多个导电栅格部件。

6.本发明实施例提供一种半导体装置,包括:介电材料;第一测试垫,位于介电材料内,第一测试垫,包括:外框;栅格区,从外框向内延伸,栅格区包括多个导电栅格构件(grid member),所述导电栅格构件通过介电材料彼此分开;及面板区,位于栅格区的内部,其中所述导电栅格构件的第一个将面板区连接至外框,且其中所述导电栅格构件的第一个具有第一厚度,且面板区具有第二厚度,第一厚度小于第二厚度。

附图说明

7.本公开的各面向从以下详细描述中配合附图可最好地被理解。应强调的是,依据业界的标准做法,各种部件并未按照比例绘制且仅用于说明的目的。事实上,为了清楚讨论,各种部件的尺寸可任意放大或缩小。

8.图1a绘示出在制造半导体晶粒的中间步骤中于半导体晶圆内形成测试垫的剖面图。

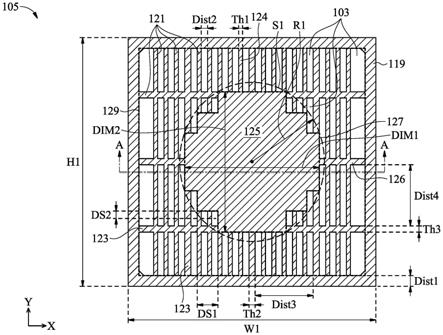

9.图1b是根据一些实施例,绘示出图1a的测试垫的平面图。

10.图2绘示出在制造半导体晶粒的中间步骤中于半导体晶圆的不同金属化层内形成测试垫的剖面图。

11.图3是根据一实施例,绘示出另一测试垫的平面图。

12.图4是根据一些实施例,绘示出测试数据。

13.其中,附图标记说明如下:

14.100:半导体晶圆

15.101:半导体基板

16.103:介电层

17.105:第一测试垫

18.107:第一内连线层

19.108:装置元件

20.109:装置区

21.111:划线区

22.113:阻障层

23.115:导电材料

24.119:框架

25.121:栅格部件

26.123:直线的第二系列

27.124:直线的第一系列

28.125:第一面板区

29.126:直线的第三系列

30.127:第一粗虚线

31.129:第二粗虚线

32.201:第一蚀刻停止层

33.203:第二内连线层

34.205:第二测试垫

35.207:第二蚀刻停止层

36.209:第三内连线层

37.211:第三测试垫

38.213:第三蚀刻停止层

39.215:第四内连线层

40.217:第四测试垫

41.219:第四蚀刻停止层

42.221:第五内连线层

43.223:第五测试垫

44.225:第五蚀刻停止层

45.227:第六内连线层

46.229:第六测试垫

47.231:第六蚀刻停止层

48.233:第七内连线层

49.235:第七测试垫

50.237:第七蚀刻停止层

51.239:第八内连线层

52.241:第八测试垫

53.243:第八蚀刻停止层

54.245:第九内连线层

55.247:第九测试垫

56.249:第九蚀刻停止层

57.251:钝化层

58.305:第二测试垫

59.325:第二面板区

60.327:第三粗虚线

61.m0:底部金属化层

62.m1:第一金属化层

63.m2:第二金属化层

64.m3:第三金属化层

65.m4:第四金属化层

66.m5:第五金属化层

67.m6:第六金属化层

68.m7:第七金属化层

69.m8:第八金属化层

70.d1:第一深度

71.d2:第二深度

72.d3:第三深度

73.d4:第四深度

74.d5:第五深度

75.d6:第六深度

76.d7:第七深度

77.d8:第八深度

78.d9:第九深度

79.w1:第一宽度

80.h1:第一高度

81.th1:第一厚度

82.th2:第二厚度

83.th3:第三厚度

84.p1:第一节距

85.p2:第二节距

86.p3:第二节距

87.s1:圆

88.s2:第二形状

89.r1:第一半径

90.ds1:第一锯齿距离

91.ds2:第二锯齿距离

92.dim1:第一尺寸

93.dim2:第二尺寸

94.dim3:第三尺寸

95.dim4:第四尺寸

96.dist1:第一距离

97.dist2:第二距离

98.dist3:第三距离

99.dist4:第四距离

100.aa:线

具体实施方式

101.以下内容提供了许多不同的实施例或范例,以实施本发明实施例的不同部件。以下描述组件及配置方式的具体范例,以简化本发明实施例。当然,这些仅仅是范例,而非意图限制本发明实施例。举例而言,在以下描述中提及于第二部件上方或其上形成第一部件,其可包含第一部件及第二部件以直接接触件的方式形成的实施例,并且可包含在第一部件及第二部件之间形成额外的部件,使得第一部件及第二部件可不直接接触件的实施例。此外,本发明实施例可在各种范例中重复参见数值及/或字母。如此重复是为了简化及清楚的目的,其本身并非用于指定所讨论的各种实施例及/或配置之间的关系。

102.再者,此处可能使用空间相对用语,例如“在

……

之下”、“在

……

下方”、“下方的”、“在

……

上方”、“上方的”等类似的用语,以便描述图式中一部件或部件与另一(些)部件或部件之间的关系。空间相对用语除了包含图示绘示的方位外,也意图包含使用中或操作中的装置的不同方位。当装置被旋转至不同方位时(旋转90度或其他方位),此处所使用的空间相对描述也将同样地依旋转后的方位来解释。

103.随着整合至3dic装置中的系统的复杂性提高,在3dic装置的制造过程中,验证穿过金属化层的正确电性连接、以及识别已知良好的晶粒的重要性日益增加。因此,可将测试垫(例如,晶圆接受度测试(wafer acceptance test,wat)垫、隆起(bumping)垫等)结合到装置的不同金属化层中,以帮助位于3d封装及/或3dic装置内的部件的验证测试。可将测试垫形成于重分布层(redistribution layer)中或基板上,以允许3d封装或3dic的测试、允使探针及/或探针卡(probe cards)等的使用。可于中间结构以及最终结构上进行验证测试。此外,本文公开的结构及方法可与包含已知良好晶粒的中间验证的测试方法结合使用,以增加产率并降低成本。

104.图1a绘示出在制造半导体晶粒的中间步骤中半导体晶圆100的剖面图。具体而言,图1a是根据一些实施例,绘示出于半导体晶圆100的第一内连线层107中形成第一测试垫

105。装置元件108形成于半导体晶圆100的装置区109中的半导体基板101中及/或上方。第一内连线层107形成于装置元件108及半导体基板101上方,并且在本文中也可将第一内连线层107称作底部金属化层m0。根据一些实施例,第一测试垫105形成于第一内连线层107中并且可位于例如半导体晶圆100的划线区111内。

105.然而,在其他实施例中,第一测试垫105可位于其他合适的区域中,例如位于半导体晶圆100的装置区109内。举例而言,第一测试垫105可位于半导体晶粒的测试区内,上述半导体晶粒的测试区位于半导体晶粒的接触垫以及密封环(seal ring)之间。可使用任何合适的位置。

106.第一测试垫105经由第一内连线层107电性耦合至一或多个装置元件108,并允许在半导体晶圆100的制造期间对一或多个装置元件108进行原位测试。举例而言,可将第一测试垫105用于促进晶圆接受度测试(wafer acceptance testing,wat)及/或电路探针(circuit probe,cp)测试以进行制程控制监视(process control monitoring,pcm)。可进行wat以分析晶圆制造制程在制造的各个阶段的成功,并尝试确定任何制造缺陷的原因。电路探针(circuit probe,cp)测试涉及使用一或多个探针来确定哪个晶粒良好及哪些晶粒不良好。

107.在一实施例中,半导体基板101可包括掺杂或未掺杂的块状硅、或者绝缘体上覆硅(silicon

‑

on

‑

insulator,soi)基板的主动层。一般而言,soi基板包括例如下列的半导体材料层:硅(silicon)、锗(germanium)、硅锗(silicon germanium)、soi、绝缘体上覆硅锗(silicon germanium on insulator,sgoi)、或其组合。可使用的其他基板包括多层基板、梯度基板、或混合方位(hybrid orientation)基板。

108.如本领域具有通常知识者认识的是,可形成包括例如下列的主动装置及被动装置的各种装置:晶体管、二极管、电容器、电阻器、其组合等,以提供半导体晶圆100所期望的结构及功能性要求的设计。可使用包括例如下列的各种制程于半导体基板101中及/或上方形成装置元件108:沉积、蚀刻、布植、光学微影、退火、及/或其他合适的制程。

109.第一内连线层107包括形成于装置元件108及半导体基板101上方的一或多个介电层103,以隔离并保护装置元件108。在一些实施例中,介电层103中的至少一个是由低k介电材料所形成,上述低k介电材料具有k值例如低于约4.0。在一些实施例中,介电层103可由例下列的材料所形成:硼磷硅酸盐玻璃(boron phosphorous silicate glass,bpsg)、碳掺杂氧化物、氧化硅、多孔碳掺杂二氧化硅、氧化硅、氮化硅、sicoh、聚合物、其组合等,上述聚合物例如聚酰亚胺,并且可通过例如下列制程来沉积介电层103:化学气相沉积(chemical vapor deposition,cvd)、物理气相沉积(physical vapor deposition,pvd)、其组合等。可经由例如下列的制程来形成介电层103:旋涂制程、化学气相沉积(chemical vapor deposition,cvd)、pecvd、lpcvd、物理气相沉积(physical vapor deposition,pvd)、其组合等。一或多个介电层103可形成为具有约至约之间的厚度,例如约之间的厚度,例如约然而,可使用任何合适的材料、任何合适的制程、以及任何合适的厚度。

110.图1a是根据一些实施例,进一步绘示出第一测试垫105可形成于第一内连线层107中,并且例如位于半导体晶圆100的划线区111内。第一测试垫105通过一或多个导电部件经由第一内连线层107电性耦合至一或多个装置元件108。第一测试垫105允许在于第一内连

线层107上方形成后续的金属化层之前,在制造半导体晶圆100的中间步骤中,对所需的整合电路进行原位测试。如此,可例如于底部金属化层m0进行wat及/或cp测试,以分析晶圆制造制程的成功,并确定哪些晶粒是良好的及哪些晶粒是不良好的。

111.根据一些实施例,使用双镶嵌制程形成第一测试垫105,以在一开始于第一内连线层107的一或多个介电层103中形成开口。在一实施例中,可通过于第一内连线层107的最顶介电层上方设置并图案化光阻材料来形成开口。一旦设置并图案化光阻材料,可使用干式蚀刻制程将图案从光阻转移至下方的介电层103中,以形成于第一内连线层107中达第一深度d1的开口,上述干式蚀刻制程例如反应性离子蚀刻。根据一些实施例,第一深度d1介于约20nm至约150nm之间,例如约25nm。然而,可使用任何合适的深度。一旦形成开口,可例如通过灰化及/或蚀刻制程来移除光阻材料。

112.一旦移除了光阻,可用导电结构填充或过度填充开口,以形成第一测试垫105的导电结构。在一实施例中,可通过于第一内连线层107上方沉积阻障层113来形成第一测试垫105的导电结构,上述阻障层113顺应于(conform to)开口的底部、及侧壁,并符合第一内连线层107的上表面。在一些实施例中,阻障层113可为使用例如下列沉积制程来沉积的阻障材料:化学气相沉积、物理气相沉积、原子层沉积等的沉积制程,上述阻障材料例如氮化钛、或氮化钽。然而,可使用任何合适的材料或沉积方法来形成阻障层。在一些实施例中,可将阻障层形成为介于约至约之间的厚度,例如约然而,可使用任何合适的材料及厚度。

113.一旦形成了阻障层113,便可沉积导电材料115以填充及/或过度填充第一内连线层107内的开口。在一实施例中,导电材料115可为例如使用晶种层(未绘示)及电镀制程来形成的例如下列的材料:铜、钨、钌、二氧化钛、其组合等,上述电镀制程例如电化学电镀,尽管依据所需的材料也可使用其他的形成制程,例如溅射、蒸发、原子层沉积、或pecvd制程。一旦用导电材料115填充或过度填充开口,则可移除开口外部任何多余的材料,举例而言,通过化学机械平坦化(chemical mechanical planarization,cmp),以使用第一内连线层107来平坦化第一测试垫105。

114.第一内连线层107还包括例如下列的一或多个导电部件(未绘示):金属线、导电导孔(例如,连接件)、接触插塞、或导电沟槽、再分布线(redistribution lines)、导电垫等,上述导电部件形成于介电层103中,以将装置元件108与上方结构电性耦合、与彼此电性耦合、并且也与第一测试垫105电性耦合。在一实施例中,可同时形成第一内连线层107内的一或多个导电部件、及第一测试垫105,并且可使用相同于形成第一测试垫105的制程来形成第一内连线层107内的一或多个导电部件。然而,如果需要的话,可使用与第一测试垫105不同的材料、不同的制程、以及在不同的时间形成一或多个导电部件。

115.图1b绘示出第一测试垫105的平面图,其中图1b中的线a

‑

a绘示出在图1a中可看到的第一测试垫105的切割线。根据一些实施例,第一测试垫105包括框架119、栅格部件121、第一面板区125,其中框架119形成于第一测试垫105的外周边,第一面板区125位于框架119内,且栅格部件121从沿着框架119的一个点延伸至沿着框架119的另一个点,其中至少一些栅格部件121与第一面板区125相交。图1b进一步绘示出框架119与栅格部件121之间的区域,且第一面板区125被第一内连线层107的介电层103的部分分开。如此,第一测试垫105在本文中也可称作“蜘蛛垫(spider pad)”。

116.在一些实施例中,尽管框架119可具有任何合适的规则形状或任何合适的不规则形状,但是框架119为矩形并且具有内周边及外周边。框架119的形状可包括例如下列任何合适的轮廓:弯曲的边缘、凸起的(convex)边缘、凹陷的(concave)边缘、直的边缘、成角度的(angled)边缘、其组合等。框架119形状的示例包括但不限于圆形、椭圆形、三角形、矩形、正方形、菱形、梯形等。再者,框架119可具有任何合适的方位。根据一些实施例中,框架119具有介于约20μm至约80μm之间的第一高度h1,例如约30μm,框架119具有介于约20μm至约80μm之间的第一宽度w1,例如约30μm。如此,框架119(因而,第一测试垫105)具有介于约400μm2至约6400μm2之间的第一面积a1(例如,a1=h1xw1),例如约900μm2。在一些实施例中,框架119的内周边可以介于约0.5μm至约5μm的第一距离dist1与外周边分开,例如约2.5μm。然而,可使用任何合适的高度、宽度、面积、及距离。

117.根据一些实施例,栅格部件121可具有相同的形状或可具有不同的形状,可具有相同的方位或不同的方位,并且可以相同的角度或不同的角度来设置。根据一些实施例,栅格部件121可具有相同的厚度或可具有不同的厚度,并且可以相同的节距(pitches)或以不同的节距来设置。在一些实施例中,栅格部件121包括平行于彼此的直线的第一系列124,上述直线的第一系列124具有第一方位(例如,y方向),具有相同的第一厚度th1,上述第一厚度th1介于约0.1μm至约4μm之间,例如约0.5μm。然而,可将任何合适的形状、方位、角度、厚度、及节距用于直线的第一系列124。

118.提供栅格部件121在此范围内的第一厚度th1确保了直线的第一系列124的完整性。举例而言,提供具有至少0.1μm的第一厚度th1的栅格部件121,防止了栅格部件121由于在图案化及沉积制程期间光学微影曝光的限制而破裂。提供栅格部件121不大于4μm的第一厚度th1,减少了或甚至防止了凹陷(dishing),并且避免了在化学机械平坦化制程期间对直线的第一系列124的过度抛光。

119.此外,可将直线的第一系列124设置成彼此之间距离为介于约0.1μm至约4μm的第二距离dist 2,例如约1μm。将直线的第一系列124以第二距离dist2设置,允许了图案密度比例(th1/(th1+dist2))在化学机械平坦化期间减小或消除栅格部件121的凹陷。举例而言,具有第二距离dist2小于0.1μm时,图案密度比例增加,这可能导致化学机械平坦化期间凹陷的增加。在大于4μm的第二距离dist2处设置直线的第一系列124可能会增加第一测试垫105的垫电阻(pad resistance),这可能会影响晶圆接受度测试测量的结果。

120.在一些实施例中,栅格部件121还包括彼此平行并且具有第一方位(例如,y方向)的直线的第二系列123。在此实施例中,直线的第二系列123可具有大于(直线的第一系列的)第一厚度th1的第二厚度th2,例如介于约0.5μm至约4.0μm之间,例如约1μm。再者,可将直线的第二系列123设置成彼此之间距离为介于约1μm至约10μm之间的第三距离dist3,例如约8.5μm。然而,可将任何合适的形状、方位、角度、厚度、及节距用于直线的第二系列123。

121.在一些实施例中,栅格部件121包括垂直于第一直线的第一系列124的方位的直线的第三系列126。在此实施例中,直线的第三系列126具有大于第一厚度th1的第三厚度th3,且第三厚度th3可介于约0.5μm至约4μm之间,例如约1μm,并且可将直线的第三系列126设置成彼此之间距离约介于1μm至约10μm之间的第四距离dist4,例如约8.5μm。然而,可将任何合适的形状、方位、角度、厚度、及节距用于直线的第三系列126。

122.提供栅格部件121在此范围内的第三厚度th3确保了栅格部件121的完整性。举例

而言,提供具有至少0.5μm的第三厚度th3的栅格部件121,防止了栅格部件121由于在图案化及沉积制程期间光学微影曝光的限制而破裂。提供栅格部件121不大于4μm的第三厚度th3,减少了或甚至防止了凹陷(dishing),并且避免了在化学机械平坦化制程期间对栅格部件121的过度抛光。将直线的第三系列126以第四距离dist4设置,允许了图案密度比例(th3/(th3+dist4))在化学机械平坦化期间减小或消除直线的第三系列126的凹陷。举例而言,具有第四距离dist4小于1μm时,图案密度比例增加,这可能导致化学机械平坦化期间凹陷的增加。在大于10μm的第四距离dist4处设置直线的第三系列126可能会增加垫电阻(pad resistance),这可能会影响晶圆接受度测试测量的结果。

123.图1b进一步绘示出于实心区内的第一面板区125是具有锯齿边缘的第一形状s1(例如,圆形、椭圆形(elliptical)、广椭圆形(oval)等)。第一面板区125可位于第一测试垫105的中心区内,并且其尺寸及形状被设置为提供足够的接触面积以接收晶圆测试探针。然而,第一面板区125(例如,探针区)也可位于框架119内的其他位置,并且甚至可与框架119的一或多个部分一体成型。在一些实施例中,栅格部件121的第二系列的栅格部件与具有第一方位(例如,y方向)的第一面板区125的中心线相交,且栅格部件121的第二系列的其他栅格部件与第一面板区125的外边缘部分相交。在一些实施例中,栅格部件121的第三系列126的栅格部件与具有第二方位(例如,x方向)的第一面板区125的中心线相交,而栅格部件121的第三系列126的其他栅格部件与第一面板区125的外边缘部分相交。

124.图1b更绘示出第一面板区125可具有长轴(例如,第一尺寸dim1)及短轴(例如,第二尺寸dim2)。根据一些实施例,第一尺寸dim1介于约10μm至约30μm之间,例如约20μm,且第二尺寸dim2介于约10μm至约30μm之间,例如约20μm。此外,第一面板区125具有以第一粗虚线127突出显示的第二面积a2,且第二面积a2可介于约78μm2至约707μm2之间,例如约314μm2。然而,可使用任何合适的尺寸、半径、及/或面积。

125.此外,在一些实施例中,第一面板区125最远的边缘可沿着圆s1,上述圆s1具有介于约5μm至约15μm之间的第一半径r1,例如约10μm,而锯齿边缘从圆s1向内延伸。在这样的实施例中,锯齿边缘可在第一方向上以第一锯齿距离ds1向内延伸,上述第一锯齿距离ds1介于约0.5μm至约4μm之间,例如约3μm,并且可在第二方向上以第二锯齿距离ds2向内延伸,上述第二锯齿距离ds2介于约0.5μm至约4μm之间,例如约3μm。然而,可使用任何合适的尺寸。

126.图1b进一步绘示出第一测试垫105于第一面板区125的周边及框架119的内周边之间由栅格部件121所占据的区域内具有第三面积a3,上述框架119的内周边通过第二粗虚线129突出显示。根据一些实施例,第三面积a3介于约100μm2至约6241μm2之间,例如约625μm2。然而,可使用任何合适的区域。在一些实施例中,第一面板区125的面积与第一测试垫105的面积的第一比例(ratio1=a2/a1)可介于约1:1.3至约1:82之间,例如约1:2.9,且栅格部件121所占据的面积与第一测试垫105的面积的第二比例(ratio2=a3/a1)可介于约1:1至约1:4之间,例如约1:1.44。然而,可使用任何合适的面积及比例。

127.一旦形成了第一测试垫105,可将第一测试垫105用于在半导体晶圆100的制造期间对一或多个装置元件108进行原位测试。举例而言,可将第一测试垫105用于促进晶圆接受度测试(wafer acceptance testing,wat)、及/或电路探针(circuit probe,cp)测试以进行制程控制监视(process control monitoring,pcm)。可进行wat以分析晶圆制造制程

在制造的各个阶段的成功,并尝试确定任何制造缺陷的原因。电路探针(circuit probe,cp)测试涉及使用一或多个探针来确定哪些晶粒良好、以及哪些晶粒不良好。可通过探针针头(probe needle)(未绘示)与第一测试垫105接触来进行针测。此探针针头可为具有多个探针针头的探针卡(probe card)的一部分,举例而言,探针针头连接至测试装置(未绘示)。在测试(例如,wat、及/或pcm)期间,将探针针头放置在与第一测试垫105接触的位置,以进行电性接触,因此可在形成半导体晶圆100目前的中间阶段,将电压或电流用于测试装置的功能及性能。如果半导体晶圆100通过了晶圆接受度测试,则晶粒为已知良好晶粒(known good die,kgd)。

128.图2绘示出在制造半导体晶粒的中间步骤中半导体晶圆100的剖面图。具体而言,根据一些实施例,图2绘示出于半导体晶圆100的第一内连线层107上方形成另外的内连线层(为了清楚仅绘示出划线区111)。具体而言,图2绘示出测试垫(例如,第二测试垫205、第三测试垫211、第四测试垫217、第五测试垫223、第六测试垫229、第七测试垫235、第八测试垫241、及第九测试垫247)形成于金属化层(例如,第一金属化层m1、第二金属化层m2、第三金属化层m3、第四金属化层m4、第五金属化层m5、第六金属化层m6、第七金属化层m7、及第八金属化层m8)中,上述金属化层形成于底部金属化层m0上方。尽管在图2中绘示出九个测试垫(例如,第一测试垫105、第二测试垫205、第三测试垫211、第四测试垫217、第五测试垫223、第六测试垫229、第七测试垫235、第八测试垫241、第九测试垫247)及九个内连线层(例如,第一内连线层107、第二内连线层203、第三配线层209、第四内连线层215、第五内连线层221、第六内连线层227、第七内连线层233、第八内连线层239、及第九内连线层245),但是可使用任何合适数量的测试垫、及合适数量的内连线层(例如,金属化层)。

129.一旦形成了第一内连线层107于底部金属化层m0,且在底部金属化层m0的装置元件上进行了任何所需的wat及pcm测试,则蚀刻停止层201可形成于第一内连线层107上方,以将底部金属化层m0中的第一测试垫105与上方结构隔离。蚀刻停止层201用于保护第一内连线层107、并为后续蚀刻制程提供控制点(control point),例如在随后形成的金属化层中。

130.根据一些实施例,可使用例如下列的材料形成蚀刻停止层201:氮化硅(silicon nitride,sin)、氮化物、碳化物、硼化物、碳掺杂的氧化物(例如,sioc)、或氧化铝、其组合等。尽管可使用任何合适的沉积技术,但是可使用例如下列的制程来形成蚀刻停止层201:等离子体增强化学气相沉积(plasma enhanced chemical vapor deposition,pecvd)、低压cvd(low pressure cvd,lpcvd)、pvd、cvd、ald、其组合等。

131.一旦于第一内连线层107上方形成了蚀刻停止层201,便可于蚀刻停止层201上方形成第二内连线层203。根据一些实施例,第二内连线层203包括一或多个介电层103、多个导电部件(未绘示)、及第二测试垫205。可形成第二内连线层203的多个导电部件以将第一内连线层107的多个导电部件及(图1a所示)装置元件108中的一或多个电性耦合至上方结构。再者,形成于第二内连线层203中至少一个的导电部件,经由第一内连线层107至第二内连线层203,将第二测试垫205电性耦合至一或多个装置元件108。可使用适合于如上所述于第一内连线层107中形成一或多个介电层103、多个导电部件、及第一测试垫105的任何材料及制程,来形成一或多个介电层103、多个导电部件、及第二测试垫205。然而,可使用其他合适的材料、制程及深度。

132.根据一些实施例,将第二测试垫205形成为大于第一深度d1的第二深度d2,并且第二深度d2可介于约20nm至约850nm之间,例如约40nm。一旦形成了第二测试垫205,可于底部金属化层m0的一或多个装置元件108上进行任何所需的wat及pcm测试。

133.一旦使用第二测试垫205进行了所需的测试,可在于第二内连线层203上方形成第二蚀刻停止层207,以将导电部件及第二测试垫205与上方结构隔离。在一实施例中,可使用如前文所述的关于第一蚀刻停止层201的材料及制程来形成第二蚀刻停止层207。然而,可使用任何合适的材料及制程。

134.一旦于第二内连线层203上方形成了第二蚀刻停止层207,可于第二蚀刻停止层207上方形成第三内连线层209作为第二金属化层m2,上述第三内连线层209包括一或多个介电层103、多个导电部件(未绘示)、及第三测试垫211。在一实施例中,可使用类似于第二内连线层203的形成制程及材料来形成第三内连线层209,尽管可将第三测试垫211形成为介于约20nm至约850nm之间的第三深度d3,例如约36nm。然而,可使用任何合适的方法、材料、及深度。

135.第三内连线层209的多个导电部件的一或多个,将第三测试垫211及/或上方结构电性耦合至第二内连线层203的多个导电部件的一或多个。如此,第一内连线层107的一或多个装置元件108(如图1a所示)电性耦合至第三测试垫211。一旦形成了第三测试垫211,可于底部金属化层m0的一或多个装置元件108上进行任何所需的wat及pcm测试。

136.后续测试使用第三内连线层209的第三测试垫211,可通过重复沉积另外的刻蚀停止层(例如,第三蚀刻停止层213、第四蚀刻停止层219、第五蚀刻停止层225、第六蚀刻停止层231、第七蚀刻停止层237、第八蚀刻停止层243、及第九蚀刻停止层249)、形成另外的内连线层(例如,第四内连线层215、第五内连线层221、第六内连线层227、第七内连线层233、第八内连线层239、第九内连线层245)作为金属化层(例如,第三金属化层m3、第四金属化层m4、第五金属化层m5、第六金属化层m6、第七金属化层m7、第八金属化层m8)来继续制程,直到所需的最顶金属化层(例如,第八金属化层m8)形成,上述另外的内连线层包括另外的测试垫(例如,第四测试垫217、第五测试垫223、在第六测试垫229、第七测试垫235、在第八测试垫241、第九测试垫247)、另外的导电结构(未绘示)。在形成每个内连线层之后,可使用形成于各个金属化层内的测试垫来进行进一步所需的测试,以分别接触下方的金属化层。

137.根据一些实施例中,可将金属化层的测试垫(例如,第一测试垫105、第二测试垫205、第三测试垫211、第四测试垫217、第五测试垫223、第六测试垫229、第七测试垫235、第八测试垫241、及第九测试垫247)形成为相同的深度(例如,第一深度d1)、或者可将它们形成为不同的深度(例如,第一深度d1、第二深度d2、第三深度d3、第四深度d4、第五深度d5、第六深度d6、第七深度d7、第八深度d8、及第九深度d9)。根据一些实施例,底部金属层m0的第一深度d1可介于约20nm至约150nm之间,例如约25nm。第一金属化层m1的第二深度d2可介于约20nm至约850nm之间,例如约40nm。第二金属化层m2的第三深度d3可介于约20nm至约850nm之间,例如约36nm。第三金属化层m3的第四深度d4可介于约20nm至约850nm之间,例如约46nm。第四金属化层m4的第五深度d5可介于约20nm至约850nm之间,例如约56nm。第五金属化层m5的第六深度d6可介于约20nm至约850nm之间,例如约76nm。第六金属化层m6的第七深度d7可介于约20nm至约850nm之间,例如约76nm。第七金属化层m7的第八深度d8可介于约20nm至约850nm之间,例如约150nm。第八金属化层m8的第九深度d9可介于约20nm至约850nm

之间,例如约850nm。然而,可使用任何合适的深度。

138.再者,金属化层的测试垫可具有相同的形状、尺寸(例如,第一高度h1、第一宽度w1、第一距离dist1、第一厚度th1、第二厚度th2、第三厚度th3、第一节距p1、第二节距p2、第三节距p3、第一尺寸dim1、及第二尺寸dim2)及面积,或者它们可以具有不同的形状、尺寸、及面积。根据一些实施例,底部金属化层m0的测试垫至第八金属化层m8的测试垫可具有相同的第一比例ratio1及相同的第二比例ratio2,或者它们可具有不同的比例。

139.图2进一步绘示出于最顶内连线层(例如,第八金属化层m8)上方形成的钝化层251。根据一些实施例,钝化层251可为聚苯并恶唑(polybenzoxazole,pbo),但是也可使用任何合适的材料,例如苯环丁烯(benzocyclobutene,bcb)、聚酰亚胺、或聚酰亚胺衍生物。可使用例如旋涂制程来设置钝化层251,但是也可使用任何合适的方法。一旦形成了钝化层251,可于钝化层251上方、及/或穿过钝化层251形成另外的层(例如,再分布层、另外的导电部件、连接件等),以将上方的导电部件及/或半导体装置电性耦合至位于半导体晶圆100的装置区109中的装置元件。举例而言,可使用光学微影技术将钝化层251图案化,以形成开口,穿过开口露出最顶内连线层(例如,第八金属化层m8)的导电部件。一旦露出了导电部件,可使用例如铝、铝合金、铜、或铜合金的导电材料于开口中形成另外的导电部件,尽管可使用其他金属材料。再者,一旦形成了钝化层251且任何上方的导电部件、及/或任何上方的半导体装置电性耦合至装置元件,则半导体晶圆100可经历进一步的封装制程,以封装形成于半导体晶圆内的半导体晶粒。

140.图3是根据另一实施例,绘示出具有第二面板区325的第二测试垫305的平面图。第二测试垫305类似于第一测试垫105,不同之处在于第二面板区325的形状不同于第一面板区125的形状。第二面板区325为具有带有直的边缘(straight edges)的第二形状s2(例如,矩形、正方形等)的实心区。尽管图3中所示的第二面板区325具有矩形的周边,但是第二面板区325可具有任何合适的形状。第二面板区325可具有任何合适的规则形状或任何合适的不规则形状,包括前文所述针对框架119的形状任何示例。

141.再者,尽管第一测试垫105与第二测试垫305的宽度、高度、及面积可彼此不相同,但第二测试垫305可具有与第一测试垫105相同的第一宽度w1、第一高度h1、及第一面积(a1=w1xh1)。此外,第二测试垫305的框架119可具有与第一测试垫105的框架119相同尺寸的内周,尽管它们也可不同。框架119的内周在图3中通过第二粗虚线129来突出显示。第二面板区325可以具有介于约15μm至约30μm之间的第三尺寸dim3的长轴,例如约15μm,并且具有介于约12μm至约18μm之间的第四尺寸dim4的短轴,例如约12μm。如此,第二面板区325在第二面板区325的周边内具有以第三粗虚线327来突出显示的第四面积(a4=dim3xdim4),并且在第二面板区325的周边以及由第二粗虚线129突出显示的框架119的内周边之间被栅格部件121所占据的区中具有第五面积a5。根据一些实施例,第四面积a4可介于约180μm2至约540μm2之间,例如约180μm2,且第五面积a5可介于约100μm2至约6241μm2之间,例如约625μm2。再者,第二面板区325的面积与框架119的面积的第三比例(ratio3=a4/a1)可介于约1:1.1至约1:35之间,例如约1:3,且第四栅格部件121所占据的面积与框架119的面积的第四比例(ratio4=a5/a1)可介于约1:1至约1:4之间,例如约1:1.44。然而,可使用任何合适的面积及比例。

142.通过使用本文所述的蜘蛛垫设计,可减少或消除可能对测试垫产生的损坏或源自

于测试垫的损坏所造成的损坏。举例而言,在半导体晶圆的制造期间,用于移除沉积的过量材料的化学机械平坦化(chemical mechanical planarization,cmp)制程也可能导致固体导电部件遭受凹陷(例如,过度抛光),使得固体导电部件的上表面减少至介电层的平坦表面下方。如此,在测试过程中,探针可能无法与具有严重凹陷问题的测试垫充分接触,从而阻止进行所需的测试。

143.然而,通过使用栅格部件121以及第一面板区125,可使这种凹陷最小化。具体而言,通过在一或多个介电层103的介电质内将栅格部件121隔开,第一测试垫105上材料的密度可更相等,从而导致更少的凹陷。

144.再者,在测试过程中(例如,wat及/或pcm),使用探针(probe)在探针脚(probe pin)及测试垫之间建立电性接触,因此可施加电压或电流以作为装置功能及性能的测试,且这些探针可能会损坏测试垫。这种损坏再加上由单粒化(singulation)制程所引起的较大机械应力,可能会传递至装置区。对于包括低k介电材料的介电层,这种损伤的传递尤其会发生。

145.然而,通过使用如本文所述的蜘蛛垫设计,可将由凹陷及针测所引起的损坏最小化。举例而言,图4绘示出在第一测试垫105的工作周期(duty cycle)的前十次探针测试期间经历晶圆接受度测试(wat)及/或pcm的第一测试垫105(例如,蜘蛛垫)的电阻的表。在第一探针测试期间,蜘蛛垫具有小于约4欧姆的电阻。再者,即使经过十次探针测试,测试探针对蜘蛛垫几乎没有造成损坏。如图4所示,在十次探针测试中,蜘蛛垫的电阻维持在4欧姆或4欧姆以下。

146.水平栅格垫(未绘示)形成与蜘蛛垫相同的尺寸,然而仅具有一系列栅格部件121彼此平行,并且从框架119的一侧延伸至框架119的另一侧,而框架119之间没有形成中间的面板区(例如,第一面板区125),则其电阻将比蜘蛛垫的电阻高。举例而言,在第一探针测试期间,水平栅格垫具有大于约6欧姆的电阻。再者,在探针测试(例如十次探针测试)之后,测试探针对水平栅格垫造成的损坏将水平栅格的电阻增加至8欧姆以上。对水平测试垫的重大损坏可能会导致不准确及/或完全失败的探针测试(例如,wat及/或pcm)。

147.根据本文揭示的实施例,测试垫的栅格部件之间的介电材料有助于防止测试垫凹陷,使得可在测试期间使测试探针及测试垫之间进行充分的接触。再者,测试垫的面板区在重复测试期间为探针提供了稳固的接触区,从而防止了探针的任何打滑对测试垫的栅格部分造成损坏。如此,相较于仅具有实心垫区的测试垫或仅具有栅格部件的测试垫,根据本文揭示的实施例的测试垫可产生具有较少由于凹陷而导致的缺陷,并且可在重复测试中保持其实质完整性及电阻。

148.在一实施例中,一种方法,包括:沉积介电层于基板上;蚀刻多个开口于介电层中;及沉积导电材料于所述开口中,以形成测试垫的第一栅格部件(grid feature)及面板区,第一栅格部件从面板区纵向延伸至测试垫的周边,第一栅格部件于面板区具有第一宽度,第一宽度小于面板区在第一栅格部件的宽度。在一实施例中,方法还包括使用测试垫进行探针测试。在一实施例中,其中沉积导电材料于所述开口中的步骤还包括形成测试垫的第二栅格部件,第二栅格部件该面板区纵向延伸至测试垫的周边,介电层的第一部分设置于第一栅格部件及第二栅格部件之间。在一实施例中,第二栅格部件具有第二宽度,第二宽度大于第一宽度。在一实施例中,面板区具有一锯齿边缘。在一实施例中,沉积导电材料于所

述开口中的步骤还包括形成测试垫的第三栅格部件,第三栅格部件从面板区延伸至测试垫的周边,第三栅格部件垂直于第一栅格部件。在一实施例中,面板区为矩形。

149.在另一实施例中,一种方法,包括:蚀刻多个开口于基板上方的介电层中;沉积导电材料于所述开口中;及用介电层平坦化导电材料,以形成测试垫,测试垫包括框、位于框内的栅格区、以及位于栅格区的内部的探针区,栅格区包括被介电层的多个部分隔开的多个导电栅格部件。在一实施例中,用介电层的平坦化导电材料的步骤包括形成与框及探针区相交的所述导电栅格部件。在一实施例中,形成所述导电栅格部件的步骤包括形成第一栅格部件于第一方位上,以及形成第二栅格部件于垂直于第一方位的第二方位上。在一实施例中,形成第一栅格部件的步骤包括将第一栅格部件形成为第一厚度;及形成第二栅格部件的步骤包括将第二栅格部件形成为大于第一厚度的第二厚度。在一实施例中,形成与框及探针区相交的所述导电栅格部件中的至少一些,包括形成第三栅格部件在第一方位上,并将第三栅格部件形成为第二厚度。在一实施例中,沉积第二介电层于测试垫上方;及形成第二测试垫于第二介电层中。在一实施例中,相较于测试垫延伸进介电层中的程度,第二测试垫延伸进第二介电层中的程度更大。

150.在又一实施例中,一种半导体装置,包括:介电材料;第一测试垫,位于介电材料内,第一测试垫,包括:外框;栅格区,从外框向内延伸,栅格区包括多个导电栅格构件(grid member),所述导电栅格构件通过介电材料彼此分开;及面板区,位于栅格区的内部,其中所述导电栅格构件的第一个将面板区连接至外框,且其中所述导电栅格构件的第一个具有第一厚度,且面板区具有第二厚度,第一厚度小于第二厚度。在一实施例中,所述导电栅格构件中的第二个具有第三厚度,第三厚度大于第一厚度。在一实施例中,介电材料将面板区与外框分开,介电材料设置于所述导电栅格构件的第一个及所述导电栅格构件的第二个之间。在一实施例中,所述导电栅格构件中的第一个及所述导电栅格构件中的第二个各自对准第一方向。在一实施例中,半导体装置还包括第二测试垫位于第一测试垫上方,第二测试垫包括第二外框、第二栅格区、及第二面板区。在一实施例中,半导体装置还包括所述导电栅格构件中的第三个,其中所述导电栅格构件中的第三个垂直于所述导电栅格构件中的第一个。

151.以上概述数个实施例的部件,以便在本发明所属技术领域中具有通常知识者可更加理解本发明实施例的观点。在本发明所属技术领域中具有通常知识者应理解,他们能轻易地以本发明实施例为基础,设计或修改其他制程及结构,以达到与在此介绍的实施例相同的目的及/或优势。在本发明所属技术领域中具有通常知识者也应理解,此类等效的结构并无悖离本发明的精神与范围,且他们能在不悖离本发明的精神及范围下,做各式各样的改变、取代及替代。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1