半导体封装体及其制造方法与流程

1.本技术案主张2020年5月1日申请的美国正式申请案第16/864,767号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

2.本公开涉及一种半导体封装体及其制造方法。特别是涉及一种具有气隙以降低导电构件之间的电容耦合的半导体封装体及其制造方法。

背景技术:

3.近年来,由于各种电子构件的集成密度不断提高,半导体工业已历经快速的成长。这些持续微缩化的电子构件需要比先前的封装体占据更小面积的较小封装体。然而,在二维(2d)中可实现的半导体封装体的微缩化存在着物理限制。虽然2d微缩化仍然是新设计的选择之一,但采用利用z方向的三维(3d)封装方案已成为业界研究的焦点。尽管如此,3d封装技术仍存在待处理的挑战。

4.上文的“先前技术”说明仅是提供背景技术,并未承认上文的“先前技术”说明揭示本公开的标的,不组成本公开的先前技术,且上文的“先前技术”的任何说明均不应做为本案的任一部分。

技术实现要素:

5.本公开的一方面提供一种半导体封装体。该半导体封装体包括:一第一半导体结构,具有一第一表面和从该第一表面凹陷的多个第一凹部;以及一第二半导体结构,具有一第二表面和从该第二表面凹陷的多个第二凹部,其中该第一和第二半导体结构彼此接合,该第一表面与该第二表面接触,每一个所述第一凹部与所述第二凹部的其中之一彼此重叠并结合以形成密封于该半导体封装体中的一气隙。

6.在一些实施例中,该第一半导体结构包括多个第一导电结构,其具有与该第一表面实质上共平面的表面,该第二半导体结构包括多个第二导电结构,其具有与该第二表面实质上共平面的表面,且所述第一导电结构分别与所述第二导电结构接触。

7.在一些实施例中,所述气隙的其中之一位于相邻的所述第一导电结构之间,且位于相邻的所述第二导电结构之间。

8.在一些实施例中,所述第一凹部在形状和尺寸上与所述第二凹部实质上相同。

9.在一些实施例中,该第一表面为一第一绝缘结构的一表面,所述第一凹部凹陷至该第一绝缘结构之中,该第二表面为一第二绝缘结构的一表面,且所述第二凹部凹陷至该第二绝缘结构之中。

10.在一些实施例中,该第一半导体结构包括多个第一钝化层共形地覆盖所述第一凹部的表面,且该第二半导体结构包括多个第二钝化层共形地覆盖所述第二凹部的表面。

11.在一些实施例中,所述气隙分别被所述第一钝化层的其中之一和所述第二钝化层的其中之一包围。

12.本公开的另一方面提供一种半导体封装体。该半导体封装体包括:一第一半导体

结构,具有一第一接合表面;一第二半导体结构,具有一第二接合表面,其与该第一半导体结构接合,其中该第一接合表面与该第二接合表面部分地接触,该第一接合表面的一部分与该第二接合表面的一部分隔离,该第一和该第二接合表面的所述部分之间的一空间被密封并形成一气隙于该半导体封装体中。

13.在一些实施例中,该第一接合表面具有一第一凹陷部分,该第二接合表面具有一第二凹陷部分,该第一凹陷部分和该第二凹陷部分结合以形成该气隙。

14.在一些实施例中,该第一凹陷部分与该第二凹陷部分在形状和尺寸上与彼此实质上相同。

15.本公开的又一方面提供一种半导体封装体的制造方法。该方法包括:提供具有一集成电路的一基板;形成具有接合结构和支撑结构的一第一绝缘层堆叠于该集成电路上;形成一掩膜图案于该第一绝缘层堆叠上;移除该第一绝缘层堆叠的一些部分以形成多个第一凹部于该第一绝缘层堆叠的一顶部区域中;形成一钝化层共形地覆盖所述第一凹部和该第一绝缘层堆叠的一顶表面;移除该钝化层位于该第一绝缘层堆叠的该顶表面上方的部分,以形成一第一半导体结构;提供具有一第二绝缘层堆叠的一第二半导体结构,其中该第二绝缘层堆叠具有多个第二凹部;以及接合该第一半导体结构与该第二半导体结构,所述第一凹部和所述第二凹部形成多个气隙。

16.在一些实施例中,所述第一凹部和所述第二凹部彼此重叠并结合以形成密封于该半导体封装体中的所述气隙。

17.在一些实施例中,该第一半导体结构包括多个第一导电结构,其具有与该第一绝缘层堆叠的该顶表面实质上共平面的表面,该第二半导体结构包括多个第二导电结构,其具有与该第二绝缘层堆叠的一顶表面实质上共平面的表面,且所述第一导电结构与所述第二导电结构接触以形成用以传递信号的一导线。

18.在一些实施例中,所述气隙的其中之一位于相邻的所述第一导电结构之间,且位于相邻的所述第二导电结构之间。

19.在一些实施例中,所述第一凹部在形状和尺寸上与所述第二凹部实质上相同。

20.在一些实施例中,该第二半导体结构包括一第二钝化层共形地覆盖所述第二凹部和该第二绝缘层堆叠的一顶表面。

21.在一些实施例中,所述气隙分别被该第一钝化层和该第二钝化层包围。

22.在一些实施例中,所述气隙的其中之一位于所述第一导电结构的其中一者和所述第二导电结构的其中一者之间。

23.在一些实施例中,该半导体封装体的制造方法还包括:在接合该第一半导体结构与该第二半导体结构之前,进行一紫外线(uv)固化制程以移除悬键(dangling bonds)。

24.在一些实施例中,该半导体封装体的制造方法还包括:进行一快速热氮化以致密化该钝化层。

25.综上所述,根据本公开实施例的半导体封装体包括彼此接合的两个半导体结构,且包括密封于半导体结构之间的界面处的气隙。一些气隙位于用来在半导体结构之间建立电性连接的导电构件之间。由于空气的低介电常数,故可通过在这些导电构件之间设置气隙来减少它们之间的电容耦合。借此,可降低导电构件的rc延迟。据此,可改善半导体结构之间的信号传递。

26.上文已相当广泛地概述本公开的技术特征及优点,而使下文的本公开详细描述得以获得较佳了解。组成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

附图说明

27.本公开各方面可配合以下图式及详细说明阅读以便了解。要强调的是,依照工业上的标准惯例,各个部件(feature)并未按照比例绘制。事实上,为了清楚的讨论,可能任意的放大或缩小各个部件的尺寸。

28.图1是根据本公开一些实施例显示半导体结构的制造方法流程图。

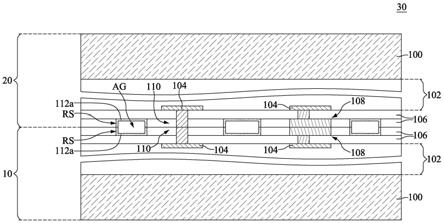

29.图2a到图2i是显示结构在图1所示制程期间各阶段的剖面示意图。

30.图3是根据本公开一些实施例显示半导体结构的制造方法流程图。

31.图4a到图4k是显示结构在图3所示制程期间各阶段的剖面示意图。

32.其中,附图标记说明如下:

33.10:半导体结构

34.11:接合表面

35.20:半导体结构

36.21:接合表面

37.30:半导体封装体

38.40:半导体结构

39.41:接合表面

40.50:半导体结构

41.51:接d合表面

42.60:半导体封装体

43.100:基板

44.102:集成电路

45.104:内连线

46.106:绝缘层

47.108:接合结构

48.108a:接合垫

49.108b:布线结构

50.110:支撑结构

51.112:钝化层

52.112a:钝化层

53.200:基板

54.202:集成电路

55.204:内连线

56.206a:绝缘层

57.206b:绝缘层

58.206c:绝缘层

59.210:支撑结构

60.300:基板

61.302:集成电路

62.304:内连线

63.306a:绝缘层

64.306b:绝缘层

65.306c:绝缘层

66.308:接合结构

67.ag:气隙

68.ag’:气隙

69.m30:制造方法

70.m60:制造方法

71.pr:掩膜图案

72.rs:凹部

73.rs’:凹部

74.s11:步骤

75.s13:步骤

76.s15:步骤

77.s17:步骤

78.s19:步骤

79.s21:步骤

80.s23:步骤

81.s25:步骤

82.s31:步骤

83.s33:步骤

84.s35:步骤

85.s37:步骤

86.s39:步骤

87.s41:步骤

88.s43:步骤

89.s45:步骤

90.s47:步骤

91.s49:步骤

92.s51:步骤

93.t

206a

:厚度

94.t

206b

:厚度

95.t

206c

:厚度

96.t

306a

:厚度

97.t

306b

:厚度

98.t

306c

:厚度

99.t

306c’:厚度

100.th1:穿孔

101.th2:穿孔

102.w:开口

具体实施方式

103.以下揭示提供许多不同的实施例或是例子来实行本公开实施例的不同部件。以下描述具体的元件及其排列的例子以简化本公开实施例。当然这些仅是例子且不该以此限定本公开实施例的范围。例如,在描述中提及第一个部件形成于第二个部件“之上”或“上”时,其可能包括第一个部件与第二个部件直接接触的实施例,也可能包括两者之间有其他部件形成而没有直接接触的实施例。此外,本公开可能在不同实施例中重复参照符号及/或标记。这些重复是为了简化与清晰的目的,并非用以限定所讨论的不同实施例及/或结构之间的关系。

104.此外,此处用到与空间相关的用词,例如:“在

…

下方”、“下方”、“较低的”、“之上”、“较高的”、及其相似的用词是为了便于描述图式中所示的一个元件或部件与另一个元件或部件之间的关系。这些空间关系词是用以涵盖图式所描绘的方位之外的使用中或操作中的元件的不同方位。装置可能被转向不同方位(旋转90度或其他方位),则其中使用的空间相关形容词也可相同地照着解释。

105.图1是根据本公开一些实施例显示半导体结构的制造方法m30流程图。图2a到图2i是显示图1所示制程期间各阶段的中间结构的剖面示意图。

106.参照图1和图2a,进行步骤s11,提供具有集成电路102的基板100。在一些实施例中,基板100为晶圆形式。在这些实施例中,基板100可为半导体芯片或绝缘体上半导体(semiconductor

‑

on

‑

insulator;soi)芯片。例如,半导体芯片或soi芯片中的半导体材料可包括元素半导体(例如:si)、合金半导体(例如:sige)、化合物半导体(例如:第3

‑

5族半导体、第2

‑

6族半导体)、或前述的组合。此外,半导体材料可掺杂有第一导电类型(例如:n型)或与第一导电类型互补的第二导电类型(例如:p型)。在基板100为晶圆形式的那些实施例中,基板100可具有通过划线区域(均未显示)与彼此分离的晶粒区域,且集成电路102散布在晶粒区域内。集成电路102可包括形成于基板100表面处的主动元件及/或被动元件(均未显示),且可包括位于主动元件及/或被动元件之上的内连线(也未显示)。内连线被配置为内连接主动元件及/或被动元件,并且将主动元件及/或被动元件布线到集成电路102的顶侧。例如,主动元件可包括金属氧化物半导体场效晶体管(metal

‑

oxide

‑

semiconductor field effect transistors;mosfet),而被动元件可包括电容器。此外,内连线可形成于一介电层堆叠中,且可包括分别延伸于所述介电层的其中一者的表面上的导电线路和垂直延伸并连接到至少一导电线路的导电通孔。应注意的是,在图2a只显示出内连线的最顶端部分,并将其标记为内连线104。此外,集成电路102的顶侧可称为最终形成的半导体结构(例

如,如图2f所示的半导体结构10)的主动侧,而基板100的底侧可称为半导体结构的背侧。

107.参照图1和图2b,进行步骤s13,形成绝缘层106堆叠(例如,两层绝缘层106)以及接合结构108和支撑结构110于集成电路102上。接合结构108和支撑结构110穿过绝缘层106堆叠。应注意的是,只显示出接合结构108的其中之一和支撑结构110的其中之一。接合结构108电性连接到内连线(亦即,内连线104)的最顶端部分,并且可用作集成电路102的输入/输出(i/o)。在一些实施例中,接合结构108分别包括接合垫108a和将接合垫108a连接到内连线(亦即,内连线104)的最顶端部分的布线结构108b。接合垫108a可形成于最外层绝缘层106中,并具有与最外层绝缘层106的顶表面实质上共平面的一顶表面。布线结构108b,像是导电通孔或导电柱,从接合垫108a的底端延伸到内连线(亦即,内连线104)的最顶端部分。另一方面,支撑结构110可形成为导电通孔或导电柱,并延伸穿过绝缘层106堆叠。在一些实施例中,支撑结构110可电性连接到内连线(即,内连线104)的最顶端部分。在这些实施例中,经连接的内连线104和支撑结构110可为电性浮动的,且被配置以增强最终形成的半导体结构(例如,如图2i所示的半导体封装体30)的机械强度。可选地,经连接的内连线104和支撑结构110可电性接地,且可用作集成电路102的电磁屏蔽。在其他实施例中,支撑结构110可不电性连接到任何内连线104,且可为电后浮动的或电性接地的。

108.此外,在一些实施例中,支撑结构110可彼此连接以形成壁(wall),且该壁横向地包围接合结构108。在这些实施例中,壁可用作密封环。在替代实施例中,支撑结构110在横向上与彼此分离,并且与接合结构108一起被密封环(未显示)横向地包围。

109.绝缘层106的材料可包括无机绝缘材料(例如:氧化硅、氮化硅、氮氧化硅、其类似材料、或前述的组合),而接合结构108和支撑结构110可由导电材料组成,像是金属或金属合金(例如:铜、铜合金、其类似材料、或前述的组合)。在一些实施例中,用于形成每一层绝缘层106的方法可包括沉积制程(例如:化学气相沉积(chemical vapor deposition;cvd)制程),而用于形成位于绝缘层106堆叠中的接合结构108和支撑结构110的方法可包括至少一个镶嵌制程。然而,本技术领域具有通常知识者可选择其他可行的材料及/或其他合适的形成方法来形成绝缘层106、接合结构108、和支撑结构110,本公开不限于此。

110.在一些实施例中,接合结构108和支撑结构110中的导电材料通过障壁层(未显示)与绝缘层106堆叠分离。障壁层的材料(在下文中称为障壁材料)可包括ti、tin、ta、tan、其类似材料、或前述的组合。此外,用于形成障壁层的方法可包括沉积制程,像是物理气相沉积(physical vapor deposition;pvd)制程或原子层沉积(atomic layer deposition;ald)制程。

111.参照图1和图2c,进行步骤s15,并且形成掩膜图案pr于绝缘层106堆叠上。掩膜图案pr(像是光阻图案)具有开口w,其定义在随后的步骤期间要在该绝缘层106堆叠形成凹部的位置(例如:如图2d所示的凹部rs)。每一个开口w与接合结构108和支撑结构110均横向地间隔开。一些开口w分别位于接合结构108的其中一者和支撑结构110的其中一者之间,且位于相邻的接合结构108之间或相邻的支撑结构110之间。此外,一些其他的开口w可位于接合结构108和支撑结构110的分布范围之外。在那些掩膜图案pr是光阻图案的实施例中,用于形成掩膜图案pr的方法可包括涂布制程和微影制程。

112.参照图1和图2d,进行步骤s17,通过利用掩膜图案pr作为阴影掩膜来移除绝缘层106堆叠的一些部分,以形成凹部rs于该绝缘层106堆叠的顶部区域中。在一些实施例中,通

过像是非等向性蚀刻制程(anisotropic etching process)的蚀刻制程来移除绝缘层106堆叠与掩膜图案pr的开口w重叠的部分以形成凹部rs。与掩膜图案pr的开口w相同,每一个凹部rs分别与接合结构108和支撑结构110横向地间隔开。一些凹部rs分别位于接合结构108的其中一者和支撑结构110的其中一者之间。此外,一些其他的凹部rs可位于接合结构108和支撑结构110的分布范围之外。在一些实施例中,将最外层绝缘层106与开口w重叠的部分移除,而位于最外层绝缘层106下方的绝缘层106则可实质上保持完整。在这些实施例中,在参照图2b所述的步骤s13期间,蚀刻停止层(未显示)可设置于两个垂直地相邻的绝缘层106之间,且对这些绝缘层106具有足够的蚀刻选择性。通过这种方式,在凹部w形成之后,可暴露出蚀刻停止层与开口w重叠的部分,并可定义凹部rs的底表面。可选地,可省略蚀刻停止层,且在蚀刻制程期间可移除或不移除位于最外层绝缘层106下方的绝缘层106。

113.参照图1和图2e,进行步骤s19,全面地(globally formed)形成钝化层112。其结果,绝缘层106堆叠、接合结构108和支撑结构110的顶表面被钝化层112覆盖。在一些实施例中,钝化层112共形地覆盖下方的结构。在这些实施例中,凹部rs可不被钝化层112填充,且钝化层112在绝缘层106堆叠的顶部区域中相应于凹部rs凹陷。钝化层112的材料可包括例如氮化硅。此外,用于形成钝化层112的方法可包括沉积制程,像是原子层沉积(ald)制程。然而,本技术领域具有通常知识者可选择其他可行的绝缘材料及/或其他合适的形成方法来形成钝化层112,本公开不限于此。

114.参照图1和图2f,进行步骤s21,移除钝化层112位于最外层绝缘层106的顶表面上方的部分。其结果,只留下凹部rs中部分的钝化层112,并将其分别称为钝化层112a。此外,暴露出最外层绝缘层106的顶表面以及接合结构108和支撑结构110的顶表面。在一些实施例中,用于移除部分的钝化层112的方法可包括一平坦化制程。例如,平坦化制程可包括化学机械研磨(chemical mechanical polishing;cmp)制程、蚀刻制程、或前述的组合。

115.在一些实施例中,钝化层112a由氮化硅组成,并且在步骤s21之后进行快速热氮化(rapid thermal nitridation;rtn)制程。通过进行rtn制程,可进一步致密化钝化层112中的氮化硅。在替代实施例中,钝化层112a可由氧化硅组成,且氧化硅在经过rtn制程之后可变成氮氧化硅或氮化硅。此外,在一些实施例中,可进行紫外线(uv)固化制程以移除导电构件(例如,接合结构108、支撑结构110和集成电路102的内连线)中的悬键(dangling bonds)。在这些实施例中,uv固化制程可接在rtn制程之后,但本公开不限于此。

116.至此,形成了半导体结构10。半导体结构10将与另一半导体结构(例如,如图2g所示的半导体结构20)接合,而且最外层绝缘层106、钝化层112a、接合结构108、和支撑结构110的暴露表面可共同定义半导体结构10的接合表面11。接合表面(例如,凹部rs中的钝化层112a的表面)的至少一些部分可不与随后接合的半导体结构(例如,如图2g所示的半导体结构20)接触。在一些实施例中,半导体结构10保持晶圆形式。在替代实施例中,可在图2f所示的结构上进行单片化制程(singulation process),使得可为单片结构之一的半导体结构10成为芯片形式。

117.参照图1和图2g,进行步骤s23,提供半导体结构20。在一些实施例中,通过参照图2a到图2f所述的方法来提供半导体结构20。为了避免重复描述,半导体结构10、20中的构件具有相同的标记。类似于半导体结构10,半导体结构20可保持晶圆形式。可选地,可进一步进行单片化制程,且可为单片结构之一的半导体结构20为芯片形式。半导体结构20将被接

合到半导体结构10上,且最外层绝缘层106、钝化层112a、接合结构108、和支撑结构110的暴露表面可共同定义半导体结构20的接合表面21。接合表面的至少一些部分(例如,凹部rs中的钝化层112a的表面)可不参与半导体结构10、20的接合。

118.参照图1和图2h

‑

2i,进行步骤s25,将半导体结构10、20彼此接合以形成半导体封装体30。关于半导体结构10、20,其可分别为晶圆形式或芯片形式,而半导体封装体30可为晶圆上晶圆(wafer

‑

on

‑

wafer)结构、晶圆上芯片(chip

‑

on

‑

wafer)结构、或芯片上芯片(chip

‑

on

‑

chip)结构。一旦半导体结构10、20接合在一起,半导体结构10、20的接合表面就与彼此部分地接触。在一些实施例中,半导体结构10、20的最外层绝缘层106彼此接合,且半导体结构10的绝缘层106堆叠与半导体结构20的绝缘层106堆叠连接以形成结合的绝缘层106堆叠。此外,半导体结构10、20的接合结构108与彼此接合,并且在半导体结构10、20的集成电路102之间建立电性连接。此外,来自半导体结构10、20的支撑结构110彼此接合,并且可为电性浮动或电性接地的。另一方面,半导体结构10、20的凹部rs彼此对准,使得半导体结构10的钝化层112a的垂直延伸部分与半导体结构20的钝化层112a的垂直延伸部分接合。据此,可通过半导体结构10、20的钝化层112a来密封凹部rs中的空腔,并形成气隙ag于接合结构(亦即,半导体封装体30)中。气隙ag分别由彼此接合的两个钝化层112a包围。接合结构108、支撑结构110、钝化层112a、和气隙ag位于结合的绝缘层106堆叠中。承自凹部rs的本质,一些气隙ag位于接合结构108和支撑结构110的分布范围之内,而一些其他的气隙ag位于接合结构108和支撑结构110的分布范围之外。

119.在一些实施例中,用于接合半导体结构10、20的方法包括通过例如拾取和放置(pick and place;pnp)制程将半导体结构10、20中的一个放置于另一个上,并进行混合接合制程以在半导体结构10、20之间建立物理接合。在一些实施例中,在真空气氛或惰性气氛中进行混合接合制程,以防止导电构件的氧化及/或湿气侵入。混合接合制程可包括用于接合绝缘构件的第一加热步骤和用于接合导电构件的第二加热步骤。例如,绝缘部件可包括附接的绝缘层106和钝化层112a,而导电构件可包括附接的接合结构108和支撑结构110。在一些实施例中,第一加热步骤在第二加热步骤之前。此外,在一些实施例中,第一加热步骤的加热温度低于第二加热步骤的加热温度。例如,第一加热步骤的加热温度可以在150℃至250℃的范围内,而第二加热步骤的加热温度可以在180℃至350℃的范围内。然而,本技术领域具有通常知识者可根据制程需求调整第一加热步骤和第二加热步骤的顺序和加热温度,本公开不限于此。

120.由于空气的低介电常数(例如:大约1),故可通过设置气隙ag来减少横向相邻的接合结构108之间的电容耦合。类似地,接合结构108和支撑结构110之间的电容耦合可因气隙ag而减少。因此,可降低接合结构108的电阻电容延迟(resistive

‑

capacitive delay;rc延迟)。从而,可改善半导体结构10、20的集成电路102之间的信号传递。

121.图3是根据本公开一些实施例显示半导体结构的制造方法m60流程图。图4a到图4k是显示结构在图3所示制程期间各阶段的剖面示意图。参照图3和图4a到图4k描述的实施例和参照图1和图2a到图2i描述的实施例相似,将只讨论它们之间的差异而不再重复相同或相似的部分。此外,相似的标记代表相似或相同的构件(例如:基板100和基板200)。

122.参照图3和图4a,进行步骤s31,提供形成有集成电路202的基板200。应注意的是,只显示出集成电路202中内连线的最顶端部分,并将其标记为内连线204。

123.随后,进行步骤s33,形成绝缘层206a、206b、206c于集成电路202上。绝缘层206a位于绝缘层206b、206c的下方,且绝缘层206b夹在绝缘层206a、206c之间。绝缘层206a具有厚度t

206a

、绝缘层206b具有厚度t

206b

、且绝缘层206c具有厚度t

206c

。在一些实施例中,厚度t

206b

小于厚度t

206a

和厚度t

206c

,且厚度t

206a

可大于、等于、或小于厚度t

206c

。此外,在一些实施例中,绝缘层206b的材料不同于绝缘层206a、206c的材料。例如,绝缘层206b可由氮化硅组成,而绝缘层206a、206c可由氧化硅组成。用于形成每一层绝缘层206a、206b、206c的方法可包括沉积制程,像是化学气相沉积(cvd)制程。然而,本技术领域具有通常知识者可调整绝缘层206a、206b、206c的厚度t

206a

、t

206b

、t

206c

,并选择其他合适的材料和形成绝缘层206a、206b、206c的形成方法,本公开不限于此。

124.参照图3和图4b,进行步骤s35,形成穿孔th1于绝缘层206a、206b、206c中。穿孔th1穿过绝缘层206a、206、206c,并暴露出内连线(亦即,内连线204)的一些最顶端部分。在一些实施例中,暴露的内连线204位于靠近晶粒区域边缘的位置(如参照图2a所描述的)。用于形成穿孔th1的方法可包括进行微影制程和一个或多个蚀刻制程(例如:非等向性蚀刻)。

125.参照图3和图4c,进行步骤s37,形成支撑结构210于穿孔th1中。支撑结构210与先前暴露的内连线204接触。连接的支撑结构210和内连线204为电性浮动或电性接地的。在一些实施例中,用于形成支撑结构210的方法包括通过沉积制程(例如:物理气相沉积(pvd)制程)、镀覆制程(例如:电镀制程或无电镀制程)、或前述的组合将导电材料填充到穿孔th1中。此外,可进行平坦化制程以移除导电材料位于绝缘层206c的顶表面上方的部分。例如,导电材料可包括金属或金属合金(例如:铜、铜合金、其类似材料、或前述的组合)。此外,平坦化制程可包括例如:cmp制程、蚀刻制程、或前述的组合。

126.在一些实施例中,每一个支撑结构210还包括障壁层(未显示),其覆盖每一个穿孔th1中导电材料的侧壁(或侧壁及底表面)。障壁层(在下文中称为障壁材料)的材料可包括ti、tin、ta、tan、其类似材料、或前述的组合。此外,用于形成障壁层的方法可包括通过像是物理气相沉积(pvd)制程或原子层沉积(ald)制程的沉积制程将障壁材料填充到穿孔th1中。在一些实施例中,可通过用来移除导电材料位于绝缘层206c的顶表面上方的部分的平坦化制程来移除障壁材料位于绝缘层206c的顶表面上方的部分。

127.参照图3和图4d,进行步骤s39,移除绝缘层206c。随着绝缘层206c的移除,暴露出绝缘层206b的顶表面和支撑结构210的侧壁的上部分。此外,支撑结构210目前从绝缘层206b的顶表面突出的高度实质上等于绝缘层206c被移除的厚度(亦即,如图4a所示的厚度t

206c

)。

128.参照图3和图4e,进行步骤s41,形成穿孔th2于绝缘层206b、206a中。穿孔th2穿过绝缘层206b、206a,并暴露出内连线(亦即,内连线204)先前被绝缘层206a覆盖的一些最顶端部分。穿孔th2被配置为在随后的步骤中被另一半导体结构的导电构件插入(例如:如图4j所示的半导体结构50的接合结构308)。在一些实施例中,用于形成穿孔th2的方法包括微影制程和至少一蚀刻制程。

129.至此,已形成了半导体结构40。半导体结构40可保持晶圆形式。可选地,可进一步进行单片化制程,且可为单片结构之一的半导体结构40为芯片形式。在一些实施例中,可在以下步骤中将半导体结构40翻转并接合到另一半导体结构(例如,如图4j所示的半导体结构50)上。绝缘层206a、206b、内连线204、和支撑结构210的暴露表面共同定义半导体结构40

的接合表面41。接合表面的至少一些部分可不和与半导体结构40接合的半导体结构接触。

130.参照图3和图4f,进行步骤s43,形成绝缘层306a、306b、306c于形成有集成电路302的基板300上。基板300和集成电路302类似于参照图2a和图4a所述的基板100、200和集成电路102、202,只显示出集成电路302中内连线的最顶端部分,并将其标记为内连线304。此外,绝缘层306a、306b、306c在材料和堆叠顺序方面可类似于参照图4a所描述的绝缘层206a、206b、206c(亦即,绝缘层306a、306b、306c依序堆叠于集成电路302上)。在一些实施例中,绝缘层306a、306b、306c的总厚度大于绝缘层206a、206b、206c的总厚度(如图4a所示)。在这些实施例中,绝缘层306c的厚度t

306c

可大于绝缘层206c的厚度t

206c

(如图4a所示)。另一方面,绝缘层306b的厚度t

306b

与绝缘层206b的厚度t

206b

(如图4a所示)可实质上相同,且绝缘层306a的厚度t

306a

与绝缘层206a的厚度t

206a

(如图4a所示)可实质上相同。可选地,厚度t

306c

、t

306b

、t

306a

可分别大于、等于、或小于厚度t

206c

、t

206b

、和t

206a

(如图4a所示),只要绝缘层306a、306b、306c的总厚度大于绝缘层206a、206b、206c的总厚度即可。

131.参照图3和图4g,进行步骤s45,形成接合结构308于绝缘层306a、306b、306c中。接合结构308穿过绝缘层306a、306b、306c,并与集成电路302中内连线(亦即,内连线304)的一些最顶端部分接触。在一些实施例中,接合结构308被定位在对应于如图4e所示的半导体结构40的穿孔th2的位置,且接合结构308的宽度分别与每一个穿孔th2的宽度实质上相同。在这样的实施例中,可在以下步骤中将接合结构308插入并填充穿孔th2(如图4j所示)。与参照图4c所述的支撑结构210类似,在一些实施例中,每一个接合结构308包括导电材料和覆盖导电材料的侧壁(或侧壁及底表面)的障壁层。可选地,可省略障壁层。

132.参照图3和图4h,进行步骤s47,薄化绝缘层306c。其结果,接合结构308从薄化的绝缘层306c突出。在一些实施例中,将绝缘层306c薄化到厚度t

306c’,该厚度t

306c’实质上等于支撑结构210从绝缘层206b突出的高度(亦即,厚度t

206c

,如参照图4d所述)。在这些实施例中,在移除薄化的绝缘层306c的一部分(如将参照图4i所述的)之后,如图4e所示的支撑结构210和绝缘层206b可同时接合在绝缘层306b和绝缘层306c的剩余部分上(如将参照图4j所述的)。用于薄化绝缘层306c的方法可包括例如回蚀刻制程。

133.参照图3和图4i,进行步骤s49,移除绝缘层306c的一部分。形成由绝缘层306c的剩余部分和绝缘层306b的暴露部分定义的凹部rs’。在一些实施例中,绝缘层306c被移除的部分先前包围接合结构308,在将绝缘层306c的一部分移除之后,接合结构308的暴露部分的高度增加。接合结构308的暴露部分的高度实质上等于如图4e所示的支撑结构210的高度,且接合结构308的埋藏部分的高度实质上等于绝缘层306a、306b的总厚度。这样一来,当将半导体结构40的支撑结构210接合到绝缘层306b的暴露表面上时,接合结构308可插入穿孔th1中并且刚好到达内连线204,如图4j所示。另一方面,绝缘层306c的剩余部分可与接合结构308横向地间隔开。在一些实施例中,绝缘层306c的剩余部分在横向上包围接合结构308,并且呈现为环形。用于移除一部分的绝缘层306c的方法可包括微影制程和蚀刻制程(例如:非等向性蚀刻)。

134.至此,已形成了半导体结构50。半导体结构50可保持晶圆形式。可选地,可进一步进行单片化制程,且可为单片结构之一的半导体结构50为芯片形式。如图4j所示,半导体结构50与半导体结构40接合。绝缘层306c、绝缘层306b、和接合结构308的暴露表面可共同定义半导体结构50的接合表面51。半导体结构50的接合表面的至少一部分可不与半导体结构

40的接合表面接触,如以下步骤中所述。

135.参照图3和图4j至图4k,进行步骤s51,将如图4e所示的半导体结构40翻转并接合到半导体结构50上。半导体结构40的一部分绝缘层206b接合到半导体结构50的绝缘层306c上,而半导体结构40的支撑结构210可接合到绝缘层306b的暴露表面上,并且可与绝缘层306c横向地接触或不接触。此外,半导体结构50的接合结构308插入半导体结构40的穿孔th2,且半导体结构50的接合结构308的顶表面和与穿孔th2重叠的内连线204接触。由于支撑结构210从绝缘层206b突出的部分的高度实质上等于绝缘层306c的厚度,因此支撑结构210可刚好到达绝缘层306b的暴露表面。此外,由于接合结构308从绝缘层306b突出的高度实质上等于绝缘层306c、206b、206a的厚度的总和,所以接合结构308可刚好到达内连线204的先前暴露的表面。此外,由于在接合制程之前已经移除了半导体结构50的绝缘层306c的一部分(如参照图4i所描述的),所以半导体结构40的绝缘层206b可不完全与半导体结构50的绝缘层306c接触。半导体结构40的绝缘层206b的一部分可不沿着垂直方向与半导体结构50接触。半导体结构40的绝缘层206b和半导体结构50的绝缘层306b之间的空间可被绝缘层306c横向地包围,并且被密封在接合结构中以形成气隙ag’。此外,气隙ag’的区域可散布在接合结构308和支撑结构210之间。

136.可将包括结合的半导体结构40、50的结构称为半导体封装体60。在一些实施例中,半导体封装体60可进一步接受其他封装制程及/或测试步骤。

137.如上所述,根据本公开实施例的半导体封装体包括彼此接合的两个半导体结构,且包括密封于半导体结构之间的界面处的气隙。一些气隙位于用来在半导体结构之间建立电性连接的导电构件之间。由于空气的低介电常数,故可通过在这些导电构件之间设置气隙来减少它们之间的电容耦合。借此,可降低导电构件的rc延迟。据此,可改善半导体结构之间的信号传递。

138.本公开的一方面提供一种半导体封装体。该半导体封装体包括:一第一半导体结构,具有一第一表面和从该第一表面凹陷的多个第一凹部;以及一第二半导体结构,具有一第二表面和从该第二表面凹陷的多个第二凹部,其中该第一和第二半导体结构与彼此接合,该第一表面与该第二表面接触,每一个所述第一凹部与所述第二凹部的其中之一彼此重叠并结合以形成密封于该半导体封装体中的一气隙。

139.本公开的另一方面提供了一种半导体封装体。该半导体封装体包括:一第一半导体结构,具有一第一表面和从该第一表面凹陷的一第一凹部,并且包括从该第一凹部的一底表面突出的第一导电结构;以及一第二导电结构,具有一第二表面和从该第二表面凹陷的一第二凹部,并且包括从该第二表面突出的一第二导电结构,其中该第二半导体结构接合到该第一半导体结构上,该第一导电结构插入第二凹部中,该第二导电结构与该第一凹部的该底表面接触,该第二表面的一部分与该第一表面接触以密封该第一凹部,从而形成一气隙于该半导体封装体中。

140.本公开的又另一方面提供一种半导体封装体。该半导体封装体包括:一第一半导体结构,具有一第一接合表面;一第二半导体结构,具有一第二接合表面,其与该第一半导体结构接合,其中该第一接合表面与该第二接合表面部分地接触,该第一接合表面的一部分与该第二接合表面的一部分隔离,该第一和该第二接合表面的所述部分之间的一空间被密封并形成一气隙于该半导体封装体中。

141.虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多制程,且以其他制程或前述的组合替代上述的许多制程。

142.再者,本技术案的范围并不受限于说明书中该的制程、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的揭示内容理解可根据本公开而使用与本文该的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的制程、机械、制造、物质组成物、手段、方法、或步骤。据此,此等制程、机械、制造、物质组成物、手段、方法、或步骤是包含于本技术案的权利要求内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1