发光元件及其制造方法与流程

1.本发明涉及一种发光元件,更详言之,是涉及一种具有提升亮度的发光元件。

背景技术:

2.固态发光元件中的发光二极管(leds)具有具低耗电量、低产热、寿命长、体积小、反应速度快以及良好光电特性,例如具有稳定的发光波长等特性,故已被广泛的应用于家用装置、指示灯及光电产品等。

3.现有的发光二极管包含一基板、一n型半导体层、一活性区域及一p型半导体层形成于基板上、以及分别形成于p型/n型半导体层上的p、n

‑

电极。当通过电极对发光二极管通电,且在一特定值的顺向偏压时,来自p型半导体层的空穴及来自n型半导体层的电子在活性区域内结合以放出光。然而,随着发光二极管应用于不同的光电产品,对于发光二极管的亮度规格也提高,如何提升其亮度,为本技术领域人员所研究开发的目标之一。

技术实现要素:

4.本发明揭露一种发光元件,包含一半导体叠层,依序包含一第一半导体层、一活性区域以及一第二半导体层,其中第一半导体层包含一第一半导体层上表面;一暴露区,位于半导体叠层内,暴露第一半导体层上表面;一第一保护层,覆盖暴露区以及部分第二半导体层;一第一反射结构,位于第二半导体层上,包含一或多个第一开口;以及一第二反射结构,位于第一反射结构上,经由第一开口与第二半导体层电连接;其中,第一保护层的一部分位于第一半导体层上表面之上且具有一第一厚度,第一保护层的另一部分位于第二半导体层之上且具有一第二厚度,第一厚度小于第二厚度。

5.本发明揭露一种发光元件,包含一半导体叠层,依序包含一第一半导体层、一活性区域以及一第二半导体层,其中第一半导体层包含一第一半导体层上表面;一暴露区,位于半导体叠层内,暴露第一半导体层上表面;一第一保护层,覆盖暴露区以及部分第二半导体层;一蚀刻停止层,位于第二半导体层上;一第一反射结构,位于蚀刻停止层上,包含一或多个第一开口,且第一开口暴露蚀刻停止层;一第二反射结构,位于第一反射结构上,经由第一开口与蚀刻停止层及第二半导体层电连接;一电极位于第一保护层上;一第二保护层位于电极上,覆盖暴露区,包含一第二开口暴露电极;以及一焊垫,经由第二开口与电极连接。

附图说明

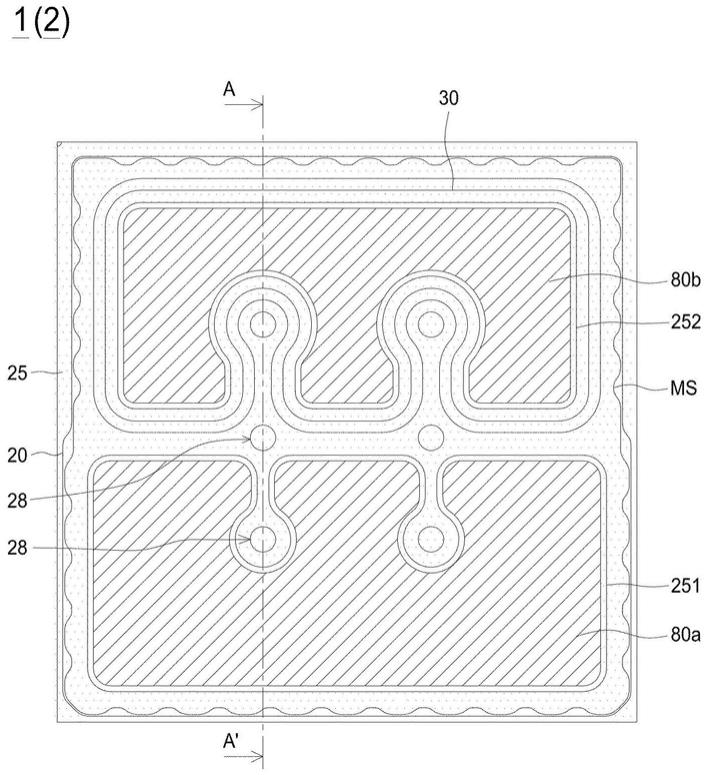

6.图1a为本发明一实施例发光元件1、2的上视图;

7.图1b为本发明一实施例发光元件1的截面图;

8.图1c为本发明一实施例发光元件1的局部截面图;

9.图1d为本发明一实施例发光元件2的截面图;

10.图1e为本发明一实施例发光元件2的局部截面图;

11.图2a至图2h为本发明一实施例发光元件1制造方法中于各阶段的上视图;

12.图3a至图3f为本发明一实施例发光元件1制造方法中于各阶段的截面图;

13.图4a至图4c为本发明一实施例发光元件1制造方法中于部分阶段的截面图;

14.图5a及图5b为本发明一实施例发光元件1制造方法中于部分阶段的截面图;

15.图6a及图6b为本发明一实施例发光元件1中第一反射结构的一截面局部放大图;

16.图7a至图7i为本发明一实施例发光元件2制造方法中于各阶段的上视图;

17.图8a至图8g为本发明一实施例发光元件2制造方法中于各阶段的截面图;

18.图9a至图9c为本发明一实施例发光元件2制造方法中于部分阶段的截面图;

19.图10a及图10b为本发明一实施例发光元件2制造方法中于部分阶段的截面图;

20.图11为本发明一实施例发光装置3的示意图;

21.图12为本发明一实施例发光元件4的示意图。

22.符号说明

23.1、2

ꢀꢀꢀꢀ

发光元件

24.3、4

ꢀꢀꢀꢀ

发光装置

25.10

ꢀꢀꢀꢀꢀꢀ

基板

26.10a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

基板上表面

27.12

ꢀꢀꢀꢀꢀꢀꢀ

半导体叠层

28.121

ꢀꢀꢀꢀꢀ

第一半导体层

29.121a

ꢀꢀꢀꢀ

第一半导体层上表面

30.122

ꢀꢀꢀꢀꢀ

第二半导体层

31.123

ꢀꢀꢀꢀꢀ

活性区域

32.18

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

透明导电层

33.180

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

透明导电层开口

34.26

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

蚀刻停止层

35.28

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

暴露区

36.20

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电极

37.30

ꢀꢀꢀꢀꢀꢀꢀꢀ

第二电极

38.36

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二反射结构

39.360

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二反射结构开口

40.27

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

激光

41.23a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

下部保护层

42.23b

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

上部保护层

43.23

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一保护层

44.230、231

ꢀꢀꢀ

第一保护层开口

45.232

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

上部保护层开口

46.25

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二保护层

47.251、252

ꢀꢀꢀ

第二保护层开口

48.50

ꢀꢀꢀꢀꢀꢀꢀꢀ

第一反射结构

49.50a、50b、50c、50d

ꢀꢀ

第一子层、第二子层、第三子层、第四子层

50.501、502

ꢀꢀ

第一反射结构开口

51.51

ꢀꢀꢀꢀꢀꢀ

载板

52.511、512

ꢀꢀ

垫片

53.53

ꢀꢀꢀꢀꢀꢀ

绝缘部

54.54

ꢀꢀꢀꢀꢀꢀ

反射结构

55.602

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

灯罩

56.604

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

反射镜

57.606

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

承载部

58.608

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

发光单元

59.610

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

发光模块

60.612

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

灯座

61.614

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

散热片

62.616

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

连接部

63.618

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电连接元件

64.t1、t1’、t、t

’ꢀ

厚度

65.ms

ꢀꢀꢀꢀ

高台

66.iso

ꢀꢀꢀꢀ

走道区

具体实施方式

67.下文中,将参照图示详细地描述本发明的示例性实施例,已使得本发明领域技术人员能够充分地理解本发明的精神。本发明并不限于以下的实施例,而是可以以其他形式实施。在本说明书中,有一些相同的符号,其表示具有相同或是类似的结构、功能、原理的元件,且为业界具有一般知识能力者可以依据本说明书的教导而推知。为说明书的简洁度考虑,相同的符号的元件将不再重述。

68.图1a显示本发明一实施例发光元件1的上视图。图2a至图2h显示本发明一实施例发光元件1制造方法中各阶段的上视图;图3a至图3f显示发光元件1制造方法中各阶段的截面图。发光元件1的制造方法详述如下。首先,参照图2a及图3a,在基板10上方形成半导体叠层12,以及在半导体叠层12上形成下部保护层23a。接着,参照图2b及图3a,在半导体叠层12上形成及透明导电层18。图3a显示图2a及图2b的步骤完成后,沿a

‑

a’线段的截面图。基板10可以是一晶片,与形成于其上的半导体叠层12构成一半导体晶片。半导体晶片在后续切割制作工艺后分离成多个发光元件1,以下的实施例图示及说明将以单一个发光元件1做代表。

69.基板10可以是一成长基板,包括用于生长磷化镓铟(algainp)的砷化镓(gaas)基板、及磷化镓(gap)基板,或用于生长氮化铟镓(ingan)或氮化铝镓(algan)的蓝宝石(al2o3)基板,氮化镓(gan)基板,碳化硅(sic)基板、及氮化铝(aln)基板。基板10包含一上表面10a。基板10可以是一图案化基板,即,基板10在其上表面10a上具有图案化结构(图未示)。在一实施例中,从半导体叠层12发射的光可以被基板10的图案化结构所折射及/或反射,从而提高发光元件的亮度。此外,图案化结构减缓或抑制了基板10与半导体叠层12之间因晶格不匹配而导致的错位,从而改善半导体叠层12的外延品质。

70.在本技术案的一实施例中,在基板10上形成半导体叠层12的方法包含有机金属化

vapor deposition,pecvd)来形成。第一子层50a及第二子层50b的形成方式为溅镀。

80.在另一实施例中,如图6b所示,第一反射结构50包含多组材料叠层,第一组材料叠层由第一子层50a及第二子层50b交互堆叠所组成,第二组材料叠层由第三子层50c及第四子层50d交互堆叠所组成。在一实施例中,第二组材料叠层例如为介电材料,由一第三子层50c及一第四子层50d组成一介电材料对。第三子层50c相较于第四子层50d具有较高的折射率,在一实施例中,第三子层50c相较于第四子层50d具有较小的厚度。第三子层50c与第一子层50a具有不同厚度,第三子层50c与第一子层50a可以是相同材料或不同材料。第四子层50d与第二子层50b具有不同厚度,第四子层50d与第二子层50b可以是相同材料或不同材料。

81.在另一实施例中,第一反射结构50还可包含一上层(图未示)位于第一子层50a(及/或第二子层50b)上,相对第二半导体层122的另一侧。也就是说,先于半导体叠层12上形成第一子层50a及第二子层50b,接着再形成上层。上层为非导电材料,包含有机材料或无机材料,其中无机材料可以是介电材料。上层的厚度大于第一子层50a及第二子层50b的厚度。在一实施例中,上层的形成方式与第一子层50a及第二子层50b不同,例如,上层的形成方式为化学气相沉积,更佳地,通过等离子体辅助化学气相沉积(plasma enhanced chemical vapor deposition,pecvd)来形成。第一子层50a及第二子层50b的形成方式为溅镀。

82.在另一实施例中,第一反射结构50包含多组材料叠层与底层及/或上层。在另一实施例中,在形成第一反射结构50之前,通过原子沉积法于基板10及半导体叠层20的一表面上形成一致密层(图未示)以直接披覆半导体叠层12的表面。在一实施例中,借由致密层可更致密的覆盖填补半导体叠层12的表面缺陷,避免水气的侵入。致密层的材料包含无机材料,例如氧化硅、氧化铝、氧化铪、氧化钽、氧化锆、氧化钇、氧化镧、氧化钽、氮化硅、氮化铝或氮氧化硅。在本实施例中,致密层与半导体叠层12相接的介面包含金属元素及氧,其中金属元素包含铝、铪、钽、锆、钇、镧或钽。致密层包含一厚度介于之间,较佳介于之间。

83.在一实施例中,第一反射结构50的厚度介于0.3μm至6μm。在一实施例中,第一反射结构50的侧壁,例如开口501、502的侧壁与透明导电层18的内夹角介于5度至80度。

84.在一实施例中,第一反射结构50在相邻开口501之间不具有开口502。

85.在另一实施例中,第一反射结构50并非如图2c具有多个开口501、502,而是以多个分开的岛状(图未示)分布于第二半导体层122上。

86.接着,参照图2d及图3c,实施一第二反射结构36形成步骤。图3c显示图2a至图2d的步骤完成后,沿a

‑

a’线段的截面图。图2d仅绘示高台ms及第二反射结构36。第二反射结构36对应形成于透明导电层18及第一反射结构50上,其经由第一反射结构50的开口502与透明导电层18及第二半导体层122电连接,且包含多个开口360对应于第一反射结构50的开口501,形成在暴露区28上。第二反射结构36包含一金属结构,可包含单层金属或是由多层金属所形成的叠层。于一实施例中,第二反射结构36包含阻障层(图未示)及反射层(图未示),阻障层形成并覆盖于反射层上,阻障层可以防止反射层的金属元素的迁移、扩散或氧化。反射层的材料包含对于半导体叠层12所发射的光线具有高反射率的金属材料,例如银(ag)、金(au)、铝(al)、钛(ti)、铬(cr)、铜(cu)、镍(ni)、铂(pt)、钌(ru)或上述材料的合金或叠

层。阻障层的材料包括铬(cr)、铂(pt)、钛(ti)、钨(w)、锌(zn)或上述材料的合金或叠层。在一实施例中,当阻障层为金属叠层时,阻障层是由两层或两层以上的金属交替堆叠而形成,例如cr/pt,cr/ti,cr/tiw,cr/w,cr/zn,ti/pt,ti/w,ti/tiw,ti/zn,pt/tiw,pt/w,pt/zn,tiw/w,tiw/zn,或w/zn等。在另一实施例中(图未示),第一反射结构50包含多个岛状分布于第二半导体层122上,第二反射结构36经由岛状之间的间隙与透明导电层18及第二半导体层122电连接。

87.接着,参照图2e及图3d,实施一上部保护层23b形成步骤。图3d显示图2a至图2e的步骤完成后,沿a

‑

a’线段的截面图。图2e仅绘示高台ms、第二反射结构36及上部保护层23b。上部保护层23b形成在第二反射结构36上,覆盖部分第二反射结构36的上表面,并且覆盖下部保护层23a。在暴露区28以及暴露区28附近,上部保护层23b与下部保护层23a相叠且连接。

88.上部保护层23b包含开口230、231以及232。参照图2e,多个开口230间隔地设置于上部保护层23b的周围,露出半导体叠层12周围暴露区28的底部,也就是第一半导体层上表面121a,其功能及对应截面结构将详述如后。多个开口231设置于半导体叠层12内部的暴露区28,露出暴露区28的底部的第一半导体层上表面121a。开口232露出第二反射结构36,在本实施例中仅绘示单一个开口232,然而本发明不限于此,上部保护层23b可包含多个开口232分别暴露第二反射结构36。在一实施例中,先形成一绝缘材料覆盖第二反射结构36及暴露区28,接着再利用显影蚀刻等方式形成开口230、231及232,以形成上部保护层23b。在形成开口230、231的同时,也移除了开口230、231正下方的下部保护层23a。上部保护层23b与下部保护层23a构成一第一保护层23,上部保护层23b与下部保护层23a可为相同材料或不同材料。也就是说,第一保护层23具有多个开口230间隔地设置于其周围,露出第一半导体层上表面121a,以及多个开口231设置于半导体叠层12内部的暴露区28,露出暴露区28的底部的第一半导体层上表面121a。上部保护层23b相对于半导体叠层12所发出的光线为透明,其材料为非导电材料,包含有机材料或无机材料。其中有机材料包含su8、苯并环丁烯(bcb)、过氟环丁烷(pfcb)、环氧树脂(epoxy)、丙烯酸树脂(acrylic resin)、环烯烃聚合物(coc)、聚甲基丙烯酸甲酯(pmma)、聚对苯二甲酸乙二酯(pet)、聚碳酸酯(pc)、聚酰亚胺(polyimide)、聚醚酰亚胺(polyetherimide)或氟碳聚合物(fluorocarbon polymer)。无机材料包含硅胶(silicone)、玻璃(glass)或是介电材料。介电材料例如为氧化硅(sio

x

)、氮化硅(sin

x

)、氧氮化硅(sio

x

n

y

)、氧化铌(nb2o5)、氧化铪(hfo2)、氧化钛(tio

x

)、氟化镁(mgf2)、氧化铝(al2o3)等。下部保护层23a的形成方式包含原子沉积法(atomic layer deposition,ald)、溅镀(sputtering)、蒸镀(evaporation)及旋涂(spin

‑

coating)等方式。由于第一保护层23覆盖暴露区28的侧壁,也就是半导体叠层12的侧壁,可以保护半导体叠层12,避免在后续制作工艺中可能破坏半导体叠层12。在另一实施例中,在半导体叠层12的周围,上部保护层23b还覆盖第一半导体层121的侧壁。

89.接着,参照图2f及图3e,实施一电极形成步骤。图3e显示图2a至图2f的步骤完成后,沿a

‑

a’线段的截面图。图2f仅绘示高台ms、上部保护层23b及电极。电极包含第一电极20以及第二电极30,其中第一电极20覆盖上部保护层23b,经由上部保护层23b的开口230及231,接触暴露区28底部的第一半导体层121并与其形成电连接。第二电极30与第一电极20相互分离,形成在上部保护层23b的开口232中,接触第二反射结构36并与第二半导体层122

电连接。电极包含金属材料,例如铝(al)、铬(cr)、铂(pt)、钛(ti)、钨(w)、锌(zn)或上述材料的合金或叠层。

90.接着,参照图2g,实施一第二保护层形成步骤。参照图2h,实施一焊垫形成步骤。图3f显示图2a至图2g的步骤完成后,沿a

‑

a’线段的截面图。图2g仅绘示高台ms、第一电极20、第二电极30及第二保护层25。

91.第二保护层25形成在第一电极20、第二电极30以及暴露区28上,并延伸覆盖第一半导体层121的侧壁及走道区iso。第二保护层25包含开口251以及252,其中,开口251露出第一电极20,开口252露出第二电极30。在本实施例中仅绘示单一个开口251及单一个开口252,然而本发明不限于此,上部保护层23b可包含多个开口251及开口252。第二保护层25的材料包括为非导电材料,包含有机材料或无机材料。其中有机材料包含su8、苯并环丁烯(bcb)、过氟环丁烷(pfcb)、环氧树脂(epoxy)、丙烯酸树脂(acrylic resin)、环烯烃聚合物(coc)、聚甲基丙烯酸甲酯(pmma)、聚对苯二甲酸乙二酯(pet)、聚碳酸酯(pc)、聚醚酰亚胺(polyetherimide)、聚酰亚胺(polyimide)或氟碳聚合物(fluorocarbon polymer)。无机材料包含硅胶(silicone)、玻璃(glass)或是介电材料,介电材料例如为氧化硅(sio

x

)、氮化硅(sin

x

)、氧氮化硅(sio

x

n

y

)、氧化铌(nb2o5)、氧化铪(hfo2)、氧化钛(tio

x

)、氟化镁(mgf2)、氧化铝(al2o3)等。在一实施例中,第二保护层25由一对或多对不同折射率的材料交互堆叠所形成,通过不同折射率材料的选择搭配其厚度设计,第二保护层25形成一反射结构,对特定波长范围的光线提供反射功能,例如为一分布式布拉格反射器。在一实施例中,类似于第一反射结构50,第二保护层25包含一组或多组材料叠层,与底层及/或上层。在一实施例中,具有分布式布拉格反射器的第二保护层25覆盖半导体叠层12位于走道区iso的侧壁,有利于走道区iso附近的光摘出,增进发光元件1的亮度。在一实施例中,具有分布式布拉格反射器的第二保护层25包含m对介电材料对,第一反射结构50包含n对介电材料对,其中m大于n。在一实施例中,第二保护层的厚度大于第一反射结构50的厚度。

92.在一实施例中,第二保护层25的厚度可为1μm至6μm。若第二保护层25的厚度小于1μm,较薄的厚度可能会使得第二保护层25的绝缘性和抗湿性变弱,降低发光元件1的可靠度。在一实施例中,第二保护层25的厚度大于上部保护层23b的厚度。

93.接着,参照图2h,在开口251及252内分别形成第一焊垫80a及第二焊垫80b。图2h仅绘示高台ms、第一电极20、第二电极30、第二保护层25及焊垫。第一焊垫80a与第一电极20相接,和第一半导体层121形成电连接。第二焊垫80b与第二电极30相接,和第二半导体层122形成电连接。第一焊垫80a及第二焊垫80b包含金属材料,例如铬(cr)、钛(ti)、钨(w)、金(au)、铝(al)、铟(in)、锡(sn)、镍(ni)、铂(pt)等金属或上述材料的叠层或合金。第一焊垫80a及第二焊垫80b可由单个层或是多个层所组成。例如,第一焊垫80a及第二焊垫80b可包括ti/au、ti/pt/au、cr/au、cr/pt/au、ni/au、ni/pt/au或cr/al/cr/ni/au。在后续切割(dicing)制作工艺完成并形成独立的发光元件1后,第一焊垫80a及第二焊垫80b以倒装的方式和一载板(图未示)上的电路接合,以达到和外部电子元件或外部电源的连接。在另一实施例中,第一焊垫80a及/或第二焊垫80b更可覆盖于第二保护层25上。在另一实施例中,第一焊垫80a及/或第二焊垫80b可避开暴露区28分布在半导体叠层12内的内部区域,以避免因高低差造成焊垫与半导体叠层12之间各层介面可能产生的剥离。第一焊垫80a及第二焊垫80b的表面有对应第一反射结构50的开口502形成的多个凹部(图未示),借由该些凹

部,在后续封装制作工艺中,可提升焊垫与载板之间的接合力,以提升制作工艺良率。

94.最后,沿着走道区iso,也就是各发光元件1的周围,将半导体晶片分割形成多个发光元件1。在一实施例中,如图3f所示,用激光27照射基板10的下表面,激光27聚焦于基板10内部,使基板10内部形成变质区(图未示),再自变质区沿着基板10的晶面形成裂痕将各发光元件1分割开来。但是本实施例的切割方式并不限于此,任何其他适用于将晶片切割成发光元件的方法,也可适用。

95.在一实施例中,图4a至图4c显示发光元件1制造方法中于图2a至图2e的步骤中沿a

‑

a”的部分截面图。图4a显示形成下部保护层23a、透明导电层18与第一反射结构50材料层于半导体叠层12上。其中,下部保护层23a在暴露区28上的厚度为t1。接着,参照图4b,以蚀刻的方式在第一反射结构50材料层中形成开口501及502,移除暴露区28上方的第一反射结构50材料层。其中,蚀刻包含干蚀刻,例如为感应耦合核等离子体(inductively coupled plasma,icp)蚀刻。在一实施例中,蚀刻包含干蚀刻搭配湿蚀刻。在蚀刻第一反射结构50材料层以形成开口502时,由于透明导电层18覆盖第二半导体层122,所以第二半导体层122不会因蚀刻而造成损伤。在一实施例中,透明导电层18可作为蚀刻停止层。在蚀刻第一反射结构50材料层以形成开口501以及移除暴露区28上方的第一反射结构50材料层时,由于下部保护层23a覆盖暴露区28,所以暴露区28底部的第一半导体层121不会因蚀刻而造成损伤。蚀刻第一反射结构50的步骤完成后,位于暴露区28的下部保护层23a具有厚度t1’。其中厚度t1’大于且厚度t1’小于厚度t1。通过下部保护层23a覆盖暴露区28以保护第一半导体层121,可以确保第一反射结构50的开口501可被完全打开,暴露区28上方不残留其材料层,又可确保第一半导体层121不受损伤。在另一实施中,并非所有暴露区28上的第一反射结构50材料层被移除,而是仅位于半导体叠层12内部区域的暴露区28上的第一反射结构50材料层被移除。

96.接着,参照图4c,依序形成第二反射结构36、上部保护层23b以及上部保护层的开口231、232及230(未绘示于图4c)。上部保护层23b与下部保护层23a构成第一保护层23。在暴露区28以及暴露区28附近的第二半导体层122上,上部保护层23b叠加在下部保护层23a,并与其相接。在形成开口230、231的同时,也移除了开口230、231正下方的下部保护层23a。也就是说,第一保护层23具有多个开口230间隔地设置于其周围,露出第一半导体层上表面121a,以及多个开口231设置于半导体叠层12内部的暴露区28,露出第一半导体层上表面121a。在暴露区28底部上方的第一保护层23的厚度(即,位于暴露区28的下部保护层23a的厚度t1’与上部保护层23b的厚度的总和)为t,在第二半导体层122上的第一保护层23的厚度(即,位于此处的下部保护层23a厚度与上部保护层23b厚度的总和)为t’,t小于t’。在一实施例中,t与t’的差值大于在另一实施例中,t与t’的差值大于在一实施例中,位于暴露区28的下部保护层23a的厚度t1’,小于位于第二半导体层122上表面的下部保护层23a的厚度t1。接着,依照前述图2f至图2h中的步骤,完成发光元件1。

97.图5a及图5b分别显示图2a至图2f的步骤完成后,沿b

‑

b’线段及c

‑

c’线段的截面图。参照图2f及图5a,第一电极20接触第一保护层23的开口230所暴露出的第一半导体层上表面121a。参照图2f及图5b,在没有开口230的地方,第一保护层23覆盖半导体叠层12周围的暴露区28,使第一电极20不接触第一半导体层上表面121a。如此一来,在半导体叠层12周围,第一电极20经由间隔设置的开口230,间隔地接触第一半导体层上表面121a,使电流在

半导体叠层12的周围均匀扩散。

98.图1a显示依本实施例制造方法所制作的发光元件1的上视图,图1b显示图1a中沿a

‑

a’线段的截面图,图1c显示图1b中的局部放大图。

99.参照图1a、图1b及图1c,发光元件1包含基板10、半导体叠层12位于基板上10、暴露区28包含位于半导体叠层12的周围环绕半导体叠层12的环绕区域以及分布在半导体叠层12内的内部区域,暴露出第一半导体层上表面121a、透明导电层18位于第二半导体层122上、第一反射结构50位于透明导电层18上,包含多个开口502暴露出透明导电层18、第二反射结构36位于第一反射结构50上,经由第一反射结构开口502与透明导电层18及第二半导体层122电连接。第二反射结构36与第一反射结构50形成一全方位反射镜(omnidirectional reflector,odr),增进光的反射及发光元件1的亮度。第一保护层23覆盖暴露区28,并延伸覆盖部分该第二半导体层122的上表面。第一保护层23包含下部保护层23a及上部半导体层23b。其中,下部保护层23a接触半导体叠层12,更详言之,下部保护层23a接触暴露区28侧壁及部分底部,上部保护层23b自暴露区28延伸至覆盖第二反射结构36,包含开口232暴露第二反射结构36。此外,第一保护层23包含开口231位于半导体叠层12内部区域的暴露区28,暴露出第一半导体层上表面121a。在一实施例中,第一保护层23更包含开口230位于半导体叠层12周围的暴露区28,暴露出第一半导体层上表面121a。在暴露区28底部上方的第一保护层23的厚度为t,在第二半导体层122上的第一保护层23的厚度为t’,t小于t’。在一实施例中,t与t’的差值大于在另一实施例中,t与t’的差值大于

100.第一电极20覆盖第一保护层23上,经由第一保护层开口231及230与第一半导体层121电连接。第二电极30与第一电极20相互分离,经由上部保护层开口232接触第二反射结构36,与第二半导体层122电连接。在一实施例中,第二电极30位于上部保护层开口232中。在另一实施例中,第二电极30位于上部保护层开口232中更延伸至上部保护层23b上。第二保护层25位于第一电极20与第二电极30上,包含开口251暴露第一电极20与开口252暴露第二电极30。如图1b所示,第二保护层25更覆盖半导体叠层12周围的侧壁及基板上表面10a。在一实施例中,第二保护层25包含分布式布拉格反射结构,可以增加光在半导体叠层12周围的反射,增进发光元件1亮度。第一焊垫80a位于开口251,并接触第一电极20。第二焊垫80b位于开口252,并接触第二电极30。

101.图1a显示本技术案一实施例发光元件2的上视图。图7a至图7i显示本技术案一实施例发光元件2制造方法中各阶段的上视图;图8a至图8g显示发光元件2制造方法中各阶段的截面图。发光元件2的制造方法详述如下。发光元件2的部分制作工艺及结构和发光元件1类似,类似的制作工艺及结构请参考发光元件1的说明及图式,不再赘述,后续将针对差异处详细说明。首先,参照图7a至图7b及图8a,其步骤如图2a至图2b及图3a说明所述,故于此不再赘述。

102.接着,参照图7c及图8b,实施一蚀刻停止层26形成步骤。图8b显示图7a至图7c的步骤完成后,沿a

‑

a’线段的截面图。图7c仅绘示高台ms、透明导电层18及蚀刻停止层26。先在透明导电层18的上表面形成蚀刻停止材料层(未图示),然后以显影蚀刻或掀离(lift

‑

off)等制作工艺,在透明导电层18的上表面形成蚀刻停止层26。蚀刻停止层26为多个彼此分离的岛状结构。

103.在一实施例中,蚀刻停止层26包含一金属,金属材料包含对发光元件2发出的光有高反射率的反射金属,例如银(ag)、金(au)、铝(al)、钛(ti)、铬(cr)、铜(cu)、镍(ni)、铂(pt)、钌(ru)或上述材料的合金或叠层。

104.在一实施例中,蚀刻停止层26包含屏障层(图未示)及接触层(图未示),接触层位于透明导电层18及屏障层之间,屏障层可以防止接触层的金属元素的迁移、扩散或氧化。接触层的材料包含对于半导体叠层12所发射的光线具有高反射率的金属材料,例如银(ag)、金(au)、铝(al)、钛(ti)、铬(cr)、铜(cu)、镍(ni)、铂(pt)、钌(ru)或上述材料的合金或叠层。屏障层的材料包括铬(cr)、铂(pt)、钛(ti)、钨(w)、锌(zn)或上述材料的合金或叠层。在一实施例中,当屏障层为金属叠层时,屏障层是由两层或两层以上的金属交替堆叠而形成,例如cr/pt,cr/ti,cr/tiw,cr/w,cr/zn,ti/pt,ti/w,ti/tiw,ti/zn,pt/tiw,pt/w,pt/zn,tiw/w,tiw/zn,或w/zn等。

105.接着,参照图7d及图8c,实施一第一反射结构50形成步骤。图8c显示图7a至图7d的步骤完成后,沿a

‑

a’线段的截面图。图7d仅绘示高台ms及第一反射结构50。先在第二半导体层122的上表面形成一反射材料层,然后以显影蚀刻等制作工艺,在反射材料层中形成相互分离的开孔501及502后以形成第一反射结构50。开孔501的位置对应于暴露区28及透明导电层开孔180,开孔502分布在第二半导体层122上,并暴露其下方的蚀刻停止层26。第一反射结构50的材料、叠层、厚度及形成方法等,如图6a至图6b说明所述,故于此不再赘述。

106.在一实施例中,蚀刻停止层26包含被开孔502暴露的中央部分及与第一反射结构50重叠的边缘部分,在显影蚀刻第一反射结构50时,可能会过蚀刻至蚀刻停止层26的中央部分,而使得蚀刻停止层26的中央部分的厚度小于蚀刻停止层26的边缘部分。

107.接着,参照图7e及图8d,实施一第二反射结构36形成步骤。图8d显示图7a至图7e的步骤完成后,沿a

‑

a’线段的截面图。图7e仅绘示高台ms及第二反射结构36。第二反射结构36对应形成于透明导电层18、蚀刻停止层26及第一反射结构50上,其经由第一反射结构50的开口502与蚀刻停止层26、透明导电层18及第二半导体层122电连接,且包含多个开口360对应于第一反射结构50的开口501,形成在暴露区28上。第二反射结构36包含一金属结构,可包含单一金属层或是由多个金属层所形成的叠层。在一实施例中,第二半导体层122于基板10上的投影面积与第二反射结构36于基板10上的投影面积的比例为100%~120%。通过调整第二反射结构36的面积使其接近于第二半导体层122于基板10上的投影面积,以提升第二反射结构36的反射面积,提高发光元件的光摘出效率。第二反射结构36的材料、叠层、厚度及形成方法等,如图2d及图3c说明所述,故于此不再赘述。

108.最后,参照图7f至图7i及图8e至图8g,其步骤如图2e至图2h及图3d至3f说明所述,故于此不再赘述。

109.在一实施例中,图9a至图9c显示发光元件2制造方法中于图7a至图7f的步骤中沿a

‑

a”的部分截面图。图9a显示形成下部保护层23a、透明导电层18、蚀刻停止层26与第一反射结构50于半导体叠层12上。其中,部分第一反射结构50材料层形成于位于暴露区28的下部保护层23a上,下部保护层23a在暴露区28上的厚度为t1。接着,参照图9b,以蚀刻的方式在第一反射结构50材料层形成开口501及502,并移除暴露区28上方的第一反射结构50材料层。其中,蚀刻包含干蚀刻,例如为感应耦合核等离子体(inductively coupled plasma,icp)蚀刻。在一实施例中,蚀刻包含干蚀刻搭配湿蚀刻。在蚀刻第一反射结构50材料层以形

成开口502时,由于蚀刻停止层26覆盖透明导电层18,所以透明导电层18不会因蚀刻而造成损伤。在蚀刻第一反射结构50材料层以形成开口501以及移除暴露区28上方的第一反射结构50时,由于下部保护层23a覆盖暴露区28,所以暴露区28底部的第一半导体层121不会因蚀刻而造成损伤。蚀刻第一反射结构50的步骤完成后,位于暴露区28的下部保护层23a具有厚度t1’。其中厚度t1’大于且厚度t1’小于厚度t1。通过下部保护层23a覆盖暴露区28以保护第一半导体层121,可以确保第一反射结构50的开口501可被完全打开,暴露区28上方不残留其材料层,又可确保第一半导体层121不受损伤。在另一实施中,并非所有暴露区28上的第一反射结构50材料层被移除,而是仅位于半导体叠层12内部区域的暴露区28上的第一反射结构50被移除。参照图9c,第一保护层23与其他层别的叠构关系及其位于不同位置的厚度差异,如图4c说明所述,故于此不再赘述。

110.图10a及图10b分别显示图7a至图7g的步骤完成后,图7g沿b

‑

b’线段及c

‑

c’线段的截面图。参照图7g及图10a至图10b,第一电极20、第一保护层23及半导体叠层12的叠层位置关系,如图2f及图5a至图5b说明所述,故于此不再赘述。

111.图1a显示依本实施例制造方法所制作的发光元件2的上视图,图1d显示图1a中沿a

‑

a’线段的截面图,图1e显示图1d中的局部放大图。

112.参照图1a、图1d及图1e,发光元件2包含基板10、半导体叠层12位于基板上10、暴露区28包含位于半导体叠层12的周围环绕半导体叠层12的环绕区域以及分布在半导体叠层12内的内部区域,暴露出第一半导体层上表面121a、透明导电层18位于第二半导体层122上、蚀刻停止层26位于透明导电层18上,包含多个彼此分离的岛状结构、第一反射结构50位于透明导电层18及蚀刻停止层26上,包含多个开口502暴露出蚀刻停止层26、第二反射结构36位于第一反射结构50上,经由第一反射结构开口502与蚀刻停止层26、透明导电层18及第二半导体层122电连接。第二反射结构36与第一反射结构50形成一全方位反射镜(omnidirectional reflector,odr),增进光的反射及发光元件2的亮度。然而,第一保护层23与其他层别的叠构关系及于不同位置的厚度关系,以及第一电极20、第二电极30、第一焊垫80a及第二焊垫80b与其他层别的叠构关系,已如图1b及图1c说明所述,故于此不再赘述。

113.图11为依本发明一实施例的发光装置3的示意图。将前述实施例中的发光元件1、2以倒装芯片的形式安装于载板51的第一垫片511、第二垫片512上。第一垫片511、第二垫片512之间通过一包含绝缘材料的绝缘部53做电性绝缘。倒装芯片安装是将与焊垫形成面相对的基板10侧向上,作为主要的出光面。为了增加发光装置3的光摘出效率,可于发光元件1、2的周围设置一反射结构54。

114.图12为依本发明一实施例的发光装置4的示意图。发光装置4为包含一灯罩602、一反射镜604、一发光模块610、一灯座612、一散热片614、一连接部616以及一电连接元件618。发光模块610包含一承载部606,以及多个发光单元608位于承载部606上,其中多个发光单元608可为前述实施例中的发光元件1、2或发光装置3。

115.上述实施例仅为例示性说明本技术案的原理及其功效,而非用于限制本技术案。任何本技术案所属技术领域中具有通常知识者均可在不违背本技术案的技术原理及精神的情况下,对上述实施例进行修改及变化。举凡依本技术案权利要求所述的形状、构造、特征及精神所为的均等变化与修饰,均应包括于本技术案的权利要求内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1