绝缘体上覆硅上的射频开关装置及其制造方法与流程

1.本发明关于一种半导体装置。更明确地说,本发明关于绝缘体上覆硅(soi)上的射频(rf)开关装置及其制造方法。

背景技术:

2.晶体管常做为开关和放大器的元件。硅基金属氧化物半导体场效晶体管(mosfet)科技数十年来已经精进而提高高频性能并降低成本。相较于旧的双极晶体管装置,硅mosfet因为它的相对容易制造和微处理器的高需求所带来的大规模集积以及电源效率而特别有吸引力。改变用于微处理器的传统低功率mosfet以用于高功率和高频应用。可以使用改进的掺杂分布和装置结构以允许在数十伏或更高的电压下运行。经由改进的载流子移动性,可以使用诸如绝缘体上覆硅技术和iii

‑

v半导体技术之类的改性材料系统来实现更高的功率运行和更高的最大工作频率。

技术实现要素:

3.本段摘录并汇编本发明的某些特性;其他特性将在后续段落中揭露。其旨在涵盖申请专利范围的精神和范畴内所包括的各种修改和类似配置。

4.以下呈现本揭露书的一个或多个观点的简化概要,以便提供对这些观点的基本理解。本概要不是揭露的所有特性的广泛概述,既不旨在标识所有观点的关键元件,也不是要描绘本公开的任何或所有观点的范围。其唯一目的是以简化的形式呈现揭露书的一个或多个观点的一些概念,做为稍后介绍的详细说明的序言。

5.现有的半导体晶体管制程可在传统栅极结构旁形成横向延伸。可改变这些横向栅极延伸下方的介电厚度,以调节装置性能并实现更高的截止频率,而不会影响高操作电压下的抗电压能力。这些延伸的电极尺寸不受光刻解析度和对准能力的限制,并且与传统制程相容,以便于与其他装置集积。横向延伸和介电隔片可用于形成自动对正源极、漏极、通道区。可以在狭窄的栅极延伸下形成狭窄的高度掺杂通道,以改善工作频率而不会显著增加元件电容。

6.一方面,本发明提供绝缘体上覆硅(soi)上的射频(rf)开关装置,包含:基板,在基板顶表面延伸有半导体区,半导体区的第一和第二端沿着平行于基板顶表面的方向彼此相对;第一介电层,形成于基板半导体区上方,具有第一厚度;第一栅极,在第一和第二端之间位于半导体区上方的第一介电层上;第二介电层,具有第二厚度,形成于原第一介电层邻接第一栅极并接近第一端,其中第二介电层独立形成于第一介电层后;及第二栅极,位于第二介电层上方并与第一栅极电性短路接触,其中相对于第一栅极的第二栅极侧壁显著地垂直于基板顶表面。

7.优选地,第二厚度不等于第一厚度。

8.优选地,射频开关装置进一步包含第一隔片,形成于基板半导体区上方并邻接第二栅极。

9.优选地,射频开关装置进一步包含形成于第一介电层和第二介电层上的导电层。

10.优选地,射频开关装置进一步包含位于半导体区上方的第三栅极邻接第一栅极并接近第二端,与半导体区隔着从第一端延伸到第二端的第二介电层。

11.优选地,相对于第一栅极的第三栅极侧壁显著地垂直于基板顶表面。

12.优选地,射频开关装置进一步包含第二隔片,形成基板半导体区上方并邻接第三栅极。

13.优选地,掺杂源极在第一端形成于半导体区内;掺杂漏极在第二端形成于半导体区内;掺杂通道形成于掺杂源极与掺杂漏极之间,掺杂通道的多数载流子类型与掺杂源极和掺杂漏极的多数载流子类型相反。

14.优选地,射频开关装置进一步包含形成于第一栅极和第二栅极上的导电材料,以将第一栅极和第二栅极电耦合。

15.另一方面,本发明提供制造上述射频开关装置的方法。该方法包含以下步骤:提供基板,在基板顶表面延伸有半导体区,半导体区的第一和第二端沿着平行于基板顶表面的方向彼此相对;在半导体区上方形成第一介电层;在第一和第二端之间将第一栅极设置于半导体区上方;在第一介电层上形成具有第二厚度的第二介电层,在第一栅极下方邻接第一介电层并接近第一端;及在第二介电层上方设置第二栅极。

16.优选地,该方法进一步包含以下步骤:植入第一掺杂剂以在基板顶表面下方延伸的半导体区内形成第一掺杂区块,来形成掺杂通道;植入第二掺杂剂,在第一端的半导体区内形成掺杂源极;及植入第二掺杂剂,在第二端的半导体区内形成掺杂漏极,其中掺杂通道形成于掺杂源极与掺杂漏极之间,掺杂通道的多数载流子类型与掺杂源极和掺杂漏极的多数载流子类型相反。

17.优选地,该方法进一步包含以下步骤:在基板半导体区上方形成第一隔片邻接第二栅极。

18.优选地,第二栅极由以下步骤形成:在第一栅极上方形成导电层;及用各向异性反应离子蚀刻(rie)制程对导电层进行选择性蚀刻,在第二介电层上留下一部分的导电层以形成第二栅极,第二栅极的垂直侧壁显著地垂直于基板顶表面。

19.优选地,导电层是在形成于第一栅极之上后,进行选择性蚀刻产生第二电栅极,并且不须使用光罩决定第二栅极尺寸;第二栅极宽度由导电层的形成厚度来界定。

20.优选地,对导电层光刻包括以下步骤:在导电层上形成保护介电材料层,具有保护层厚度;及使用各向异性反应离子蚀刻制程来蚀刻保护介电材料层;其中各向异性反应离子蚀刻制程优先沿着垂直于基板顶表面的方向蚀刻保护介电材料层和导电层;其中各向异性反应离子蚀刻制程除去保护介电材料层的蚀刻率大于导电层的蚀刻率;其中整合规划保护层厚度和各向异性反应离子蚀刻制程,使得残余保护介电材料附在第二栅极的垂直侧壁,正对第一栅极而最远离第一栅极;其中整合规划保护层厚度和各向异性反应离子蚀刻制程,使得残余保护介电材料附在第三栅极的垂直侧壁,正对第一栅极而最远离第一栅极。

附图说明

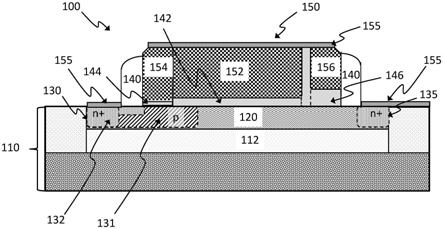

21.图1是依据本文所揭露之实施例的示例装置的截面示意图。

22.图2是依据本文所揭露之另一实施例的示例装置的截面示意图。

23.图3a

‑

3f是截面示意图,描绘依据本文所揭露之实施例之图1的装置在不同制造阶段。

24.图4是依据一些实施例的示例晶体管制程的流程图。

25.图5a是依据本文所揭露之实施例的另一示例装置的截面示意图。

26.图5b是截面示意图,显示依据本文所揭露之实施例的图5a的装置制程的元件。

27.图5c是依据本文所揭露之实施例的另一示例装置的截面示意图。

具体实施方式

28.现在参照以下实施例来更详细说明本发明。

29.下面结合附图的详细说明旨在做为各种配置的描述,并不意图代表可以实践本文描述的概念的唯一组态。详细说明包含特定细节是为了提供对各种概念的透彻理解。然而,对于本领域技术人员而言显而易见的是,可以在没有这些特定细节的情况下实践这些概念。在某些情况下,以方块图形式显示众所周知的结构和元件,以避免掩盖了此种概念。

30.在本文中,“示例性”一词用于表示“做为示例、实例或说明”。本文所描述为“示例性”的任何实施方式或观点不必然要解释为比其他观点更优选或有利。同样地,“观点”一词并不要求本文所有观点都包含所讨论的特性、优点或操作模式。“耦合”一词在本文中用于指两个物体之间的直接或间接耦合。例如,如果物体a实体接触物体b,且物体b接触物体c,则即使彼此没有直接实体接触,物体a和c仍然可以视为彼此耦合。例如,即使第一物体不与第二物体直接实体接触,第一物体也可以耦合到第二物体。“电路”一词广泛使用,旨在包含电气装置和导体的硬体以及资讯和指令的软体,当连接和配置的硬体时,能够实现本文中描述的功能,而不受限于电子电路的类型,当由处理器所执行的软体时,能够实现本文中描述的功能。

31.应了解的是,图式是为了说明的目的,各种元件未依照比例以便于明了。方向性用语如“顶”、“底”、“侧”、“上”、“上方”、“下方”及类似用语表示图的方位,除非特别指明,否则不表示任何特定方位。

32.传统硅和绝缘体上覆硅装置虽因低成本以及容易与诸如传统微处理器的其他硅基半导体装置集积而吸引人,但这些装置有缺点。详言之,传统硅装置的最大切换速度有限,输出功率不佳。改变诸如栅极介电材料和厚度的结构细节可调整硅mosfet的工作频率。然而,提高工作频率之诸如打薄栅极介电层的修改通常导致击穿电压下降及其他诸如栅极诱发漏极漏电(gidl)增大的不良特征。

33.包含iii

‑

v半导体装置(例如gaas、gan等等)的复合半导体装置可在rf放大器应用中达成较高工作频率和较佳输出功率(亦即,较大电流密度)。然而,复合半导体制造比硅基半导体制造贵。再者,复合半导体装置不易与无所不在的硅装置集积。虽然绝缘体上覆硅(soi)技术可经由降低的基板电容和其他因素来改善性能,但soi为基础的射频装置仍要在工作频率、击穿电压、漏电之间拿捏。

34.mosfet的重要性能特征包含最大工作频率(以单位增益截止频率表示)、各种击穿电压(例如,栅极到漏极击穿、栅极到源极击穿、栅极到阱击穿、漏极到源极击穿)、导通电阻、寄生电容等等。对做为放大器的mosfet,衍生的性能特征包含电压增益与工作频宽的乘积(“增益

‑

频宽乘积”)和击穿电压与截止频率的乘积(“bv

‑

ft乘积”)。通常,高增益伴随的

代价是减少工作频宽,反之亦然。同样地,高击穿电压通常伴随的代价是单位增益截止频率降低,反之亦然。除了其他参数,掺杂调控和元件结构也影响击穿电压。装置击穿的另一成因是栅极介电层。薄栅极介电层可降低导通电阻,但更容易降低工作耐电压。因此,传统mosfet中,无法打薄栅极介电层来改善装置性能而不牺牲在高工作电压防止击穿。诸如栅极诱发漏极漏电(gidl)的其他性能特征也有隐忧。

35.传统mosfet结构中,增大的漏极电压会使形成在漏极与通道区之间的接面的耗尽区延伸到栅极之下,导致有效通道长度缩短,输出电阻下降,做为放大器时增益退化。因此,最好将耗尽区伸入漏极侧飘移区,借以增加击穿电压并增加输出电阻,当mosfet做为放大器时导致增益较高。

36.传统硅mosfet中,降低通道长度可增加切换速度。为避免漏极诱发势垒降低(dibl),必须增加通道掺杂,而会提高装置的临限电压(vt)。当通道掺杂增加时,栅极介电层必须变薄以避免提高vt。然而,打薄栅极介电层通常导致诸如击穿电压下降和gidl增加的不良效应。

37.本文所揭露的装置和方法可增加有效通道掺杂而没有降低击穿电压的一般副作用,令硅基rf放大器、开关、其他装置可实现高于传统硅装置(包含soi装置)的工作频率,而不牺牲在高电压的无击穿运行和其他重要特征。例如,本文所揭露的装置和方法可使射频开关降低杂散谐波产生。mosfet为基础的射频开关中的谐波是因栅极诱发漏极漏电(gidl)所引起。gidl因能带之间的电荷穿隧形成,故随增加的电压而指数性增加。以下进一步说明依据本文所揭露之实施例的具有低gidl的硅基装置和其制造方法。此种装置成本低,装置尺寸小,容易与用于硅半导体科技的无所不在的无线装置集积。

38.以下参照示例装置和其制造方法来讨论本文的一些观点。本文所揭露的某些示例装置和方法虽以绝缘体上覆硅技术来讨论,但应了解所揭露的改良可应用于一般硅晶圆及其他半导体平台。

39.图1是示例绝缘体上覆硅装置100的截面示意图,适于做为射频(rf)放大器。装置100是制造在soi基板110上的mosfet,具有掩埋氧化物112,其上有n型硅主体120。为了说明,示例装置100和其他装置显示为n通道晶体管,具有n型源极和漏极(例如源极130和漏极135)以及p型通道(例如,形成通道的p型阱131)。然而,本文所揭露的方法同样可用来制造p通道晶体管,将n型掺杂取代p型掺杂,反之亦然。

40.高度掺杂n型(n+)阱132形成于p型掺杂p型阱131内可形成源极,与n型主体120一起形成通道。高度掺杂n型(n+)阱形成漏极135。装置100的栅极是栅极150,包含栅极152、154、156,各自以装置操作区分隔一个以上的介电层而无电接触。栅极152、154、156可由合适导电性和其他性质的材料组合来形成。一些实施例中,栅极152、154、156可由高度掺杂(包含简并掺杂)多晶硅形成。注意操作区与栅极150之间的介电层厚度在栅极152、154、156之下各不相同。第一介电材料140和第二介电材料144可为任何合适材料,包含但不限于二氧化硅、氮化硅、氧化铈、氧化铪等等)。第一介电材料140可包含在不同时间形成的部分(例如,如图3a的虚线和图3f的隔片343所示)。

41.如所示(以下并配合图3a

‑

e进一步说明),栅极152、156通过第一介电材料140与操作区分离,而最接近源极130的栅极154通过较薄的第二介电材料144与p型阱131分离。合适导电材料155(例如,任何合适金属或金属硅化物)做为栅极150与源极130和漏极135的顶接

点。导电材料155的例子诸如但不限于以钛或钴硅扩散硅化作用制程所形成的硅化物。在硅化制程前,若实施硅的磊晶生长以关闭栅极之间的间隙,具有诸如具金属扩散性质的镍元素之可做金属硅化材料。

42.一些实施例中,栅极152、154、156可以有显著地垂直的侧壁,与操作区表面形成约90

°

的角度,容许栅极152、154、156在装置100制造时做为掺杂剂扩散的自对准光罩(例如,以下配合图3a

‑

e来进一步说明)。

43.相较于传统横向扩散金属氧化物半导体(ldmos)装置,区146在栅极156下的第一介电材料140的厚度大于第二介电材料144,可降低来自漏极135的有效电场而提高击穿电压。同时,第二介电材料144相当低的厚度可以有高增益,而不牺牲装置100的耐高电压能力。可依照应用需求选择示例装置100的结构尺寸以得到所要的性能规格。注意,使用本文所揭露的方法在类似于示例装置100的装置中可达成至少150ghz

‑

volts的击穿电压截止频率乘积。应了解区146在栅极156下的介电材料140的厚度、介电材料144的厚度、区142在栅极152下的介电材料140的厚度可独立调整以配合各种应用。

44.例如,使用相当薄的介电材料144可达成高跨导。同时,介电材料140在区146相对于介电材料140在区142(连同栅极152的横向尺寸)选择较大厚度可用于装置接近漏极135改善高电压承受。通常,当介电材料140是二氧化硅时,介电材料140在区146有20nm厚度足以使示例装置100承受~20v的施加漏极

‑

栅极电压。进一步增加介电层140在区146于栅极156下的厚度,也可以有在较高电压的无击穿运行。

45.示例装置100是修改的n通道横向扩散金属氧化物半导体(ldmos)晶体管。当装置100在主动模式时,电流可在施加的漏极

‑

源极偏压下从源极130流到漏极135。由于电流由电子带动,故考虑从源极130流到漏极135的电子流便能了解装置特征。最接近源极130的栅极154与p型通道阱131隔着薄的第二介电材料144,在区142和区146于栅极152、156下可分别使第一介电材料140的厚度更薄。以轻度n掺杂主体120分隔通道阱131与漏极135可进一步改善击穿电压,当装置运行时,导致电子可流到漏极阱135的耗尽区变宽。

46.一些实施例中,薄的第二介电材料144为厚度或更小。最接近源极130的栅极154与通道阱131之间的高有效电容可导致在该处有较高载流子浓度,相较于具有均匀栅极介电层的传统ldmosfet有较低导通电阻。虽然打薄传统装置的栅极介电层同样可降低导通电阻,但这会导致不良的漏流(因为gidl)增加及降低耐高压能力。

47.使用示例参数可进一步了解示例装置100的特性。例如,示例装置100的击穿电压取决于在区146下接近漏极的耗尽区。若介电材料146是厚的二氧化硅,且无轻度掺杂漏极(ldd)植入物用于漏极135,则介电层击穿电压可预期为至少20v,容许在15v峰值的安全运行。飘移区形成在栅极152下。在vd>vg的作用模式运行中,飘移区在表面附近形成载流子耗尽区,载流子在远离表面的深度流动。结果,在飘移区于栅极152下的有效栅极介电层厚度相当于介电材料140在该区的厚度加上耗尽表面区的深度(以合适介电常数修正)。结果,介电材料140在区142于栅极152下的厚度可变薄以改进通道的线性模式通态电导。此外,形成在主体120与p阱131之间的接面有栅极履盖,借以提高击穿电压以及n型源极132、p型阱131、n型主体120(连同在漏极135的n型阱)所形成之寄生npn双极晶体管的整体bvceo,bvceo部分限制示例装置100的高电压掌控能力。p阱131的掺杂可在1.0e18 cm

‑

3的范围,因使用薄介电材料144而远高于一般高电压ldmos装置。p阱131的高度掺杂降低寄生bjt的注

入比和电流增益,因此改进示例装置100的击穿电压。

48.可选择示例装置100的尺寸,使得从漏极135的边缘至p阱131的边缘的总飘移长度大于主体120的厚度四倍,借以几乎消除漏极诱发势垒降低(dibl)效应。例如,主体区120的厚度可选为界定飘移区的长度为~200nm。最接近漏极135的栅极152的边缘与漏极135的横向距离可选为100nm或任何其他合适值。

49.例如,类似示例装置100的装置可做为击穿电压在5v与20v之间的rf放大器。此例中的主体120的厚度为50nm,其下为400nm的掩埋氧化物。第一栅极152的长度宜在~200与1000nm之间,决定装置的击穿电压。

50.可选择在中间栅极152下的介电材料142的厚度以使夹断开始时的最佳漏极电流,后者部份决定装置100的输出功率。在第二栅极154下的薄介电材料144的厚度选择薄的,在高偏压被遮罩时发挥最佳性能。以装置运行时所须承受的漏极电压选择在第三栅极156上的区146中的介电材料厚度。

51.对于某些应用,栅极152和156的累积宽度最好是主体120的~4x厚度以抑制dibl效应。可调整栅极154的宽度和其下的掺杂,以设定临限电压并调整导通电阻。使用较大的栅极156的厚度和其下的栅极介电层厚度可进一步增加装置100的高耐压。

52.图2示例绝缘体上覆硅装置200(修改的n通道mosfet)的截面示意图,适于做为射频开关。虽然装置200类似装置100,且可使用许多相同制程步骤来制造,但最好做为开关而非放大器。为此,在栅极254下不需要超薄栅极介电层(例如,图1的第二介电材料144)。因此,在示例装置200,栅极250分成中间栅极252和二个对称延伸栅极254、256。栅极252、254、256可由合适导电性和其他性质的材料组合来形成。一些实施例中,栅极252、254、256可由高度掺杂(包含简并掺杂)多晶硅形成。如下所述,介电材料240在中间栅极252与通道220之间产生的间隙小于栅极254、256与通道220之间。栅极252、254、256可由导电材料255(例如,导电材料155)电耦合(例如,彼此短路),可为任何合适金属或金属硅化物,也可电接触源极230和漏极235。

53.例如,类似示例装置200的装置可具有5v与20v之间的击穿电压,设计rf天线协调器的理想元件。此例中的主体220的厚度为50nm,其下有400nm的掩埋氧化物。第一栅极252的长度在~50与1000nm之间对某些应用较好。分别选择在第二和第三栅极254、256下的区244、246中的介电材料厚度,以承受装置运行时所施加的漏极电压并降低归因于gidl的谐波,因此厚度高于252。为此,介电层240在区244、246的厚度为20nm很适合。对于某些应用,栅极250的累积宽度最好是主体220的~4x厚度以降低dibl效应。

54.合适栅极(例如,栅极252、254、256)可为~200nm厚的多晶硅,栅极254、256与栅极252间隔20nm。

55.在装置200,中间栅极252与延伸栅极254、256之间的间隙预期会增加导通电阻。然而,当传统fet过驱动(亦即,vg>>vth)时,载流子迁移率降低。当装置200过驱动时,可选择栅极254、256下的介电层厚度,使得载流子迁移率在区244、246下保持正常,相较于没有延伸栅极254、256的传统晶体管,低gidl电流导致低谐波失真和高于传统装置的击穿电压(导通电阻温和增加~10

–

15%)。

56.图3a

‑

3f是在示例制程中的选择点之示例装置300的截面示意图,显示适于制造示例装置300的步骤(例如,图1的示例装置)。图3a

‑

3f虽显示做为rf放大器之装置的制造,但

应了解,只要有合适修改,本文所揭露的方法可应用于其他装置和其他半导体技术(例如,非soi硅基装置、复合半导体装置等等),如下所述。

57.如图3a,提供半导体基板310。为了说明,基板310显示为soi晶圆,具有掩埋氧化物层312和其上的硅主体320。如所示,半导体基板310可设有形成于区主体320上方的栅极352,将变成栅极结构350的一部分(例如,图1的栅极150)。如所示,栅极352被介电材料340包含。在一些实施例,基板310可只设有下介电材料340a,形成目前第一介电材料340的下部(由虚线代表),在此情形,可稍后形成上介电材料340b。基板310显示为部分耗尽的soi晶圆。然而,在一些实施例,可使用完全耗尽的soi晶圆。

58.在一些实施例,基板310没有第一介电材料340也没有栅极352。在此种实施例,方法可包含形成第一介电材料340的下部340a及栅极352。第一介电材料340可为任何合适材料,包含但不限于各种氧化物和氮化物(例如,二氧化硅、氧化铪、氧化铈、氮化硅、氮化硼等等)及其组合。

59.如图3c,第一介电材料340可经由光刻和蚀刻、或任何其他制程的合适组合来构图,在基板310的顶表面322上靠近栅极352露出区325。在一些实施例,第一介电材料340是二氧化硅,可在蚀刻使用氢氟酸(hf)溶液的光刻胶显影后所露出的区域来构图。如所示,栅极352可做为掺杂剂植入362的硬遮罩。如所示,掺杂剂植入362可在轻度n掺杂的主体320内产生p型阱331。此区块一部分可形成完整装置300的源极阱330(以下配合图3f进一步说明)。p型阱331的尺寸或至少一部分可因此自我对正最接近栅极352的边缘。

60.因硅材料的载流子迁移率之故,需要缩小元件尺寸以产生高速rf性能。现有已知技术是先形成不同厚度栅极介电氧化物,接着经由同一个对准标的在栅极介电氧化物上对准栅极结构,使得装置难以缩小。所提的方法在栅极152上进行对正如图3c,有效解除对准误差导致小尺寸元件的参数变动。

61.如图3c,薄介电材料344可形成于区325上。在一些实施例,薄介电材料344可为使用热氧化物制程所形成的二氧化硅。可选择第二介电材料344的厚度以达成装置300所要的性能特征。详言之,由于介电材料344在完整晶体管的栅极354与主体320之间在区325形成栅极介电层(如下所述),该厚度至少部份决定装置300的导通电阻和其截止频率。如所示,可使介电材料340的厚度在区346比区344大。

62.在一些实施例,想使厚度尽量小而不造成短路。可调整装置性能以配合不同特征。例如,介电材料愈薄,驱动电流愈大。同样地,随着介电材料344的厚度增加,驱动电流减小。可依据特定应用所要的特征来选择任何合适厚度的各种介电材料。

63.对于大部分应用,厚的氧化物层可用于介电材料344。包含高k介电层的其他材料及任何其他合适介电层可用来进一步调整所要的性能特征。

64.如图3d,导电层353可位于图3c的结构上,形成图3e的结构。导电层353可为任何合适材料,包含金属和/或高度掺杂的多晶硅。注意,可选择导电层353的厚度,使得可使用反应离子蚀刻来构图导电层353,而不需要独立的光刻步骤。通过选择合适反应离子蚀刻制程(例如,在低压的反应离子蚀刻),导电层353在栅极352和区325上的部份可除去,而留下层353沿着栅极352之侧壁355的部分,并使构图的介电材料340的侧壁357完整,借以形成延伸栅极354、356(例如,图1的栅极154、156)。此种非光刻制程可用来产生细小纳米等级结构,而不需要额外遮罩和可做纳米(或次纳米)光罩对正之设备的花费。清除353层残余所需的

过蚀刻会造成延伸栅极354、356高度低于中间栅极352。

65.在一些实施例,为帮助图3d之结构的后续构图以形成图3e和3f的结构,薄氧化物层(例如,氧化物层359)或其他层可沉积在导电层353上如图3d。当进行合适各向异性选择蚀刻制程(例如,在hbr:cl电浆的低压蚀刻)最好在垂直于基板表面的方向除去材料时,此氧化物涂层保护导电层353的侧壁免于蚀刻,导致成各个延伸栅极354、356的显著地垂直侧壁355a、b及357a、b如图3e

‑

3f。保护氧化物涂层确保垂直栅极354、356有一致尺寸,不会与区块产生中的源极或漏极掺杂的阱由金属硅化物短路。

66.本文的说明是为了显示实施例的关键特性,可省略各种已知处理步骤。例如,在一些实施例中多晶硅做为栅极材料,衬里氧化物可沉积或热生长成为多晶硅退火制程的一部分,驱动重度n型掺杂剂扩散到多晶硅。此种衬里氧化物层可为~厚,可在蚀刻多晶硅以构图栅极前由反应离子蚀刻除去。这可控制关键尺寸(“cd控制”)。随后形成介电隔片343防止源极和漏极在硅化物形成时与各个栅极354、356短路。

67.如图3f,介电隔片343可邻接延伸的栅极354、356。介电隔片343可做为掺杂剂植入制程364的硬遮罩,可用来形成源极和漏极阱。如所示,源极和漏极阱是掺杂的n+。一或多个热退火步骤可进一步界定源极阱332和漏极阱335的范围、以及源极阱332和通道阱331的界面、漏极阱335和主体320的界面。在一些实施例中栅极354、356是多晶硅,一或多个退火步骤也可用于使掺杂剂扩散到栅极354、356内,确保具有充分导电性。在一些实施例,热退火步骤可用来修复栅极354、356的反应离子蚀刻所引发的蚀刻损害,额外退火进一步使掺杂制程364和/或掺杂制程362所导入的掺杂剂扩散。在一些实施例,源极、漏极、通道的掺杂轮廓在通道阱331与主体320之间的界面逐渐扩散,借以降低陡峭掺杂分布造成的高电场。

68.未明示的额外传统步骤可包含横向掺杂剂扩散以形成掺杂的源极和漏极区如图3f,隔片343的沉积和构图,以及可由硅化物、金属、或任何其他合适材料所形成之源极和漏极接点的沉积。要了解若使用完全耗尽的soi,则掺杂区尺寸会改变;例如,p型阱331和形成漏极335的n型阱可在掩埋氧化物312的界面延伸到主体320的底部。

69.图4显示制造晶体管(例如,示例装置100)的示例制程400的流程图。如下述,在本文的范围内可在特定实施中省略一些或所有显示的特性,一些显示的特性并非所有实施例都需要。示例制程400具有步骤402、404、406、408、410、412、414、416。这些步骤可以是人操作半导体制造设备、自动控制系统操作此种设备、或其任何组合,合称为“操作者”。一些示例中,制程400可由执行下述功能或演算法的任何合适装置或手段来进行。一些示例中,步骤406和408的顺序可颠倒以容许穿过氧化物的植入。

70.在步骤402,操作者提供基板,在基板顶表面下有半导体区(例如,图3的主体320)。基板沿着平行于基板顶表面的方向有彼此相对的第一和第二端(例如,图3a

‑

3f的源极330和漏极335);位于半导体区上的第一介电材料(例如,图3的下介电材料340a);位于半导体区上在第一和第二端之间的第一栅极(例如,图3的栅极352)。

71.在步骤404,操作者在第一栅极和基板上形成第二介电材料(例如,图3的上介电材料340b)。第二介电材料可为二氧化硅、氮化硅、或任何其他合适介电材料或其组合,可由溅射、物理蒸气沉积、化学蒸气沉积、或任何其他合适方法来沉积。

72.在步骤406,操作者构图第一和第二介电材料,在邻接至少第一栅极第一侧壁且接近第一端露出基板顶表面的第一区(例如,区电极325如图3c)。在一些实施例,构图第二介

电材料包含先构图光阻以产生蚀刻遮罩。可使用任何合适湿或干蚀刻制程来除去第二介电材料的露出区及第一区内的第一介电材料。例如,可使用氢氟酸溶液除去二氧化硅。

73.在步骤408,操作者将第一掺杂剂(例如,图3c的掺杂剂362)施加于基板,在基板第一区块内形成第一掺杂的区块对应于第一区。因基板在第一区内露出,故第一掺杂区块的宽度至少部分由第一区宽度决定。第一掺杂剂可使用任何合适制程来施加,包含掺杂剂从涂层扩散或离子植入。若晶体管是n通道晶体管,则选择第一掺杂剂以产生p掺杂区。若晶体管是p通道晶体管,则选择第一掺杂剂以产生n掺杂区。

74.在步骤410,操作者在第一区上形成第三介电材料(例如,图3c的薄介电材料344),其厚度小于在第一栅极与基板顶表面之间的第一介电材料厚度。第三介电材料可为二氧化硅、氮化硅、或任何其他合适介电材料或其组合,可由溅射、物理蒸气沉积、化学蒸气沉积、或任何其他合适方法来沉积。在一些实施例,在第一区的基板顶表面使用热氧化可在第一区上形成第三介电材料。

75.在步骤412,操作者构图导电层来形成第二栅极(例如,图3d的导电层353,构图如图3e以形成两个延伸栅极354和356)。导电层可由任何合适制程(例如,化学蒸气沉积、溅射等等)来沉积。第二栅极接近半导体区第一端,邻接至少第一栅极的第一侧壁,位于第二介电材料和第一掺杂区块的至少一部份上。在一些实施例,可构图第二栅极而不需要进行光刻步骤。例如,可经由诸如具高度各向异性的反应离子蚀刻(rie)制程来蚀刻导电层,有效除去导电层区块,同时导电层沿着第一栅极侧壁的部分仍完整。选择导电层起始厚度可控制第二栅极宽度。

76.第二栅极可窄小到至少数十纳米的等级,而不需要进行高解析度光刻和高精确度光罩对正。此步骤可包含沿着第一栅极相对侧壁(并接近半导体区第二端)形成与第二栅极相对的第三栅极。在对应于第三栅极的区域不需除去第二介电材料。结果,第三栅极可与半导体区隔着介电材料,其厚度大于第一栅极和/或第二栅极(例如见图1)。在第三栅极下有厚介电层的重大好处是降低在整体栅极结构与漏极之间的电容(“cgd”)。降低的cgd有较高功率增益和较高最大工作频率(增益大于或等于单位功率增益时的最高频率所测量的)。延伸的栅极结构有高速性能,而没有传统窄栅极结构的高栅极电阻rg所造成的功率增益退化。

77.在步骤414,操作者构图第四介电材料来形成第一介电隔片邻接第二栅极(例如,其中一个介电隔片343邻接第二栅极354如图3f)。第四介电材料可为前述的任何合适介电材料,可使用任何合适制程来沉积和构图,包含配合步骤412的上述反应离子蚀刻。第一隔片可做为施加掺杂剂的硬遮罩,用来在第一掺杂区块内形成源极阱。于是,在步骤416,操作者将第二掺杂剂施加于基板,在基板第一掺杂区块内形成第二掺杂区块(例如,图3f的n+阱332)。第二掺杂区块的宽度至少由第一区宽度、第二栅极位置、第一隔片宽度决定(参见,例如图3f的说明)。步骤414也可包含形成第二隔片邻接实施例的第三栅极,包含形成第三栅极如上述。此种实施例中,第二隔片可做为遮罩,第二掺杂剂透过它形成可做为晶体管漏极的第三掺杂区(例如,图3f的第三栅极356、隔片343、漏极335)。选择第二掺杂剂引入与第一掺杂剂相反的多数载流子类型,使得源极的掺杂与形成于第二栅极下的通道相反。

78.另一方面,本文所揭露的方法不限于soi为基础的装置,例如,如图5a~5c所示。图5b显示适用于低耗损电力管理装置的示例装置500,其特性类似于图1的示例装置100,使用

常规半导体基板510来制造。soi版本也可用于缩小元件隔离空间和提高切换速度以降低外部被动元件尺寸。源极阱由形成于p掺杂阱532内的n+掺杂阱533所形成。p+掺杂阱534对p掺杂阱532形成欧姆接触且连接n掺杂源极阱533。延伸的栅极554宽度可大于0.1um。

79.n型阱533、p型阱532、n型基板510形成寄生npn双极接面晶体管。在高电压运行下跨过形成于p型主体531与n型主体510之间之pn接面的漏电流流向p阱接点534,成为寄生bjt的基极电流。具有单一厚栅极介电层的传统装置中,p阱532的掺杂通常约为5.0e16 cm

‑

3以达成可接受的栅极临限电压。然而,高p阱电阻会使形成于p型阱532与n型源极阱533之间的pn接面正向偏压,造成故障。使用延伸的栅极554可使用薄介电材料544,在p型阱532容许较高掺杂剂浓度(例如,~1.0e17

–

1.0e18 cm

‑

3),同时降低导通电阻(ron)。这降低寄生bjt的电流增益,借以增加bvceo和整体高电压掌控能力。

80.再者,深轻度掺杂p型主体阱531可隔离源极阱530与掺杂轻度n型的基板510。轻度掺杂p型阱531增加装置击穿电压,在与基板背景掺杂的接面具有合适大的耗尽区。同时,本文所揭露之方法所做的薄介电材料544容许p型阱532被重度掺杂,造成反向偏压电流的低电阻路径。

81.如所示,n+掺杂漏极阱535经由轻度掺杂基板510和p型通道阱532耦合到源极阱530。在此配置中,当装置运行时基板510携带电流的部分做为飘移区,当经由栅极550而正偏压时,做为耗尽模式晶体管通道,包括第一栅极552和第二栅极554(类似于图1的装置100的栅极152、154)。隔离沟557可用来保护栅极隔离高漏极电压,传统热局部氧化(locos)也是低成本好选项。大耗尽区形成于深p主体531与n基板510之间。隔离沟在漏极降低电场强度。电流向通道集中,连同通道上的薄栅极介电层,降低通态耗损同时维持装置的高电压承受。

82.类似于装置100,装置500在栅极554与有效通道之间有薄介电材料544,在区542有介电材料540,其厚度大于介电材料544。通过构图导电层555,栅极552、554以及源极阱530和漏极阱535可设有电接点(例如,合适金属或金属硅化物)。为了说明,示例装置500显示为具有n型源极和漏极阱以及p型通道阱的n

‑

p

‑

n晶体管。然而,应了解本文所揭露的方法以p型掺杂取代n型掺杂或反之,则同样可用来制造具有p型通道的p

‑

n

‑

p晶体管。

83.图5a描绘用来制造形成图5b之源极阱530的结构的示例掺杂制程。如所示,一层光阻559在包含漏极阱535的结构上构图,露出源极阱530。倾斜的掺杂剂植入560可用来形成深p掺杂主体阱531。第二掺杂剂植入565可用来形成较浅、较高度掺杂的p阱532,有利于进一步降低寄生路径电阻。在除去光阻559后,类似于配合图3a

‑

3f所述的制程可用来制造装置500。延伸栅极556和厚介电层546可取代沟以使图5c的装置更精巧。可构图额外光罩以在漏极535阻隔p阱532植入物。

84.图1~5的一或多个元件、步骤、特性、功能可重新安排或结合成单一元件、步骤、特性、功能,或在几个元件、步骤、特性、功能中实施。也可增加额外元件、步骤、功能而不偏离本文所揭露的新颖特性。图1~5的装置和/或元件可执行本文所述的一或多个方法、特性、或步骤。

85.要了解所揭露之方法的特定步骤次序是说明示例制程。根据设计偏好,要了解方法的特定步骤次序可重新安排。申请专利范围的方法主张依序的各种步骤,但除非本文特别叙明,否则不限于特定次序。

86.前文令任何熟悉此技艺人士能实施本文所述的各种观点。对这些观点的各种修改都是熟悉此技艺人士很清楚的,本文所界定的一般原理可用于其他观点。因此,申请专利范围不要受限于本文所述的观点,而是与申请专利范围文字一致的完整范畴,其中除非特别指明,否则单数的元件不意味“一个或只有一个”,而是“一个或以上”。除非特别指明,否则“一些”指的是“一个或以上”。“至少其中一个”的项目列表指的是这些项目的任何组合,包含单一构件。例如,“a、b、c的至少其中一个”要涵盖:a;b;c;a和b;a和c;b和c;a、b和c。申请专利范围意欲涵盖熟悉此技艺人士现在已知或将来会知晓的本文所说明的各种要件的结构性和功能性等效者。

87.虽以特定组态和操作顺序来说明实施例,但应了解实施例可增加、省略、或改变元件、操作等等。于是,本文所揭露的实施例是范例而非限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1