芯片封装结构以及制作方法、电子设备与流程

1.本技术涉及芯片封装技术领域,尤其涉及一种芯片封装结构以及制作方法、电子设备。

背景技术:

2.随着封装内系统(system in package,sip)技术的发展,会不断增加封装模组中单位体积内芯片或器件的密度,满足电子设备小型化的要求。

3.为提高封装模组的集成度,一般采用双面封装技术。随着双面封装模组中集成度的要求提高,对双面封装模组的引出输入/输出(input/output,i/o)管脚数量的需求也会增加。目前,由于双面封装模组结构的限制,使得双面封装模组的引出i/o管脚数量也受到限制,从而影响双面封装模组的应用范围。

技术实现要素:

4.本技术实施例提供一种芯片封装结构以及制作方法、电子设备,能够提高封装后的封装模组的引出i/o管脚的数量,提高封装模组的集成度以及封装模组的应用范围。

5.第一方面,本技术提供一种芯片封装结构。该芯片封装结构包括:基板、第一芯片、器件模组、第一塑封层和第二塑封层。其中,器件模组耦接于基板的第一面,且被第一塑封层包覆塑封。第一芯片耦接于基板的第二面,且被第二塑封层包覆塑封。第二塑封层远离基板的一侧设置有rdl布线层,rdl布线层用于引出外部焊接管脚。第二塑封层内设置有第一导体柱,且第一导体柱的第一端与基板耦接,第一导体柱的第二端与rdl布线层耦接。

6.基于上述芯片封装结构,该芯片封装结构中采用双面封装结构,该双面封装结构中,在封装第一芯片的第二塑封层内设置第一导体柱,在第二塑封层远离基板的一侧设置rdl布线层。该rdl布线层用于引出外部焊接管脚,作为引出i/o管脚。第一导体柱分别与基板和 rdl布线层相耦接,使得rdl布线层上的引出i/o管脚能够与基板实现信号连接,从而在提高芯片封装结构的集成度的基础上,使该芯片封装结构能够适用更多的应用场景,进而提高对引出i/o管脚数量具有更高要求的电子设备的小型化竞争力。

7.结合第一方面,一种可能的的设计方式中,上述器件模组可以包括无源器件、wb芯片以及焊接芯片的一种或多种。在上述芯片封装结构中,可以适用多种芯片封装场景。

8.结合第一方面,一种可能的的设计方式中,上述芯片封装结构还可以包括第二芯片。第二芯片堆叠于第一芯片远离基板的一侧,且被第二塑封层包覆塑封。第二芯片远离第一芯片的一侧具有焊接凸点;焊接凸点与rdl布线层耦接。如此,当双面封装结构的其中一面需要封装至少两个芯片(如第一芯片和第二芯片)时,可以通过堆叠的方式进行封装,从而降低芯片封装结构的横向尺寸,提高芯片封装结构中器件的集成度。

9.结合第一方面,一种可能的的设计方式中,第二塑封层可以包括第二内部塑封层和第二外部塑封层。第二内部塑封层用于对第一芯片包覆塑封。第二外部塑封层用于对第二芯片包覆塑封。第一导体柱包括第一内侧导体柱和第一外侧导体柱。第一内侧导体柱位

于第二内部塑封层内。第一外侧导体柱位于第二外部塑封层内。第一内侧导体柱与第一外侧导体柱相耦接。如此,在芯片封装结构的制作过程中,可以对第一芯片和第一内侧导体柱通过第二内部塑封层塑封;还可对第二芯片和第一外侧导体柱通过第二外部塑封层塑封。在完成第二内部塑封层的塑封时,不仅可以对第二内部塑封层进行减薄处理,还可以对第一芯片的衬底进行减薄处理,以降低第一芯片的厚度,从而降低整个芯片封装结构的厚度,提供芯片封装的集成度。

10.结合第一方面,一种可能的的设计方式中,第一芯片和第二芯片之间可以通过贴片胶贴装。

11.结合第一方面,一种可能的的设计方式中,上述基板内可以设置有接地层。第一塑封层的外表面设置有屏蔽层,屏蔽层与接地层耦接。如此,可以使基板内的接地层与屏蔽层之间形成法拉第笼结构,以对基板上的器件模组进行电磁屏蔽,提高芯片封装结构的性能。

12.结合第一方面,一种可能的的设计方式中,屏蔽层的外侧还可以设置有第三塑封层;第三塑封层远离屏蔽层的一侧贴装有天线结构。第一塑封层内设置有第二导体柱;第三塑封层内设置有第三导体柱。第二导体柱的第一端与基板耦接,第二导体柱的第二端与第三导体柱的第一端耦接,第三导体柱的第二端与天线结构耦接。如此,可以利用封装天线(antenna inpackage,aip)技术对天线结构进行封装,提高芯片的集成度,满足芯片模组小型化的要求。

13.结合第一方面,一种可能的的设计方式中,天线结构与第三塑封层之间设置有第一介质层。制作时,可以先在第三塑封层远离基板的一面制作第一介质层,在第一介质层上更容易通过溅射种子层、图形转移、电镀和蚀刻等工艺实现天线结构的制作,从而提高芯片封装结构的稳定性和可靠性。

14.结合第一方面,一种可能的的设计方式中,第二塑封层与rdl布线层之间设置有第二介质层;第二介质层靠近第一导体柱的位置处设置有第一通孔结构,第一导体柱通过第一通孔结构与rdl布线层连接。制作时,可以先在第二塑封层远离基板的一面制作第二介质层,在第二介质层上更容易通过溅射种子层、图形转移、电镀和蚀刻等工艺实现rdl布线层的制作,从而提高芯片封装结构的稳定性和可靠性。

15.第二方面,本技术提供一种电子设备。该电子设备包括外接部件以及与外接部件相耦接的至少一个如上第一方面任一种可能的芯片封装结构。

16.可选地,上述外接部件包括封装基板、转接板,或者,扇出型的至少一层重布线层中的至少一种。

17.第三方面,本技术提供一种芯片封装结构的制作方法。该制作方法包括:在基板的第一面上设置器件模组,使器件模组与基板耦接。在基板的第一面上设置第一塑封层,使器件模组被第一塑封层包覆塑封。在基板的第二面上设置第一芯片和第一导体柱,使第一芯片和第一导体柱均与基板耦接。在基板的第二面上设置第二塑封层,使第一芯片和第一导体柱被第二塑封层包覆塑封。在第二塑封层远离基板的一侧制作rdl布线层,且在rdl布线层上引出外部焊接管脚。

18.结合第三方面,一种可能的的设计方式中,上述方法还可以包括:在第一芯片远离基板的一侧设置第二芯片,第二芯片远离第一芯片的一侧具有焊接凸点;焊接凸点与rdl布线层耦接。

19.结合第三方面,一种可能的的设计方式中,在基板的第二面上设置第一芯片和第一导体柱,包括:在基板的第二面上设置第一芯片和第一内侧导体柱,使第一芯片和第一导体柱均与基板耦接。在第一内侧导体柱上焊接第一外侧导体柱。在基板的第二面上设置第二塑封层,包括:在基板的第二面上设置第二内部塑封层,使第一芯片和第一内侧导体柱被第二内部塑封层包覆塑封。在第二内部塑封层远离基板的一面上设置第二外部塑封层,使第二芯片和第一外侧导体柱被第二外部塑封层包覆塑封。

20.结合第三方面,一种可能的的设计方式中,方法还可以包括:在第一塑封层远离基板的一面制作屏蔽层。

21.结合第三方面,一种可能的的设计方式中,方法还可以包括:在基板的第一面上焊接第二导体柱。

22.结合第三方面,一种可能的的设计方式中,上述方法还可以包括:在第二导体柱远离基板的一端焊接第三导体柱。在屏蔽层远离基板的一侧设置第三塑封层,使屏蔽层和第三导体柱被第三塑封层包覆塑封。在第三塑封层远离屏蔽层的一侧贴装天线结构,使天线结构与第三导体柱耦接。

23.可以理解地,上述提供的任一种芯片封装结构的制作方法、电子设备等,均可以由上文所提供的对应的芯片封装结构来实现,或与上文所提供的对应的芯片封装结构相关联,因此,其所能达到的有益效果可参考上文所提供的芯片封装结构中的有益效果,此处不再赘述。

附图说明

24.图1为本技术实施例提供的一种电子设备的结构示意图;

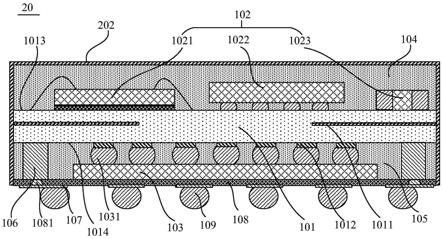

25.图2为本技术实施例提供的芯片封装结构的结构示意图一;

26.图3为本技术实施例提供的芯片封装结构的制作方法的流程图一;

27.图4为执行图3中的s301形成的结构示意图;

28.图5为执行图3中的s302形成的结构示意图;

29.图6为执行图3中的s303形成的结构示意图;

30.图7为执行图3中的s304形成的结构示意图;

31.图8为执行图3中的s305形成的结构示意图;

32.图9为本技术实施例提供的芯片封装结构的结构示意图二;

33.图10为执行图3中的s303形成的另一种结构示意图;

34.图11为执行图3中的s304形成的另一种结构示意图;

35.图12为执行图3中的s305形成的另一种结构示意图;

36.图13为本技术实施例提供的芯片封装结构的结构示意图三;

37.图14为执行图3中的s303和s304形成的另一种结构示意图;

38.图15为本技术实施例提供的芯片封装结构的结构示意图四;

39.图16为本技术实施例提供的芯片封装结构的结构示意图五;

40.图17为本技术实施例提供的芯片封装结构的制作方法的流程图二;

41.图18为执行图17中的s1701形成的一种结构示意图;

42.图19为执行图17中的s1702形成的一种结构示意图;

43.图20为执行图17中的s1703和s1704形成的一种结构示意图;

44.图21为执行图17中的s1705形成的一种中间结构示意图;

45.图22为执行图17中的s1705形成的一种结构示意图;

46.图23为执行图17中的s1706、s1707和s1708形成的结构示意图;

47.图24为本技术实施例提供的另一种电子设备的结构示意图。

48.附图标记:01

‑

电子设备;10

‑

外接部件;20

‑

芯片封装结构;101

‑

基板;1011

‑

接地层;1012

‑ꢀ

焊盘;1013

‑

基板的第一面;1014

‑

基板的第二面;102

‑

器件模组;1021

‑

wb芯片;1022

‑

焊接芯片;1023

‑

无源器件;103

‑

第一芯片;1031

‑

芯片焊球;104

‑

第一塑封层;105

‑

第二塑封层; 1051

‑

第二内部塑封层;1052

‑

第二外部塑封层;106

‑

第一导体柱;1061

‑

第一内侧导体柱;1062

‑ꢀ

第一外侧导体柱;107

‑

rdl布线层;108

‑

介质层;1081

‑

第一互连孔;109

‑

外部焊接管脚;201

‑ꢀ

第二芯片;2011

‑

焊接凸点;202

‑

屏蔽层;203

‑

第三塑封层;204

‑

天线结构;205

‑

第二导体柱;206

‑

第三导体柱;207

‑

介质层。

具体实施方式

49.为了使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术作进一步地详细描述。

50.以下,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,除非另有说明,“多个”的含义是两个或两个以上。

51.此外,本技术中,“上”、“下”等方位术语是相对于附图中的部件示意置放的方位来定义的,应当理解到,这些方向性术语是相对的概念,它们用于相对于的描述和澄清,其可以根据附图中部件所放置的方位的变化而相应地发生变化。

52.在本技术中,除非另有明确的规定和限定,术语“连接”应做广义理解,例如,“连接”可以是固定连接,也可以是可拆卸连接,或成一体;可以是直接相连,也可以通过中间媒介间接相连。此外,术语“耦接”可以是实现信号传输的电性连接的方式。“耦接”可以是直接的电性连接,也可以通过中间媒介间接电性连接。

53.本技术实施例提供一种的电子设备。该电子设备包括手机(mobile phone)、平板电脑(pad)、电脑、智能穿戴产品(例如,智能手表、智能手环)、虚拟现实(virtual reality,vr)终端设备、增强现实(augmented reality,ar)终端设备等电子产品。本技术实施例对上述电子设备的具体形式不做特殊限制。

54.如图1所示,上述电子设备01包括外接部件10以及与该外接部件10相耦接的至少一个芯片封装结构20。其中,上述外接部件10可以包括封装基板、硅基转接板(interposer)以及扇出型(integrated fan

‑

out,info)的至少一层重布线层(redistribution layer,rdl)中的至少一种。

55.上述芯片封装结构20可以包括多个芯片或器件模组。该芯片封装结构20中的芯片可以为逻辑芯片,也可以为存储芯片。芯片封装结构20可以设置如图1所示的焊球阵列(ball gridarray,bga),或者多个阵列排布的铜柱凸块(copper pillar bump),用于与外接部件10相耦接。

56.此外,电子设备01还包括印刷电路板(printed circuit boards,pcb)。上述外接部件10还可以通过电连接件(如bga焊球阵列)与pcb相耦接。在此情况下,上述芯片封装结构20 可以通过外接部件10与pcb上其他芯片或者芯片封装结构实现信号传输。

57.以下对上述芯片封装结构20进行说明。

58.在本技术的一些实施例中,如图2所示,上述芯片封装结构20可以包括基板101、第一芯片103、器件模组102、第一塑封层104和第二塑封层105。其中,基板101是芯片封装的载体,基板101中包括一个或多个布线层,可以对基板101上设置的多个芯片提供电连接,以实现封装后芯片的功能。器件模组102可以包括无源器件1023、打线(wire bonding,wb) 芯片1021以及焊接芯片1022的一种或多种,还可以包括已经完成封装的球珊阵列封装(ballgrid array,bga)器件、栅格阵列封装(land grid array,lga)器件、或者方形扁平无引脚封装(quad flat no

‑

leads package,qfn)器件,本技术实施例不做特殊限制。

59.示例性地,如图2所示,上述器件模组102耦接于上述基板101的第一面1013,且被第一塑封层104包覆塑封。该器件模组102可以包括无源器件1023、wb芯片1021以及焊接芯片1022。应理解,无源器件1023可以通过表面贴装技术(surface mounted technology,smt) 实现与基板101相耦接。wb芯片1021可以指在芯片封装时,通过金属丝线将芯片的电路结构耦合至基板101的芯片。也就是说,wb芯片1021可以通过金属丝线(wirebond)与基板 101耦接。焊接芯片1022可以指在芯片封装时,通过焊接(如焊盘和焊球)的方式将芯片的电路结构耦合至基板101的芯片。也就是说,焊接芯片1022可以通过焊接的方式与基板101 相耦接。

60.上述器件模组102耦接至基板101之后,可以通过第一塑封层104实现该器件模组102 中各器件或芯片的包裹,以实现不同器件或芯片之间的隔离以及器件或芯片与外部器件的隔离。该第一塑封层104的材质可以为树脂和填料混合而成的热固型材料,其中树脂可以为环氧树脂等树脂材料,填料可以为氧化硅(sio2)或氮化硼(bn)等无机材料,填料可以调整树脂的特性,实现高导热、高熔点、低热膨胀系数(coefficient of thermal expansion,cte)的材料特性。当然,第一塑封层104的材质也可以为其他类型的材料,如陶瓷或玻璃等,本技术实施例不做特殊限制。

61.上述第一芯片103耦接于上述基板101的第二面1014,且被第二塑封层105包覆塑封。该第一芯片103可以为焊接芯片1022,并通过焊接(如焊盘、焊球)的方式耦接至上述基板 101。例如,如图2所示,基板101远离器件模组102的一面设置有多个焊盘1012,该第一芯片103通过多个芯片焊球1031焊接至基板101上的多个焊盘1012,从而实现第一芯片103 与基板101相耦接。

62.为了使芯片封装结构20具有用于与外接部件相耦接的焊球阵列,或多个阵列排布的铜柱凸块。在第二塑封层105远离基板101的一侧设置有rdl布线层107,该rdl布线层107 可以用于引出外部焊接管脚109。该外部焊接管脚109可以是如图2所示的bga焊球阵列,也可以是lga连接触点,也可以是多个阵列排布的铜柱凸块,本技术实施例不做特殊限制。

63.在上述芯片封装结构20中,rdl布线层107引出的外部焊接管脚109可以与图1所示的外接部件10实现信号连接。为了使外接部件10能够与芯片封装结构20内部的芯片结构 (如第一芯片或器件模组)形成信号连接,则rdl布线层107引出的外部焊接管脚109需要与芯片封装结构20中的基板101实现信号连接。

64.在此情况下,可以通过铜柱实现rdl布线层107与基板101的信号连接。具体地,可以在第二塑封层105内设置有第一导体柱106,且第一导体柱106的第一端与基板101耦接,第一导体柱106的第二端与上述rdl布线层107耦接。其中,第一导体柱106可以为设置在第二塑封层105内部的铜柱。也即,铜柱的第一端与基板101相耦接,铜柱的第二端与rdl 布线层107,从而实现rdl布线层107与基板101的信号连接。

65.应理解,本技术实施例中的导体柱(如第一导体柱106)是由金属导电材料制成的柱体结构,如采用铜、镍、钨等金属导电材料。导体柱的结构可以是圆柱、三棱柱、圆台状柱体结构等任意柱体结构,本技术实施例不做特殊限制。

66.如此一来,该芯片封装结构20中采用双面封装结构,该双面封装结构中,在封装第一芯片103的第二塑封层105内设置第一导体柱106,在第二塑封层105远离基板101的一侧设置rdl布线层107。该rdl布线层107用于引出外部焊接管脚109,作为引出i/o管脚。第一导体柱106分别与基板101和rdl布线层107相耦接,使得rdl布线层107上的引出i/o 管脚能够与基板101实现信号连接,从而在提高芯片封装结构的集成度的基础上,使该芯片封装结构能够适用更多的应用场景,进而提高对引出i/o管脚数量具有更高要求的电子设备的小型化竞争力。

67.需要说明的是,rdl布线层107可以包括一层布线层,也可以包括多个层叠设置的布线层,本技术实施例不做特殊限制。当rdl布线层107包括多个层叠设置的布线层时,相邻的布线层之间可以通过互连结构互连,使得基板101与rdl布线层107上的引出焊接管脚109 信号连接。

68.应理解,上述芯片(如第一芯片103、wb芯片1021、焊接芯片1022)可以包括衬底和设置与衬底上的电路结构。其中衬底可以为玻璃衬底、非晶硅(amorphous silicon,a

‑

si)衬底、或者碳化硅(sic)衬底等,本技术实施例不做特殊限制。

69.此外,为了便于rdl布线层107的制作,提高rdl布线层107与第二塑封层105之间的结合力,提高整个芯片封装结构20的可靠性,在第二塑封层105与rdl布线层107之间设置有一介质层108(即第二介质层)。该介质层108的材质可以是聚酰亚胺(polyimide,pi)、苯并环丁烯(benzocyclobutene,bcb)等绝缘材料。为了实现rdl布线层107与第一导体柱 106的互连,介质层108靠近第一导体柱106的位置处设置有第一互连孔1081。第一互连孔 1081内可以填充金属材料(如铜、镍等),从而使得第一导体柱106通过第一互连孔1081与 rdl布线层107耦接。

70.以下对图2所示的芯片封装结构20的制作方法进行举例说明。如图3所示,该芯片封装结构的制作方法,包括:

71.s301,在基板101的第一面1013上设置器件模组102,使该器件模组102与基板101耦接。

72.示例性地,如图4所示,对于smt器件(如无源器件1023),可以在基板101的第一面 1013上印刷锡膏,使smt器件贴装在基板101的第一面1013上,并与基板101耦接。对于wb芯片1021,可以先将该芯片的衬底朝向基板101,并采用贴片胶或点胶的方式使wb芯片1021贴装在基板101的第一面1013上,然后再通过金属丝线将wb芯片1021的电路结构与基板101相连接,以实现wb芯片1021与基板101的互连以及信号传输。对于焊接芯片 1022,可以将焊接芯片1022的焊接面(即设置芯片焊球的一面)朝向基板101,并且采用回流焊接、激光焊接等

方式将焊接芯片1022焊接至基板101,从而实现焊接芯片1022与基板 101的互连以及信号传输。

73.s302,在基板101的第一面1013上设置第一塑封层104,使该器件模组102被第一塑封层104包覆塑封。

74.示例性地,如图5所示,在实现了器件模组102与基板101之间的贴装或互连后,可以使用等离子(plasma)工艺对基板101或器件模组102进行处理。经过plasma处理后,可以采用塑封工艺对器件进行塑封包裹,并且器件与器件之间的间隙、器件与基板101之间的间隙均需实现塑封包裹。

75.s303,在基板101的第二面1014上设置第一芯片103和第一导体柱106,使第一芯片 103和第一导体柱106均与基板101耦接。

76.示例性地,如图6所示,在基板101的第二面1014上,对于第一芯片103,可以将第一芯片103的焊接面朝向基板101,并且采用回流焊接、激光焊接等方式将第一芯片103焊接至基板101,从而实现第一芯片103与基板101的互连以及信号传输。

77.如图2所示,第一导体柱106可以为铜柱结构,在基板101的第二面1014上还可以将铜柱结构,采用回流焊接或激光焊接等方式焊接至基板101,从而实现第一导体柱106的第一端与基板101耦接。

78.s304,如图7所示,在基板101的第二面1014上设置第二塑封层105,使第一芯片103 和第一导体柱106被第二塑封层105包覆塑封。

79.示例性地,在实现了第一芯片103和第一导体柱106与基板101相耦接后,可以采用塑封工艺对第一芯片103和第一导体柱106进行塑封包裹,形成第二塑封层105。其中,塑封时,需将第一芯片103和第一导体柱106完全包裹在塑封料的内部。也就是说,塑封料的高度需超出第一芯片103和第一导体柱106的高度。

80.需要说明的是,为了降低整个芯片封装结构20的厚度,第一导体柱106的高度可以略高于第一芯片103的厚度,甚至与第一芯片103的厚度相等,本技术实施例不做特殊限制。

81.s305,在第二塑封层105远离基板101的一侧制作rdl布线层107,且在rdl布线层 107上引出外部焊接管脚109。

82.示例性地,在完成了第二塑封层105对第一芯片103和第一导体柱106的塑封包裹后,为了露出第一导体柱106,可以通过减薄几台对第二塑封层105进行减薄处理,从而裸露出第一导体柱106。

83.裸露出第一导体柱106后,可以在第二塑封层105远离基板101的一侧采用喷涂聚酰亚胺等绝缘材料制作形成介质层108,然后在介质层108正对第一导体柱106的位置处采用采用光刻工艺(包括掩膜、曝光、显影以及刻蚀等工艺)形成第一互连孔1081,在第一互连孔 1081中填充导电材料(如铜、镍等)。最后,可以在介质层108远离第二塑封层105的一侧制作rdl布线层107,如图8所示。

84.在制作rdl布线层107时,可以采用溅射种子层、rdl图形转移、电镀、刻蚀等工艺步骤实现。rdl布线层107可以为一层,也可以为多层互连结构,本技术实施例不做特殊限制。其中,种子层(seed layer),是一层通过化学镀、溅射、或蒸镀等工艺制作在基材表面的很薄的金属层,作为rdl布线层107制作过程中执行电镀工艺的起始金属层,也叫籽晶层。种子层的材料可以为铜、镍等导电金属。rdl图形转移可以通过光刻胶或光敏感光膜等材料经过

曝光、显影等工艺实现。

85.在完成了rdl布线层107的制作之后,可以使上述芯片封装结构20的引出i/o管脚扇出到芯片封装结构20的一侧的整个面上,从而可以实现更多的引出外部焊接管脚109(如焊球),可以适用于该芯片封装结构20中的芯片/器件模组102与外部器件互连链路较多的场景。

86.在本技术的另一些实施例中,如图9所示,上述芯片封装结构20还可以包括第二芯片 201。该第二芯片201堆叠于上述第一芯片103远离基板101的一侧,并且也可以被第二塑封层105包覆塑封。如此,当双面封装结构的其中一面需要封装至少两个芯片(如第一芯片103 和第二芯片201)时,可以通过堆叠的方式进行封装,从而降低芯片封装结构的横向尺寸,提高芯片封装结构中器件的集成度。

87.需要说明的是,上述第二芯片201可以为带焊接凸点(bump)2011的芯片。为了使第二芯片201能够与基板101实现信号连接,如图9所示,可以将第二芯片201与第一芯片103 背靠背进行贴装,即可以将第一芯片103的衬底和第二芯片201的衬底,通过贴片胶实现贴装。也就是说,在贴装完成后,第二芯片201远离第一芯片103的一侧是具有焊接凸点2011 的。该第二芯片201的焊接凸点2011可以与rdl布线层107相耦接。当第二芯片201的焊接凸点2011与rdl布线层107相耦接后,由于rdl布线层107通过第一导体柱106与基板 101实现信号连接,从而使得第二芯片201也可以与基板101实现信号连接。

88.在此情况下,在上述包括第二芯片201的芯片封装结构20在制作过程中,可以在上述 s303步骤中,完成了第一芯片103焊接至基板101后,在第一芯片103的背面(即第一芯片 103远离基板101的一面)上点胶,然后将第二芯片201的衬底朝向第一芯片103,使第二芯片201贴装到第一芯片103上,以形成如图10所示的结构。

89.在执行上述s304步骤时,还需要对第二芯片201进行塑封包裹,如图11所示。由于第二芯片201具有焊接凸点2011,第二塑封层105中塑封料的高度,需超出第一导体柱106的高度,以及需超出第一芯片103和第二芯片201的厚度之和。应理解,为降低整个芯片封装结构20的厚度,第一导体柱106的高度可以略高于第一芯片103和第二芯片201的厚度之和,例如,第一导体柱106的高度可以比第一芯片103和第二芯片201的厚度之和高0至200 微米(um),或者第一导体柱106的高度可以与第一芯片103和第二芯片201的厚度相等。

90.在执行上述s305步骤时,为了使第二芯片201的焊接凸点2011可以与rdl布线层107 相耦接,需要对第二塑封层105进行减薄,并裸露出第二芯片201的焊接凸点2011以及第一导体柱106。如图12所示,在第二塑封层105远离基板101的一侧制作形成的介质层108上,对应第二芯片201的焊接凸点2011的位置处还需采用光刻工艺形成第一互连孔,并在互连孔内填充导电材料,以使第二芯片201与rdl布线层107形成互连,从而在rdl布线层107 通过第一导体柱106与基板101形成互连的情况下,第二芯片201也可以与基板101形成互连而实现信号连接。

91.在本技术的另一些实施例中,如图13所示所示的芯片封装结构20中,图9所示的第二塑封层105可以包括第二内部塑封层1051和第二外部塑封层1052。其中,第二内部塑封层 1051可以用于对第一芯片103包覆塑封。第二外部塑封层1052可以用于对第二芯片201包覆塑封。图9所示的第一导体柱106也可以分为第一内侧导体柱1061和第一外侧导体柱1062。第一内侧导体柱1061位于所述第二内部塑封层1051内。第一外侧导体柱1062位于第二外部

塑封层1052内。第一内侧导体柱1061与第一外侧导体柱1062相耦接。

92.需要说明的是,在图9所示的芯片封装结构20中,通过第二塑封层105对第一芯片103、第二芯片201、第一导体柱106整体塑封,塑封后的高度至少是第一芯片和第二芯片的厚度之和。然而,在图13所示的芯片封装结构20中,第一芯片103和第一内侧导体柱1061由第二内部塑封层1051包覆塑封,塑封后可以对第一芯片103的衬底、第一内侧导体柱1061以及第二内部塑封层1051整体减薄,从而降低第一芯片103的厚度。相应地,第二芯片201、第一外侧导体柱1062由第二外部塑封层1052包覆塑封。塑封完成后,第二内部塑封层1051 和第二外部塑封层1052的高度为减薄后的第一芯片103的厚度与第二芯片201的厚度之和,从而可以降低芯片封装结构20的厚度。

93.在此情况下,在对图13所示的芯片封装结构20的制作过程中,可以先执行上述s303步骤,在基板101的第二面1014上设置第一芯片103和第一内侧导体柱1061,然后执行上述 s304步骤,如图14中的(a)所示,对第一芯片103和第一内侧导体柱1061完成塑封包裹,形成第二内部塑封层1051。在形成第二内部塑封层1051后,可以对形成的第二内部塑封层 1051进行减薄处理。在减薄处理的过程中,不仅可以对第二内部塑封层1051进行减薄处理,还可以对第一芯片103的衬底进行减薄处理,以降低第一芯片103的厚度,并裸露出第一内侧导体柱1061。

94.在完成对第二内部塑封层1051的减薄处理之后,如图14中的(b)所示,可以在第一芯片103的背面(即第一芯片103的衬底面)贴装第二芯片201,并且在第一内侧导体柱1061 上焊接铜柱,作为第一外侧导体柱1062。在完成了第一外侧导体柱1062的焊接和第二芯片 201的贴装后,可以执行上述s304步骤中的类似方法,对第二芯片201和第一外侧导体柱 1062进行塑封包裹,以形成第二外部塑封层1052,如图14中的(c)所示。接着,可以对第二外部塑封层1052进行减薄处理,并裸露出第二芯片201的焊接凸点以及第一外侧导体柱 1062。

95.此外,在上述图2、图9和图13所示的芯片封装结构20中,基板101内还设置有接地层1011。在第一塑封层104的外表面设置有屏蔽层202。该屏蔽层202与基板101内的接地层1011实现耦接,从而使基板101内的接地层1011与屏蔽层202之间形成法拉第笼结构,以对基板101上的器件模组102进行电磁屏蔽。具体地,如图2、图9和图13所示,在基板 101的侧面上有从基板101的内部延伸至基板101的边缘的接地网络层(即接地层1011),在第一塑封层104的外表面形成的屏蔽层202沿着第一塑封层104的外表面延伸至基板101的接地层1011处,并与接地层1011耦接。

96.在此情况下,屏蔽层202的制作可以采用溅射工艺实现,屏蔽层202的结构可以为三层金属薄膜结构,例如不锈钢层(steel use stainless,sus)、铜层以及不锈钢层sus三层结构。当然,屏蔽层202的制作也可以采用喷涂工艺实现,利用喷涂工艺制作的屏蔽层202可以采用导电银浆等屏蔽材料,本技术实施例对屏蔽层202的材质和制作方法不做特殊限制。

97.在本技术的另一些实施例中,可以利用封装天线(antenna in package,aip)技术对天线进行封装,例如对于射频集成电路(radio frequency intergreted circuit,rfic)射频前端(radiofrequency front end,rffe)器件,以及天线(antenna,ant)结构可以封装到一个芯片封装结构20中,以提高芯片的集成度,满足芯片模组小型化的要求。

98.下面以天线结构204封装至图2或图9所示的芯片封装结构20为例进行说明。示例性地,如图15和图16所示,在图2和图9所述的芯片封装结构20的基础上,可以在屏蔽层 202的外侧设置第三塑封层203,使第三塑封层203将整个屏蔽层202进行包覆塑封。对于天线结构204,可以将天线结构204贴装在第三塑封层203远离上述屏蔽层202的一侧。其中,屏蔽层202也可以作为天线结构204的接地参考面。

99.为了使天线结构204与基板101之间形成馈电连接,可以在上述第一塑封层104内设置第二导体柱205,可以在上述第三塑封层203内设置第三导体柱206。其中,第二导体柱205 的第一端与基板101耦接,第二导体柱205的第二端与第三导体柱206的第一端耦接,第三导体柱206的第二端与天线结构204耦接。应理解,第二导体柱205和第三导体柱206均可以为铜柱结构。

100.在此情况下,制作该包括天线结构204的芯片封装结构20的方法,如图17所示,可以包括:

101.s1701,在基板101的第一面1013上设置器件模组102,并焊接第二导体柱205,使该器件模组102和第二导体柱205均与基板耦接。

102.示例性地,可以在执行上述图3中的s301步骤时,将第二导体柱205焊接至基板101的第一面1013上,如图18所示。

103.s1702,在基板101的第一面1013上设置第一塑封层104,使该器件模组102和第二导体柱205被第一塑封层104包覆塑封。

104.示例性地,可以在执行上述s302步骤,将器件模组102和第二导体柱205均塑封在第一塑封层104内,如图19所示。

105.s1703,在基板101的第二面1014上设置第一芯片103和第一导体柱106,使第一芯片 103和第一导体柱106均与基板101耦接。

106.s1704,在基板101的第二面1014上设置第二塑封层105,使第一芯片103和第一导体柱106被第二塑封层105包覆塑封。

107.在第一塑封层104制作完成之后,可以执行上述s1703和s1704步骤,形成如图20中的 (a)或图20中的(b)所示的结构,具体的制作方法可以参考上述s303和s304中的描述,此处不再赘述。

108.s1705,在第一塑封层远离基板的一面制作屏蔽层。

109.在形成如图20中的(a)或图20中的(b)所示的结构后,可以采用减薄几台对第一塑封层104进行减薄处理,使第二导体柱205的第二端裸露出来。然后可以通过分板机从第一塑封层104的上表面(即远离基板101的一面)向基板101的第二面1014切割形成l形区域,并裸露出基板101上的接地网络(即接地层1011),如图21中的(a)或图21中的(b) 所示。接着,可以在经过减薄后的第一塑封层104的表面(即远离基板101的一面),以及切割形成的l形区域制作屏蔽层202,最终可以形成l形结构的屏蔽层200,如图22中的(a) 或图22中的(b)所示。屏蔽层202的制作可以采用溅射工艺或喷涂工艺实现,屏蔽层202 的材质可以为三层金属薄膜结构,也可以是导电银浆等屏蔽材料。

110.需要说明的是,在此芯片封装结构20中,屏蔽层202的制作需要裸露出第二导体柱205,也就是说,在第二导体柱205的第二端上以及第二导体柱205的第二端周围的部分不需要制作屏蔽层202,以便实现天线结构204通过第二导体柱205与第三导体柱206与基板101

实现信号连接。

111.s1706,在第二导体柱远离基板的一端焊接第三导体柱。

112.在屏蔽层202制作完成之后,如图23中的(a)或图23中的(b)所示,可以在裸露出的第二导体柱205的第二端上焊接第三导体柱206。第三导体柱206可以通过回流焊接或激光焊接的方式进行焊接。

113.s1707,在屏蔽层远离基板的一侧制作第三塑封层,使屏蔽层和第三导体柱通过第三塑封层包覆塑封。

114.如图23中的(a)或图23中的(b)所示,在第三导体柱206焊接到第二导体柱205之后,可以在屏蔽层202上面(即屏蔽层202远离基板101的一面)上进行二次塑封,形成第三塑封层203,并且使第三塑封层203可以将整个屏蔽层202以及整个第三导体柱206覆盖。

115.s1708,在第三塑封层远离屏蔽层的一侧贴装天线结构,使天线结构与第三导体柱耦接。

116.如图23中的(a)或图23中的(b)所示,在第三塑封层203制作完成之后,可以采用减薄几台对第三塑封层203进行减薄处理,使第三导体柱206的第二端裸露出来。接着,可以在第三塑封层203的表面(即第三塑封层203远离屏蔽层202的一面)制作天线结构204。天线结构204可以通过溅射种子层、图形转移、电镀、蚀刻等工艺实现。

117.此外,在图15和图16所示的芯片封装结构20中,天线结构204与第三塑封层203之间设置有介质层207(即第一介质层)。相比于第三塑封层203,介质层207能够提高天线结构 204与第三塑封层203之间的结合力,在介质层207上更容易通过溅射种子层、图形转移、电镀和蚀刻等工艺实现天线结构204的制作,从而提高芯片封装结构的稳定性和可靠性。

118.s1709,在第二塑封层105远离基板101的一侧制作rdl布线层107,且在rdl布线层 107上引出外部焊接管脚109。

119.在上述天线结构204制作完成形成图23中的(a)或图23中的(b)的结构后,可以在执行上述s1709步骤完成rdl布线层的制作,以及外部焊接管脚的制作,该s1709步骤可以参考上述s305步骤,此处不再赘述。

120.示例性地,图24为本技术实施例提供的另一种电子设备的结构示意图。该电子设备可以是终端设备,也可以是基站。如图24所示,该电子设备可包括应用子系统,内存(memory),大容量存储器(massive storge),基带子系统,射频集成电路(radio frequency intergreted circuit, rfic),射频前端(radio frequency front end,rffe)器件,以及天线(antenna,ant),这些器件可以通过各种互联总线或其他电连接方式耦合。

121.图24中,ant_1表示第一天线,ant_n表示第n天线,n为大于1的正整数。tx表示发射路径,rx表示接收路径,不同的数字表示不同的路径。fbrx表示反馈接收路径,prx 表示主接收路径,drx表示分集接收路径。hb表示高频,lb表示低频,两者是指频率的相对高低。bb表示基带。应理解,图24中的标记和组件仅为示意目的,仅作为一种可能的实现方式,本技术实施例还包括其他的实现方式。

122.其中,应用子系统可作为电子设备的主控制系统或主计算系统,用于运行主操作系统和应用程序,管理整个电子设备的软硬件资源,并可为用户提供用户操作界面。应用子系统可包括一个或多个处理核心。此外,应用子系统中也可包括与其他子系统(例如基带子系统) 相关的驱动软件。基带子系统也可包括以及一个或多个处理核心,以及硬件加速器

(hardwareaccelerator,hac)和缓存等。

123.图24中,rffe器件,rfic 1(以及可选的rfic 2)可以共同组成射频子系统。射频子系统可以进一步分为射频接收通道(rf receive path)和射频发射通道(rf transmit path)。射频接收通道可通过天线接收射频信号,对该射频信号进行处理(如放大、滤波和下变频)以得到基带信号,并传递给基带子系统。射频发射通道可接收来自基带子系统的基带信号,对基带信号进行射频处理(如上变频、放大和滤波)以得到射频信号,并最终通过天线将该射频信号辐射到空间中。具体地,射频子系统可包括天线开关,天线调谐器,低噪声放大器(lownoise amplifier,lna),功率放大器(power amplifier,pa),混频器(mixer),本地振荡器(localoscillator,lo)、滤波器(filter)等电子器件,这些电子器件可以根据需要集成到一个或多个芯片中。天线有时也可以认为是射频子系统的一部分。

124.基带子系统可以从基带信号中提取有用的信息或数据比特,或者将信息或数据比特转换为待发射的基带信号。这些信息或数据比特可以是表示语音、文本、视频等用户数据或控制信息的数据。例如,基带子系统可以实现诸如调制和解调,编码和解码等信号处理操作。对于不同的无线接入技术,例如5g nr和4g lte,往往具有不完全相同的基带信号处理操作。因此,为了支持多种移动通信模式的融合,基带子系统可同时包括多个处理核心,或者多个 hac。

125.此外,由于射频信号是模拟信号,基带子系统处理的信号主要是数字信号,电子设备中还需要有模数转换器件。模数转换器件包括将模拟信号转换为数字信号的模数转换器(analogto digital converter,adc),以及将数字信号转换为模拟信号的数模转换器(digital to analogconverter,dac)。本技术实施例中,模数转换器件可以设置在基带子系统中,也可以设置在射频子系统中。

126.应理解,本技术实施例中,处理核心可表示处理器,该处理器可以是通用处理器,也可以是为特定领域设计的处理器。例如,该处理器可以是中央处理单元(center processing unit, cpu),也可以是数字信号处理器(digital signal processor,dsp)。该处理器也可以是微控制器(micro control unit,mcu),图形处理器(graphics processing unit,gpu)、图像信号处理器(image signal processing,isp),音频信号处理器(audio signal processor,asp),以及为人工智能(artificial intelligence,ai)应用专门设计的处理器。ai处理器包括但不限于神经网络处理器(neural network processing unit,npu),张量处理器(tensor processing unit,tpu)以及被称为ai引擎的处理器。

127.硬件加速器可用于实现一些处理开销较大的子功能,如数据包(data packet)的组装和解析,数据包的加解密等。这些子功能采用通用功能的处理器也可以实现,但是因为性能或成本的考量,采用硬件加速器可能更加合适。因此,硬件加速器的种类和数目可以基于需求来具体选择。在具体的实现方式中,可以使用现场可编程门阵列(field programmable gate array, fpga)和专用集成电路(application specified intergated circuit,asic)中的一种或组合来实现。当然,硬件加速器中也可以使用一个或多个处理核心。

128.存储器可分为易失性存储器(volatile memory)和非易失性存储器(non

‑

volatile memory, nvm)。易失性存储器是指当电源供应中断后,内部存放的数据便会丢失的存储器。目前,易失性存储器主要是随机存取存储器(random access memory,ram),包括

静态随机存取存储器(static ram,sram)和动态随机存取存储器(dynamic ram,dram)。非易失性存储器是指即使电源供应中断,内部存放的数据也不会因此丢失的存储器。常见的非易失性存储器包括只读存储器(read only memory,rom)、光盘、磁盘以及基于闪存(flash memory)技术的各种存储器等。通常来说,内存可以选用易失性存储器,大容量存储器可以选用非易失性存储器,例如磁盘或闪存。

129.本技术实施例中,基带子系统和射频子系统共同组成通信子系统,为电子设备提供无线通信功能。通常,基带子系统负责管理通信子系统的软硬件资源,并且可以配置射频子系统的工作参数。基带子系统的一个或多个处理核心可以集成为一个或多个芯片,该芯片可称为基带处理芯片或基带芯片。类似地,rfic可以被称为射频处理芯片或射频芯片。此外,随着技术的演进,通信子系统中射频子系统和基带子系统的功能划分也可以有所调整。例如,将部分射频子系统的功能集成到基带子系统中,或者将部分基带子系统的功能集成到射频子系统中。在实际应用中,基于应用场景的需要,电子设备可采用不同数目和不同类型的处理核心的组合。

130.本技术实施例中,射频子系统可包括独立的天线,独立的射频前端(rf front end,rffe) 器件,以及独立的射频芯片。射频芯片有时也被称为接收机(receiver)、发射机(transmitter) 或收发机(transceiver)。天线、射频前端器件和射频处理芯片都可以单独制造和销售。当然,射频子系统也可以基于功耗和性能的需求,采用不同的器件或者不同的集成方式。例如,将属于射频前端的部分器件集成在射频芯片中,甚至将天线和射频前端器件都集成射频芯片中,该射频芯片也可以称为射频天线模组或天线模组。

131.本技术实施例中,基带子系统可以作为独立的芯片,该芯片可被称调制解调器(modem) 芯片。基带子系统的硬件组件可以按照modem芯片为单位来制造和销售。modem芯片有时也被称为基带芯片或基带处理器。此外,基带子系统也可以进一步集成在soc芯片中,以soc 芯片为单位来制造和销售。基带子系统的软件组件可以在芯片出厂前内置在芯片的硬件组件中,也可以在芯片出厂后从其他非易失性存储器中导入到芯片的硬件组件中,或者还可以通过网络以在线方式下载和更新这些软件组件。

132.需要说明的是,上述电子设备中的天线、射频前端、以及rfic可以通过上述图15和图 16所示的芯片封装结构实现。也就是说,天线、射频前端以及rfic可以封装到上述图15和图16所示的芯片封装结构中,以提高电子设备中各器件模组的集成度。

133.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1