一种基于系统总线的三维芯片及其三维化方法

1.本发明属于集成电路芯片设计领域,并特别涉及一种基于系统总线的三维芯片及其三维化方法。

背景技术:

2.如今在摩尔定律放缓的时代,就提高晶体管的密度提出了3d芯片的概念。目前多家企业已经实现了在存储芯片的多层堆叠。针对于逻辑芯片如何实现3d化成为了人们关注的话题。众所周知,若采用先进的制造工艺就意味着更高的流片成本,若能够实现逻辑芯片的3d化也就意味着可以采用成本低的工艺技术来实现先进工艺芯片的性能。

3.在芯片3d化的发展过程中,相继出现了tsv和dbi的封装技术,这为3d芯片在物理上能够实现奠定了基础。就如何将芯片设计实现3d化,本发明提出具体的同构逻辑芯片3d化的实现方法。

4.目前3d化主流是存储芯片,与逻辑芯片存在本质区别。本发明的三维逻辑芯片设计要通过系统总线来实现芯片间的互连,要在系统总线上做出很大调整。故无法按照存储芯片的三维化思路处理逻辑芯片。

技术实现要素:

5.本发明要解决的问题是如何在设计上实现同构芯片之间的通信,以实现芯片的3d化。为解决上述问题,本发明提供了一种实现同构芯片3d化的设计方法。该3d芯片包括:

6.两片及以上同构逻辑芯片;

7.多层同构逻辑芯片垂直堆叠,芯片的各个模块完全重合;

8.各层芯片之间通过系统总线在片内或者片外互连实现片间通信。

9.本发明提出同构芯片垂直堆叠的设计方法。将多层同构逻辑芯片进行垂直堆叠,通过系统总线实现片间通信,完成同构芯片3d化。

10.本发明还提出了一种基于系统总线的三维芯片,其中包括:

11.至少两片同构逻辑芯片,且该同构逻辑芯片间相互垂直堆叠,同构逻辑芯片间的各个模块相互重合,

12.每片同构逻辑芯片内部的系统总线与相邻其同构逻辑芯片内部的系统总线相连,以构成该三维芯片。

13.所述的基于系统总线的三维芯片,其中该相连包括片内连接和/或片外相连。

14.所述的基于系统总线的三维芯片,其中该片内连接包括在该三维芯片内直接键合,和/或在该三维芯片内以硅通孔的方式相连。

15.所述的基于系统总线的三维芯片,其中该片外连接具体为:同构逻辑芯片中系统总线向三维芯片片外延伸至三维芯片的外围,在三维芯片外通过键合的方式相互连接。

16.所述的基于系统总线的三维芯片,其中每片同构逻辑芯片内部的系统总线通过多条通道与相邻其同构逻辑芯片内部的系统总线相连。

17.本发明还提出了一种基于系统总线的三维芯片的三维化方法,其中包括:

18.步骤1、将同构逻辑芯片相互垂直堆叠,且同构逻辑芯片间的各个模块相互重合;

19.步骤2、每片同构逻辑芯片通过其内部的系统总线与相邻同构逻辑芯片内部的系统总线相连,以形成该三维芯片。

20.所述的基于系统总线的三维芯片的三维化方法,其中该相连包括片内连接和/或片外相连。

21.所述的基于系统总线的三维芯片的三维化方法,其中该片内连接包括在该三维芯片内以硅通孔的方式相连;

22.在每个同构逻辑芯片的底部与顶部分别设有bump与pad,bump与pad之间形成硅通孔,该同构逻辑芯片中系统总线上的i/o与bump相连。

23.所述的基于系统总线的三维芯片的三维化方法,其中该片外连接具体为:同构逻辑芯片中系统总线向三维芯片片外延伸至三维芯片的外围,在三维芯片外通过键合的方式相互连接。

24.所述的基于系统总线的三维芯片的三维化方法,其中每片同构逻辑芯片内部的系统总线通过多条通道与相邻其同构逻辑芯片内部的系统总线相连。

附图说明

25.图1a和图1b为本发明的一种实施例,所述的3d芯片由两层同构芯片堆叠,在系统总线通过直接键合的方式在片内实现互连的效果图;

26.图2为本发明的一种实施例,所述的3d芯片由两层同构芯片堆叠,在系统总线通过wirebonding的方式在片外实现互连的效果图;

27.图3为本发明的一种实施例,所述的3d芯片由三层同构芯片堆叠,在系统总线通过直接键合和硅通孔的方式在片内实现互连的效果图;

28.图4为本发明的一种实施例,所述的3d芯片是由三层同构芯片堆叠,在系统总线通过wirebonding的方式在片外实现互连的效果图;

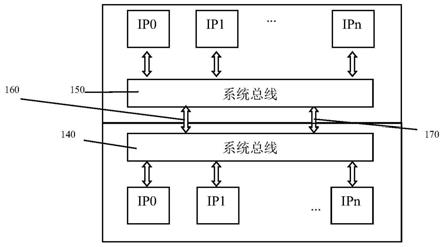

29.图5为本发明通过顶部与底部在片内以硅通孔(tsv)的方式进行堆叠的效果图。

具体实施方式

30.为让本发明的上述特征和效果能阐述的更明确易懂,下文特举实施例,并配合说明书附图作详细说明如下。

31.在本发明优选的实施例中,提出了多层同构逻辑芯片垂直堆叠的方式。其中包括:两片及两片以上同构逻辑芯片在设计上如何在片内或者片外实现信息通信,来完成芯片的3d化。

32.如图1a和图1b所示,该3d芯片(100),它是由两片同构逻辑芯片(110和120)通过顶部与顶部在片内以直接键合(130)的方式(比如:dbi)进行堆叠。芯片中的各个模块完全重叠。将各个芯片中的系统总线(140和150)通过直接键合的方式实现片间的信息交互,完成芯片的3d化设计。

33.在每片芯片的系统总线之间形成两条通道(160和170),用于各自作为主(从)设备时进行信息交互。例如若第一层芯片为主设备,第二层芯片为从设备时用一条,若第二层芯

片作主设备,第一层芯片就为从设备用另外一条通道。

34.如图2所示,该3d芯片(200),它是由两片同构逻辑芯片(210和220)通过顶部与顶部的方式进行堆叠。芯片中的各个模块完全重叠。将各个芯片中的系统总线(250和260)向片外延伸到芯片的外围,在片外通过键合wire bonding(240)的方式实现片间的信息交互,完成芯片的3d化设计。片外信息交互的优点是难度低,成本低,缺点是延时就会高。

35.片内键合优点延时低,缺点难度大,成本就高。

36.为降低通信延时,其wirebonding的连接方法是:每层芯片要与其他层芯片进行两两互连,比如三层芯片1,2相连;2,3相连;1,3相连。

37.如图3所示,该3d芯片(300),它是由三层同构逻辑芯片(310、320和330)堆叠而成,其中第一层和第二层(310和320)通过顶部与顶部在片内通过直接键合(340)的方式(比如:dbi)进行堆叠,第二层和第三层(320和330)通过顶部与底部在片内以硅通孔(tsv)(350)的方式进行堆叠。芯片中的各个模块完全重叠。将各个芯片中的系统总线(360、370和380)通过直接键合(340)和/或硅通孔(350)的方式实现片间的信息交互,完成芯片的3d化设计。

38.具体来说,本发明的三维逻辑芯片设计要通过系统总线来实现芯片间的互连,要在系统总线上做出很大调整,包括如图5所示,通过顶部与底部在片内以硅通孔(tsv)的方式进行堆叠。芯片中的各个模块完全重叠。在单个芯片的底部与顶部分别作上bump凸块与pad引脚,bump与pad之间形成硅通孔,将系统总线上的i/o引入到bump上,以此实现各层芯片之间的信息交互。

39.如图4所示,该3d芯片(400),它是由三层同构逻辑芯片(410、420和430)堆叠而成,其中第一层和第二层(410和420)通过顶部与顶部进行堆叠,第二层和第三层(420和430)通过顶部与底部进行堆叠。芯片中的各个模块完全重叠。将各个芯片中的系统总线(440、450和460)向片外延伸到芯片的外围,在片外通过wirebonding(470)的方式实现片间的信息交互,完成芯片的3d化设计。

40.以下为与上述实施例对应的方法实施例,本实施方式可与上述实施方式互相配合实施。上述实施方式中提到的相关技术细节在本实施方式中依然有效,为了减少重复,这里不再赘述。相应地,本实施方式中提到的相关技术细节也可应用在上述实施方式中。

41.本发明还提出了一种基于系统总线的三维芯片的三维化方法,其中包括:

42.步骤1、将同构逻辑芯片相互垂直堆叠,且同构逻辑芯片间的各个模块相互重合;

43.步骤2、每片同构逻辑芯片通过其内部的系统总线与相邻同构逻辑芯片内部的系统总线相连,以形成该三维芯片。

44.所述的基于系统总线的三维芯片的三维化方法,其中该相连包括片内连接和/或片外相连。

45.所述的基于系统总线的三维芯片的三维化方法,其中该片内连接包括在该三维芯片内以硅通孔的方式相连;

46.在每个同构逻辑芯片的底部与顶部分别设有bump与pad,bump与pad之间形成硅通孔,该同构逻辑芯片中系统总线上的i/o与bump相连。

47.所述的基于系统总线的三维芯片的三维化方法,其中该片外连接具体为:同构逻辑芯片中系统总线向三维芯片片外延伸至三维芯片的外围,在三维芯片外通过键合的方式相互连接。

48.所述的基于系统总线的三维芯片的三维化方法,其中每片同构逻辑芯片内部的系统总线通过多条通道与相邻其同构逻辑芯片内部的系统总线相连。

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1